Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                            |

|----------------------------|--------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                     |

| Core Processor             | ARM® Cortex®-M4                                                                            |

| Core Size                  | 32-Bit Single-Core                                                                         |

| Speed                      | 80MHz                                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                                 |

| Number of I/O              | 51                                                                                         |

| Program Memory Size        | 1MB (1M x 8)                                                                               |

| Program Memory Type        | FLASH                                                                                      |

| EEPROM Size                | -                                                                                          |

| RAM Size                   | 128K x 8                                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                      |

| Oscillator Type            | Internal                                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                          |

| Mounting Type              | Surface Mount                                                                              |

| Package / Case             | 64-LQFP                                                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l476rgt6tr                    |

|                            |                                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table 2. STM32L476xx family device features and peripheral counts (continued)

| Peripheral            | STM32L476<br>Zx | STM32L476<br>Qx                                                                                                                                    | STM32L476<br>Vx | STM32L476<br>Mx | STM32L476<br>Jx | STM32L476<br>Rx |  |  |  |

|-----------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|-----------------|--|--|--|

| Max. CPU frequency    |                 | 80 MHz                                                                                                                                             |                 |                 |                 |                 |  |  |  |

| Operating voltage     |                 | 1.71 to 3.6 V                                                                                                                                      |                 |                 |                 |                 |  |  |  |

| Operating temperature |                 | Ambient operating temperature: -40 to 85 °C / -40 to 105 °C / -40 to 125 °C<br>Junction temperature: -40 to 105 °C / -40 to 125 °C / -40 to 130 °C |                 |                 |                 |                 |  |  |  |

| Packages              | LQFP144         | UFBGA132                                                                                                                                           | LQFP100         | WLCSP81         | WLCSP72         | LQFP64          |  |  |  |

1. For the LQFP100 package, only FMC Bank1 is available. Bank1 can only support a multiplexed NOR/PSRAM memory using the NE1 Chip Select.

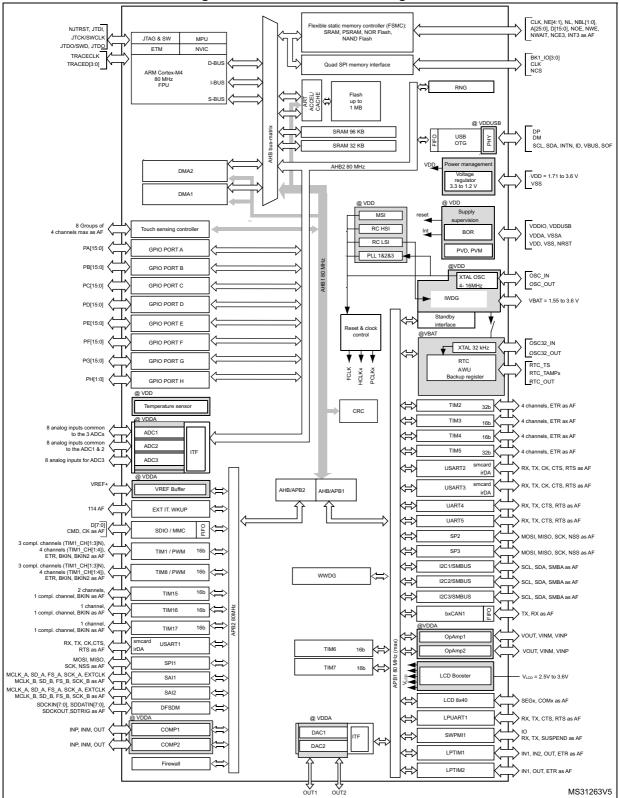

Figure 1. STM32L476xx block diagram

# 3.4 Embedded Flash memory

STM32L476xx devices feature up to 1 Mbyte of embedded Flash memory available for storing programs and data. The Flash memory is divided into two banks allowing read-while-write operations. This feature allows to perform a read operation from one bank while an erase or program operation is performed to the other bank. The dual bank boot is also supported. Each bank contains 256 pages of 2 Kbyte.

Flexible protections can be configured thanks to option bytes:

- Readout protection (RDP) to protect the whole memory. Three levels are available:

- Level 0: no readout protection

- Level 1: memory readout protection: the Flash memory cannot be read from or written to if either debug features are connected, boot in RAM or bootloader is selected

- Level 2: chip readout protection: debug features (Cortex-M4 JTAG and serial wire), boot in RAM and bootloader selection are disabled (JTAG fuse). This selection is irreversible.

| Area      | Protection<br>level | U    | ser executio | on                 | Debug, boot from RAM or boot<br>from system memory (loader) |       |                    |  |

|-----------|---------------------|------|--------------|--------------------|-------------------------------------------------------------|-------|--------------------|--|

|           | IEVEI               | Read | Write        | Erase              | Read                                                        | Write | Erase              |  |

| Main      | 1                   | Yes  | Yes          | Yes                | No                                                          | No    | No                 |  |

| memory    | 2                   | Yes  | Yes          | Yes                | N/A                                                         | N/A   | N/A                |  |

| System    | 1                   | Yes  | No           | No                 | Yes                                                         | No    | No                 |  |

| memory    | 2                   | Yes  | No           | No                 | N/A                                                         | N/A   | N/A                |  |

| Option    | 1                   | Yes  | Yes          | Yes                | Yes                                                         | Yes   | Yes                |  |

| bytes     | 2                   | Yes  | No           | No                 | N/A                                                         | N/A   | N/A                |  |

| Backup    | 1                   | Yes  | Yes          | N/A <sup>(1)</sup> | No                                                          | No    | N/A <sup>(1)</sup> |  |

| registers | 2                   | Yes  | Yes          | N/A                | N/A                                                         | N/A   | N/A                |  |

| SRAM2     | 1                   | Yes  | Yes          | Yes <sup>(1)</sup> | No                                                          | No    | No <sup>(1)</sup>  |  |

| STAIVIZ   | 2                   | Yes  | Yes          | Yes                | N/A                                                         | N/A   | N/A                |  |

Table 3. Access status versus readout protection level and execution modes

1. Erased when RDP change from Level 1 to Level 0.

- Write protection (WRP): the protected area is protected against erasing and programming. Two areas per bank can be selected, with 2-Kbyte granularity.

- Proprietary code readout protection (PCROP): a part of the flash memory can be

protected against read and write from third parties. The protected area is execute-only:

it can only be reached by the STM32 CPU, as an instruction code, while all other

accesses (DMA, debug and CPU data read, write and erase) are strictly prohibited.

One area per bank can be selected, with 64-bit granularity. An additional option bit

(PCROP\_RDP) allows to select if the PCROP area is erased or not when the RDP

protection is changed from Level 1 to Level 0.

## 3.9.3 Voltage regulator

Two embedded linear voltage regulators supply most of the digital circuitries: the main regulator (MR) and the low-power regulator (LPR).

- The MR is used in the Run and Sleep modes and in the Stop 0 mode.

- The LPR is used in Low-Power Run, Low-Power Sleep, Stop 1 and Stop 2 modes. It is also used to supply the 32 Kbyte SRAM2 in Standby with RAM2 retention.

- Both regulators are in power-down in Standby and Shutdown modes: the regulator output is in high impedance, and the kernel circuitry is powered down thus inducing zero consumption.

The ultralow-power STM32L476xx supports dynamic voltage scaling to optimize its power consumption in run mode. The voltage from the Main Regulator that supplies the logic (VCORE) can be adjusted according to the system's maximum operating frequency.

There are two power consumption ranges:

- Range 1 with the CPU running at up to 80 MHz.

- Range 2 with a maximum CPU frequency of 26 MHz. All peripheral clocks are also limited to 26 MHz.

The VCORE can be supplied by the low-power regulator, the main regulator being switched off. The system is then in Low-power run mode.

Low-power run mode with the CPU running at up to 2 MHz. Peripherals with independent clock can be clocked by HSI16.

## 3.9.4 Low-power modes

The ultra-low-power STM32L476xx supports seven low-power modes to achieve the best compromise between low-power consumption, short startup time, available peripherals and available wakeup sources:

# 3.11 Clocks and startup

The clock controller (see *Figure 3*) distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

- Clock prescaler: to get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler

- **Safe clock switching:** clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management:** to reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- **System clock source:** four different clock sources can be used to drive the master clock SYSCLK:

- 4-48 MHz high-speed external crystal or ceramic resonator (HSE), that can supply a PLL. The HSE can also be configured in bypass mode for an external clock.

- 16 MHz high-speed internal RC oscillator (HSI16), trimmable by software, that can supply a PLL

- Multispeed internal RC oscillator (MSI), trimmable by software, able to generate 12 frequencies from 100 kHz to 48 MHz. When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be automatically trimmed by hardware to reach better than ±0.25% accuracy. In this mode the MSI can feed the USB device, saving the need of an external high-speed crystal (HSE). The MSI can supply a PLL.

- System PLL which can be fed by HSE, HSI16 or MSI, with a maximum frequency at 80 MHz.

- **Auxiliary clock source:** two ultralow-power clock sources that can be used to drive the LCD controller and the real-time clock:

- 32.768 kHz low-speed external crystal (LSE), supporting four drive capability modes. The LSE can also be configured in bypass mode for an external clock.

- 32 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock accuracy is ±5% accuracy.

- **Peripheral clock sources:** Several peripherals (USB, SDMMC, RNG, SAI, USARTs, I2Cs, LPTimers, ADC, SWPMI) have their own independent clock whatever the system clock. Three PLLs, each having three independent outputs allowing the highest flexibility, can generate independent clocks for the ADC, the USB/SDMMC/RNG and the two SAIs.

- **Startup clock:** after reset, the microcontroller restarts by default with an internal 4 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- **Clock security system (CSS):** this feature can be enabled by software. If a HSE clock failure occurs, the master clock is automatically switched to HSI16 and a software

Many features are shared with those of the general-purpose TIMx timers (described in *Section 3.24.2*) using the same architecture, so the advanced-control timers can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

# 3.24.2 General-purpose timers (TIM2, TIM3, TIM4, TIM5, TIM15, TIM16, TIM17)

There are up to seven synchronizable general-purpose timers embedded in the STM32L476 (see *Table 10* for differences). Each general-purpose timer can be used to generate PWM outputs, or act as a simple time base.

• TIM2, TIM3, TIM4 and TIM5

They are full-featured general-purpose timers:

- TIM2 and TIM5 have a 32-bit auto-reload up/downcounter and 32-bit prescaler

- TIM3 and TIM4 have 16-bit auto-reload up/downcounter and 16-bit prescaler.

These timers feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. They can work together, or with the other general-purpose timers via the Timer Link feature for synchronization or event chaining.

The counters can be frozen in debug mode.

All have independent DMA request generation and support quadrature encoders.

• TIM15, 16 and 17

They are general-purpose timers with mid-range features:

They have 16-bit auto-reload upcounters and 16-bit prescalers.

- TIM15 has 2 channels and 1 complementary channel

- TIM16 and TIM17 have 1 channel and 1 complementary channel

All channels can be used for input capture/output compare, PWM or one-pulse mode output.

The timers can work together via the Timer Link feature for synchronization or event chaining. The timers have independent DMA request generation.

The counters can be frozen in debug mode.

## 3.24.3 Basic timers (TIM6 and TIM7)

The basic timers are mainly used for DAC trigger generation. They can also be used as generic 16-bit timebases.

## 3.24.4 Low-power timer (LPTIM1 and LPTIM2)

The devices embed two low-power timers. These timers have an independent clock and are running in Stop mode if they are clocked by LSE, LSI or an external clock. They are able to wakeup the system from Stop mode.

LPTIM1 is active in Stop 0, Stop 1 and Stop 2 modes.

LPTIM2 is active in Stop 0 and Stop 1 mode.

| SAI features <sup>(1)</sup>                            | SAI1       | SAI2       |

|--------------------------------------------------------|------------|------------|

| I2S, LSB or MSB-justified, PCM/DSP, TDM, AC'97         | Х          | Х          |

| Mute mode                                              | Х          | Х          |

| Stereo/Mono audio frame capability.                    | Х          | Х          |

| 16 slots                                               | Х          | Х          |

| Data size configurable: 8-, 10-, 16-, 20-, 24-, 32-bit | Х          | Х          |

| FIFO Size                                              | X (8 Word) | X (8 Word) |

| SPDIF                                                  | Х          | Х          |

Table 13. SAI implementation

1. X: supported

# 3.31 Single wire protocol master interface (SWPMI)

The Single wire protocol master interface (SWPMI) is the master interface corresponding to the Contactless Frontend (CLF) defined in the ETSI TS 102 613 technical specification. The main features are:

- full-duplex communication mode

- automatic SWP bus state management (active, suspend, resume)

- configurable bitrate up to 2 Mbit/s

- automatic SOF, EOF and CRC handling

SWPMI can be served by the DMA controller.

# 3.32 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

The CAN peripheral supports:

- Supports CAN protocol version 2.0 A, B Active

- Bit rates up to 1 Mbit/s

|        |         | Pin N   | Numb    |          |         |                                       |          |               |       | Pin functions                                                                                                                                                                    |                                                       |

|--------|---------|---------|---------|----------|---------|---------------------------------------|----------|---------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| LQFP64 | WLCSP72 | WLCSP81 | LQFP100 | UFBGA132 | LQFP144 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                                                                              | Additional functions                                  |

| -      | -       | -       | 20      | -        | 31      | VREF-                                 | S        | -             | -     | -                                                                                                                                                                                | -                                                     |

| 12     | G9      | G9      | -       | J1       | -       | VSSA/VREF-                            | -        | -             | -     | -                                                                                                                                                                                | -                                                     |

| -      | G8      | G8      | 21      | L1       | 32      | VREF+                                 | S        | -             | -     | -                                                                                                                                                                                | VREFBUF_<br>OUT                                       |

| -      | H9      | H9      | 22      | M1       | 33      | VDDA                                  | S        | -             | -     | -                                                                                                                                                                                | -                                                     |

| 13     | -       | -       | -       | -        | -       | VDDA/VREF+                            | S        | -             | -     | -                                                                                                                                                                                | -                                                     |

| 14     | H8      | H8      | 23      | L2       | 34      | PA0                                   | I/O      | FT_a          | -     | TIM2_CH1, TIM5_CH1,<br>TIM8_ETR, USART2_CTS,<br>UART4_TX,<br>SAI1_EXTCLK,<br>TIM2_ETR, EVENTOUT                                                                                  | OPAMP1_<br>VINP,<br>ADC12_IN5,<br>RTC_TAMP<br>2/WKUP1 |

| -      | -       | -       | -       | М3       | -       | OPAMP1_VINM                           | I        | TT            | -     | -                                                                                                                                                                                | -                                                     |

| 15     | G4      | G4      | 24      | M2       | 35      | PA1                                   | I/O      | FT_la         | -     | TIM2_CH2, TIM5_CH2,<br>USART2_RTS_DE,<br>UART4_RX, LCD_SEG0,<br>TIM15_CH1N, EVENTOUT                                                                                             | OPAMP1_<br>VINM,<br>ADC12_IN6                         |

| 16     | G6      | G6      | 25      | К3       | 36      | PA2                                   | I/O      | FT_la         | -     | TIM2_CH3, TIM5_CH3,<br>USART2_TX, LCD_SEG1,<br>SAI2_EXTCLK,<br>TIM15_CH1, EVENTOUT                                                                                               | ADC12_IN7,<br>WKUP4/<br>LSCO                          |

| 17     | H7      | H7      | 26      | L3       | 37      | PA3                                   | I/O      | TT            | -     | TIM2_CH4, TIM5_CH4,<br>USART2_RX, LCD_SEG2,<br>TIM15_CH2, EVENTOUT                                                                                                               | OPAMP1_<br>VOUT,<br>ADC12_IN8                         |

| 18     | J9      | J9      | 27      | E3       | 38      | VSS                                   | S        | -             | -     | -                                                                                                                                                                                | -                                                     |

| 19     | J8      | J8      | 28      | H3       | 39      | VDD                                   | S        | -             | -     | -                                                                                                                                                                                | -                                                     |

| 20     | G5      | G5      | 29      | J4       | 40      | PA4                                   | I/O      | TT_a          | -     | SPI1_NSS, SPI3_NSS,<br>USART2_CK, SAI1_FS_B,<br>LPTIM2_OUT, EVENTOUT                                                                                                             | ADC12_<br>IN9, DAC1_<br>OUT1                          |

| 21     | H6      | H6      | 30      | K4       | 41      | PA5                                   | I/O      | TT_a          | -     | TIM2_CH1, TIM2_ETR,<br>TIM8_CH1N, SPI1_SCK,<br>LPTIM2_ETR, EVENTOUT                                                                                                              | ADC12_<br>IN10,<br>DAC1_<br>OUT2                      |

| 22     | H5      | H5      | 31      | L4       | 42      | PA6                                   | I/O      | FT_la         | -     | TIM1_BKIN, TIM3_CH1,<br>TIM8_BKIN, SPI1_MISO,<br>USART3_CTS,<br>QUADSPI_BK1_IO3,<br>LCD_SEG3,<br>TIM1_BKIN_COMP2,<br>TIM8_BKIN_COMP2,<br>TIM8_BKIN_COMP2,<br>TIM16_CH1, EVENTOUT | OPAMP2_<br>VINP,<br>ADC12_<br>IN11                    |

| Table 15. STM32L476xxSTM32L476xx pin definitions | (continued) |

|--------------------------------------------------|-------------|

|                                                  | (001111100) |

|        |         | Pin N   | Numb    | er       |         |                                       |          |               |       | Pin functions                                                                                                      |                      |

|--------|---------|---------|---------|----------|---------|---------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------------------------------------------|----------------------|

| LQFP64 | WLCSP72 | WLCSP81 | LQFP100 | UFBGA132 | LQFP144 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                | Additional functions |

| -      | -       | -       | 82      | В9       | 115     | PD1                                   | I/O      | FT            | -     | SPI2_SCK,<br>DFSDM_CKIN7,<br>CAN1_TX, FMC_D3,<br>EVENTOUT                                                          | -                    |

| 54     | A3      | A3      | 83      | C8       | 116     | PD2                                   | I/O      | FT_I          | -     | TIM3_ETR,<br>USART3_RTS_DE,<br>UART5_RX, TSC_SYNC,<br>LCD_COM7/LCD_SEG31/<br>LCD_SEG43,<br>SDMMC1_CMD,<br>EVENTOUT | -                    |

| -      | -       | -       | 84      | B8       | 117     | PD3                                   | I/O      | FT            | -     | SPI2_MISO,<br>DFSDM_DATIN0,<br>USART2_CTS, FMC_CLK,<br>EVENTOUT                                                    | -                    |

| -      | -       | E5      | 85      | В7       | 118     | PD4                                   | I/O      | FT            | -     | SPI2_MOSI,<br>DFSDM_CKIN0,<br>USART2_RTS_DE,<br>FMC_NOE, EVENTOUT                                                  | -                    |

| -      | -       | D4      | 86      | A6       | 119     | PD5                                   | I/O      | FT            | -     | USART2_TX, FMC_NWE,<br>EVENTOUT                                                                                    | -                    |

| -      | -       | -       | -       | -        | 120     | VSS                                   | S        | -             | -     | -                                                                                                                  | -                    |

| -      | -       | E4      | -       | -        | 121     | VDD                                   | S        | -             | -     | -                                                                                                                  | -                    |

| -      | -       | D5      | 87      | B6       | 122     | PD6                                   | I/O      | FT            | -     | DFSDM_DATIN1,<br>USART2_RX,<br>FMC_NWAIT, SAI1_SD_A,<br>EVENTOUT                                                   | -                    |

| -      | -       | D6      | 88      | A5       | 123     | PD7                                   | I/O      | FT            | -     | DFSDM_CKIN1,<br>USART2_CK, FMC_NE1,<br>EVENTOUT                                                                    | -                    |

| -      | A4      | A4      | -       | D9       | 124     | PG9                                   | I/O      | FT_s          | -     | SPI3_SCK, USART1_TX,<br>FMC_NCE3/FMC_NE2,<br>SAI2_SCK_A,<br>TIM15_CH1N, EVENTOUT                                   | -                    |

| -      | B4      | B4      | -       | D8       | 125     | PG10                                  | I/O      | FT_s          | -     | LPTIM1_IN1, SPI3_MISO,<br>USART1_RX, FMC_NE3,<br>SAI2_FS_A, TIM15_CH1,<br>EVENTOUT                                 | -                    |

| -      | C4      | C4      | -       | G3       | 126     | PG11                                  | I/O      | FT_s          | -     | LPTIM1_IN2, SPI3_MOSI,<br>USART1_CTS,<br>SAI2_MCLK_A,<br>TIM15_CH2, EVENTOUT                                       | -                    |

| Table 15. STM32L476xxSTM32L476xx pin definitions (continued) |

|--------------------------------------------------------------|

|--------------------------------------------------------------|

|        |      | AF0     | AF1                                | AF2                              | AF3                  | AF4            | AF5       | AF6          | AF7                          |

|--------|------|---------|------------------------------------|----------------------------------|----------------------|----------------|-----------|--------------|------------------------------|

| P      | ort  | SYS_AF  | TIM1/TIM2/<br>TIM5/TIM8/<br>LPTIM1 | TIM1/TIM2/<br>TIM3/TIM4/<br>TIM5 | TIM8                 | 12C1/12C2/12C3 | SPI1/SPI2 | SPI3/DFSDM   | USART1/<br>USART2/<br>USART3 |

|        | PE0  | -       | -                                  | TIM4_ETR                         | -                    | -              | -         | -            | -                            |

|        | PE1  | -       | -                                  | -                                | -                    | -              | -         | -            | -                            |

|        | PE2  | TRACECK | -                                  | TIM3_ETR                         | -                    | -              | -         | -            | -                            |

|        | PE3  | TRACED0 | -                                  | TIM3_CH1                         | -                    | -              | -         | -            | -                            |

|        | PE4  | TRACED1 | -                                  | TIM3_CH2                         | -                    | -              | -         | DFSDM_DATIN3 | -                            |

|        | PE5  | TRACED2 | -                                  | TIM3_CH3                         | -                    | -              | -         | DFSDM_CKIN3  | -                            |

|        | PE6  | TRACED3 | -                                  | TIM3_CH4                         | -                    | -              | -         | -            | -                            |

|        | PE7  | -       | TIM1_ETR                           | -                                | -                    | -              | -         | DFSDM_DATIN2 | -                            |

| Port E | PE8  | -       | TIM1_CH1N                          | -                                | -                    | -              | -         | DFSDM_CKIN2  | -                            |

|        | PE9  | -       | TIM1_CH1                           | -                                | -                    | -              | -         | DFSDM_CKOUT  | -                            |

|        | PE10 | -       | TIM1_CH2N                          | -                                | -                    | -              | -         | DFSDM_DATIN4 | -                            |

|        | PE11 | -       | TIM1_CH2                           | -                                | -                    | -              | -         | DFSDM_CKIN4  | -                            |

|        | PE12 | -       | TIM1_CH3N                          | -                                | -                    | -              | SPI1_NSS  | DFSDM_DATIN5 | -                            |

|        | PE13 | -       | TIM1_CH3                           | -                                | -                    | -              | SPI1_SCK  | DFSDM_CKIN5  | -                            |

|        | PE14 | -       | TIM1_CH4                           | TIM1_BKIN2                       | TIM1_BKIN2_<br>COMP2 | -              | SPI1_MISO | -            | -                            |

|        | PE15 | -       | TIM1_BKIN                          | -                                | TIM1_BKIN_<br>COMP1  | -              | SPI1_MOSI | -            | -                            |

DocID025976 Rev 4

571

77/232

STM32L476xx

Pinouts and pin description

#### 5

# Memory mapping

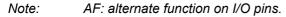

#### Figure 10. STM32L476 memory map

DocID025976 Rev 4

## 6.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 53*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                    | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD} = 3.3 \text{ V}, T_A = +25 \text{ °C},$<br>f <sub>HCLK</sub> = 80 MHz,<br>conforming to IEC 61000-4-2 | 3B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3 \text{ V}, T_A = +25 \text{ °C},$<br>f <sub>HCLK</sub> = 80 MHz,<br>conforming to IEC 61000-4-4 | 4A              |

#### Table 53. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

| Symbol           | Parameter                                                                    | Conditions                                                                                                                | Min | Тур | Max                    | Unit |

|------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------|------|

|                  |                                                                              | $V_{IN} \le Max(V_{DDXXX})^{(4)}$                                                                                         | -   | -   | ±100                   |      |

|                  | FT_xx input leakage current <sup>(3)</sup>                                   | $\begin{array}{l} Max(V_{DDXXX}) \leq V_{IN} \leq \\ Max(V_{DDXXX}) + 1 \ V^{(4)(5)} \end{array}$                         | -   | -   | 650 <sup>(3)(6)</sup>  |      |

|                  |                                                                              | $\begin{array}{l} {\sf Max}({\sf V}_{{\sf DDXXX}})\text{+}1~{\sf V} < \\ {\sf VIN} \leq 5.5~{\sf V}^{(3)(5)} \end{array}$ | -   | -   | 200 <sup>(6)</sup>     |      |

|                  |                                                                              | $V_{IN} \le Max(V_{DDXXX})^{(4)}$                                                                                         | -   | -   | ±150                   |      |

|                  | FT_lu, FT_u and<br>PC3 IO                                                    | $\begin{array}{l} Max(V_{DDXXX}) \leq V_{IN} \leq \\ Max(V_{DDXXX}) + 1 \ V^{(4)} \end{array}$                            | -   | -   | 2500 <sup>(3)(7)</sup> |      |

| l <sub>lkg</sub> |                                                                              | $Max(V_{DDXXX})+1 V < VIN \le 5.5 V^{(4)(5)(7)}$                                                                          | -   | -   | 250 <sup>(7)</sup>     | - nA |

|                  | TT_xx input leakage current                                                  | $V_{IN} \le Max(V_{DDXXX})^{(6)}$                                                                                         | -   | -   | ±150                   |      |

|                  |                                                                              | Max(V <sub>DDXXX</sub> ) ≤ V <sub>IN</sub> < 3.6 V <sup>(6)</sup>                                                         | -   | -   | 2000 <sup>(3)</sup>    |      |

|                  | OPAMPx_VINM<br>(x=1,2) dedicated<br>input leakage current<br>(UFBGA132 only) | T <sub>J</sub> = 75 °C                                                                                                    | -   | -   | 1                      |      |

| R <sub>PU</sub>  | Weak pull-up<br>equivalent resistor <sup>(8)</sup>                           | V <sub>IN</sub> = V <sub>SS</sub>                                                                                         | 25  | 40  | 55                     | kΩ   |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(8)</sup>                            | V <sub>IN</sub> = V <sub>DDIOx</sub>                                                                                      | 25  | 40  | 55                     | kΩ   |

| CIO              | I/O pin capacitance                                                          | -                                                                                                                         | -   | 5   | -                      | pF   |

| Table 58. I/O static characteristics (co | ontinued) |

|------------------------------------------|-----------|

|------------------------------------------|-----------|

1. Refer to Figure 22: I/O input characteristics.

- 2. Tested in production.

- 3. Guaranteed by design.

- 4. Max(V<sub>DDXXX</sub>) is the maximum value of all the I/O supplies. Refer to Table: Legend/Abbreviations used in the pinout table.

- 5. All TX\_xx IO except FT\_lu, FT\_u and PC3.

- 6. This value represents the pad leakage of the IO itself. The total product pad leakage is provided by this formula:  $I_{Total\_Ileak\_max} = 10 \ \mu A + [number of IOs where V_{IN} is applied on the pad] \times I_{Ikg}(Max)$ .

- 7. To sustain a voltage higher than MIN( $V_{DD}$ ,  $V_{DDA}$ ,  $V_{DDIO2}$ ,  $V_{DDUSB}$ ,  $V_{LCD}$ ) +0.3 V, the internal Pull-up and Pull-Down resistors must be disabled.

- Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

- 1. Guaranteed by design, unless otherwise specified.

- 2. Refer to *Table 25: Embedded internal voltage reference*.

- 3. Guaranteed by characterization results.

# 6.3.21 Operational amplifiers characteristics

| Symbol                                | Parameter                                                                                  | Con                       | ditions                  | Min | Тур | Max              | Unit  |  |

|---------------------------------------|--------------------------------------------------------------------------------------------|---------------------------|--------------------------|-----|-----|------------------|-------|--|

| V <sub>DDA</sub>                      | Analog supply voltage <sup>(2)</sup>                                                       |                           | -                        | 1.8 | -   | 3.6              | V     |  |

| CMIR                                  | Common mode input range                                                                    |                           | -                        | 0   | -   | V <sub>DDA</sub> | V     |  |

| VI <sub>OFFSET</sub>                  | Input offset                                                                               | 25 °C, No Load on output. |                          | -   | -   | ±1.5             | mV    |  |

| VIOFFSET                              | voltage                                                                                    | All voltage/Temp.         |                          | -   | -   | ±3               | mv    |  |

| ∆VI <sub>OFFSET</sub>                 | Input offset                                                                               | Normal mode               |                          | -   | ±5  | -                | µV/°C |  |

| OFFSET                                | voltage drift                                                                              | Low-power mode            |                          | -   | ±10 | -                | μν/Ο  |  |

| TRIMOFFSETP<br>TRIMLPOFFSETP          | Offset trim step<br>at low common<br>input voltage<br>(0.1 <sub>x</sub> V <sub>DDA</sub> ) |                           | -                        | -   | 0.8 | 1.1              | mV    |  |

| TRIMOFFSETN<br>TRIMLPOFFSETN          | Offset trim step<br>at high common<br>input voltage<br>(0.9 x V <sub>DDA</sub> )           |                           | -                        | -   | 1   | 1.35             |       |  |

|                                       | Drive current                                                                              | Normal mode               | V <sub>DDA</sub> ≥2V     | -   | -   | 500              | μΑ    |  |

| I <sub>LOAD</sub>                     | Drive current                                                                              | Low-power mode            | VDDA = 2 V               | -   | -   | 100              |       |  |

|                                       | Drive current in                                                                           | Normal mode               | V <sub>DDA</sub> ≥2V     | -   | -   | 450              |       |  |

| I <sub>LOAD_PGA</sub>                 | PGA mode                                                                                   | Low-power mode            | VDDA = 2 V               | -   | -   | 50               |       |  |

| P                                     | Resistive load<br>(connected to                                                            | Normal mode               | - V <sub>DDA</sub> < 2 V | 4   | -   | -                |       |  |

| R <sub>LOAD</sub> VSSA or to<br>VDDA) |                                                                                            | Low-power mode            | VDDA > 2 V               | 20  | -   | -                | kΩ    |  |

| in<br>R <sub>LOAD_PGA</sub> (c<br>V   | (connected to                                                                              | Normal mode               |                          | 4.5 | -   | -                | K12   |  |

|                                       |                                                                                            | Low-power mode            |                          | 40  | -   | -                |       |  |

| C <sub>LOAD</sub>                     | Capacitive load                                                                            |                           | -                        | -   | -   | 50               | pF    |  |

| CMRR                                  | Common mode                                                                                | Normal mode               |                          | -   | -85 | -                | dB    |  |

| CIVILAT                               | rejection ratio                                                                            | Low-power mode            |                          | -   | -90 | -                | UD    |  |

## Table 73. OPAMP characteristics<sup>(1)</sup>

| Symbol                            | Parameter                                                                                    |                                                    | cteristics <sup>(1)</sup> (continu                                                              | Min                       | Тур  | Max  | Unit  |

|-----------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------|------|------|-------|

|                                   | Power supply                                                                                 | Normal mode                                        | C <sub>LOAD</sub> ≤ 50 pf,<br>R <sub>LOAD</sub> ≥ 4 kΩ DC                                       | 70                        | 85   | _    | 10    |

| PSRR                              | PSRR rejection ratio Low-power mode $C_{LOAD} \le 50$ pf,<br>$R_{LOAD} \ge 20$ k $\Omega$ DC |                                                    | 72                                                                                              | 90                        | -    | dB   |       |

|                                   |                                                                                              | Normal mode                                        | V <sub>DDA</sub> ≥ 2.4 V                                                                        | 550                       | 1600 | 2200 | kHz   |

|                                   | Gain Bandwidth                                                                               | Low-power mode                                     | (OPA_RANGE = 1)                                                                                 | 100                       | 420  | 600  |       |

| GBW                               | Product                                                                                      | Normal mode                                        | V <sub>DDA</sub> < 2.4 V                                                                        | 250                       | 700  | 950  |       |

|                                   |                                                                                              | Low-power mode                                     | (OPA_RANGE = 0)                                                                                 | 40                        | 180  | 280  |       |

|                                   |                                                                                              | Normal mode                                        |                                                                                                 | -                         | 700  | -    |       |

| <b>22</b> <sup>(3)</sup>          | Slew rate<br>(from 10 and                                                                    | Low-power mode                                     | V <sub>DDA</sub> ≥ 2.4 V                                                                        | -                         | 180  | -    | N/Las |

| SR <sup>(3)</sup>                 | 90% of output                                                                                | Normal mode                                        |                                                                                                 | -                         | 300  | -    | V/ms  |

|                                   | voltage)                                                                                     | Low-power mode                                     | V <sub>DDA</sub> < 2.4 V                                                                        | -                         | 80   | -    |       |

| 10                                |                                                                                              | Normal mode                                        |                                                                                                 | 55                        | 110  | -    | dB    |

| AO                                | Open loop gain                                                                               | Low-power mode                                     |                                                                                                 | 45                        | 110  | -    |       |

| V <sub>OHSAT</sub> <sup>(3)</sup> | High saturation voltage                                                                      | Normal mode                                        | I <sub>load</sub> = max or R <sub>load</sub> =                                                  | V <sub>DDA</sub> -<br>100 | -    | -    |       |

|                                   |                                                                                              |                                                    | V <sub>DDA</sub> -<br>50                                                                        | -                         | -    | mV   |       |

| V (3)                             | Low saturation                                                                               | Normal mode                                        | I <sub>load</sub> = max or R <sub>load</sub> =                                                  | -                         | -    | 100  |       |

| V <sub>OLSAT</sub> <sup>(3)</sup> | voltage                                                                                      | Low-power mode                                     | min Input at 0.                                                                                 | -                         | -    | 50   |       |

|                                   | Dhace mersin                                                                                 | Normal mode                                        |                                                                                                 | -                         | 74   | -    | 0     |

| Φm                                | Phase margin                                                                                 | Low-power mode                                     |                                                                                                 | -                         | 66   | -    |       |

| 014                               |                                                                                              | Normal mode                                        |                                                                                                 | -                         | 13   | -    |       |

| GM                                | Gain margin                                                                                  | Low-power mode                                     |                                                                                                 | -                         | 20   | -    | dB    |

|                                   | ↓ Wake up time                                                                               |                                                    | $C_{LOAD} \le 50 \text{ pf},$<br>$R_{LOAD} \ge 4 \text{ k}\Omega$<br>follower<br>configuration  | -                         | 5    | 10   |       |

| <sup>t</sup> WAKEUP from          | from OFF state.                                                                              |                                                    | $C_{LOAD} \le 50 \text{ pf},$<br>$R_{LOAD} \ge 20 \text{ k}\Omega$<br>follower<br>configuration | -                         | 10   | 30   | μs    |

|                                   |                                                                                              | Dedicated input (BGA132 only)                      |                                                                                                 | -                         | -    | _(4) |       |

| I <sub>bias</sub>                 | OPAMP input<br>bias current                                                                  | General purpose input (all packages except BGA132) |                                                                                                 | -                         | -    | _(4) | nA    |

|                                   |                                                                                              | -                                                  |                                                                                                 | -                         | 2    | -    |       |

| PCA coin <sup>(3)</sup>           | Non inverting                                                                                |                                                    |                                                                                                 | -                         | 4    | -    |       |

| PGA gain <sup>(3)</sup>           | gain value                                                                                   |                                                    |                                                                                                 | -                         | 8    | -    |       |

|                                   |                                                                                              |                                                    |                                                                                                 |                           |      |      |       |

| Table 73. OPAMP characteristics | (1) | (continued) |

|---------------------------------|-----|-------------|

|---------------------------------|-----|-------------|

## **USB** characteristics

The STM32L476xx USB interface is fully compliant with the USB specification version 2.0 and is USB-IF certified (for Full-speed device operation).

| Symbol                          | Parameter                                      | Conditions              | Min                | Тур  | Мах  | Unit |

|---------------------------------|------------------------------------------------|-------------------------|--------------------|------|------|------|

| V <sub>DDUSB</sub>              | USB transceiver operating voltage              |                         | 3.0 <sup>(1)</sup> | -    | 3.6  | V    |

| R <sub>PUI</sub>                | Embedded USB_DP pull-up value during idle      |                         | 900                | 1250 | 1600 |      |

| R <sub>PUR</sub>                | Embedded USB_DP pull-up value during reception |                         | 1400               | 2300 | 3200 | Ω    |

| Z <sub>DRV</sub> <sup>(2)</sup> | Output driver impedance <sup>(3)</sup>         | Driving high<br>and low | 28                 | 36   | 44   | Ω    |

| Table 89. US | SB electrical | characteristics |

|--------------|---------------|-----------------|

|--------------|---------------|-----------------|

1. The STM32L476xx USB functionality is ensured down to 2.7 V but not the full USB electrical characteristics which are degraded in the 2.7-to-3.0 V voltage range.

2. Guaranteed by design.

3. No external termination series resistors are required on USB\_DP (D+) and USB\_DM (D-); the matching impedance is already included in the embedded driver.

## CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

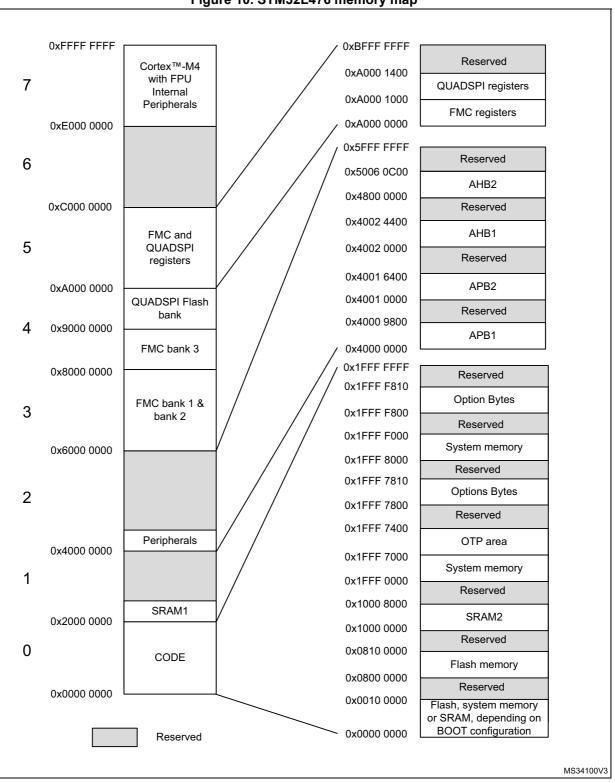

## 6.3.28 FSMC characteristics

Unless otherwise specified, the parameters given in *Table 90* to *Table 103* for the FMC interface are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 22*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output

characteristics.

#### Asynchronous waveforms and timings

*Figure 37* through *Figure 40* represent asynchronous waveforms and *Table 90* through *Table 97* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- AddressSetupTime = 0x1

- AddressHoldTime = 0x1

- DataSetupTime = 0x1 (except for asynchronous NWAIT mode, DataSetupTime = 0x5)

- BusTurnAroundDuration = 0x0

In all timing tables, the THCLK is the HCLK clock period.

| Symbol                    | Parameter                             | Min                     | Мах                     | Unit |

|---------------------------|---------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                       | 2T <sub>HCLK</sub> -0.5 | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>v(NOE_NE)</sub>    | FMC_NEx low to FMC_NOE low            | 0                       | 1                       |      |

| t <sub>w(NOE)</sub>       | FMC_NOE low time                      | 2T <sub>HCLK</sub> -0.5 | 2T <sub>HCLK</sub> +1   |      |

| t <sub>h(NE_NOE)</sub>    | FMC_NOE high to FMC_NE high hold time | 0                       | -                       |      |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid            | -                       | 3.5                     |      |

| t <sub>h(A_NOE)</sub>     | Address hold time after FMC_NOE high  | 0                       | -                       |      |

| t <sub>v(BL_NE)</sub>     | FMC_NEx low to FMC_BL valid           | -                       | 2                       | ns   |

| t <sub>h(BL_NOE)</sub>    | FMC_BL hold time after FMC_NOE high   | 0                       | -                       | 115  |

| t <sub>su(Data_NE)</sub>  | Data to FMC_NEx high setup time       | T <sub>HCLK</sub> -1    | -                       |      |

| t <sub>su(Data_NOE)</sub> | Data to FMC_NOEx high setup time      | T <sub>HCLK</sub> -0.5  | -                       |      |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FMC_NOE high     | 0                       | -                       |      |

| t <sub>h(Data_NE)</sub>   | Data hold time after FMC_NEx high     | 0                       | -                       |      |

| t <sub>v(NADV_NE)</sub>   | FMC_NEx low to FMC_NADV low           | -                       | 1                       |      |

| t <sub>w(NADV)</sub>      | FMC_NADV low time                     | _                       | T <sub>HCLK</sub> +0.5  |      |

Table 90. Asynchronous non-multiplexed SRAM/PSRAM/NOR read timings<sup>(1)(2)</sup>

1. CL = 30 pF.

2. Guaranteed by characterization results.

| Table 91. Asynchronous non-multiplexed SRAM/PSRAM/NOR read-NWAIT |

|------------------------------------------------------------------|

| timings <sup>(1)(2)</sup>                                        |

| Symbol                    | Parameter                                 | Min                     | Мах                     | Unit |

|---------------------------|-------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 7T <sub>HCLK</sub> -0.5 | 7T <sub>HCLK</sub> +0.5 |      |

| t <sub>w(NOE)</sub>       | FMC_NWE low time                          | 5T <sub>HCLK</sub> -0.5 | 5T <sub>HCLK</sub> +0.5 |      |

| t <sub>w(NWAIT)</sub>     | FMC_NWAIT low time                        | T <sub>HCLK</sub> -0.5  | -                       | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 5T <sub>HCLK</sub> +2   | -                       |      |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub>      | -                       |      |

1. CL = 30 pF.

2. Guaranteed by characterization results.

- 1. CL = 30 pF.

- 2. Guaranteed by characterization results.

## Figure 44. Synchronous non-multiplexed PSRAM write timings

As applications do not commonly use the STM32L476xx at maximum dissipation, it is useful to calculate the exact power consumption and junction temperature to determine which temperature range will be best suited to the application.

The following examples show how to calculate the temperature range needed for a given application.

#### **Example 1: High-performance application**

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax}$  = 82 °C (measured according to JESD51-2), I<sub>DDmax</sub> = 50 mA, V<sub>DD</sub> = 3.5 V, maximum 20 I/Os used at the same time in output at low level with I<sub>OL</sub> = 8 mA, V<sub>OL</sub>= 0.4 V and maximum 8 I/Os used at the same time in output at low level with I<sub>OL</sub> = 20 mA, V<sub>OL</sub>= 1.3 V

P<sub>INTmax</sub> = 50 mA × 3.5 V= 175 mW

P<sub>IOmax</sub> = 20 × 8 mA × 0.4 V + 8 × 20 mA × 1.3 V = 272 mW

This gives:  $P_{INTmax}$  = 175 mW and  $P_{IOmax}$  = 272 mW:

P<sub>Dmax</sub> = 175 + 272 = 447 mW

Using the values obtained in Table 113  $T_{Jmax}$  is calculated as follows:

– For LQFP64, 45 °C/W

This is within the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ) see Section 8: Part numbering.

In this case, parts must be ordered at least with the temperature range suffix 6 (see Part numbering).

Note: With this given  $P_{Dmax}$  we can find the  $T_{Amax}$  allowed for a given device temperature range (order code suffix 6 or 7).

Suffix 6:  $T_{Amax} = T_{Jmax} - (45^{\circ}C/W \times 447 \text{ mW}) = 105\text{-}20.115 = 84.885 ^{\circ}C$ Suffix 7:  $T_{Amax} = T_{Jmax} - (45^{\circ}C/W \times 447 \text{ mW}) = 125\text{-}20.115 = 104.885 ^{\circ}C$

#### **Example 2: High-temperature application**

Using the same rules, it is possible to address applications that run at high ambient temperatures with a low dissipation, as long as junction temperature  $T_J$  remains within the specified range.

Assuming the following application conditions:

Maximum ambient temperature  $T_{Amax} = 100 \text{ °C}$  (measured according to JESD51-2),  $I_{DDmax} = 20 \text{ mA}, V_{DD} = 3.5 \text{ V}$ , maximum 20 I/Os used at the same time in output at low level with  $I_{OL} = 8 \text{ mA}, V_{OL} = 0.4 \text{ V}$   $P_{INTmax} = 20 \text{ mA} \times 3.5 \text{ V} = 70 \text{ mW}$   $P_{IOmax} = 20 \times 8 \text{ mA} \times 0.4 \text{ V} = 64 \text{ mW}$ This gives:  $P_{INTmax} = 70 \text{ mW}$  and  $P_{IOmax} = 64 \text{ mW}$ :  $P_{Dmax} = 70 + 64 = 134 \text{ mW}$

Thus: P<sub>Dmax</sub> = 134 mW