#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                              |

|----------------------------|-----------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                                  |

| Speed                      | 80MHz                                                                                               |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                                          |

| Number of I/O              | 114                                                                                                 |

| Program Memory Size        | 512KB (512K x 8)                                                                                    |

| Program Memory Type        | FLASH                                                                                               |

| EEPROM Size                | -                                                                                                   |

| RAM Size                   | 128K x 8                                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                                        |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                               |

| Oscillator Type            | Internal                                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                   |

| Mounting Type              | Surface Mount                                                                                       |

| Package / Case             | 144-LQFP                                                                                            |

| Supplier Device Package    | 144-LQFP (20x20)                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l476zet6tr                             |

|                            |                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 49.<br>Figure 50. | LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline<br>LQFP144 - 144-pin,20 x 20 mm low-profile quad flat package | 208 |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| rigure ee.               | recommended footprint.                                                                                                            | 210 |

| Figure 51.<br>Figure 52. | LQFP144 marking (package top view)                                                                                                |     |

| riguro oz.               | package outline.                                                                                                                  | 212 |

| Figure 53.               | UFBGA132 - 132-ball, 7 x 7 mm ultra thin fine pitch ball grid array                                                               |     |

| package rec              | commended footprint213                                                                                                            |     |

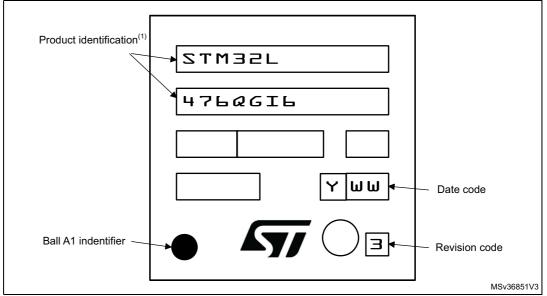

| Figure 54.               | UFBGA132 marking (package top view)                                                                                               | 214 |

| Figure 55.               | LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline                                                               | 215 |

| Figure 56.               | LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat                                                                               |     |

|                          | recommended footprint                                                                                                             | 216 |

| Figure 57.               | LQFP100 marking (package top view)                                                                                                | 217 |

| Figure 58.               | WLCSP81 - 81-ball, 4.4084 x 3.7594 mm, 0.4 mm pitch wafer level                                                                   |     |

| -                        | chip scale package outline                                                                                                        | 218 |

| Figure 59.               | WLCSP81- 81-ball, 4.4084 x 3.7594 mm, 0.4 mm pitch wafer level chip scale                                                         |     |

| -                        | package recommended footprint                                                                                                     | 219 |

| Figure 60.               | WLCSP81 marking (package top view)                                                                                                |     |

| Figure 61.               | WLCSP72 - 72-ball, 4.4084 x 3.7594 mm, 0.4 mm pitch wafer level chip                                                              |     |

| U                        | scale package outline                                                                                                             | 220 |

| Figure 62.               | WLCSP72 - 72-ball, 4.4084 x 3.7594 mm, 0.4 mm pitch wafer level                                                                   |     |

| 0                        | chip scale package recommended footprint                                                                                          | 221 |

| Figure 63.               | WLCSP72 marking (package top view)                                                                                                |     |

| Figure 64.               | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline                                                                 |     |

| Figure 65.               | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package                                                                         |     |

| 0                        | recommended footprint                                                                                                             | 224 |

| Figure 66.               | LQFP64 marking (package top view)                                                                                                 |     |

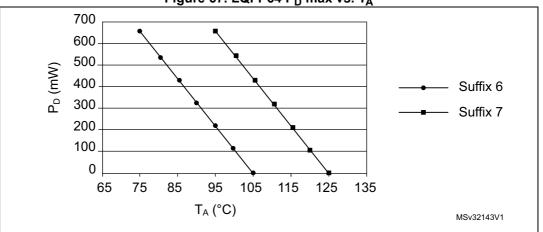

| Figure 67.               | LQFP64 $P_D$ max vs. $T_A$                                                                                                        |     |

### 3.12 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. Fast I/O toggling can be achieved thanks to their mapping on the AHB2 bus.

The I/Os alternate function configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

### 3.13 Direct memory access controller (DMA)

The device embeds 2 DMAs. Refer to *Table 7: DMA implementation* for the features implementation.

Direct memory access (DMA) is used in order to provide high-speed data transfer between peripherals and memory as well as memory to memory. Data can be quickly moved by DMA without any CPU actions. This keeps CPU resources free for other operations.

The two DMA controllers have 14 channels in total, each dedicated to managing memory access requests from one or more peripherals. Each has an arbiter for handling the priority between DMA requests.

The DMA supports:

- 14 independently configurable channels (requests)

- Each channel is connected to dedicated hardware DMA requests, software trigger is also supported on each channel. This configuration is done by software.

- Priorities between requests from channels of one DMA are software programmable (4 levels consisting of very high, high, medium, low) or hardware in case of equality (request 1 has priority over request 2, etc.)

- Independent source and destination transfer size (byte, half word, word), emulating packing and unpacking. Source/destination addresses must be aligned on the data size.

- Support for circular buffer management

- 3 event flags (DMA Half Transfer, DMA Transfer complete and DMA Transfer Error) logically ORed together in a single interrupt request for each channel

- Memory-to-memory transfer

- Peripheral-to-memory and memory-to-peripheral, and peripheral-to-peripheral transfers

- Access to Flash, SRAM, APB and AHB peripherals as source and destination

- Programmable number of data to be transferred: up to 65536.

#### Table 7. DMA implementation

| DMA features               | DMA1 | DMA2 |

|----------------------------|------|------|

| Number of regular channels | 7    | 7    |

## 3.14 Interrupts and events

### 3.14.1 Nested vectored interrupt controller (NVIC)

The devices embed a nested vectored interrupt controller able to manage 16 priority levels, and handle up to 81 maskable interrupt channels plus the 16 interrupt lines of the  $Cortex^{\mathbb{B}}$ -M4.

The NVIC benefits are the following:

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

The NVIC hardware block provides flexible interrupt management features with minimal interrupt latency.

### 3.14.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 36 edge detector lines used to generate interrupt/event requests and wake-up the system from Stop mode. Each external line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently A pending register maintains the status of the interrupt requests. The internal lines are connected to peripherals with wakeup from Stop mode capability. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 114 GPIOs can be connected to the 16 external interrupt lines.

- Noise-wave generation

- Triangular-wave generation

- Dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- External triggers for conversion

- Sample and hold low-power mode, with internal or external capacitor

The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

### 3.17 Voltage reference buffer (VREFBUF)

The STM32L476xx devices embed an voltage reference buffer which can be used as voltage reference for ADCs, DACs and also as voltage reference for external components through the VREF+ pin.

The internal voltage reference buffer supports two voltages:

- 2.048 V

- 2.5 V.

An external voltage reference can be provided through the VREF+ pin when the internal voltage reference buffer is off.

The VREF+ pin is double-bonded with VDDA on some packages. In these packages the internal voltage reference buffer is not available.

## 3.18 Comparators (COMP)

The STM32L476xx devices embed two rail-to-rail comparators with programmable reference voltage (internal or external), hysteresis and speed (low speed for low-power) and with selectable output polarity.

The reference voltage can be one of the following:

- External I/O

- DAC output channels

- Internal reference voltage or submultiple (1/4, 1/2, 3/4).

All comparators can wake up from Stop mode, generate interrupts and breaks for the timers and can be also combined into a window comparator.

This low-power timer supports the following features:

- 16-bit up counter with 16-bit autoreload register

- 16-bit compare register

- Configurable output: pulse, PWM

- Continuous/ one shot mode

- Selectable software/hardware input trigger

- Selectable clock source

- Internal clock sources: LSE, LSI, HSI16 or APB clock

- External clock source over LPTIM input (working even with no internal clock source running, used by pulse counter application).

- Programmable digital glitch filter

- Encoder mode (LPTIM1 only)

#### 3.24.5 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC (LSI) and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

### 3.24.6 System window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### 3.24.7 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- A 24-bit down counter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0.

- Programmable clock source

### 3.26 Inter-integrated circuit interface (I2C)

The device embeds 3 I2C. Refer to *Table 11: I2C implementation* for the features implementation.

The I<sup>2</sup>C bus interface handles communications between the microcontroller and the serial I<sup>2</sup>C bus. It controls all I<sup>2</sup>C bus-specific sequencing, protocol, arbitration and timing.

The I2C peripheral supports:

- I<sup>2</sup>C-bus specification and user manual rev. 5 compatibility:

- Slave and master modes, multimaster capability

- Standard-mode (Sm), with a bitrate up to 100 kbit/s

- Fast-mode (Fm), with a bitrate up to 400 kbit/s

- Fast-mode Plus (Fm+), with a bitrate up to 1 Mbit/s and 20 mA output drive I/Os

- 7-bit and 10-bit addressing mode, multiple 7-bit slave addresses

- Programmable setup and hold times

- Optional clock stretching

- System Management Bus (SMBus) specification rev 2.0 compatibility:

- Hardware PEC (Packet Error Checking) generation and verification with ACK control

- Address resolution protocol (ARP) support

- SMBus alert

- Power System Management Protocol (PMBus<sup>TM</sup>) specification rev 1.1 compatibility

- Independent clock: a choice of independent clock sources allowing the I2C communication speed to be independent from the PCLK reprogramming. Refer to Figure 3: Clock tree.

- Wakeup from Stop mode on address match

- Programmable analog and digital noise filters

- 1-byte buffer with DMA capability

#### Table 11. I2C implementation

| I2C features <sup>(1)</sup>                                 | I2C1 | I2C2 | I2C3 |

|-------------------------------------------------------------|------|------|------|

| Standard-mode (up to 100 kbit/s)                            | Х    | Х    | Х    |

| Fast-mode (up to 400 kbit/s)                                | Х    | Х    | Х    |

| Fast-mode Plus with 20mA output drive I/Os (up to 1 Mbit/s) | Х    | Х    | Х    |

| Programmable analog and digital noise filters               | Х    | Х    | Х    |

| SMBus/PMBus hardware support                                | Х    | Х    | Х    |

| Independent clock                                           | Х    | Х    | Х    |

| Wakeup from Stop 0 / Stop 1 mode on address match           | Х    | Х    | Х    |

| Wakeup from Stop 2 mode on address match                    | -    | -    | Х    |

1. X: supported

# 3.36 Quad SPI memory interface (QUADSPI)

The Quad SPI is a specialized communication interface targeting single, dual or quad SPI flash memories. It can operate in any of the three following modes:

- Indirect mode: all the operations are performed using the QUADSPI registers

- Status polling mode: the external flash status register is periodically read and an interrupt can be generated in case of flag setting

- Memory-mapped mode: the external flash is memory mapped and is seen by the system as if it were an internal memory

The Quad SPI interface supports:

- Three functional modes: indirect, status-polling, and memory-mapped

- SDR and DDR support

- Fully programmable opcode for both indirect and memory mapped mode

- Fully programmable frame format for both indirect and memory mapped mode

- Each of the 5 following phases can be configured independently (enable, length, single/dual/quad communication)

- Instruction phase

- Address phase

- Alternate bytes phase

- Dummy cycles phase

- Data phase

- Integrated FIFO for reception and transmission

- 8, 16, and 32-bit data accesses are allowed

- DMA channel for indirect mode operations

- Programmable masking for external flash flag management

- Timeout management

- Interrupt generation on FIFO threshold, timeout, status match, operation complete, and access error

|        |         | Pin N   | lumb    | er       |         |                                       |          |               |       | Pin functions                                                                                                                                                      |                      |

|--------|---------|---------|---------|----------|---------|---------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| LQFP64 | WLCSP72 | WLCSP81 | LQFP100 | UFBGA132 | LQFP144 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                                                                | Additional functions |

| -      | C5      | C5      | -       | D7       | 127     | PG12                                  | I/O      | FT_s          | -     | LPTIM1_ETR, SPI3_NSS,<br>USART1_RTS_DE,<br>FMC_NE4, SAI2_SD_A,<br>EVENTOUT                                                                                         | -                    |

| -      | B5      | B5      | -       | C7       | 128     | PG13                                  | I/O      | FT_fs         | -     | I2C1_SDA, USART1_CK,<br>FMC_A24, EVENTOUT                                                                                                                          | -                    |

| -      | A5      | A5      | _       | C6       | 129     | PG14                                  | I/O      | FT_fs         | -     | I2C1_SCL, FMC_A25,<br>EVENTOUT                                                                                                                                     | -                    |

| -      | -       | -       | -       | F7       | 130     | VSS                                   | S        | -             | -     | -                                                                                                                                                                  | -                    |

| -      | B6      | B6      | -       | G7       | 131     | VDDIO2                                | S        | -             | -     | -                                                                                                                                                                  | -                    |

| -      | -       | -       | -       | K1       | 132     | PG15                                  | I/O      | FT_s          | -     | LPTIM1_OUT,<br>I2C1_SMBA, EVENTOUT                                                                                                                                 | -                    |

| 55     | A6      | A6      | 89      | A8       | 133     | PB3<br>(JTDO-<br>TRACESWO)            | I/O      | FT_la         | (3)   | JTDO-TRACESWO,<br>TIM2_CH2, SPI1_SCK,<br>SPI3_SCK,<br>USART1_RTS_DE,<br>LCD_SEG7, SAI1_SCK_B,<br>EVENTOUT                                                          | COMP2_<br>INM        |

| 56     | C6      | C6      | 90      | A7       | 134     | PB4<br>(NJTRST)                       | I/O      | FT_la         | (3)   | NJTRST, TIM3_CH1,<br>SPI1_MISO, SPI3_MISO,<br>USART1_CTS,<br>UART5_RTS_DE,<br>TSC_G2_IO1, LCD_SEG8,<br>SAI1_MCLK_B,<br>TIM17_BKIN, EVENTOUT                        | COMP2_<br>INP        |

| 57     | C7      | C7      | 91      | C5       | 135     | PB5                                   | I/O      | FT_la         | -     | LPTIM1_IN1, TIM3_CH2,<br>I2C1_SMBA, SPI1_MOSI,<br>SPI3_MOSI, USART1_CK,<br>UART5_CTS,<br>TSC_G2_IO2, LCD_SEG9,<br>COMP2_OUT,<br>SAI1_SD_B, TIM16_BKIN,<br>EVENTOUT | -                    |

| 58     | В7      | B7      | 92      | В5       | 136     | PB6                                   | I/O      | FT_fa         | -     | LPTIM1_ETR, TIM4_CH1,<br>TIM8_BKIN2, I2C1_SCL,<br>DFSDM_DATIN5,<br>USART1_TX,<br>TSC_G2_IO3,<br>TIM8_BKIN2_COMP2,<br>SAI1_FS_B,<br>TIM16_CH1N, EVENTOUT            | COMP2_<br>INP        |

Table 15. STM32L476xxSTM32L476xx pin definitions (continued)

| Symbol    | Parameter Conditions M      |                                      |     | Мах | Unit |  |

|-----------|-----------------------------|--------------------------------------|-----|-----|------|--|

|           | Ambient temperature for the | Maximum power dissipation            | -40 | 85  |      |  |

|           | suffix 6 version            | Low-power dissipation <sup>(5)</sup> | -40 | 105 |      |  |

| т.        | Ambient temperature for the | Maximum power dissipation            | -40 | 105 | °C   |  |

| IA suffix | suffix 7 version            | Low-power dissipation <sup>(5)</sup> | -40 | 125 |      |  |

|           | Ambient temperature for the | Maximum power dissipation            | -40 | 125 |      |  |

|           | suffix 3 version            | Low-power dissipation <sup>(5)</sup> | -40 | 130 |      |  |

|           |                             | Suffix 6 version                     | -40 | 105 |      |  |

| ТJ        | Junction temperature range  | Suffix 7 version                     | -40 | 125 | °C   |  |

|           |                             | Suffix 3 version                     | -40 | 130 | 1    |  |

| Table 22. Genera | I operating | conditions | (continued) |

|------------------|-------------|------------|-------------|

|------------------|-------------|------------|-------------|

1. When RESET is released functionality is guaranteed down to  $V_{BOR0}$  Min.

2. This formula has to be applied only on the power supplies related to the IO structure described by the pin definition table. Maximum I/O input voltage is the smallest value between MIN( $V_{DD}$ ,  $V_{DDA}$ ,  $V_{DDIO2}$ ,  $V_{DDUSB}$ ,  $V_{LCD}$ )+3.6 V and 5.5V.

3. For operation with voltage higher than Min (V<sub>DD</sub>, V<sub>DDA</sub>, V<sub>DDIO2</sub>, V<sub>DDUSB</sub>, V<sub>LCD</sub>) +0.3 V, the internal Pull-up and Pull-Down resistors must be disabled.

4. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$  (see Section 7.7: Thermal characteristics).

In low-power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.7: Thermal characteristics).

### 6.3.2 Operating conditions at power-up / power-down

The parameters given in *Table 23* are derived from tests performed under the ambient temperature condition summarized in *Table 22*.

| Symbol              | Parameter                         | Conditions | Min | Max | Unit |

|---------------------|-----------------------------------|------------|-----|-----|------|

| +                   | V <sub>DD</sub> rise time rate    |            | 0   | ∞   |      |

| t <sub>VDD</sub>    | V <sub>DD</sub> fall time rate    | -          | 10  | ∞   |      |

| +                   | V <sub>DDA</sub> rise time rate   |            | 0   | ∞   |      |

| t <sub>VDDA</sub>   | V <sub>DDA</sub> fall time rate   | -          | 10  | ∞   | μs/V |

| +                   | V <sub>DDUSB</sub> rise time rate |            | 0   | ∞   | μ5/ν |

| t <sub>VDDUSB</sub> | V <sub>DDUSB</sub> fall time rate | -          | 10  | ∞   |      |

| t <sub>VDDIO2</sub> | V <sub>DDIO2</sub> rise time rate | _          | 0   | ∞   |      |

|                     | V <sub>DDIO2</sub> fall time rate | -          | 10  | ∞   |      |

Table 23. Operating conditions at power-up / power-down

### 6.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 24* are derived from tests performed under the ambient temperature conditions summarized in *Table 22: General operating conditions*.

| Symbol                                       | Parameter                                                               | Conditions                                              | ТҮР      |       |       |       |        | MAX <sup>(1)</sup> |       |       |       |        | Unit   |    |

|----------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------|----------|-------|-------|-------|--------|--------------------|-------|-------|-------|--------|--------|----|

| Symbol                                       | Falameter                                                               | -                                                       | $V_{DD}$ | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C             | 25 °C | 55 °C | 85 °C | 105 °C | 125 °C | -  |

|                                              |                                                                         |                                                         | 1.8 V    | 210   | 378   | 1299  | 3437   | 9357               | -     | -     | -     | -      | -      |    |

|                                              | Supply current                                                          | RTC clocked by LSE                                      | 2.4 V    | 303   | 499   | 1577  | 4056   | 10825              | -     | -     | -     | -      | -      | 1  |

| I <sub>DD</sub> (Shutdown<br>with RTC)<br>re | in Shutdown<br>mode<br>(backup<br>registers<br>retained) RTC<br>enabled | bypassed at 32768 Hz                                    | 3 V      | 422   | 655   | 1925  | 4820   | 12569              | -     | -     | -     | -      | -      | 1  |

|                                              |                                                                         |                                                         | 3.6 V    | 584   | 888   | 2511  | 6158   | 15706              | -     | -     | -     | -      | -      | nA |

|                                              |                                                                         | s<br>t) RTC RTC clocked by LSE                          | 1.8 V    | 329   | 499   | 1408  | 3460   | -                  | -     | -     | -     | -      | -      |    |

|                                              |                                                                         |                                                         | 2.4 V    | 431   | 634   | 1688  | 4064   | -                  | -     | -     | -     | -      | -      | 1  |

|                                              |                                                                         |                                                         | 3 V      | 554   | 791   | 2025  | 4795   | -                  | -     | -     | -     | -      | -      | 1  |

|                                              |                                                                         |                                                         | 3.6 V    | 729   | 1040  | 2619  | 6129   | -                  | -     | -     | -     | -      | -      | 1  |

| l <sub>DD</sub> (wakeup<br>from<br>Shutdown) | Supply current<br>during wakeup<br>from Shutdown<br>mode                | Wakeup clock is<br>MSI = 4 MHz.<br>See <sup>(3)</sup> . | 3 V      | 0.6   | -     | -     | -      | -                  | -     | -     | -     | -      | -      | mA |

1. Guaranteed by characterization results, unless otherwise specified.

2. Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8 pF loading capacitors.

3. Wakeup with code execution from Flash. Average value given for a typical wakeup time as specified in *Table 41: Low-power mode wakeup timings*.

118/232

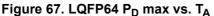

#### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in Section 6.3.14. However, the recommended clock input waveform is shown in Figure 17.

| Symbol                                       | Parameter                             | Conditions | Min                    | Тур    | Мах                    | Unit |

|----------------------------------------------|---------------------------------------|------------|------------------------|--------|------------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source frequency  | -          | -                      | 32.768 | 1000                   | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage | -          | 0.7 V <sub>DDIOx</sub> | -      | V <sub>DDIOx</sub>     | V    |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage  | -          | V <sub>SS</sub>        | -      | 0.3 V <sub>DDIOx</sub> |      |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time             | -          | 250                    | -      | -                      | ns   |

| Table 44. Low-speed external user clock characteristics <sup>(1)</sup> |

|------------------------------------------------------------------------|

|------------------------------------------------------------------------|

1. Guaranteed by design.

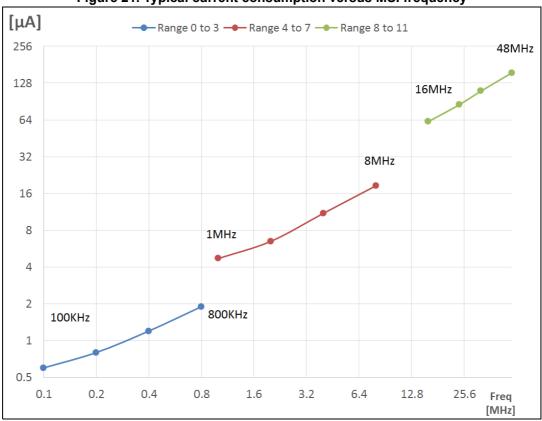

Figure 21. Typical current consumption versus MSI frequency

Low-speed internal (LSI) RC oscillator

| Table 49. LSI oscillator of | characteristics <sup>(1)</sup> |

|-----------------------------|--------------------------------|

|-----------------------------|--------------------------------|

| Symbol                                 | Parameter                            | Conditions                                          |      | Тур | Max   | Unit |  |

|----------------------------------------|--------------------------------------|-----------------------------------------------------|------|-----|-------|------|--|

| f                                      |                                      | V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 30 °C     |      | -   | 32.96 | kHz  |  |

| f <sub>LSI</sub> L                     | LSI Frequency                        | V <sub>DD</sub> = 1.62 to 3.6 V, TA = -40 to 125 °C | 29.5 | -   | 34    |      |  |

| t <sub>SU</sub> (LSI) <sup>(2)</sup>   | LSI oscillator start-<br>up time     | -                                                   | -    | 80  | 130   | μs   |  |

| t <sub>STAB</sub> (LSI) <sup>(2)</sup> | LSI oscillator<br>stabilisation time | 5% of final frequency                               | -    | 125 | 180   | μs   |  |

| I <sub>DD</sub> (LSI) <sup>(2)</sup>   | LSI oscillator power consomption     | -                                                   | -    | 110 | 180   | nA   |  |

1. Guaranteed by characterization results.

2. Guaranteed by design.

### 6.3.9 PLL characteristics

The parameters given in *Table 50* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 22: General operating conditions*.

| Sym-<br>bol                                          | Parameter              | Conditions <sup>(4)</sup>                                                                                                                        |                          |                          | Min  | Тур  | Max | Unit                                |

|------------------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|------|------|-----|-------------------------------------|

|                                                      |                        |                                                                                                                                                  | Single                   | Fast channel (max speed) | -    | 4    | 5   |                                     |

| Total<br>ET unadjusted                               |                        | ended                                                                                                                                            | Slow channel (max speed) | -                        | 4    | 5    |     |                                     |

|                                                      | unadjusted<br>error    |                                                                                                                                                  | Differential             | Fast channel (max speed) | -    | 3.5  | 4.5 |                                     |

|                                                      |                        |                                                                                                                                                  | Differential             | Slow channel (max speed) | -    | 3.5  | 4.5 |                                     |

|                                                      |                        |                                                                                                                                                  | Single                   | Fast channel (max speed) | -    | 1    | 2.5 |                                     |

| EO                                                   | Offset                 |                                                                                                                                                  | ended                    | Slow channel (max speed) | -    | 1    | 2.5 |                                     |

| EO                                                   | error                  |                                                                                                                                                  | Differential             | Fast channel (max speed) | -    | 1.5  | 2.5 |                                     |

|                                                      |                        |                                                                                                                                                  | Dillerential             | Slow channel (max speed) | -    | 1.5  | 2.5 |                                     |

|                                                      |                        |                                                                                                                                                  | Single                   | Fast channel (max speed) | -    | 2.5  | 4.5 |                                     |

| EG                                                   | Gain error             |                                                                                                                                                  | ended                    | Slow channel (max speed) | -    | 2.5  | 4.5 |                                     |

| EG                                                   | Gainenor               | erential<br>arity<br>r ADC clock frequency $\leq$<br>80 MHz,<br>Sampling rate $\leq$ 5.33 Msps,<br>V <sub>DDA</sub> = VREF+ = 3 V,<br>TA = 25 °C | Differential             | Fast channel (max speed) | -    | 2.5  | 3.5 | - LSB<br>-<br>-<br>-<br>-<br>-<br>- |

|                                                      |                        |                                                                                                                                                  | Differential             | Slow channel (max speed) | -    | 2.5  | 3.5 |                                     |

|                                                      |                        |                                                                                                                                                  | Single<br>ended          | Fast channel (max speed) | -    | 1    | 1.5 |                                     |

| ED                                                   | Differential linearity |                                                                                                                                                  |                          | Slow channel (max speed) | -    | 1    | 1.5 |                                     |

| ED                                                   | error                  |                                                                                                                                                  | Differential             | Fast channel (max speed) | -    | 1    | 1.2 |                                     |

|                                                      |                        |                                                                                                                                                  |                          | Slow channel (max speed) | -    | 1    | 1.2 |                                     |

|                                                      |                        |                                                                                                                                                  | Single<br>ended          | Fast channel (max speed) | -    | 1.5  | 2.5 |                                     |

| EL                                                   | Integral<br>linearity  |                                                                                                                                                  |                          | Slow channel (max speed) | -    | 1.5  | 2.5 |                                     |

| EL                                                   | error                  |                                                                                                                                                  | Differential             | Fast channel (max speed) | -    | 1    | 2   |                                     |

|                                                      |                        |                                                                                                                                                  |                          | Slow channel (max speed) | -    | 1    | 2   |                                     |

|                                                      |                        |                                                                                                                                                  | Single                   | Fast channel (max speed) | 10.4 | 10.5 | -   |                                     |

| ENOB                                                 | Effective number of    |                                                                                                                                                  | ended                    | Slow channel (max speed) | 10.4 | 10.5 | -   |                                     |

| ENOD                                                 | bits                   |                                                                                                                                                  | Differential             | Fast channel (max speed) | 10.8 | 10.9 | -   | bits                                |

|                                                      |                        |                                                                                                                                                  | Differential             | Slow channel (max speed) | 10.8 | 10.9 | -   | 1                                   |

|                                                      | Cignal to              |                                                                                                                                                  | Single                   | Fast channel (max speed) | 64.4 | 65   | -   |                                     |

| SINAD Signal-to-<br>noise and<br>distortion<br>ratio | noise and              |                                                                                                                                                  | ended                    | Slow channel (max speed) | 64.4 | 65   | -   |                                     |

|                                                      |                        |                                                                                                                                                  | Differential             | Fast channel (max speed) | 66.8 | 67.4 | -   |                                     |

|                                                      | 1400                   | Di Di                                                                                                                                            | Differential             | Slow channel (max speed) | 66.8 | 67.4 | -   | ٩D                                  |

|                                                      |                        |                                                                                                                                                  | Single<br>ended          | Fast channel (max speed) | 65   | 66   | -   | dB                                  |

| SNR                                                  | Signal-to-             |                                                                                                                                                  |                          | Slow channel (max speed) | 65   | 66   | -   | 1                                   |

| SINK                                                 | noise ratio            |                                                                                                                                                  | Difforential             | Fast channel (max speed) | 67   | 68   | -   |                                     |

|                                                      |                        |                                                                                                                                                  | Differential             | Slow channel (max speed) | 67   | 68   | -   |                                     |

# 6.3.18 Digital-to-Analog converter characteristics

| Symbol                | Parameter                                                                                                           | Co                                                                          | onditions                                        | Min     | Тур              | Max                        | Unit |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------|---------|------------------|----------------------------|------|

| V <sub>DDA</sub>      | Analog supply voltage for<br>DAC ON                                                                                 | -                                                                           |                                                  | 1.8     | -                | 3.6                        |      |

| $V_{REF}$ +           | Positive reference voltage                                                                                          | -                                                                           |                                                  | 1.8     | -                | $V_{DDA}$                  | V    |

| V <sub>REF-</sub>     | Negative reference voltage                                                                                          |                                                                             | -                                                |         | V <sub>SSA</sub> |                            |      |

| RL                    | Resistive load                                                                                                      | DAC output<br>buffer ON                                                     | connected to $V_{SSA}$<br>connected to $V_{DDA}$ | 5<br>25 | -                | -                          | kΩ   |

| R <sub>O</sub>        | Output Impedance                                                                                                    | DAC output bu                                                               |                                                  | 9.6     | 11.7             | 13.8                       | kΩ   |

|                       | Output impedance sample                                                                                             |                                                                             | V <sub>DD</sub> = 2.7 V                          | -       | -                | 2                          |      |

| R <sub>BON</sub>      | and hold mode, output buffer ON                                                                                     | DAC output<br>buffer ON                                                     | V <sub>DD</sub> = 2.0 V                          | -       | -                | 3.5                        | kΩ   |

|                       | Output impedance sample                                                                                             | DAC output                                                                  | V <sub>DD</sub> = 2.7 V                          | -       | -                | 16.5                       | kΩ   |

| R <sub>BOFF</sub>     | and hold mode, output<br>buffer OFF                                                                                 | buffer OFF                                                                  | V <sub>DD</sub> = 2.0 V                          | -       | -                | 18.0                       |      |

| CL                    | Canaaitiya laad                                                                                                     | DAC output buffer ON                                                        |                                                  | -       | -                | 50                         | pF   |

| C <sub>SH</sub>       | Capacitive load                                                                                                     | Sample and hold mode                                                        |                                                  | -       | - 0.1            | 1                          | μF   |

| V <sub>DAC_OUT</sub>  | Voltage on DAC_OUT                                                                                                  | DAC output buffer ON                                                        |                                                  | 0.2     | -                | V <sub>REF+</sub><br>- 0.2 | v    |

|                       | output                                                                                                              | DAC output buffer OFF                                                       |                                                  | 0       | -                | V <sub>REF+</sub>          |      |

|                       | Cottling time (full coole) for                                                                                      |                                                                             | ±0.5 LSB                                         | -       | 1.7              | 3                          | μs   |

|                       |                                                                                                                     | Normal mode<br>DAC output                                                   | ±1 LSB                                           | -       | 1.6              | 2.9                        |      |

|                       | between the lowest and the highest input codes                                                                      | buffer ON                                                                   | ±2 LSB                                           | -       | 1.55             | 2.85                       |      |

| t <sub>SETTLING</sub> | when DAC_OUT reaches                                                                                                | CL ≤ 50 pF,<br>RL ≥ 5 kΩ                                                    | ±4 LSB                                           | -       | 1.48             | 2.8                        |      |

|                       | final value ±0.5LSB,<br>±1 LSB, ±2 LSB, ±4 LSB,                                                                     |                                                                             | ±8 LSB                                           | -       | 1.4              | 2.75                       |      |

| ±8 LSB)               |                                                                                                                     | Normal mode DAC output buffer<br>OFF, ±1LSB, CL = 10 pF                     |                                                  | -       | 2                | 2.5                        |      |

| . (2)                 | Wakeup time from off state (setting the ENx bit in the                                                              | Normal mode DAC output buffer ON CL $\leq$ 50 pF, RL $\geq$ 5 k $\Omega$    |                                                  | -       | 4.2              | 7.5                        |      |

| 'WAKEUP'              | t <sub>WAKEUP</sub> <sup>(2)</sup> (Setting the ENX bit in the<br>DAC Control register) until<br>final value ±1 LSB |                                                                             | Normal mode DAC output buffer<br>OFF, CL ≤ 10 pF |         | 2                | 5                          | μs   |

| PSRR                  | V <sub>DDA</sub> supply rejection ratio                                                                             | Normal mode DAC output buffer ON<br>CL $\leq$ 50 pF, RL = 5 k $\Omega$ , DC |                                                  | -       | -80              | -28                        | dB   |

# Table 69. DAC characteristics<sup>(1)</sup>

### 6.3.27 Communication interfaces characteristics

### I<sup>2</sup>C interface characteristics

The I2C interface meets the timings requirements of the  $I^2$ C-bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+): with a bit rate up to 1 Mbit/s.

The I2C timings requirements are guaranteed by design when the I2C peripheral is properly configured (refer to RM0351 reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DDIOx}$  is disabled, but is still present. Only FT\_f I/O pins support Fm+ low level output current maximum requirement. Refer to Section 6.3.14: I/O port characteristics for the I2C I/Os characteristics.

All I2C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

| Symbol          | Parameter                                                              | Min               | Мах                | Unit |

|-----------------|------------------------------------------------------------------------|-------------------|--------------------|------|

| t <sub>AF</sub> | Maximum pulse width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |

### Table 82. I2C analog filter characteristics<sup>(1)</sup>

1. Guaranteed by design.

2. Spikes with widths below  $t_{AF(min)}$  are filtered.

3. Spikes with widths above  $t_{AF(max)}$  are not filtered

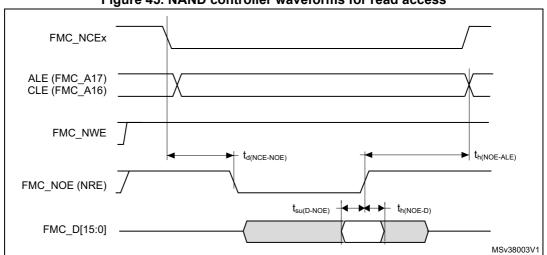

Figure 45. NAND controller waveforms for read access

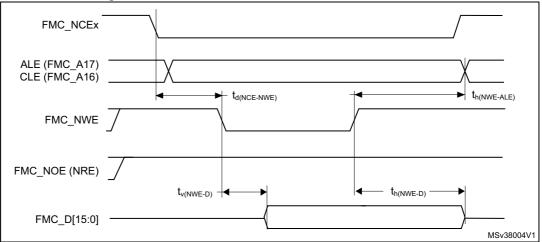

Figure 46. NAND controller waveforms for write access

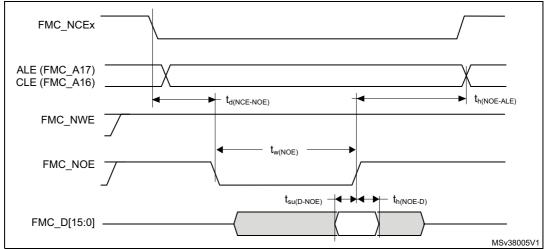

Figure 47. NAND controller waveforms for common memory read access

DocID025976 Rev 4

### **Device marking**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 7.4 WLCSP81 package information

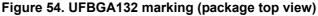

Figure 58. WLCSP81 - 81-ball, 4.4084 x 3.7594 mm, 0.4 mm pitch wafer level chip scale package outline

1. Drawing is not to scale.

| Table 108. WLCSP81- 81-ball, 4.4084 x 3.7594 mm, 0.4 mm pitch wafer level chip scale |

|--------------------------------------------------------------------------------------|

| package mechanical data                                                              |

| Symbol            | millimeters |        |        | inches <sup>(1)</sup> |        |        |  |

|-------------------|-------------|--------|--------|-----------------------|--------|--------|--|

| Symbol            | Min         | Тур    | Max    | Min                   | Тур    | Max    |  |

| А                 | 0.525       | 0.555  | 0.585  | 0.0207                | 0.0219 | 0.0230 |  |

| A1                | -           | 0.175  | -      | -                     | 0.0069 | -      |  |

| A2                | -           | 0.380  | -      | -                     | 0.0150 | -      |  |

| A3 <sup>(2)</sup> | -           | 0.025  | -      | -                     | 0.0010 | -      |  |

| b <sup>(3)</sup>  | 0.220       | 0.250  | 0.280  | 0.0087                | 0.0098 | 0.0110 |  |

| D                 | 4.3734      | 4.4084 | 4.4434 | 0.1722                | 0.1736 | 0.1749 |  |

| E                 | 3.7244      | 3.7594 | 3.7944 | 0.1466                | 0.1480 | 0.1494 |  |

| е                 | -           | 0.400  | -      | -                     | 0.0157 | -      |  |

| e1                | -           | 3.200  | -      | -                     | 0.1260 | -      |  |

| e2                | -           | 3.200  | -      | -                     | 0.1260 | -      |  |

# Table 108. WLCSP81- 81-ball, 4.4084 x 3.7594 mm, 0.4 mm pitch wafer level chip scalepackage mechanical data (continued)

| Symbol | millimeters |        |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|--------|-------|-----------------------|--------|--------|--|

| Symbol | Min         | Тур    | Мах   | Min                   | Тур    | Max    |  |

| F      | -           | 0.6042 | -     | -                     | 0.0238 | -      |  |

| G      | -           | 0.2797 | -     | -                     | 0.0110 | -      |  |

| aaa    | -           | -      | 0.100 | -                     | -      | 0.0039 |  |

| bbb    | -           | -      | 0.100 | -                     | -      | 0.0039 |  |

| ссс    | -           | -      | 0.100 | -                     | -      | 0.0039 |  |

| ddd    | -           | -      | 0.050 | -                     | -      | 0.0020 |  |

| eee    | -           | -      | 0.050 | -                     | -      | 0.0020 |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

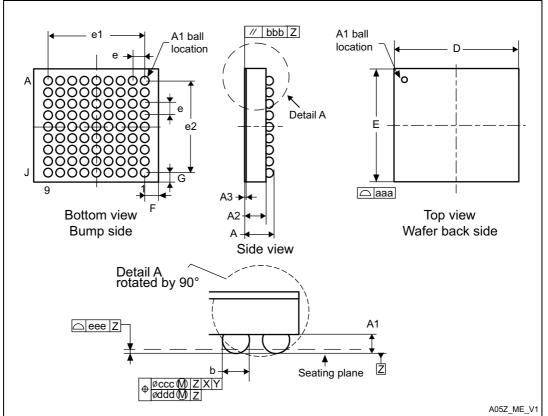

# Figure 59. WLCSP81- 81-ball, 4.4084 x 3.7594 mm, 0.4 mm pitch wafer level chip scale package recommended footprint

| Table 109. WLCSP81 | recommended PCB | design rules ( | (0.4 mm pitch) |

|--------------------|-----------------|----------------|----------------|

|                    |                 | acoigniaico    |                |

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.4 mm                                                           |

| Dpad              | 0.225 mm                                                         |

| Dsm               | 0.290 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.250 mm                                                         |

| Stencil thickness | 0.100 mm                                                         |

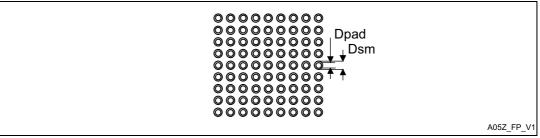

### **Device marking**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Using the values obtained in *Table 113*  $T_{Jmax}$  is calculated as follows:

- For LQFP64, 45 °C/W

- T<sub>Jmax</sub> = 100 °C + (45 °C/W × 134 mW) = 100 °C + 6.03 °C = 106.03 °C

This is above the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Section 8: Part numbering*) unless we reduce the power dissipation in order to be able to use suffix 6 parts.

Refer to *Figure 67* to select the required temperature range (suffix 6 or 7) according to your ambient temperature or power requirements.