# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                              |

|----------------------------|-----------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                                  |

| Speed                      | 80MHz                                                                                               |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                                          |

| Number of I/O              | 114                                                                                                 |

| Program Memory Size        | 1MB (1M × 8)                                                                                        |

| Program Memory Type        | FLASH                                                                                               |

| EEPROM Size                | -                                                                                                   |

| RAM Size                   | 128K x 8                                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                                        |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                               |

| Oscillator Type            | Internal                                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                   |

| Mounting Type              | Surface Mount                                                                                       |

| Package / Case             | 144-LQFP                                                                                            |

| Supplier Device Package    | 144-LQFP (20x20)                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l476zgt6                               |

|                            |                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 2. STM32L476xx family device features and peripheral counts (continued)

| Peripheral            | STM32L476<br>Zx | STM32L476<br>Qx                                                                                                                                    | STM32L476<br>Vx | STM32L476<br>Mx | STM32L476<br>Jx | STM32L476<br>Rx |  |  |  |  |

|-----------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|-----------------|--|--|--|--|

| Max. CPU frequency    |                 | 80 MHz                                                                                                                                             |                 |                 |                 |                 |  |  |  |  |

| Operating voltage     |                 |                                                                                                                                                    | 1.71 to         | o 3.6 V         |                 |                 |  |  |  |  |

| Operating temperature |                 | Ambient operating temperature: -40 to 85 °C / -40 to 105 °C / -40 to 125 °C<br>Junction temperature: -40 to 105 °C / -40 to 125 °C / -40 to 130 °C |                 |                 |                 |                 |  |  |  |  |

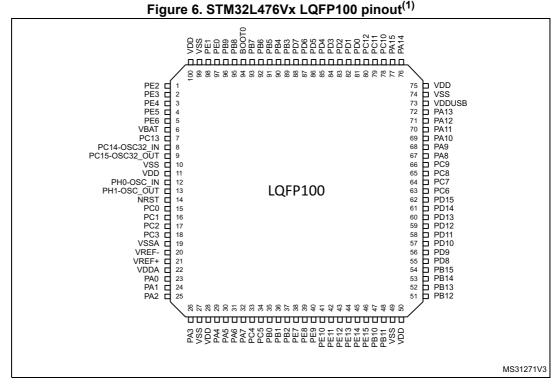

| Packages              | LQFP144         | UFBGA132                                                                                                                                           | LQFP100         | WLCSP81         | WLCSP72         | LQFP64          |  |  |  |  |

1. For the LQFP100 package, only FMC Bank1 is available. Bank1 can only support a multiplexed NOR/PSRAM memory using the NE1 Chip Select.

## 3.4 Embedded Flash memory

STM32L476xx devices feature up to 1 Mbyte of embedded Flash memory available for storing programs and data. The Flash memory is divided into two banks allowing read-while-write operations. This feature allows to perform a read operation from one bank while an erase or program operation is performed to the other bank. The dual bank boot is also supported. Each bank contains 256 pages of 2 Kbyte.

Flexible protections can be configured thanks to option bytes:

- Readout protection (RDP) to protect the whole memory. Three levels are available:

- Level 0: no readout protection

- Level 1: memory readout protection: the Flash memory cannot be read from or written to if either debug features are connected, boot in RAM or bootloader is selected

- Level 2: chip readout protection: debug features (Cortex-M4 JTAG and serial wire), boot in RAM and bootloader selection are disabled (JTAG fuse). This selection is irreversible.

| Area      | Protection<br>level | U    | ser executio | on                 | Debug, boot from RAM or boot<br>from system memory (loader) |       |                    |  |  |

|-----------|---------------------|------|--------------|--------------------|-------------------------------------------------------------|-------|--------------------|--|--|

|           | IEVEI               | Read | Write        | Erase              | Read                                                        | Write | Erase              |  |  |

| Main      | 1                   | Yes  | Yes          | Yes                | No                                                          | No    | No                 |  |  |

| memory    | 2                   | Yes  | Yes          | Yes                | N/A                                                         | N/A   | N/A                |  |  |

| System    | 1                   | Yes  | No           | No                 | Yes                                                         | No    | No                 |  |  |

| memory    | 2                   | Yes  | No           | No                 | N/A                                                         | N/A   | N/A                |  |  |

| Option    | 1                   | Yes  | Yes          | Yes                | Yes                                                         | Yes   | Yes                |  |  |

| bytes     | 2                   | Yes  | No           | No                 | N/A                                                         | N/A   | N/A                |  |  |

| Backup    | 1                   | Yes  | Yes          | N/A <sup>(1)</sup> | No                                                          | No    | N/A <sup>(1)</sup> |  |  |

| registers | 2                   | Yes  | Yes          | N/A                | N/A                                                         | N/A   | N/A                |  |  |

| SRAM2     | 1                   | Yes  | Yes          | Yes <sup>(1)</sup> | No                                                          | No    | No <sup>(1)</sup>  |  |  |

| STAIVIZ   | 2                   | Yes  | Yes          | Yes                | N/A                                                         | N/A   | N/A                |  |  |

Table 3. Access status versus readout protection level and execution modes

1. Erased when RDP change from Level 1 to Level 0.

- Write protection (WRP): the protected area is protected against erasing and programming. Two areas per bank can be selected, with 2-Kbyte granularity.

- Proprietary code readout protection (PCROP): a part of the flash memory can be

protected against read and write from third parties. The protected area is execute-only:

it can only be reached by the STM32 CPU, as an instruction code, while all other

accesses (DMA, debug and CPU data read, write and erase) are strictly prohibited.

One area per bank can be selected, with 64-bit granularity. An additional option bit

(PCROP\_RDP) allows to select if the PCROP area is erased or not when the RDP

protection is changed from Level 1 to Level 0.

Standby mode, supplied by the low-power Regulator (Standby with RAM2 retention mode).

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, WKUP pin event (configurable rising or falling edge), or an RTC event occurs (alarm, periodic wakeup, timestamp, tamper) or a failure is detected on LSE (CSS on LSE).

The system clock after wakeup is MSI up to 8 MHz.

Shutdown mode

The Shutdown mode allows to achieve the lowest power consumption. The internal regulator is switched off so that the VCORE domain is powered off. The PLL, the HSI16, the MSI, the LSI and the HSE oscillators are also switched off.

The RTC can remain active (Shutdown mode with RTC, Shutdown mode without RTC).

The BOR is not available in Shutdown mode. No power voltage monitoring is possible in this mode, therefore the switch to Backup domain is not supported.

SRAM1, SRAM2 and register contents are lost except for registers in the Backup domain.

The device exits Shutdown mode when an external reset (NRST pin), a WKUP pin event (configurable rising or falling edge), or an RTC event occurs (alarm, periodic wakeup, timestamp, tamper).

The system clock after wakeup is MSI at 4 MHz.

## 3.10 Interconnect matrix

Several peripherals have direct connections between them. This allows autonomous communication between peripherals, saving CPU resources thus power supply consumption. In addition, these hardware connections allow fast and predictable latency.

Depending on peripherals, these interconnections can operate in Run, Sleep, low-power run and sleep, Stop 0, Stop 1 and Stop 2 modes.

| Interconnect source                                                                                                                                 | Interconnect Interconnect destination |                                                                    |   | Sleep | Low-power run | Low-power sleep | Stop 0 / Stop 1 | Stop 2   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------------------------|---|-------|---------------|-----------------|-----------------|----------|

|                                                                                                                                                     | TIMx                                  | Timers synchronization or chaining                                 | Υ | Υ     | Y             | Υ               | -               | -        |

| TIMx                                                                                                                                                | ADCx<br>DACx<br>DFSDM                 | Conversion triggers                                                | Y | Y     | Y             | Y               | -               | -        |

|                                                                                                                                                     | DMA                                   | Memory to memory transfer trigger                                  | Y | Y     | Y             | Y               | -               | -        |

|                                                                                                                                                     | COMPx                                 | Comparator output blanking                                         | Y | Y     | Y             | Υ               | -               | -        |

| COMPx                                                                                                                                               | TIM1, 8<br>TIM2, 3                    | Timer input channel, trigger, break from analog signals comparison |   | Y     | Y             | Y               | -               | -        |

|                                                                                                                                                     | LPTIMERx                              | Low-power timer triggered by analog signals comparison             | Y | Y     | Y             | Y               | Y               | Y<br>(1) |

| ADCx                                                                                                                                                | TIM1, 8                               | Timer triggered by analog watchdog                                 | Y | Y     | Y             | Υ               | -               | -        |

|                                                                                                                                                     | TIM16                                 | Timer input channel from RTC events                                | Υ | Υ     | Y             | Υ               | -               | -        |

| RTC                                                                                                                                                 | LPTIMERx                              | Low-power timer triggered by RTC alarms or tampers                 | Y | Y     | Y             | Y               | Y               | Y<br>(1) |

| All clocks sources (internal and external)                                                                                                          | TIM2<br>TIM15, 16, 17                 | Clock source used as input channel for RC measurement and trimming | Y | Y     | Y             | Y               | -               | -        |

| USB                                                                                                                                                 | TIM2                                  | Timer triggered by USB SOF                                         | Y | Y     | -             | -               | -               | -        |

| CSS<br>CPU (hard fault)<br>RAM (parity error)<br>Flash memory (ECC error)<br>COMPx<br>PVD<br>DFSDM (analog<br>watchdog, short circuit<br>detection) | TIM1,8<br>TIM15,16,17                 | Timer break                                                        | Y | Y     | Y             | Y               | _               | -        |

Table 6. STM32L476xx peripherals interconnect matrix

## 3.15 Analog to digital converter (ADC)

The device embeds 3 successive approximation analog-to-digital converters with the following features:

- 12-bit native resolution, with built-in calibration

- 5.33 Msps maximum conversion rate with full resolution

- Down to 18.75 ns sampling time

- Increased conversion rate for lower resolution (up to 8.88 Msps for 6-bit resolution)

- Up to 24 external channels, some of them shared between ADC1 and ADC2, or ADC1, ADC2 and ADC3.

- 5 Internal channels: internal reference voltage, temperature sensor, VBAT/3, DAC1 and DAC2 outputs.

- One external reference pin is available on some package, allowing the input voltage range to be independent from the power supply

- Single-ended and differential mode inputs

- Low-power design

- Capable of low-current operation at low conversion rate (consumption decreases linearly with speed)

- Dual clock domain architecture: ADC speed independent from CPU frequency

- Highly versatile digital interface

- Single-shot or continuous/discontinuous sequencer-based scan mode: 2 groups of analog signals conversions can be programmed to differentiate background and high-priority real-time conversions

- Handles two ADC converters for dual mode operation (simultaneous or interleaved sampling modes)

- Each ADC support multiple trigger inputs for synchronization with on-chip timers and external signals

- Results stored into 3 data register or in RAM with DMA controller support

- Data pre-processing: left/right alignment and per channel offset compensation

- Built-in oversampling unit for enhanced SNR

- Channel-wise programmable sampling time

- Three analog watchdog for automatic voltage monitoring, generating interrupts and trigger for selected timers

- Hardware assistant to prepare the context of the injected channels to allow fast context switching

#### 3.15.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{TS}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC1\_IN17 and ADC3\_IN17 input channels which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

DocID025976 Rev 4

## 3.28 Low-power universal asynchronous receiver transmitter (LPUART)

The device embeds one Low-Power UART. The LPUART supports asynchronous serial communication with minimum power consumption. It supports half duplex single wire communication and modem operations (CTS/RTS). It allows multiprocessor communication.

The LPUART has a clock domain independent from the CPU clock, and can wakeup the system from Stop mode. The wake up events from Stop mode are programmable and can be:

- Start bit detection

- Any received data frame

- A specific programmed data frame

Only a 32.768 kHz clock (LSE) is needed to allow LPUART communication up to 9600 baud. Therefore, even in Stop mode, the LPUART can wait for an incoming frame while having an extremely low energy consumption. Higher speed clock can be used to reach higher baudrates.

LPUART interface can be served by the DMA controller.

|   | 1                  | 2    | 3               | 4               | 5   | 6    | 7      | 8    | 9    | 10   | 11     | 12   |        |

|---|--------------------|------|-----------------|-----------------|-----|------|--------|------|------|------|--------|------|--------|

| А | PE3                | PE1  | PB8             | BOOTO           | PD7 | PD5  | PB4    | PB3  | PA15 | PA14 | PA13   | PA12 |        |

| в | PE4                | PE2  | PB9             | PB7             | PB6 | PD6  | PD4    | PD3  | PD1  | PC12 | PC10   | PA11 |        |

| с | PC13               | PE5  | PE0             | VDD             | PB5 | PG14 | PG13   | PD2  | PD0  | PC11 | VDDUSB | PA10 |        |

| D | PC14-<br>OSC32_IN  | PE6  | vss             | PF2             | PF1 | PF0  | PG12   | PG10 | PG9  | PA9  | PA8    | PC9  |        |

| E | PC15-<br>OSC32_OUT | VBAT | VSS             | PF3             |     |      |        |      | PG5  | PC8  | PC7    | PC6  |        |

| F | PH0-OSC_IN         | VSS  | PF4             | PF5             |     | VSS  | VSS    |      | PG3  | PG4  | vss    | VSS  |        |

| G | PH1-<br>OSC_OUT    | VDD  | PG11            | PG6             |     | VDD  | VDDIO2 |      | PG1  | PG2  | VDD    | VDD  |        |

| н | PC0                | NRST | VDD             | PG7             |     |      |        |      | PG0  | PD15 | PD14   | PD13 |        |

| L | VSSA/VREF-         | PC1  | PC2             | PA4             | PA7 | PG8  | PF12   | PF14 | PF15 | PD12 | PD11   | PD10 |        |

| к | PG15               | PC3  | PA2             | PA5             | PC4 | PF11 | PF13   | PD9  | PD8  | PB15 | PB14   | PB13 |        |

| L | VREF+              | PA0  | PA3             | PA6             | PC5 | PB2  | PE8    | PE10 | PE12 | PB10 | PB11   | PB12 |        |

| м | VDDA               | PA1  | OPAMP1_<br>VINM | OPAMP2_<br>VINM | PB0 | PB1  | PE7    | PE9  | PE11 | PE13 | PE14   | PE15 |        |

|   |                    |      |                 |                 |     |      |        |      |      |      |        | MSv3 | 5003V7 |

Figure 5. STM32L476Qx UFBGA132 ballout<sup>(1)</sup>

1. The above figure shows the package top view.

1. The above figure shows the package top view.

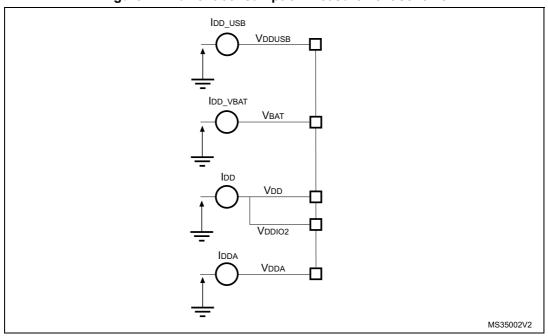

#### 6.1.7 Current consumption measurement

#### Figure 14. Current consumption measurement scheme

## 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 19: Voltage characteristics*, *Table 20: Current characteristics* and *Table 21: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                                                                                            | Min                  | Мах                                                                                                                                                                                         | Unit |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| $V_{DDX}$ - $V_{SS}$              | External main supply voltage (including $V_{DD}$ , $V_{DDA}$ , $V_{DDIO2}$ , $V_{DDUSB}$ , $V_{LCD}$ , $V_{BAT}$ ) | -0.3                 | 4.0                                                                                                                                                                                         | V    |

|                                   | Input voltage on FT_xxx pins                                                                                       | V <sub>SS</sub> -0.3 | $\begin{array}{c} \text{min} \ (\text{V}_{\text{DD}}, \ \text{V}_{\text{DDA}}, \ \text{V}_{\text{DDIO2}}, \ \text{V}_{\text{DDUSB}}, \\ \text{V}_{\text{LCD}} ) + 4.0^{(3)(4)} \end{array}$ |      |

| V <sub>IN</sub> <sup>(2)</sup>    | Input voltage on TT_xx pins                                                                                        | V <sub>SS</sub> -0.3 | 4.0                                                                                                                                                                                         | V    |

|                                   | Input voltage on BOOT0 pin                                                                                         | V <sub>SS</sub>      | 9.0                                                                                                                                                                                         |      |

|                                   | Input voltage on any other pins                                                                                    | V <sub>SS</sub> -0.3 | 4.0                                                                                                                                                                                         |      |

| ΔV <sub>DDx</sub>                 | Variations between different V <sub>DDX</sub> power pins of the same domain                                        | -                    | 50                                                                                                                                                                                          | mV   |

| V <sub>SSx</sub> -V <sub>SS</sub> | Variations between all the different ground pins <sup>(5)</sup>                                                    | -                    | 50                                                                                                                                                                                          | mV   |

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ,  $V_{DDIO2}$ ,  $V_{DDUSB}$ ,  $V_{LCD}$ ,  $V_{BAT}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

#### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

#### I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 58: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

#### I/O dynamic current consumption

In addition to the internal peripheral current consumption measured previously (see *Table 40: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the I/O supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DDIOx} \times f_{SW} \times C$$

where

${\rm I}_{\rm SW}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

$V_{DDIOx}$  is the I/O supply voltage

$f_{SW}$  is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$ +  $C_{EXT}$  +  $C_S$

$C_S$  is the PCB board capacitance including the pad pin.

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

#### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 40*. The MCU is placed under the following conditions:

- All I/O pins are in Analog mode

- The given value is calculated by measuring the difference of the current consumptions:

- when the peripheral is clocked on

- when the peripheral is clocked off

- Ambient operating temperature and supply voltage conditions summarized in *Table 19: Voltage characteristics*

- The power consumption of the digital part of the on-chip peripherals is given in *Table 40*. The power consumption of the analog part of the peripherals (where applicable) is indicated in each related section of the datasheet.

| Peripheral |                                 | Range 1 | Range 2 | Low-power run<br>and sleep | Unit   |

|------------|---------------------------------|---------|---------|----------------------------|--------|

|            | Bus Matrix <sup>(1)</sup>       | 4.5     | 3.7     | 4.1                        |        |

|            | ADC independent clock domain    | 0.4     | 0.1     | 0.2                        |        |

|            | ADC AHB clock domain            | 5.5     | 4.7     | 5.5                        |        |

|            | CRC                             | 0.4     | 0.2     | 0.3                        |        |

|            | DMA1                            | 1.4     | 1.3     | 1.4                        |        |

|            | DMA2                            | 1.5     | 1.3     | 1.4                        |        |

|            | FLASH                           | 6.2     | 5.2     | 5.8                        |        |

|            | FMC                             | 8.9     | 7.5     | 8.4                        |        |

|            | GPIOA <sup>(2)</sup>            | 4.8     | 3.8     | 4.4                        |        |

|            | GPIOB <sup>(2)</sup>            | 4.8     | 4.0     | 4.6                        |        |

|            | GPIOC <sup>(2)</sup>            | 4.5     | 3.8     | 4.3                        |        |

| AHB        | GPIOD <sup>(2)</sup>            | 4.6     | 3.9     | 4.4                        | µA/MHz |

| 7          | GPIOE <sup>(2)</sup>            | 5.2     | 4.5     | 4.9                        | h      |

|            | GPIOF <sup>(2)</sup>            | 5.9     | 4.9     | 5.7                        |        |

|            | GPIOG <sup>(2)</sup>            | 4.3     | 3.8     | 4.2                        |        |

|            | GPIOH <sup>(2)</sup>            | 0.7     | 0.6     | 0.8                        |        |

|            | OTG_FS independent clock domain | 23.2    | NA      | NA                         |        |

|            | OTG_FS AHB clock domain         | 16.4    | NA      | NA                         |        |

|            | QUADSPI                         | 7.8     | 6.7     | 7.3                        |        |

|            | RNG independent clock domain    | 2.2     | NA      | NA                         |        |

|            | RNG AHB clock domain            | 0.6     | NA      | NA                         |        |

|            | SRAM1                           | 0.9     | 0.8     | 0.9                        |        |

#### Table 40. Peripheral current consumption

| Symbol                 | Parameter                      | Conditions              | Min    | Тур | Max | Unit  |  |

|------------------------|--------------------------------|-------------------------|--------|-----|-----|-------|--|

| £                      | PLL input clock <sup>(2)</sup> | -                       | 4      | -   | 16  | MHz   |  |

| f <sub>PLL_IN</sub>    | PLL input clock duty cycle     | -                       | 45     | -   | 55  | %     |  |

| £                      | DLL multiplier output clock D  | Voltage scaling Range 1 | 2.0645 | -   | 80  | MHz   |  |

| f <sub>PLL_P_OUT</sub> | PLL multiplier output clock P  | Voltage scaling Range 2 | 2.0645 | -   | 26  | IVIHZ |  |

| £                      | DLL multiplier output clock O  | Voltage scaling Range 1 | 8      | -   | 80  | MHz   |  |

| f <sub>PLL_Q_OUT</sub> | PLL multiplier output clock Q  | Voltage scaling Range 2 | 8      | -   | 26  |       |  |

| £                      | DLL multiplier output clock D  | Voltage scaling Range 1 | 8      | -   | 80  | MHz   |  |

| f <sub>PLL_R_OUT</sub> | PLL multiplier output clock R  | Voltage scaling Range 2 | 8      | -   | 26  |       |  |

| £                      |                                | Voltage scaling Range 1 | 64     | -   | 344 | MHz   |  |

| f <sub>VCO_OUT</sub>   | PLL VCO output                 | Voltage scaling Range 2 | 64     | -   | 128 |       |  |

| t <sub>LOCK</sub>      | PLL lock time                  | -                       | -      | 15  | 40  | μs    |  |

| littor                 | RMS cycle-to-cycle jitter      | System clock 20 MHz     | -      | 40  | -   | 100   |  |

| Jitter                 | RMS period jitter              | - System clock 80 MHz   | -      | 30  | -   | ±ps   |  |

|                        |                                | VCO freq = 64 MHz       | -      | 150 | 200 |       |  |

|                        | PLL power consumption on       | VCO freq = 96 MHz       | -      | 200 | 260 | 1     |  |

| I <sub>DD</sub> (PLL)  | V <sub>DD</sub> <sup>(1)</sup> | VCO freq = 192 MHz      | -      | 300 | 380 | μA    |  |

|                        |                                | VCO freq = 344 MHz      | -      | 520 | 650 | 1     |  |

## Table 50. PLL, PLLSAI1, PLLSAI2 characteristics<sup>(1)</sup>

1. Guaranteed by design.

2. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between the 3 PLLs.

| Symbol           | Parameter                                                                    | Conditions                                                                                                                | Min | Тур | Max                    | Unit |

|------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------|------|

|                  |                                                                              | $V_{IN} \le Max(V_{DDXXX})^{(4)}$                                                                                         | -   | -   | ±100                   |      |

|                  | FT_xx input leakage current <sup>(3)</sup>                                   | $\begin{array}{l} Max(V_{DDXXX}) \leq V_{IN} \leq \\ Max(V_{DDXXX}) + 1 \ V^{(4)(5)} \end{array}$                         | -   | -   | 650 <sup>(3)(6)</sup>  |      |

|                  |                                                                              | $\begin{array}{l} {\sf Max}({\sf V}_{{\sf DDXXX}})\text{+}1~{\sf V} < \\ {\sf VIN} \leq 5.5~{\sf V}^{(3)(5)} \end{array}$ | -   | -   | 200 <sup>(6)</sup>     |      |

|                  |                                                                              | $V_{IN} \le Max(V_{DDXXX})^{(4)}$                                                                                         | -   | -   | ±150                   |      |

|                  | FT_lu, FT_u and<br>PC3 IO                                                    | $\begin{array}{l} Max(V_{DDXXX}) \leq V_{IN} \leq \\ Max(V_{DDXXX}) + 1 \ V^{(4)} \end{array}$                            | -   | -   | 2500 <sup>(3)(7)</sup> |      |

| l <sub>lkg</sub> |                                                                              | $Max(V_{DDXXX})+1 V < VIN \le 5.5 V^{(4)(5)(7)}$                                                                          | -   | -   | 250 <sup>(7)</sup>     | nA   |

|                  | TT xx input leakage                                                          | $V_{IN} \le Max(V_{DDXXX})^{(6)}$                                                                                         | -   | -   | ±150                   |      |

|                  | current                                                                      | Max(V <sub>DDXXX</sub> ) ≤ V <sub>IN</sub> < 3.6 V <sup>(6)</sup>                                                         | -   | -   | 2000 <sup>(3)</sup>    |      |

|                  | OPAMPx_VINM<br>(x=1,2) dedicated<br>input leakage current<br>(UFBGA132 only) | T <sub>J</sub> = 75 °C                                                                                                    | -   | -   | 1                      |      |

| R <sub>PU</sub>  | Weak pull-up<br>equivalent resistor <sup>(8)</sup>                           | V <sub>IN</sub> = V <sub>SS</sub>                                                                                         | 25  | 40  | 55                     | kΩ   |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(8)</sup>                            | V <sub>IN</sub> = V <sub>DDIOx</sub>                                                                                      | 25  | 40  | 55                     | kΩ   |

| CIO              | I/O pin capacitance                                                          | -                                                                                                                         | -   | 5   | -                      | pF   |

| Table 58. I/O static characteristics (co | ontinued) |

|------------------------------------------|-----------|

|------------------------------------------|-----------|

1. Refer to Figure 22: I/O input characteristics.

- 2. Tested in production.

- 3. Guaranteed by design.

- 4. Max(V<sub>DDXXX</sub>) is the maximum value of all the I/O supplies. Refer to Table: Legend/Abbreviations used in the pinout table.

- 5. All TX\_xx IO except FT\_lu, FT\_u and PC3.

- 6. This value represents the pad leakage of the IO itself. The total product pad leakage is provided by this formula:  $I_{Total\_Ileak\_max} = 10 \ \mu A + [number of IOs where V_{IN} is applied on the pad] \times I_{Ikg}(Max)$ .

- 7. To sustain a voltage higher than MIN( $V_{DD}$ ,  $V_{DDA}$ ,  $V_{DDIO2}$ ,  $V_{DDUSB}$ ,  $V_{LCD}$ ) +0.3 V, the internal Pull-up and Pull-Down resistors must be disabled.

- Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

| Symbol                    | Parameter                                          | Conditions                                        | Min     | Тур                                      | Max      | Unit               |  |  |  |

|---------------------------|----------------------------------------------------|---------------------------------------------------|---------|------------------------------------------|----------|--------------------|--|--|--|

|                           | Trigger conversion                                 | CKMODE = 00                                       | 2.5     | 3                                        | 3.5      |                    |  |  |  |

| +                         | Trigger conversion<br>latency Injected channels    | CKMODE = 01                                       | -       | -                                        | 3.0      | 1 /f               |  |  |  |

| t <sub>LATRINJ</sub>      | aborting a regular conversion                      | CKMODE = 10                                       | -       | -                                        | 3.25     | 1/f <sub>ADC</sub> |  |  |  |

|                           |                                                    | CKMODE = 11                                       | -       | -                                        | 3.125    |                    |  |  |  |

| +                         |                                                    | f <sub>ADC</sub> = 80 MHz                         | 0.03125 | -                                        | 8.00625  | μs                 |  |  |  |

| t <sub>s</sub>            | Sampling time                                      | -                                                 | 2.5     | -                                        | 640.5    | 1/f <sub>ADC</sub> |  |  |  |

| t <sub>ADCVREG_STUP</sub> | ADC voltage regulator start-up time                | -                                                 | -       | -                                        | 20       | μs                 |  |  |  |

|                           |                                                    | f <sub>ADC</sub> = 80 MHz<br>Resolution = 12 bits | 0.1875  | -                                        | 8.1625   | μs                 |  |  |  |

| t <sub>CONV</sub>         | Total conversion time<br>(including sampling time) | Resolution = 12 bits                              | success | 12.5 cycle<br>sive appro:<br>= 15 to 653 | ximation | 1/f <sub>ADC</sub> |  |  |  |

|                           |                                                    | fs = 5 Msps                                       | -       | 730                                      | 830      |                    |  |  |  |

| I <sub>DDA</sub> (ADC)    | ADC consumption from the V <sub>DDA</sub> supply   | fs = 1 Msps                                       | -       | 160                                      | 220      | μA                 |  |  |  |

|                           |                                                    | fs = 10 ksps                                      | -       | 16                                       | 50       |                    |  |  |  |

|                           | ADC consumption from                               | fs = 5 Msps                                       | -       | 130                                      | 160      |                    |  |  |  |

| I <sub>DDV_S</sub> (ADC)  | the V <sub>REF+</sub> single ended                 | fs = 1 Msps                                       | -       | 30                                       | 40       | μA                 |  |  |  |

|                           | mode                                               | fs = 10 ksps                                      | -       | 0.6                                      | 2        |                    |  |  |  |

|                           | ADC consumption from                               | fs = 5 Msps                                       | -       | 260                                      | 310      |                    |  |  |  |

| I <sub>DDV_D</sub> (ADC)  | the V <sub>REF+</sub> differential                 | fs = 1 Msps                                       | -       | 60                                       | 70       | μA                 |  |  |  |

|                           | mode                                               | fs = 10 ksps                                      | -       | 1.3                                      | 3        |                    |  |  |  |

Table 63. ADC characteristics<sup>(1) (2)</sup> (continued)

1. Guaranteed by design

2. The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V.

V<sub>REF+</sub> can be internally connected to V<sub>DDA</sub> and V<sub>REF-</sub> can be internally connected to V<sub>SSA</sub>, depending on the package. Refer to Section 4: Pinouts and pin description for further details.

|             | Table 60. ADC accuracy - minited test conditions 4. A A (continued)                                                                                                 |                           |              |                          |   |     |     |      |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------|--------------------------|---|-----|-----|------|

| Sym-<br>bol | Parameter                                                                                                                                                           | Conditions <sup>(4)</sup> |              |                          |   | Тур | Max | Unit |

| THD         | $\begin{array}{ll} \mbox{Total} & 26 \mbox{ MHz}, \\ \mbox{harmonic} & 1.65 \mbox{ V} \leq \mbox{V}_{\mbox{DDA}} \\ \mbox{distortion} & 3.6 \mbox{ V}, \end{array}$ | ADC clock frequency ≤     | Single       | Fast channel (max speed) | - | -71 | -69 |      |

|             |                                                                                                                                                                     | iotai ,                   | ended        | Slow channel (max speed) | - | -71 | -69 | dB   |

|             |                                                                                                                                                                     | 5511                      | Differential | Fast channel (max speed) | - | -73 | -72 | uр   |

|             |                                                                                                                                                                     | Voltage scaling Range 2   | Differential | Slow channel (max speed) | - | -73 | -72 |      |

| Table 68. ADC accuracy - limited test conditions $4^{(1)(2)(3)}$ |

|------------------------------------------------------------------|

|------------------------------------------------------------------|

1. Guaranteed by design.

2. ADC DC accuracy values are measured after internal calibration.

- 3. ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

- 4. The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4 V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V. No oversampling.

## 6.3.19 Voltage reference buffer characteristics

| Table 71. VREFBUF characteristics <sup>(1)</sup> |                                                                                                 |                                                                                       |                            |                          |       |                                         |         |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------|--------------------------|-------|-----------------------------------------|---------|

| Symbol                                           | Parameter                                                                                       | Conditio                                                                              | ons                        | Min                      | Тур   | Max                                     | Unit    |

|                                                  |                                                                                                 |                                                                                       | V <sub>RS</sub> = 0        | 2.4                      | -     | 3.6                                     |         |

|                                                  | Analog supply                                                                                   | Normal mode                                                                           | V <sub>RS</sub> = 1        | 2.8                      | -     | 3.6                                     | -       |

| V <sub>DDA</sub>                                 | voltage                                                                                         | $\mathbf{D}_{\mathbf{r}}$ and $\mathbf{d}_{\mathbf{r}}$ and $\mathbf{d}_{\mathbf{r}}$ | V <sub>RS</sub> = 0        | 1.65                     | -     | 2.4                                     |         |

|                                                  |                                                                                                 | Degraded mode <sup>(2)</sup>                                                          | V <sub>RS</sub> = 1        | 1.65                     | -     | 2.8                                     | V       |

|                                                  |                                                                                                 |                                                                                       | V <sub>RS</sub> = 0        | 2.046 <sup>(3)</sup>     | 2.048 | 2.049 <sup>(3)</sup>                    | V       |

| V <sub>REFBUF</sub> _                            | Voltage                                                                                         | Normal mode                                                                           | V <sub>RS</sub> = 1        | 2.498 <sup>(3)</sup>     | 2.5   | 2.502 <sup>(3)</sup>                    |         |

| OUT                                              | reference<br>output                                                                             | Degraded mode <sup>(2)</sup>                                                          | V <sub>RS</sub> = 0        | V <sub>DDA</sub> -150 mV | -     | V <sub>DDA</sub>                        | 1       |

|                                                  |                                                                                                 | Degraded mode <sup>(2)</sup>                                                          | V <sub>RS</sub> = 1        | V <sub>DDA</sub> -150 mV | -     | V <sub>DDA</sub>                        |         |

| TRIM                                             | Trim step resolution                                                                            | -                                                                                     | -                          | -                        | ±0.05 | ±0.1                                    | %       |

| CL                                               | Load capacitor                                                                                  | -                                                                                     | -                          | 0.5                      | 1     | 1.5                                     | μF      |

| esr                                              | Equivalent<br>Serial Resistor<br>of Cload                                                       | -                                                                                     | -                          | -                        | -     | 2                                       | Ω       |

| I <sub>load</sub>                                | Static load current                                                                             | -                                                                                     | -                          | -                        | -     | 4                                       | mA      |

| 1                                                | Line regulation                                                                                 | 281/51/5361/                                                                          | I <sub>load</sub> = 500 μA | -                        | 200   | 1000                                    | ppm/V   |

| I <sub>line_reg</sub>                            |                                                                                                 |                                                                                       | 2.0 V = VDDA = 3.0 V       | I <sub>load</sub> = 4 mA | -     | 100                                     | 500     |

| I <sub>load_reg</sub>                            | Load<br>regulation                                                                              | 500 µA ≤ I <sub>load</sub> ≤4 mA                                                      | Normal mode                | -                        | 50    | 500                                     | ppm/mA  |

|                                                  | Temperature                                                                                     | -40 °C < TJ < +125 °C                                                                 | 2                          | -                        | -     | T <sub>coeff</sub> _<br>vrefint +<br>50 | ppm/ °C |

| T <sub>Coeff</sub>                               | coefficient                                                                                     | 0 °C < TJ < +50 °C                                                                    |                            | -                        | -     | T <sub>coeff</sub> _<br>vrefint +<br>50 | ppin/ C |

| PSRR                                             | Power supply DC                                                                                 |                                                                                       |                            | 40                       | 60    | -                                       | dB      |

| 1 OKK                                            | rejection                                                                                       | 100 kHz                                                                               |                            | 25                       | 40    | -                                       |         |

|                                                  |                                                                                                 | CL = 0.5 μF<br>CL = 1.1 μF                                                            |                            | -                        | 300   | 350                                     | μs      |

| t <sub>START</sub>                               | Start-up time                                                                                   |                                                                                       |                            | -                        | 500   | 650                                     |         |

|                                                  |                                                                                                 | CL = 1.5 μF                                                                           |                            | -                        | 650   | 800                                     |         |

| I <sub>INRUSH</sub>                              | Control of<br>maximum DC<br>current drive<br>on VREFBUF_<br>OUT during<br>start-up phase<br>(4) | -                                                                                     | -                          | -                        | 8     | -                                       | mA      |

## Table 71. VREFBUF characteristics<sup>(1)</sup>

- 1. Guaranteed by design.

- 2. LCD enabled with 3 V internal step-up active, 1/8 duty, 1/4 bias, division ratio= 64, all pixels active, no LCD connected.

### 6.3.25 **DFSDM** characteristics

Unless otherwise specified, the parameters given in *Table 78* for DFSDM are derived from tests performed under the ambient temperature,  $f_{APB2}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 22: General operating conditions*.

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 x VDD

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (DFSDM\_CKINy, DFSDM\_DATINy, DFSDM\_CKOUT for DFSDM).

| Symbol                                         | Parameter                                                | Conditions                                                                                    | Min                                         | Тур                  | Мах                              | Unit |  |

|------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------|----------------------|----------------------------------|------|--|

| f <sub>DFSDMCLK</sub>                          | DFSDM clock                                              | -                                                                                             | -                                           | f <sub>sysclk</sub>  |                                  |      |  |

| f <sub>CKIN</sub><br>(1/T <sub>CKIN</sub> )    | Input clock<br>frequency                                 | SPI mode (SITP[1:0] = 01)                                                                     | -                                           | -                    | 20<br>(f <sub>DFSDMCLK</sub> /4) | MHz  |  |

| f <sub>скоит</sub>                             | Output clock<br>frequency                                | -                                                                                             | 20                                          |                      | MHz                              |      |  |

| DuCy <sub>CKOUT</sub>                          | Output clock<br>frequency<br>duty cycle                  | -                                                                                             | 45 50 55                                    |                      | %                                |      |  |

| t <sub>wh(CKIN)</sub><br>t <sub>wl(CKIN)</sub> | Input clock<br>high and low<br>time                      | SPI mode (SITP[1:0] = 01),<br>External clock mode<br>(SPICKSEL[1:0] = 0)                      | T <sub>CKIN</sub> /2-0.5                    | T <sub>CKIN</sub> /2 | /2 -                             |      |  |

| t <sub>su</sub>                                | Data input<br>setup time                                 | SPI mode (SITP[1:0]=01),<br>External clock mode<br>(SPICKSEL[1:0] = 0)                        | 0                                           | 0                    |                                  |      |  |

| t <sub>h</sub>                                 | Data input<br>hold time                                  | SPI mode (SITP[1:0]=01),<br>External clock mode<br>(SPICKSEL[1:0] = 0)                        | 2                                           |                      | -                                | ns   |  |

| T <sub>Manchester</sub>                        | Manchester<br>data period<br>(recovered<br>clock period) | Manchester mode (SITP[1:0]<br>= 10 or 11),<br>Internal clock mode<br>(SPICKSEL[1:0] $\neq$ 0) | (CKOUT<br>DIV+1) x<br>T <sub>DFSDMCLK</sub> |                      |                                  |      |  |

Table 78. DFSDM characteristics<sup>(1)</sup>

1. Data based on characterization results, not tested in production.

#### 6.3.27 Communication interfaces characteristics

### I<sup>2</sup>C interface characteristics

The I2C interface meets the timings requirements of the  $I^2$ C-bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+): with a bit rate up to 1 Mbit/s.

The I2C timings requirements are guaranteed by design when the I2C peripheral is properly configured (refer to RM0351 reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DDIOx}$  is disabled, but is still present. Only FT\_f I/O pins support Fm+ low level output current maximum requirement. Refer to Section 6.3.14: I/O port characteristics for the I2C I/Os characteristics.

All I2C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

| Symbol          | Parameter                                                              | Min               | Мах                | Unit |

|-----------------|------------------------------------------------------------------------|-------------------|--------------------|------|

| t <sub>AF</sub> | Maximum pulse width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |

#### Table 82. I2C analog filter characteristics<sup>(1)</sup>

1. Guaranteed by design.

2. Spikes with widths below  $t_{AF(min)}$  are filtered.

3. Spikes with widths above  $t_{AF(max)}$  are not filtered

| Symbol                                               | Parameter                                                       | Min                    | Мах | Unit |

|------------------------------------------------------|-----------------------------------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>                                  | FMC_CLK period                                                  | 2T <sub>HCLK</sub> -1  | -   |      |

| t <sub>d(CLKL-NExL)</sub>                            | FMC_CLK low to FMC_NEx low (x=02)                               | -                      | 2   |      |

| t <sub>d(CLKH-NExH)</sub>                            | FMC_CLK high to FMC_NEx high (x= 02)                            | T <sub>HCLK</sub> +0.5 | -   |      |

| t <sub>d(CLKL-NADVL)</sub>                           | FMC_CLK low to FMC_NADV low                                     | -                      | 2.5 |      |

| t <sub>d(CLKL-NADVH)</sub>                           | FMC_CLK low to FMC_NADV high                                    | 1                      | -   |      |

| t <sub>d(CLKL-AV)</sub>                              | FMC_CLK low to FMC_Ax valid (x=1625)                            | -                      | 3.5 |      |

| t <sub>d(CLKH-AIV)</sub>                             | FMC_CLK high to FMC_Ax invalid (x=1625)                         | T <sub>HCLK</sub>      | -   |      |

| t <sub>d(CLKL-NWEL)</sub>                            | FMC_CLK low to FMC_NWE low                                      | -                      | 2   |      |

| t <sub>d(CLKH-NWEH)</sub>                            | FMC_CLK high to FMC_NWE high                                    | T <sub>HCLK</sub> +1   | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>                             | FMC_CLK low to FMC_AD[15:0] valid                               | -                      | 4   |      |

| t <sub>d(CLKL-ADIV)</sub>                            | FMC_CLK low to FMC_AD[15:0] invalid                             | 0                      | -   |      |

| t <sub>d(CLKL-DATA)</sub>                            | FMC_A/D[15:0] valid data after FMC_CLK low                      | -                      | 5.5 |      |

| t <sub>d(CLKL-NBLL)</sub> FMC_CLK low to FMC_NBL low |                                                                 | -                      | 2.5 |      |

| t <sub>d(CLKH-NBLH)</sub>                            | t <sub>d(CLKH-NBLH)</sub> FMC_CLK high to FMC_NBL high          |                        | -   |      |

| t <sub>su(NWAIT-CLKH)</sub>                          | t <sub>su(NWAIT-CLKH)</sub> FMC_NWAIT valid before FMC_CLK high |                        | -   |      |

| t <sub>h(CLKH-NWAIT)</sub>                           | FMC_NWAIT valid after FMC_CLK high                              | 4                      | -   |      |

|                             |                | (1)(2)                         |

|-----------------------------|----------------|--------------------------------|

| Table 99. Synchronous multi | plexed PSRAM w | rite timings <sup>(1)(2)</sup> |

1. CL = 30 pF.

2. Guaranteed by characterization results.

eee

fff

\_

\_

\_

\_

0.0059

0.0020

| package mechanical data (continued) |     |             |     |     |                       |     |

|-------------------------------------|-----|-------------|-----|-----|-----------------------|-----|

| Cumb al                             |     | millimeters |     |     | inches <sup>(1)</sup> |     |

| Symbol                              | Min | Тур         | Мах | Min | Тур                   | Мах |

| е                                   | -   | 0.500       | -   | -   | 0.0197                | -   |

| Z                                   | -   | 0.750       | -   | -   | 0.0295                | -   |

| ddd                                 | -   | 0.080       | -   | -   | 0.0031                | -   |

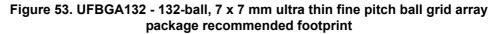

## Table 105. UFBGA132 - 132-ball. 7 x 7 mm ultra thin fine pitch ball grid array

Values in inches are converted from mm and rounded to 4 decimal digits. 1

0.150

0.050

\_

\_

\_

\_

#### Table 106. UFBGA132 recommended PCB design rules (0.5 mm pitch BGA)

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.5 mm                                                           |

| Dpad              | 0.280 mm                                                         |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.280 mm                                                         |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |

| Pad trace width   | 0.100 mm                                                         |

| Ball diameter     | 0.280 mm                                                         |