#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                              |

|----------------------------|-----------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                                  |

| Speed                      | 80MHz                                                                                               |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                                          |

| Number of I/O              | 114                                                                                                 |

| Program Memory Size        | 1MB (1M × 8)                                                                                        |

| Program Memory Type        | FLASH                                                                                               |

| EEPROM Size                | -                                                                                                   |

| RAM Size                   | 128K x 8                                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                                        |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                               |

| Oscillator Type            | Internal                                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                   |

| Mounting Type              | Surface Mount                                                                                       |

| Package / Case             | 144-LQFP                                                                                            |

| Supplier Device Package    | 144-LQFP (20x20)                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l476zgt6u                              |

|                            |                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Description

The STM32L476xx devices are the ultra-low-power microcontrollers based on the highperformance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core operating at a frequency of up to 80 MHz. The Cortex-M4 core features a Floating point unit (FPU) single precision which supports all ARM single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

The STM32L476xx devices embed high-speed memories (Flash memory up to 1 Mbyte, up to 128 Kbyte of SRAM), a flexible external memory controller (FSMC) for static memories (for devices with packages of 100 pins and more), a Quad SPI flash memories interface (available on all packages) and an extensive range of enhanced I/Os and peripherals connected to two APB buses, two AHB buses and a 32-bit multi-AHB bus matrix.

The STM32L476xx devices embed several protection mechanisms for embedded Flash memory and SRAM: readout protection, write protection, proprietary code readout protection and Firewall.

The devices offer up to three fast 12-bit ADCs (5 Msps), two comparators, two operational amplifiers, two DAC channels, an internal voltage reference buffer, a low-power RTC, two general-purpose 32-bit timer, two 16-bit PWM timers dedicated to motor control, seven general-purpose 16-bit timers, and two 16-bit low-power timers. The devices support four digital filters for external sigma delta modulators (DFSDM).

In addition, up to 24 capacitive sensing channels are available. The devices also embed an integrated LCD driver 8x40 or 4x44, with internal step-up converter.

They also feature standard and advanced communication interfaces.

- Three I2Cs

- Three SPIs

- Three USARTs, two UARTs and one Low-Power UART.

- Two SAIs (Serial Audio Interfaces)

- One SDMMC

- One CAN

- One USB OTG full-speed

- One SWPMI (Single Wire Protocol Master Interface)

The STM32L476xx operates in the -40 to +85  $^{\circ}$ C (+105  $^{\circ}$ C junction), -40 to +105  $^{\circ}$ C (+125  $^{\circ}$ C junction) and -40 to +125  $^{\circ}$ C (+130  $^{\circ}$ C junction) temperature ranges from a 1.71 to 3.6 V power supply. A comprehensive set of power-saving modes allows the design of low-power applications.

Some independent power supplies are supported: analog independent supply input for ADC, DAC, OPAMPs and comparators, 3.3 V dedicated supply input for USB and up to 14 I/Os can be supplied independently down to 1.08V. A VBAT input allows to backup the RTC and backup registers.

The STM32L476xx family offers six packages from 64-pin to 144-pin packages.

## 3.21 Liquid crystal display controller (LCD)

The LCD drives up to 8 common terminals and 44 segment terminals to drive up to 320 pixels.

- Internal step-up converter to guarantee functionality and contrast control irrespective of V<sub>DD</sub>. This converter can be deactivated, in which case the VLCD pin is used to provide the voltage to the LCD

- Supports static, 1/2, 1/3, 1/4 and 1/8 duty

- Supports static, 1/2, 1/3 and 1/4 bias

- Phase inversion to reduce power consumption and EMI

- Integrated voltage output buffers for higher LCD driving capability

- Up to 8 pixels can be programmed to blink

- Unneeded segments and common pins can be used as general I/O pins

- LCD RAM can be updated at any time owing to a double-buffer

- The LCD controller can operate in Stop mode

## 3.22 Digital filter for Sigma-Delta Modulators (DFSDM)

The device embeds one DFSDM with 4 digital filters modules and 8 external input serial channels (transceivers) or alternately 8 internal parallel inputs support.

The DFSDM peripheral is dedicated to interface the external  $\Sigma\Delta$  modulators to microcontroller and then to perform digital filtering of the received data streams (which represent analog value on  $\Sigma\Delta$  modulators inputs). DFSDM can also interface PDM (Pulse Density Modulation) microphones and perform PDM to PCM conversion and filtering in hardware. DFSDM features optional parallel data stream inputs from microcontrollers memory (through DMA/CPU transfers into DFSDM).

DFSDM transceivers support several serial interface formats (to support various  $\Sigma\Delta$  modulators). DFSDM digital filter modules perform digital processing according user selected filter parameters with up to 24-bit final ADC resolution.

The major features are:

- Combined Rx and Tx FIFO size of 1.25 KB with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 1 bidirectional control endpoint + 5 IN endpoints + 5 OUT endpoints

- 8 host channels with periodic OUT support

- HNP/SNP/IP inside (no need for any external resistor)

- Software configurable to OTG 1.3 and OTG 2.0 modes of operation

- OTG 2.0 Supports ADP (Attach detection Protocol)

- USB 2.0 LPM (Link Power Management) support

- Battery Charging Specification Revision 1.2 support

- Internal FS OTG PHY support

For OTG/Host modes, a power switch is needed in case bus-powered devices are connected.

## 3.35 Flexible static memory controller (FSMC)

The Flexible static memory controller (FSMC) includes two memory controllers:

- The NOR/PSRAM memory controller

- The NAND/memory controller

This memory controller is also named Flexible memory controller (FMC).

The main features of the FMC controller are the following:

- Interface with static-memory mapped devices including:

- Static random access memory (SRAM)

- NOR Flash memory/OneNAND Flash memory

- PSRAM (4 memory banks)

- NAND Flash memory with ECC hardware to check up to 8 Kbyte of data

- 8-,16- bit data bus width

- Independent Chip Select control for each memory bank

- Independent configuration for each memory bank

- Write FIFO

- The Maximum FMC\_CLK frequency for synchronous accesses is HCLK/2.

#### LCD parallel interface

The FMC can be configured to interface seamlessly with most graphic LCD controllers. It supports the Intel 8080 and Motorola 6800 modes, and is flexible enough to adapt to specific LCD interfaces. This LCD parallel interface capability makes it easy to build cost effective graphic applications using LCD modules with embedded controllers or high performance solutions using external controllers with dedicated acceleration.

|        |         | Pin N   | Numb    | er       |         |                                       |          | •             |       | Pin functions                                                                                                      |                      |

|--------|---------|---------|---------|----------|---------|---------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------------------------------------------|----------------------|

| LQFP64 | WLCSP72 | WLCSP81 | LQFP100 | UFBGA132 | LQFP144 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                | Additional functions |

| -      | -       | -       | 82      | В9       | 115     | PD1                                   | I/O      | FT            | -     | SPI2_SCK,<br>DFSDM_CKIN7,<br>CAN1_TX, FMC_D3,<br>EVENTOUT                                                          | -                    |

| 54     | A3      | A3      | 83      | C8       | 116     | PD2                                   | I/O      | FT_I          | -     | TIM3_ETR,<br>USART3_RTS_DE,<br>UART5_RX, TSC_SYNC,<br>LCD_COM7/LCD_SEG31/<br>LCD_SEG43,<br>SDMMC1_CMD,<br>EVENTOUT | -                    |

| -      | -       | -       | 84      | B8       | 117     | PD3                                   | I/O      | FT            | -     | SPI2_MISO,<br>DFSDM_DATIN0,<br>USART2_CTS, FMC_CLK,<br>EVENTOUT                                                    | -                    |

| -      | -       | E5      | 85      | В7       | 118     | PD4                                   | I/O      | FT            | -     | SPI2_MOSI,<br>DFSDM_CKIN0,<br>USART2_RTS_DE,<br>FMC_NOE, EVENTOUT                                                  | -                    |

| -      | -       | D4      | 86      | A6       | 119     | PD5                                   | I/O      | FT            | -     | USART2_TX, FMC_NWE,<br>EVENTOUT                                                                                    | -                    |

| -      | -       | -       | -       | -        | 120     | VSS                                   | S        | -             | -     | -                                                                                                                  | -                    |

| -      | -       | E4      | -       | -        | 121     | VDD                                   | S        | -             | -     | -                                                                                                                  | -                    |

| -      | -       | D5      | 87      | B6       | 122     | PD6                                   | I/O      | FT            | -     | DFSDM_DATIN1,<br>USART2_RX,<br>FMC_NWAIT, SAI1_SD_A,<br>EVENTOUT                                                   | -                    |

| -      | -       | D6      | 88      | A5       | 123     | PD7                                   | I/O      | FT            | -     | DFSDM_CKIN1,<br>USART2_CK, FMC_NE1,<br>EVENTOUT                                                                    | -                    |

| -      | A4      | A4      | -       | D9       | 124     | PG9                                   | I/O      | FT_s          | -     | SPI3_SCK, USART1_TX,<br>FMC_NCE3/FMC_NE2,<br>SAI2_SCK_A,<br>TIM15_CH1N, EVENTOUT                                   | -                    |

| -      | B4      | B4      | -       | D8       | 125     | PG10                                  | I/O      | FT_s          | -     | LPTIM1_IN1, SPI3_MISO,<br>USART1_RX, FMC_NE3,<br>SAI2_FS_A, TIM15_CH1,<br>EVENTOUT                                 | -                    |

| -      | C4      | C4      | -       | G3       | 126     | PG11                                  | I/O      | FT_s          | -     | LPTIM1_IN2, SPI3_MOSI,<br>USART1_CTS,<br>SAI2_MCLK_A,<br>TIM15_CH2, EVENTOUT                                       | -                    |

| Table 15. STM32L476xxSTM32L476xx pin definitions (continued) |

|--------------------------------------------------------------|

|--------------------------------------------------------------|

|     |      |      |                             |            | AF8             | AF9 | AF10                                    | AF11            | AF12                                    | AF13    | AF14 | AF15 |

|-----|------|------|-----------------------------|------------|-----------------|-----|-----------------------------------------|-----------------|-----------------------------------------|---------|------|------|

|     |      |      | UART4,<br>UART5,<br>LPUART1 | CAN1, TSC  | OTG_FS, QUADSPI | LCD | SDMMC1, COMP1,<br>COMP2, FMC,<br>SWPMI1 | SAI1, SAI2      | TIM2, TIM15,<br>TIM16, TIM17,<br>LPTIM2 | EVENTOL |      |      |

|     |      | PG0  | -                           | TSC_G8_IO3 | -               | -   | FMC_A10                                 | -               | -                                       | EVENTOL |      |      |

|     |      | PG1  | -                           | TSC_G8_IO4 | -               | -   | FMC_A11                                 | -               | -                                       | EVENTOL |      |      |

|     |      | PG2  | -                           | -          | -               | -   | FMC_A12                                 | SAI2_SCK_B      | -                                       | EVENTO  |      |      |

|     |      | PG3  | -                           | -          | -               | -   | FMC_A13                                 | SAI2_FS_B       | -                                       | EVENTO  |      |      |

|     |      | PG4  | -                           | -          | -               | -   | FMC_A14                                 | SAI2_MCLK_<br>B | -                                       | EVENTO  |      |      |

|     |      | PG5  | LPUART1_<br>CTS             | -          | -               | -   | FMC_A15                                 | SAI2_SD_B       | -                                       | EVENTO  |      |      |

|     |      | PG6  | LPUART1_<br>RTS_DE          | -          | -               | -   | -                                       | -               | -                                       | EVENTO  |      |      |

|     |      | PG7  | LPUART1_TX                  | -          | -               | -   | FMC_INT3                                | -               | -                                       | EVENTO  |      |      |

| Poi | rt G | PG8  | LPUART1_<br>RX              | -          | -               | -   | -                                       | -               | -                                       | EVENTO  |      |      |

|     |      | PG9  | -                           | -          | -               | -   | FMC_NCE3/<br>FMC_NE2                    | SAI2_SCK_A      | TIM15_CH1N                              | EVENTO  |      |      |

|     |      | PG10 | -                           | -          | -               | -   | FMC_NE3                                 | SAI2_FS_A       | TIM15_CH1                               | EVENTO  |      |      |

|     |      | PG11 | -                           | -          | -               | -   | -                                       | SAI2_MCLK_<br>A | TIM15_CH2                               | EVENTO  |      |      |

|     |      | PG12 | -                           | -          | -               | -   | FMC_NE4                                 | SAI2_SD_A       | -                                       | EVENTO  |      |      |

|     |      | PG13 | -                           | -          | -               | -   | FMC_A24                                 | -               | -                                       | EVENTO  |      |      |

|     |      | PG14 | -                           | -          | -               | -   | FMC_A25                                 | -               | -                                       | EVENTO  |      |      |

|     |      | PG15 | -                           | -          | -               | -   | -                                       | -               | -                                       | EVENTO  |      |      |

Pinouts and pin description

STM32L476xx

- 1. Guaranteed by design.

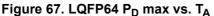

- 2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

- 3. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Figure 19. Typical application with a 32.768 kHz crystal

*Note:* An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

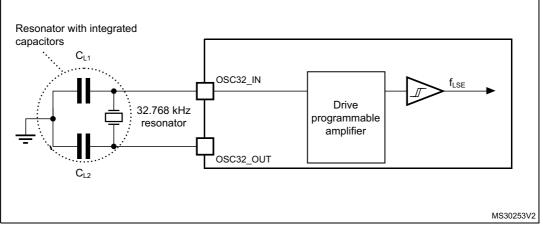

## 6.3.14 I/O port characteristics

### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 58* are derived from tests performed under the conditions summarized in *Table 22: General operating conditions*. All I/Os are designed as CMOS- and TTL-compliant (except BOOT0).

| Symbol                          | Parameter                                         | Conditions                            | Min                                          | Тур | Max                                          | Unit |

|---------------------------------|---------------------------------------------------|---------------------------------------|----------------------------------------------|-----|----------------------------------------------|------|

|                                 | I/O input low level<br>voltage except<br>BOOT0    | 1.62 V <v<sub>DDIOx&lt;3.6 V</v<sub>  | -                                            | -   | 0.3xV <sub>DDIOx</sub> <sup>(2)</sup>        |      |

| V <sub>IL</sub> (1)             | I/O input low level<br>voltage except<br>BOOT0    | 1.62 V <v<sub>DDIOx&lt;3.6 V</v<sub>  | -                                            | -   | 0.39xV <sub>DDIOx</sub> -0.06 <sup>(3)</sup> | V    |

|                                 | I/O input low level<br>voltage except<br>BOOT0    | 1.08 V <v<sub>DDIOx&lt;1.62 V</v<sub> | -                                            | -   | 0.43xV <sub>DDIOx</sub> -0.1 <sup>(3)</sup>  |      |

|                                 | BOOT0 I/O input low<br>level voltage              |                                       |                                              | -   | 0.17xV <sub>DDIOx</sub> <sup>(3)</sup>       |      |

|                                 | I/O input high level<br>voltage except<br>BOOT0   | 1.62 V <v<sub>DDIOx&lt;3.6 V</v<sub>  | 0.7xV <sub>DDIOx</sub> <sup>(2)</sup>        | -   | -                                            |      |

| V <sub>IH</sub> <sup>(1)</sup>  | I/O input high level<br>voltage except<br>BOOT0   | 1.62 V <v<sub>DDIOx&lt;3.6 V</v<sub>  | 0.49xV <sub>DDIOX</sub> +0.26 <sup>(3)</sup> | -   | -                                            | V    |

|                                 | I/O input high level<br>voltage except<br>BOOT0   | 1.08 V <v<sub>DDIOx&lt;1.62 V</v<sub> | 0.61xV <sub>DDIOX</sub> +0.05 <sup>(3)</sup> | -   | -                                            |      |

|                                 | BOOT0 I/O input<br>high level voltage             | 1.62 V <v<sub>DDIOx&lt;3.6 V</v<sub>  | 0.77xV <sub>DDIOX</sub> <sup>(3)</sup>       | -   | -                                            |      |

| (2)                             | TT_xx, FT_xxx and<br>NRST I/O input<br>hysteresis | 1.62 V <v<sub>DDIOX&lt;3.6 V</v<sub>  | -                                            | 200 | -                                            |      |

| V <sub>hys</sub> <sup>(3)</sup> | FT_sx                                             | 1.08 V <v<sub>DDIOx&lt;1.62 V</v<sub> | -                                            | 150 | -                                            | mV   |

|                                 | BOOT0 I/O input<br>hysteresis                     | 1.62 V <v<sub>DDIOx&lt;3.6 V</v<sub>  | -                                            | 200 | -                                            |      |

Table 58. I/O static characteristics

| Symbol           | Parameter                                                                    | Conditions                                                                                                                | Min | Тур | Max                    | Unit |

|------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------|------|

|                  |                                                                              | $V_{IN} \le Max(V_{DDXXX})^{(4)}$                                                                                         | -   | -   | ±100                   |      |

|                  | FT_xx input leakage current <sup>(3)</sup>                                   | $\begin{array}{l} Max(V_{DDXXX}) \leq V_{IN} \leq \\ Max(V_{DDXXX}) + 1 \ V^{(4)(5)} \end{array}$                         | -   | -   | 650 <sup>(3)(6)</sup>  |      |

|                  |                                                                              | $\begin{array}{l} {\sf Max}({\sf V}_{{\sf DDXXX}})\text{+}1~{\sf V} < \\ {\sf VIN} \leq 5.5~{\sf V}^{(3)(5)} \end{array}$ | -   | -   | 200 <sup>(6)</sup>     |      |

|                  |                                                                              | $V_{IN} \le Max(V_{DDXXX})^{(4)}$                                                                                         | -   | -   | ±150                   |      |

|                  | FT_lu, FT_u and<br>PC3 IO                                                    | $\begin{array}{l} Max(V_{DDXXX}) \leq V_{IN} \leq \\ Max(V_{DDXXX}) + 1 \ V^{(4)} \end{array}$                            | -   | -   | 2500 <sup>(3)(7)</sup> |      |

| l <sub>lkg</sub> |                                                                              | $Max(V_{DDXXX})+1 V < VIN \le 5.5 V^{(4)(5)(7)}$                                                                          | -   | -   | 250 <sup>(7)</sup>     | nA   |

|                  | TT vy input leakage                                                          | $V_{IN} \le Max(V_{DDXXX})^{(6)}$                                                                                         | -   | -   | ±150                   |      |

|                  | TT_xx input leakage current                                                  | Max(V <sub>DDXXX</sub> ) ≤ V <sub>IN</sub> < 3.6 V <sup>(6)</sup>                                                         | -   | -   | 2000 <sup>(3)</sup>    |      |

|                  | OPAMPx_VINM<br>(x=1,2) dedicated<br>input leakage current<br>(UFBGA132 only) | T <sub>J</sub> = 75 °C                                                                                                    | -   | -   | 1                      |      |

| R <sub>PU</sub>  | Weak pull-up<br>equivalent resistor <sup>(8)</sup>                           | V <sub>IN</sub> = V <sub>SS</sub>                                                                                         | 25  | 40  | 55                     | kΩ   |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(8)</sup>                            | V <sub>IN</sub> = V <sub>DDIOx</sub>                                                                                      | 25  | 40  | 55                     | kΩ   |

| C <sub>IO</sub>  | I/O pin capacitance                                                          | -                                                                                                                         | -   | 5   | -                      | pF   |

| Table 58. I/O static characteristics (co | ontinued) |

|------------------------------------------|-----------|

|------------------------------------------|-----------|

1. Refer to Figure 22: I/O input characteristics.

- 2. Tested in production.

- 3. Guaranteed by design.

- 4. Max(V<sub>DDXXX</sub>) is the maximum value of all the I/O supplies. Refer to Table: Legend/Abbreviations used in the pinout table.

- 5. All TX\_xx IO except FT\_lu, FT\_u and PC3.

- 6. This value represents the pad leakage of the IO itself. The total product pad leakage is provided by this formula:  $I_{Total\_Ileak\_max} = 10 \ \mu A + [number of IOs where V_{IN} is applied on the pad] \times I_{Ikg}(Max)$ .

- 7. To sustain a voltage higher than MIN( $V_{DD}$ ,  $V_{DDA}$ ,  $V_{DDIO2}$ ,  $V_{DDUSB}$ ,  $V_{LCD}$ ) +0.3 V, the internal Pull-up and Pull-Down resistors must be disabled.

- Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This PMOS/NMOS contribution to the series resistance is minimal (~10% order).

1. Refer to Table 60: I/O AC characteristics.

## 6.3.15 NRST pin characteristics

The NRST pin input driver uses the CMOS technology. It is connected to a permanent pull-up resistor,  $\mathsf{R}_{\mathsf{PU}}.$

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 22: General operating conditions*.

| Symbol                 | Parameter                                          | Conditions                        | Min                                 | Тур | Мах                                 | Unit |

|------------------------|----------------------------------------------------|-----------------------------------|-------------------------------------|-----|-------------------------------------|------|

| V <sub>IL(NRST)</sub>  | NRST input low level voltage                       | -                                 | -                                   | -   | 0.3 <sub>x</sub> V <sub>DDIOx</sub> | V    |

| V <sub>IH(NRST)</sub>  | NRST input high level voltage                      | -                                 | 0.7 <sub>x</sub> V <sub>DDIOx</sub> | -   | -                                   | v    |

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage hysteresis            | -                                 | -                                   | 200 | -                                   | mV   |

| R <sub>PU</sub>        | Weak pull-up<br>equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                                  | 40  | 55                                  | kΩ   |

| V <sub>F(NRST)</sub>   | NRST input filtered<br>pulse                       | -                                 | -                                   | -   | 70                                  | ns   |

| V <sub>NF(NRST)</sub>  | NRST input not filtered pulse                      | 1.71 V ≤ V <sub>DD</sub> ≤ 3.6 V  | 350                                 | _   | -                                   | ns   |

Table 61. NRST pin characteristics<sup>(1)</sup>

1. Guaranteed by design.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

|             | Table 60. Abo accuracy - miniced test conditions 2 (continued) |                                            |                          |                          |     |      |     |    |  |  |  |

|-------------|----------------------------------------------------------------|--------------------------------------------|--------------------------|--------------------------|-----|------|-----|----|--|--|--|

| Sym-<br>bol | Parameter                                                      | C                                          | Min                      | Тур                      | Max | Unit |     |    |  |  |  |

|             |                                                                | ADC clock frequency ≤                      | ck frequency ≤   onligit | Fast channel (max speed) | -   | -74  | -65 |    |  |  |  |

| THD         | Total<br>harmonic                                              | 80 MHz,                                    |                          | Slow channel (max speed) | -   | -74  | -67 | dB |  |  |  |

|             | distortion                                                     | distortion Sampling rate $\leq 5.33$ Msps, | Differential             | Fast channel (max speed) | -   | -79  | -70 | uВ |  |  |  |

|             |                                                                | $2 V \leq V_{DDA}$                         | Dillerential             | Slow channel (max speed) | -   | -79  | -71 |    |  |  |  |

Table 66. ADC accuracy - limited test conditions  $2^{(1)(2)(3)}$  (continued)

1. Guaranteed by design.

2. ADC DC accuracy values are measured after internal calibration.

- 3. ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

- 4. The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4 V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V. No oversampling.

## 6.3.22 Temperature sensor characteristics

| Symbol                                        | Parameter                                                          | Min   | Тур  | Max   | Unit  |

|-----------------------------------------------|--------------------------------------------------------------------|-------|------|-------|-------|

| T <sub>L</sub> <sup>(1)</sup>                 | V <sub>TS</sub> linearity with temperature                         | -     | ±1   | ±2    | °C    |

| Avg_Slope <sup>(2)</sup>                      | Average slope                                                      | 2.3   | 2.5  | 2.7   | mV/°C |

| V <sub>30</sub>                               | Voltage at 30°C (±5 °C) <sup>(3)</sup>                             | 0.742 | 0.76 | 0.785 | V     |

| t <sub>START</sub><br>(TS_BUF) <sup>(1)</sup> | Sensor Buffer Start-up time in continuous mode <sup>(4)</sup>      | -     | 8    | 15    | μs    |

| t <sub>START</sub> <sup>(1)</sup>             | Start-up time when entering in continuous mode <sup>(4)</sup>      | -     | 70   | 120   | μs    |

| t <sub>S_temp</sub> <sup>(1)</sup>            | ADC sampling time when reading the temperature                     | 5     | -    | -     | μs    |

| I <sub>DD</sub> (TS) <sup>(1)</sup>           | Temperature sensor consumption from $V_{DD},$ when selected by ADC | -     | 4.7  | 7     | μA    |

| Table | 74. | TS | characteristics |

|-------|-----|----|-----------------|

| TUDIC |     |    | onuluotonotioo  |

1. Guaranteed by design.

2. Guaranteed by characterization results.

3. Measured at  $V_{DDA}$  = 3.0 V ±10 mV. The  $V_{30}$  ADC conversion result is stored in the TS\_CAL1 byte. Refer to *Table 8: Temperature sensor calibration values*.

4. Continuous mode means Run/Sleep modes, or temperature sensor enable in Low-power run/Low-power sleep modes.

## 6.3.23 V<sub>BAT</sub> monitoring characteristics

#### Table 75. V<sub>BAT</sub> monitoring characteristics

| Symbol                  | Parameter                               | Min | Тур | Max | Unit |

|-------------------------|-----------------------------------------|-----|-----|-----|------|

| R                       | Resistor bridge for V <sub>BAT</sub>    | -   | 39  | -   | kΩ   |

| Q                       | Ratio on V <sub>BAT</sub> measurement   | -   | 3   | -   | -    |

| Er <sup>(1)</sup>       | Error on Q                              | -10 | -   | 10  | %    |

| t <sub>S_vbat</sub> (1) | ADC sampling time when reading the VBAT | 12  | -   | -   | μs   |

1. Guaranteed by design.

#### Table 76. V<sub>BAT</sub> charging characteristics

| Symbol          | Parameter            | Conditions | Min | Тур | Мах | Unit |

|-----------------|----------------------|------------|-----|-----|-----|------|

| R <sub>BC</sub> | Battery              | VBRS = 0   | -   | 5   | -   |      |

|                 | charging<br>resistor | VBRS = 1   | -   | 1.5 | -   | kΩ   |

Г

Т

٦

Т

#### **SPI characteristics**

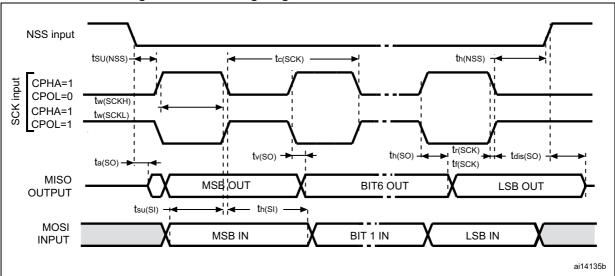

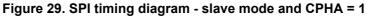

Unless otherwise specified, the parameters given in *Table 83* for SPI are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and supply voltage conditions summarized in *Table 22: General operating conditions*.

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI).

| Symbol                                       | Parameter                | Conditions                                                                              | Min                              | Тур               | Max                  | Unit |  |

|----------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------|----------------------------------|-------------------|----------------------|------|--|

|                                              |                          | Master mode receiver/full duplex<br>2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1    |                                  |                   | 24                   |      |  |

|                                              |                          | Master mode receiver/full duplex<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1   |                                  |                   | 13                   |      |  |

|                                              |                          | Master mode transmitter<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1            |                                  |                   | 40                   | MHz  |  |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency      | Slave mode receiver<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1                | -                                | -                 | 40                   |      |  |

|                                              |                          | Slave mode transmitter/full duplex<br>2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1  |                                  |                   | 26 <sup>(2)</sup>    |      |  |

|                                              |                          | Slave mode transmitter/full duplex<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1 |                                  |                   | 16 <sup>(2)</sup>    |      |  |

|                                              |                          | Voltage Range 2                                                                         |                                  |                   | 13                   |      |  |

|                                              |                          | 1.08 < V <sub>DDIO2</sub> < 1.32 V <sup>(3)</sup>                                       |                                  |                   | 8                    |      |  |

| t <sub>su(NSS)</sub>                         | NSS setup time           | Slave mode, SPI prescaler = 2                                                           | 4 <sub>x</sub> T <sub>PCLK</sub> | -                 | -                    | ns   |  |

| t <sub>h(NSS)</sub>                          | NSS hold time            | Slave mode, SPI prescaler = 2                                                           | 2 <sub>x</sub> T <sub>PCLK</sub> | -                 | -                    | ns   |  |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time    | Master mode                                                                             | T <sub>PCLK</sub> -2             | T <sub>PCLK</sub> | T <sub>PCLK</sub> +2 | ns   |  |

| t <sub>su(MI)</sub>                          | Data input setup time    | Master mode                                                                             | 3.5                              | -                 | -                    | ns   |  |

| t <sub>su(SI)</sub>                          | Data input setup time    | Slave mode                                                                              | 3                                | -                 | -                    | 115  |  |

| t <sub>h(MI)</sub>                           | Data input hold time     | Master mode                                                                             | 6.5                              | -                 | -                    | ns   |  |

| t <sub>h(SI)</sub>                           |                          | Slave mode                                                                              | 3                                | -                 | -                    | 115  |  |

| t <sub>a(SO)</sub>                           | Data output access time  | Slave mode                                                                              | 9                                | -                 | 36                   | ns   |  |

| t <sub>dis(SO)</sub>                         | Data output disable time | Slave mode                                                                              | 9                                | -                 | 16                   | ns   |  |

| Table | 83. | SPI | characteristics <sup>(</sup> | (1) | ) |

|-------|-----|-----|------------------------------|-----|---|

|-------|-----|-----|------------------------------|-----|---|

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

#### Figure 30. SPI timing diagram - master mode

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

DocID025976 Rev 4

## **Quad SPI characteristics**

Unless otherwise specified, the parameters given in *Table 84* and *Table 85* for Quad SPI are derived from tests performed under the ambient temperature,  $f_{AHB}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 22: General operating conditions*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 15 or 20 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics.

| Symbol              | Parameter                | Conditions                                                                   | Min                    | Тур | Max                    | Unit |  |

|---------------------|--------------------------|------------------------------------------------------------------------------|------------------------|-----|------------------------|------|--|

|                     |                          | 1.71 < V <sub>DD</sub> < 3.6 V, C <sub>LOAD</sub> = 20 pF<br>Voltage Range 1 | -                      | -   | 40                     |      |  |

| F <sub>CK</sub>     | Quad SPI clock frequency | 1.71 < V <sub>DD</sub> < 3.6 V, C <sub>LOAD</sub> = 15 pF<br>Voltage Range 1 | -                      | -   | 48                     | MHz  |  |

| 1/t <sub>(CK)</sub> | Quad SFT Clock frequency | $2.7 < V_{DD} < 3.6 V$ , $C_{LOAD} = 15 pF$<br>Voltage Range 1               | -                      | -   | 60                     |      |  |

|                     |                          | 1.71 < V <sub>DD</sub> < 3.6 V C <sub>LOAD</sub> = 20 pF<br>Voltage Range 2  | -                      | -   | 26                     |      |  |

| t <sub>w(CKH)</sub> | Quad SPI clock high and  | f <sub>AHBCLK</sub> = 48 MHz, presc=0                                        | t <sub>(CK)</sub> /2-2 | -   | t <sub>(CK)</sub> /2   |      |  |

| t <sub>w(CKL)</sub> | low time                 | AHBCLK- 40 Militz, presc-0                                                   | t <sub>(СК)</sub> /2   | -   | t <sub>(CK)</sub> /2+2 |      |  |

| t                   | Data input setup time    | Voltage Range 1                                                              | 4                      | -   | -                      | ]    |  |

| t <sub>s(IN)</sub>  |                          | Voltage Range 2                                                              | 3.5                    | -   | -                      |      |  |

| +                   | Data input hold time     | Voltage Range 1                                                              | 5.5                    | -   | -                      | ne   |  |

| t <sub>h(IN)</sub>  |                          | Voltage Range 2                                                              | 6.5                    | -   | -                      | ns   |  |

| +                   |                          | Voltage Range 1                                                              | -                      | 2.5 | 5                      |      |  |

| t <sub>v(OUT)</sub> | Data output valid time   | Voltage Range 2                                                              | -                      | 3   | 5                      |      |  |

| +                   | Data output hold time    | Voltage Range 1                                                              | 1.5                    | -   | -                      |      |  |

| t <sub>h(OUT)</sub> | Data output hold time    | Voltage Range 2                                                              | 2                      | -   | -                      |      |  |

1. Guaranteed by characterization results.

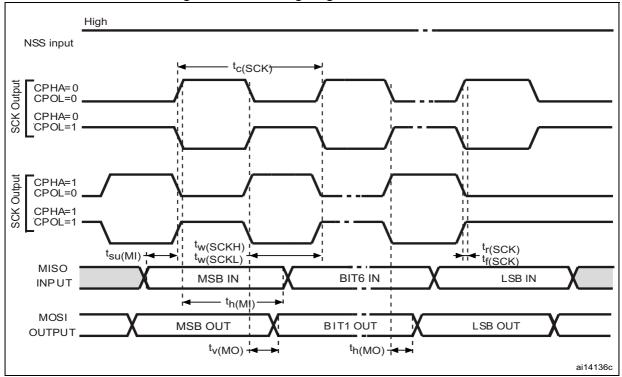

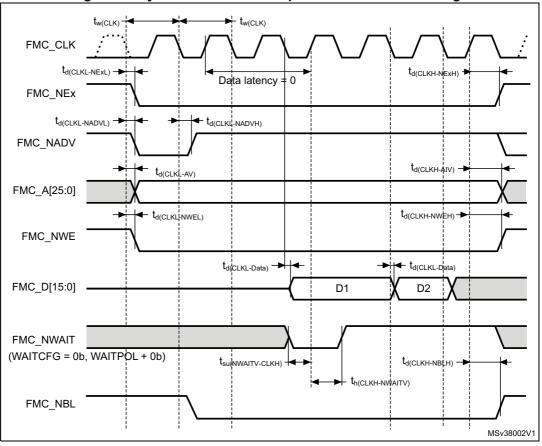

### 6.3.28 FSMC characteristics

Unless otherwise specified, the parameters given in *Table 90* to *Table 103* for the FMC interface are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 22*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output

characteristics.

#### Asynchronous waveforms and timings

*Figure 37* through *Figure 40* represent asynchronous waveforms and *Table 90* through *Table 97* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- AddressSetupTime = 0x1

- AddressHoldTime = 0x1

- DataSetupTime = 0x1 (except for asynchronous NWAIT mode, DataSetupTime = 0x5)

- BusTurnAroundDuration = 0x0

In all timing tables, the THCLK is the HCLK clock period.

Figure 37. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms

- 1. CL = 30 pF.

- 2. Guaranteed by characterization results.

#### Figure 44. Synchronous non-multiplexed PSRAM write timings

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|--------|--------|-----------------------|--------|--------|--|

|        | Min         | Тур    | Мах    | Min                   | Тур    | Max    |  |

| D3     | -           | 12.000 | -      | -                     | 0.4724 | -      |  |

| Е      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| E1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| E3     | -           | 12.000 | -      | -                     | 0.4724 | -      |  |

| е      | -           | 0.500  | -      | -                     | 0.0197 | -      |  |

| L      | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -           | 1.000  | -      | -                     | 0.0394 | -      |  |

| k      | 0.0°        | 3.5°   | 7.0°   | 0.0°                  | 3.5°   | 7.0°   |  |

| ccc    | -           | -      | 0.080  | -                     | -      | 0.0031 |  |

# Table 107. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

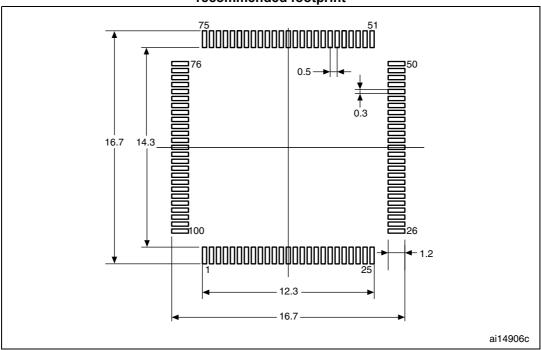

# Figure 56. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

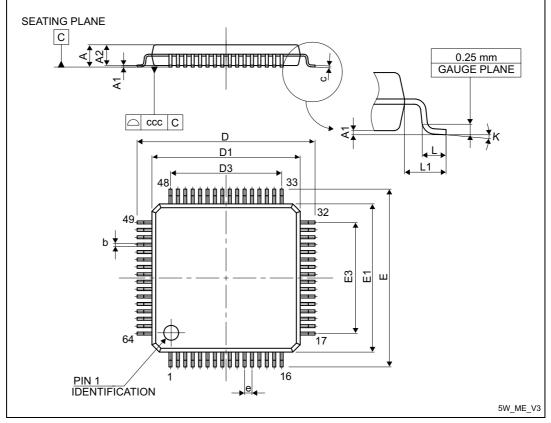

# 7.6 LQFP64 package information

Figure 64. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Table 112. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat |

|--------------------------------------------------------------|

| package mechanical data                                      |

| Symbol | millimeters |        |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|--------|-------|-----------------------|--------|--------|--|

|        | Min         | Тур    | Мах   | Min                   | Тур    | Мах    |  |

| А      | -           | -      | 1.600 | -                     | -      | 0.0630 |  |

| A1     | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |  |

| D      | -           | 12.000 | -     | -                     | 0.4724 | -      |  |

| D1     | -           | 10.000 | -     | -                     | 0.3937 | -      |  |

| D3     | -           | 7.500  | -     | -                     | 0.2953 | -      |  |

| E      | -           | 12.000 | -     | -                     | 0.4724 | -      |  |

| E1     | -           | 10.000 | -     | -                     | 0.3937 | -      |  |

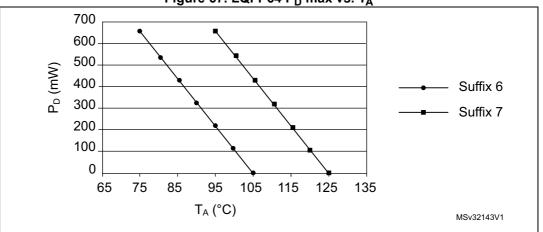

Using the values obtained in *Table 113*  $T_{Jmax}$  is calculated as follows:

- For LQFP64, 45 °C/W

- T<sub>Jmax</sub> = 100 °C + (45 °C/W × 134 mW) = 100 °C + 6.03 °C = 106.03 °C

This is above the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Section 8: Part numbering*) unless we reduce the power dissipation in order to be able to use suffix 6 parts.

Refer to *Figure 67* to select the required temperature range (suffix 6 or 7) according to your ambient temperature or power requirements.