Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 12                                                                     |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                        |

| Supplier Device Package    | 16-TSSOP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08sg4e2mtgr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The voltage measured on the internally pulled up  $\overline{\text{RESET}}$  pin will not be pulled to  $V_{DD}$ . The internal gates connected to this pin are pulled to  $V_{DD}$ . If the  $\overline{\text{RESET}}$  pin is required to drive to a  $V_{DD}$  level an external pullup should be used.

### NOTE

In EMC-sensitive applications, an external RC filter is recommended on the  $\overline{\text{RESET}}$ . See Figure 2-4 for an example.

# 2.2.4 Background / Mode Select (BKGD/MS)

During a power-on-reset (POR) or background debug force reset (see Section 5.7.2, "System Background Debug Force Reset Register (SBDFR)," for more information), the BKGD/MS pin functions as a mode select pin. Immediately after any reset, the pin functions as the background pin and can be used for background debug communication. The BKGD/MS pin contains an internal pullup device.

If nothing is connected to this pin, the MCU will enter normal operating mode at the rising edge of the internal reset after a POR or force BDC reset. If a debug system is connected to the 6-pin standard background debug header, it can hold BKGD/MS low during a POR or immediately after issuing a background debug force reset, which will force the MCU to active background mode.

The BKGD pin is used primarily for background debug controller (BDC) communications using a custom protocol that uses 16 clock cycles of the target MCU's BDC clock per bit time. The target MCU's BDC clock could be as fast as the maximum bus clock rate, so there must never be any significant capacitance connected to the BKGD/MS pin that could interfere with background serial communications.

Although the BKGD pin is a pseudo open-drain pin, the background debug communication protocol provides brief, actively driven, high speedup pulses to ensure fast rise times. Small capacitances from cables and the absolute value of the internal pullup device play almost no role in determining rise and fall times on the BKGD pin.

# 2.2.5 General-Purpose I/O and Peripheral Ports

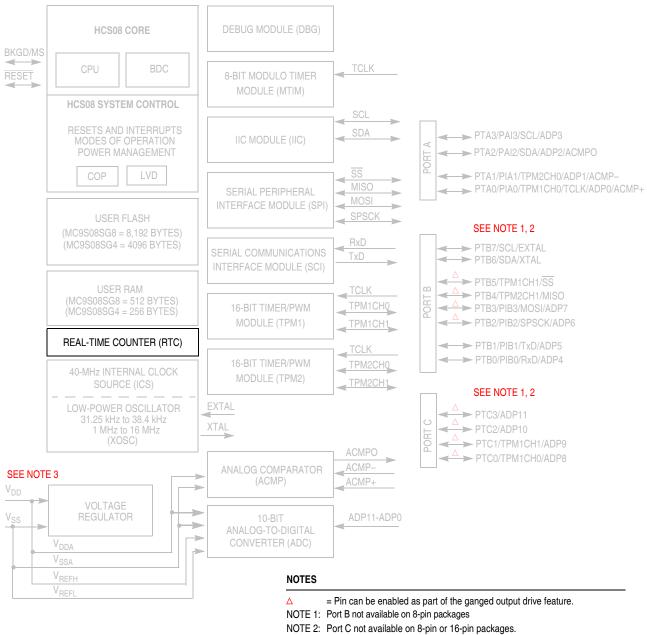

The MC9S08SG8 series of MCUs support up to 16 general-purpose I/O pins which are shared with on-chip peripheral functions (timers, serial I/O, ADC, etc.).

When a port pin is configured as a general-purpose output or a peripheral uses the port pin as an output, software can select one of two drive strengths and enable or disable slew rate control. When a port pin is configured as a general-purpose input or a peripheral uses the port pin as an input, software can enable a pull-up device. Immediately after reset, all of these pins are configured as high-impedance general-purpose inputs with internal pull-up devices disabled.

When an on-chip peripheral system is controlling a pin, data direction control bits still determine what is read from port data registers even though the peripheral module controls the pin direction by controlling the enable for the pin's output buffer. For information about controlling these pins as general-purpose I/O pins, see Chapter 6, "Parallel Input/Output Control."

Chapter 3 Modes of Operation

# Chapter 4 Memory

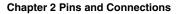

# 4.1 MC9S08SG8 Memory Map

As shown in Figure 4-1, on-chip memory in the MC9S08SG8 series of MCUs consists of RAM, FLASH program memory for nonvolatile data storage, and I/O and control/status registers. The registers are divided into three groups:

- Direct-page registers (0x0000 through 0x007F)

- High-page registers (0x1800 through 0x185F)

- Nonvolatile registers (0xFFB0 through 0xFFBF)

MC9S08SG8 MCU Series Data Sheet, Rev. 8

**Chapter 4 Memory**

| Address          | Register<br>Name | Bit 7  | 6   | 5   | 4    | 3   | 2   | 1   | Bit 0 |

|------------------|------------------|--------|-----|-----|------|-----|-----|-----|-------|

| 0x00 <b>69</b>   | TPM2C1VH         | Bit 15 | 14  | 13  | 12   | 11  | 10  | 9   | Bit 8 |

| 0x00 <b>6A</b>   | TPM2C1VL         | Bit 7  | 6   | 5   | 4    | 3   | 2   | 1   | Bit 0 |

| 0x00 <b>6B</b>   | Reserved         | —      |     | —   | —    |     |     | _   | —     |

| 0x00 <b>6C</b>   | RTCSC            | RTIF   | RTC | LKS | RTIE |     | RTC | CPS |       |

| 0x00 <b>6D</b>   | RTCCNT           |        |     |     | RTC  | CNT |     |     |       |

| 0x00 <b>6E</b>   | RTCMOD           | RTCMOD |     |     |      |     |     |     |       |

| 0x00 <b>6F -</b> | Reserved         | —      | —   | —   | —    | —   | —   | —   | —     |

| 0x00 <b>7F</b>   | 10001100         | —      | —   | —   | —    | —   | —   | —   | —     |

#### Table 4-2. Direct-Page Register Summary (Sheet 3 of 3)

```

Chapter 4 Memory

```

High-page registers, shown in Table 4-3, are accessed much less often than other I/O and control registers so they have been located outside the direct addressable memory space, starting at 0x1800.

| Address            | Register Name | Bit 7   | 6      | 5      | 4       | 3      | 2      | 1       | Bit 0   |

|--------------------|---------------|---------|--------|--------|---------|--------|--------|---------|---------|

| 0x1800             | SRS           | POR     | PIN    | COP    | ILOP    | ILAD   | 0      | LVD     | 0       |

| 0x1801             | SBDFR         | 0       | 0      | 0      | 0       | 0      | 0      | 0       | BDFR    |

| 0x1802             | SOPT1         | CO      | PT     | STOPE  | 0       | 0      | IICPS  | 0       | 0       |

| 0x1803             | SOPT2         | COPCLKS | COPW   | 0      | ACIC    | 0      | 0      | T1CH1PS | T1CH0PS |

| 0x1804 —<br>0x1805 | Reserved      | _       | _      |        | —       | _      |        | _       | _       |

| 0x1806             | SDIDH         | 1       | _      | _      | —       | ID11   | ID10   | ID9     | ID8     |

| 0x1807             | SDIDL         | ID7     | ID6    | ID5    | ID4     | ID3    | ID2    | ID1     | ID0     |

| 0x1808             | Reserved      |         |        | _      |         |        |        |         | —       |

| 0x1809             | SPMSC1        | LVWF    | LVWACK | LVWIE  | LVDRE   | LVDSE  | LVDE   | 0       | BGBE    |

| 0x180A             | SPMSC2        | 0       | 0      | LVDV   | LVWV    | PPDF   | PPDACK |         | PPDC    |

| 0x180B–<br>0x180F  | Reserved      | _       | _      | _      | —       | _      | _      | _       | _       |

| 0x1810             | DBGCAH        | Bit 15  | 14     | 13     | 12      | 11     | 10     | 9       | Bit 8   |

| 0x1811             | DBGCAL        | Bit 7   | 6      | 5      | 4       | 3      | 2      | 1       | Bit 0   |

| 0x1812             | DBGCBH        | Bit 15  | 14     | 13     | 12      | 11     | 10     | 9       | Bit 8   |

| 0x1813             | DBGCBL        | Bit 7   | 6      | 5      | 4       | 3      | 2      | 1       | Bit 0   |

| 0x1814             | DBGFH         | Bit 15  | 14     | 13     | 12      | 11     | 10     | 9       | Bit 8   |

| 0x1815             | DBGFL         | Bit 7   | 6      | 5      | 4       | 3      | 2      | 1       | Bit 0   |

| 0x1816             | DBGC          | DBGEN   | ARM    | TAG    | BRKEN   | RWA    | RWAEN  | RWB     | RWBEN   |

| 0x1817             | DBGT          | TRGSEL  | BEGIN  | 0      | 0       | TRG3   | TRG2   | TRG1    | TRG0    |

| 0x1818             | DBGS          | AF      | BF     | ARMF   | 0       | CNT3   | CNT2   | CNT1    | CNT0    |

| 0x1819–<br>0x181F  | Reserved      | _       | _      |        | _       | _      |        | _       | _       |

| 0x1820             | FCDIV         | DIVLD   | PRDIV8 |        |         | D      | IV     |         |         |

| 0x1821             | FOPT          | KEYEN   | FNORED | 0      | 0       | 0      | 0      | SE      | EC      |

| 0x1822             | Reserved      |         |        |        |         |        |        |         | —       |

| 0x1823             | FCNFG         | 0       | 0      | KEYACC | 0       | 0      | 0      | 0       | 0       |

| 0x1824             | FPROT         |         |        |        | FPS     |        |        |         | FPDIS   |

| 0x1825             | FSTAT         | FCBEF   | FCCF   | FPVIOL | FACCERR | 0      | FBLANK | 0       | 0       |

| 0x1826             | FCMD          | FCMD    |        |        |         |        |        |         |         |

| 0x1827–<br>0x183F  | Reserved      | _       | _      | _      | —       | _      | _      | _       | _       |

| 0x1840             | PTAPE         | 0       | 0      | —      | —       | PTAPE3 | PTAPE2 | PTAPE1  | PTAPE0  |

| 0x1841             | PTASE         | 0       | 0      | —      | —       | PTASE3 | PTASE2 | PTASE1  | PTASE0  |

| 0x1842             | PTADS         | 0       | 0      | —      | —       | PTADS3 | PTADS2 | PTADS1  | PTADS0  |

| 0x1843             | Reserved      |         |        | —      | —       | —      | —      | —       | —       |

| 0x1844             | PTASC         | 0       | 0      | 0      | 0       | PTAIF  | PTAACK | PTAIE   | PTAMOD  |

### Table 4-3. High-Page Register Summary (Sheet 1 of 2)

MC9S08SG8 MCU Series Data Sheet, Rev. 8

# 6.4.3 Pull-up/Pull-down Resistors

The pin interrupts can be configured to use an internal pull-up/pull-down resistor using the associated I/O port pull-up enable register. If an internal resistor is enabled, the PTxES register is used to select whether the resistor is a pull-up (PTxESn = 0) or a pull-down (PTxESn = 1).

# 6.4.4 Pin Interrupt Initialization

When a pin interrupt is first enabled, it is possible to get a false interrupt flag. To prevent a false interrupt request during pin interrupt initialization, the user should do the following:

- 1. Mask interrupts by clearing PTxIE in PTxSC.

- 2. Select the pin polarity by setting the appropriate PTxESn bits in PTxES.

- 3. If using internal pull-up/pull-down device, configure the associated pull enable bits in PTxPE.

- 4. Enable the interrupt pins by setting the appropriate PTxPEn bits in PTxPE.

- 5. Write to PTxACK in PTxSC to clear any false interrupts.

- 6. Set PTxIE in PTxSC to enable interrupts.

# 6.5 Pin Behavior in Stop Modes

Pin behavior following execution of a STOP instruction depends on the stop mode that is entered. An explanation of pin behavior for the various stop modes follows:

- Stop2 mode is a partial power-down mode, whereby I/O latches are maintained in their state as before the STOP instruction was executed. CPU register status and the state of I/O registers should be saved in RAM before the STOP instruction is executed to place the MCU in stop2 mode. Upon recovery from stop2 mode, before accessing any I/O, the user should examine the state of the PPDF bit in the SPMSC2 register. If the PPDF bit is 0, I/O must be initialized as if a power on reset had occurred. If the PPDF bit is 1, I/O data previously stored in RAM, before the STOP instruction was executed, peripherals may require being initialized and restored to their pre-stop condition. The user must then write a 1 to the PPDACK bit in the SPMSC2 register. Access to I/O is now permitted again in the user application program.

- In stop3 mode, all I/O is maintained because internal logic circuity stays powered up. Upon recovery, normal I/O function is available to the user.

# 6.6 Parallel I/O and Pin Control Registers

This section provides information about the registers associated with the parallel I/O ports. The data and data direction registers are located in page zero of the memory map. The pull up, slew rate, drive strength, and interrupt control registers are located in the high page section of the memory map.

Refer to tables in Chapter 4, "Memory," for the absolute address assignments for all parallel I/O and their pin control registers. This section refers to registers and control bits only by their names. A Freescale Semiconductor-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

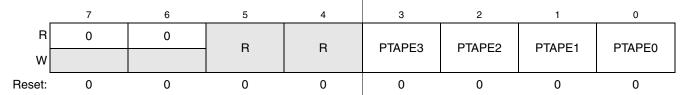

# 6.6.1.3 Port A Pull Enable Register (PTAPE)

Figure 6-5. Internal Pull Enable for Port A Register (PTAPE)

#### Table 6-4. PTAPE Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5:4<br>Reserved   | <b>Reserved Bits</b> — These bits are unused on this MCU, writes have no affect and could read as 1s or 0s.                                                                                                                                                                                                                                                                                                              |

| 3:0<br>PTAPE[3:0] | Internal Pull Enable for Port A Bits — Each of these control bits determines if the internal pull-up or pull-down device is enabled for the associated PTA pin. For port A pins that are configured as outputs, these bits have no effect and the internal pull devices are disabled.<br>0 Internal pull-up/pull-down device disabled for port A bit n.<br>1 Internal pull-up/pull-down device enabled for port A bit n. |

# 6.6.1.4 Port A Slew Rate Enable Register (PTASE)

| _      | 7 | 6 | 5  | 4 | 3      | 2      | 1      | 0      |

|--------|---|---|----|---|--------|--------|--------|--------|

| R      | 0 | 0 | в  | в | PTASE3 | PTASE2 | PTASE1 | PTASE0 |

| W      |   |   | 11 | n | TIADED | TIAOLZ | TIAGET | TIAGEO |

| Reset: | 0 | 0 | 0  | 0 | 0      | 0      | 0      | 0      |

ī

#### Figure 6-6. Slew Rate Enable for Port A Register (PTASE)

#### Table 6-5. PTASE Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5:4<br>Reserved   | <b>Reserved Bits</b> — These bits are unused on this MCU, writes have no affect and could read as 1s or 0s.                                                                                                                                                                                                                                                                   |

| 3:0<br>PTASE[3:0] | <ul> <li>Output Slew Rate Enable for Port A Bits — Each of these control bits determines if the output slew rate control is enabled for the associated PTA pin. For port A pins that are configured as inputs, these bits have no effect.</li> <li>Output slew rate control disabled for port A bit n.</li> <li>Output slew rate control enabled for port A bit n.</li> </ul> |

Chapter 6 Parallel Input/Output Control

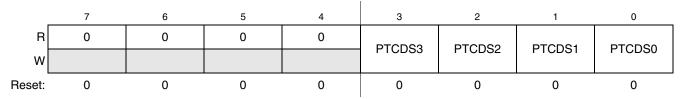

# 6.6.3.5 Port C Drive Strength Selection Register (PTCDS)

Figure 6-23. Drive Strength Selection for Port C Register (PTCDS)

#### Table 6-22. PTCDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>PTCDS[3:0] | <ul> <li>Output Drive Strength Selection for Port C Bits — Each of these control bits selects between low and high output drive for the associated PTC pin. For port C pins that are configured as inputs, these bits have no effect.</li> <li>0 Low output drive strength selected for port C bit n.</li> <li>1 High output drive strength selected for port C bit n.</li> </ul> |

# 6.6.3.6 Ganged Output Drive Control Register (GNGC)

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0     |

|--------|--------|--------|--------|--------|--------|--------|--------|-------|

| R<br>W | GNGPS7 | GNGPS6 | GNGPS5 | GNGPS4 | GNGPS3 | GNGPS2 | GNGPS1 | GNGEN |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0     |

Figure 6-24. Ganged Output Drive Control Register (GNGC)

#### Table 6-23. GNGC Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:1<br>GNGP[7:1] | <ul> <li>Ganged Output Pin Select Bits— These write-once control bits selects whether the associated pin (see Table 6-1 for pins available) is enabled for ganged output. When GNGEN = 1, all enabled ganged output pins will be controlled by the data, drive strength and slew rate settings for PTCO.</li> <li>0 Associated pin is not part of the ganged output drive.</li> <li>1 Associated pin is part of the ganged output drive. Requires GNGEN = 1.</li> </ul> |

| 0<br>GNGEN       | <ul> <li>Ganged Output Drive Enable Bit— This write-once control bit selects whether the ganged output drive feature is enabled.</li> <li>0 Ganged output drive disabled.</li> <li>1 Ganged output drive enabled. PTC0 forced to output regardless of the value of PTCDD0 in PTCDD.</li> </ul>                                                                                                                                                                          |

| Source<br>Form | Source Operation                                                     |     | Address<br>Mode<br>Opject Code |    | Cyc-by-Cyc<br>Details | Affect<br>on CCR |      |

|----------------|----------------------------------------------------------------------|-----|--------------------------------|----|-----------------------|------------------|------|

|                |                                                                      | PA  |                                | S  |                       | VH               | INZC |

| TXS            | Transfer Index Reg. to SP SP $\leftarrow$ (H:X) – 0x0001             | INH | 94                             | 2  | fp                    |                  |      |

| WAIT           | Enable Interrupts; Wait for Interrupt I bit $\leftarrow$ 0; Halt CPU | INH | 8 F                            | 2+ | fp                    |                  | 0    |

**Source Form:** Everything in the source forms columns, *except expressions in italic characters*, is literal information which must appear in the assembly source file exactly as shown. The initial 3- to 5-letter mnemonic and the characters (#, () and +) are always a literal characters.

*n* Any label or expression that evaluates to a single integer in the range 0-7.

*opr8i* Any label or expression that evaluates to an 8-bit immediate value.

opr16i Any label or expression that evaluates to a 16-bit immediate value.

opr8a Any label or expression that evaluates to an 8-bit direct-page address (0x00xx).

opr16a Any label or expression that evaluates to a 16-bit address.

oprx8 Any label or expression that evaluates to an unsigned 8-bit value, used for indexed addressing.

oprx16 Any label or expression that evaluates to a 16-bit value, used for indexed addressing.

rel Any label or expression that refers to an address that is within -128 to +127 locations from the start of the next instruction.

#### **Operation Symbols:**

| A | Accumulator |

|---|-------------|

|   |             |

- CCR Condition code register

- H Index register high byte

- M Memory location

- n Any bit

- opr Operand (one or two bytes)

- PC Program counter

- PCH Program counter high byte

- PCL Program counter low byte

- rel Relative program counter offset byte

- SP Stack pointer

- SPL Stack pointer low byte

- X Index register low byte

- & Logical AND

- Logical OR

- Logical EXCLUSIVE OR

- () Contents of

- + Add

- Subtract, Negation (two's complement)

- × Multiply

- ÷ Divide

- # Immediate value

- $\leftarrow \qquad \text{Loaded with} \qquad$

- : Concatenated with

#### CCR Bits:

- V Overflow bit

- H Half-carry bit

- I Interrupt mask

- N Negative bit

- Z Zero bit

- C Carry/borrow bit

#### Addressing Modes:

- DIR Direct addressing mode

- EXT Extended addressing mode

- IMM Immediate addressing mode

- INH Inherent addressing mode

- IX Indexed, no offset addressing mode

- IX1 Indexed, 8-bit offset addressing mode

- IX2 Indexed, 16-bit offset addressing mode

- IX+ Indexed, no offset, post increment addressing mode

- IX1+ Indexed, 8-bit offset, post increment addressing mode

- REL Relative addressing mode

- SP1 Stack pointer, 8-bit offset addressing mode

- SP2 Stack pointer 16-bit offset addressing mode

#### Cycle-by-Cycle Codes:

- f Free cycle. This indicates a cycle where the CPU does not require use of the system buses. An f cycle is always one cycle of the system bus clock and is always a read cycle.

- p Progryam fetch; read from next consecutive location in program memory

- r Read 8-bit operand

- s Push (write) one byte onto stack

- u Pop (read) one byte from stack

- v Read vector from 0xFFxx (high byte first)

- w Write 8-bit operand

#### CCR Effects:

- Þ Set or cleared

- Not affected

- U Undefined

#### Chapter 9 Analog-to-Digital Converter (S08ADCV1)

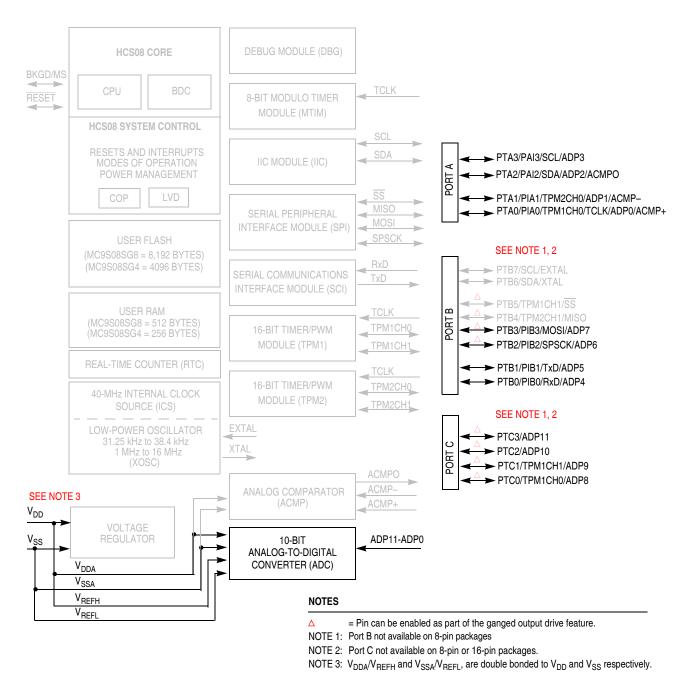

Figure 9-1. MC9S08SG8 Block Diagram with ADC Module Highlighted

# Chapter 11 Inter-Integrated Circuit (S08IICV2)

# 11.1 Introduction

The inter-integrated circuit (IIC) provides a method of communication between a number of devices. The interface is designed to operate up to 100 kbps with maximum bus loading and timing. The device is capable of operating at higher baud rates, up to a maximum of clock/20, with reduced bus loading. The maximum communication length and the number of devices that can be connected are limited by a maximum bus capacitance of 400 pF.

### NOTE

The SDA and SCL should not be driven above  $V_{DD}$ . These pins are pseudo open-drain containing a protection diode to  $V_{DD}$ .

# 11.1.1 Module Configuration

The IIC module pins, SDA and SCL can be repositioned under software control using IICPS in SOPT1 as as shown in Table 11-1. IICPS in SOPT1 selects which general-purpose I/O ports are associated with IIC operation.

| IICPS in SOPT1 | Port Pin for SDA | Port Pin for SCL |  |  |

|----------------|------------------|------------------|--|--|

| 0 (default)    | PTA2             | PTA3             |  |  |

| 1              | PTB6             | PTB7             |  |  |

#### Table 11-1. IIC Position Options

Figure 11-1 shows the MC9S08SG8 block diagram with the IIC module highlighted.

# 12.3 Register Definition

| Name     |   | 7     | 6    | 5    | 4    | 3      | 2 | 1 | 0 |  |

|----------|---|-------|------|------|------|--------|---|---|---|--|

| MTIMSC   | R | TOF   | TOIE | 0    | TSTP | 0      | 0 | 0 | 0 |  |

| MT1M30   | W |       |      | TRST |      |        |   |   |   |  |

| MTIMCLK  | R | 0     | 0    | CLKS |      | PS     |   |   |   |  |

| WITHWOLK | W |       |      |      |      | го<br> |   |   |   |  |

| MTIMCNT  | R | COUNT |      |      |      |        |   |   |   |  |

| WITHWONT | W |       |      |      |      |        |   |   |   |  |

| MTIMMOD  | R | MOD   |      |      |      |        |   |   |   |  |

|          | W |       |      |      |      |        |   |   |   |  |

Figure 12-3 is a summary of MTIM registers.

Figure 12-3. MTIM Register Summary

Each MTIM includes four registers:

- An 8-bit status and control register

- An 8-bit clock configuration register

- An 8-bit counter register

- An 8-bit modulo register

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all MTIM registers. This section refers to registers and control bits only by their names and relative address offsets.

Some MCUs may have more than one MTIM, so register names include placeholder characters to identify which MTIM is being referenced.

# Chapter 13 Real-Time Counter (S08RTCV1)

NOTE 3: V<sub>DDA</sub>/V<sub>REFH</sub> and V<sub>SSA</sub>/V<sub>REFL</sub>, are double bonded to V<sub>DD</sub> and V<sub>SS</sub> respectively.

### Figure 13-1. MC9S08SG8 Block Diagram with RTC Module Highlighted

# 13.1.1 Features

Features of the RTC module include:

- 8-bit up-counter

- 8-bit modulo match limit

- Software controllable periodic interrupt on match

- Three software selectable clock sources for input to prescaler with selectable binary-based and decimal-based divider values

- 1-kHz internal low-power oscillator (LPO)

- External clock (ERCLK)

- 32-kHz internal clock (IRCLK)

# 13.1.2 Modes of Operation

This section defines the operation in stop, wait and background debug modes.

### 13.1.2.1 Wait Mode

The RTC continues to run in wait mode if enabled before executing the appropriate instruction. Therefore, the RTC can bring the MCU out of wait mode if the real-time interrupt is enabled. For lowest possible current consumption, the RTC should be stopped by software if not needed as an interrupt source during wait mode.

### 13.1.2.2 Stop Modes

The RTC continues to run in stop2 or stop3 mode if the RTC is enabled before executing the STOP instruction. Therefore, the RTC can bring the MCU out of stop modes with no external components, if the real-time interrupt is enabled.

The LPO clock can be used in stop2 and stop3 modes. ERCLK and IRCLK clocks are only available in stop3 mode.

Power consumption is lower when all clock sources are disabled, but in that case, the real-time interrupt cannot wake up the MCU from stop modes.

### 13.1.2.3 Active Background Mode

The RTC suspends all counting during active background mode until the microcontroller returns to normal user operating mode. Counting resumes from the suspended value as long as the RTCMOD register is not written and the RTCPS and RTCLKS bits are not altered.

#### Timer/PWM Module (S08TPMV3)

Input capture, output compare, and edge-aligned PWM functions do not make sense when the counter is operating in up/down counting mode so this implies that all active channels within a TPM must be used in CPWM mode when CPWMS=1.

The TPM may be used in an 8-bit MCU. The settings in the timer channel registers are buffered to ensure coherent 16-bit updates and to avoid unexpected PWM pulse widths. Writes to any of the registers TPMxMODH, TPMxMODL, TPMxCnVH, and TPMxCnVL, actually write to buffer registers.

In center-aligned PWM mode, the TPMxCnVH:L registers are updated with the value of their write buffer according to the value of CLKSB:CLKSA bits, so:

- If (CLKSB:CLKSA = 0:0), the registers are updated when the second byte is written

- If (CLKSB:CLKSA not = 0:0), the registers are updated after the both bytes were written, and the TPM counter changes from (TPMxMODH:TPMxMODL 1) to (TPMxMODH:TPMxMODL). If the TPM counter is a free-running counter, the update is made when the TPM counter changes from 0xFFFE to 0xFFFF.

When TPMxCNTH:TPMxCNTL=TPMxMODH:TPMxMODL, the TPM can optionally generate a TOF interrupt (at the end of this count).

Writing to TPMxSC cancels any values written to TPMxMODH and/or TPMxMODL and resets the coherency mechanism for the modulo registers. Writing to TPMxCnSC cancels any values written to the channel value registers and resets the coherency mechanism for TPMxCnVH:TPMxCnVL.

# 16.5 Reset Overview

### 16.5.1 General

The TPM is reset whenever any MCU reset occurs.

# 16.5.2 Description of Reset Operation

Reset clears the TPMxSC register which disables clocks to the TPM and disables timer overflow interrupts (TOIE=0). CPWMS, MSnB, MSnA, ELSnB, and ELSnA are all cleared which configures all TPM channels for input-capture operation with the associated pins disconnected from I/O pin logic (so all MCU pins related to the TPM revert to general purpose I/O pins).

# 16.6 Interrupts

# 16.6.1 General

The TPM generates an optional interrupt for the main counter overflow and an interrupt for each channel. The meaning of channel interrupts depends on each channel's mode of operation. If the channel is configured for input capture, the interrupt flag is set each time the selected input capture edge is recognized. If the channel is configured for output compare or PWM modes, the interrupt flag is set each time the main timer counter matches the value in the 16-bit channel value register.

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>WS  | <ul> <li>Wait or Stop Status — When the target CPU is in wait or stop mode, most BDC commands cannot function. However, the BACKGROUND command can be used to force the target CPU out of wait or stop and into active background mode where all BDC commands work. Whenever the host forces the target MCU into active background mode, the host should issue a READ_STATUS command to check that BDMACT = 1 before attempting other BDC commands.</li> <li>0 Target CPU is running user application code or in active background mode (was not in wait or stop mode when background became active)</li> <li>1 Target CPU is in wait or stop mode, or a BACKGROUND command was used to change from wait or stop to active background mode</li> </ul> |

| 1<br>WSF | <ul> <li>Wait or Stop Failure Status — This status bit is set if a memory access command failed due to the target CPU executing a wait or stop instruction at or about the same time. The usual recovery strategy is to issue a BACKGROUND command to get out of wait or stop mode into active background mode, repeat the command that failed, then return to the user program. (Typically, the host would restore CPU registers and stack values and re-execute the wait or stop instruction.)</li> <li>Memory access did not conflict with a wait or stop instruction</li> <li>Memory access command failed because the CPU entered wait or stop mode</li> </ul>                                                                                   |

| 0<br>DVF | <ul> <li>Data Valid Failure Status — This status bit is not used in the MC9S08SG8 because it does not have any slow access memory.</li> <li>0 Memory access did not conflict with a slow memory access</li> <li>1 Memory access command failed because CPU was not finished with a slow memory access</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                      |

### Table 17-2. BDCSCR Register Field Descriptions (continued)

### 17.4.1.2 BDC Breakpoint Match Register (BDCBKPT)

This 16-bit register holds the address for the hardware breakpoint in the BDC. The BKPTEN and FTS control bits in BDCSCR are used to enable and configure the breakpoint logic. Dedicated serial BDC commands (READ\_BKPT and WRITE\_BKPT) are used to read and write the BDCBKPT register but is not accessible to user programs because it is not located in the normal memory map of the MCU. Breakpoints are normally set while the target MCU is in active background mode before running the user application program. For additional information about setup and use of the hardware breakpoint logic in the BDC, refer to Section 17.2.4, "BDC Hardware Breakpoint."

# 17.4.2 System Background Debug Force Reset Register (SBDFR)

This register contains a single write-only control bit. A serial background mode command such as WRITE\_BYTE must be used to write to SBDFR. Attempts to write this register from a user program are ignored. Reads always return 0x00.

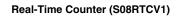

Figure A-8. Typical Frequency Deviation vs Temperature (ICS Trimmed to 16MHz bus@25°C, 5V, FEI)<sup>1</sup>

<sup>1.</sup> Based on the average of several hundred units from a typical characterization lot.

**Appendix A Electrical Characteristics**

NOTES:

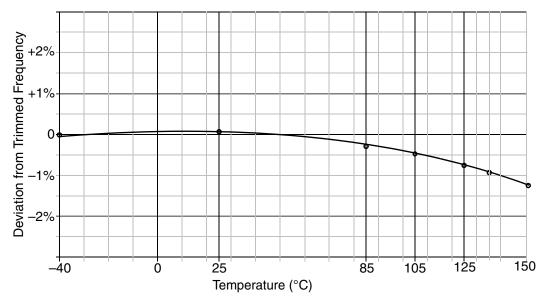

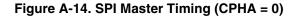

1.  $\overline{SS}$  output mode (MODFEN = 1, SSOE = 1).

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

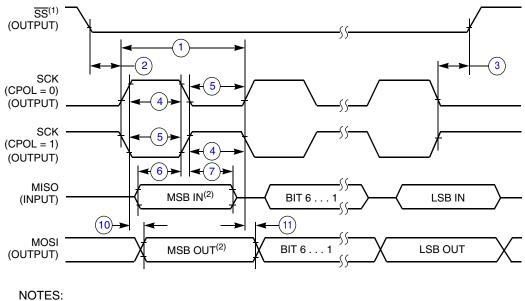

1.  $\overline{SS}$  output mode (MODFEN = 1, SSOE = 1).

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

MC9S08SG8 MCU Series Data Sheet, Rev. 8

# A.13 FLASH Specifications

This section provides details about program/erase times and program-erase endurance for the FLASH memory.

Program and erase operations do not require any special power sources other than the normal  $V_{DD}$  supply. For more detailed information about program/erase operations, see the Memory section.

|         |   |                                                                                                                                                 |                           |                            |                 |                   |        | Temp Rated <sup>1</sup> |                   |

|---------|---|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------|-----------------|-------------------|--------|-------------------------|-------------------|

| Nu<br>m | с | Characteristic                                                                                                                                  | Symbol                    | Min                        | Typical         | Max               | Unit   | Stand<br>ard            | AEC<br>Grade<br>0 |

| 1       | _ | Supply voltage for<br>program/erase                                                                                                             | V <sub>prog/erase</sub>   | 2.7                        |                 | 5.5               | V      | x                       | x                 |

| 2       | _ | Supply voltage for read operation                                                                                                               | V <sub>Read</sub> 2.7 5.5 |                            | 5.5             | V                 | x      | x                       |                   |

| 3       | — | Internal FCLK frequency <sup>2</sup>                                                                                                            | f <sub>FCLK</sub>         | 150                        |                 | 200               | kHz    | x                       | х                 |

| 4       | — | Internal FCLK period (1/f <sub>FCLK</sub> )                                                                                                     | t <sub>Fcyc</sub>         | 5                          |                 | 6.67              | μS     | х                       | х                 |

| 5       | _ | Byte program time (random<br>location) <sup>3</sup>                                                                                             | t <sub>prog</sub>         | 9                          |                 | t <sub>Fcyc</sub> | x      | x                       |                   |

| 6       | _ | Byte program time (burst mode) <sup>2</sup>                                                                                                     | t <sub>Burst</sub>        | 4                          |                 | t <sub>Fcyc</sub> | x      | x                       |                   |

| 7       | — | Page erase time <sup>2</sup>                                                                                                                    | t <sub>Page</sub>         | 4000                       |                 | t <sub>Fcyc</sub> | х      | х                       |                   |

| 8       | — | Mass erase time <sup>2</sup>                                                                                                                    | t <sub>Mass</sub>         | 20,000                     |                 | t <sub>Fcyc</sub> | х      | х                       |                   |

| 9       | с | Program/erase endurance <sup>4</sup><br>$T_L$ to $T_H = -40^{\circ}C$ to +125°C<br>$T_L$ to $T_H = -40^{\circ}C$ to +150°C<br>$T = 25^{\circ}C$ | n <sub>FLPE</sub>         | 10,000<br>10,000<br>10,000 | <br><br>100,000 |                   | cycles | x<br>                   | <br>x<br>x        |

| 10      | С | Data retention <sup>5</sup>                                                                                                                     | t <sub>D_ret</sub>        | 15 100 —                   |                 | years             | х      | х                       |                   |

<sup>1</sup> Electrical characteristics only apply to the temperature rated devices marked with x.

<sup>2</sup> The frequency of this clock is controlled by a software setting.

<sup>3</sup> These values are hardware state machine controlled. User code does not need to count cycles. This information supplied for calculating approximate time to program and erase.

<sup>4</sup> Typical endurance for FLASH is based on the intrinsic bit cell performance. For additional information on how Freescale defines typical endurance, please refer to Engineering Bulletin EB619/D, Typical Endurance for Nonvolatile Memory.

<sup>5</sup> Typical data retention values are based on intrinsic capability of the technology measured at high temperature and de-rated to 25°C using the Arrhenius equation. For additional information on how Freescale defines typical data retention, please refer to Engineering Bulletin EB618/D, Typical Data Retention for Nonvolatile Memory.

Appendix B Ordering Information and Mechanical Drawings

# **B.2** Mechanical Drawings

The following pages are mechanical specifications for MC9S08SG8 package options. See Table B-2 for the document number for each package type.

| Pin<br>Count | Туре    | Designator | Document No. |

|--------------|---------|------------|--------------|

| 20           | TSSOP   | TJ         | 98ASH70169A  |

| 16           | TSSOP   | TG         | 98ASH70247A  |

| 8            | NB SOIC | SC         | 98ASB42564B  |

#### Table B-2. Package Information