#### NXP USA Inc. - S9S08SG4E2VTGR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 12                                                                     |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                        |

| Supplier Device Package    | 16-TSSOP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08sg4e2vtgr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Chapter 4 Memory**

Table 4-2. Direct-Page Register Summary (Sheet 2 of 3)

| Address                            | Register<br>Name | Bit 7  | 6       | 5     | 4      | 3           | 2     | 1       | Bit 0    |

|------------------------------------|------------------|--------|---------|-------|--------|-------------|-------|---------|----------|

| 0x00 <b>39</b>                     | SCIBDL           | SBR7   | SBR6    | SBR5  | SBR4   | SBR3        | SBR2  | SBR1    | SBR0     |

| 0x00 <b>3A</b>                     | SCIC1            | LOOPS  | SCISWAI | RSRC  | М      | WAKE ILT    |       | PE      | PT       |

| 0x00 <b>3B</b>                     | SCIC2            | TIE    | TCIE    | RIE   | ILIE   | TE          | RE    | RWU     | SBK      |

| 0x00 <b>3C</b>                     | SCIS1            | TDRE   | TC      | RDRF  | IDLE   | OR          | NF    | FE      | PF       |

| 0x00 <b>3D</b>                     | SCIS2            | LBKDIF | RXEDGIF | 0     | RXINV  | RWUID       | BRK13 | LBKDE   | RAF      |

| 0x00 <b>3E</b>                     | SCIC3            | R8     | T8      | TXDIR | TXINV  | ORIE        | NEIE  | FEIE    | PEIE     |

| 0x00 <b>3F</b>                     | SCID             | Bit 7  | 6       | 5     | 4      | 3           | 2     | 1       | Bit 0    |

| 0x00 <b>40</b> –<br>0x00 <b>47</b> | Reserved         |        |         |       |        |             |       |         | _        |

| 0x00 <b>48</b>                     | ICSC1            | CL     | KS      |       | RDIV   |             | IREFS | IRCLKEN | IREFSTEN |

| 0x00 <b>49</b>                     | ICSC2            | BD     | VIV     | RANGE | HGO    | LP          | EREFS | ERCLKEN | EREFSTEN |

| 0x00 <b>4A</b>                     | ICSTRM           |        |         |       | TR     | MIM         |       |         |          |

| 0x00 <b>4B</b>                     | ICSSC            | 0      | 0       | 0     | IREFST | CLł         | KST   | OSCINIT | FTRIM    |

| 0x00 <b>4C</b> –<br>0x00 <b>4F</b> | Reserved         |        |         |       |        |             |       | -       | _        |

| 0x00 <b>50</b>                     | SPIC1            | SPIE   | SPE     | SPTIE | MSTR   | CPOL        | CPHA  | SSOE    | LSBFE    |

| 0x00 <b>51</b>                     | SPIC2            | 0      | 0       | 0     | MODFEN | BIDIROE     | 0     | SPISWAI | SPC0     |

| 0x00 <b>52</b>                     | SPIBR            | 0      | SPPR2   | SPPR1 | SPPR0  | 0           | SPR2  | SPR1    | SPR0     |

| 0x00 <b>53</b>                     | SPIS             | SPRF   | 0       | SPTEF | MODF   | 0           | 0     | 0       | 0        |

| 0x00 <b>54</b>                     | Reserved         | 0      | 0       | 0     | 0      | 0           | 0     | 0       | 0        |

| 0x00 <b>55</b>                     | SPID             | Bit 7  | 6       | 5     | 4      | 3           | 2     | 1       | Bit 0    |

| 0x00 <b>56</b> –<br>0x00 <b>57</b> | Reserved         | _      | _       | _     | _      | _           | _     | _       | _        |

| 0x00 <b>58</b>                     | IICA             | AD7    | AD6     | AD5   | AD4    | AD3         | AD2   | AD1     | 0        |

| 0x00 <b>59</b>                     | IICF             | ML     | JLT     |       |        | IC          | R     |         |          |

| 0x00 <b>5A</b>                     | IICC1            | IICEN  | IICIE   | MST   | TX     | TXAK RSTA 0 |       | 0       | 0        |

| 0x00 <b>5B</b>                     | IICS             | TCF    | IAAS    | BUSY  | ARBL   | 0           | SRW   | IICIF   | RXAK     |

| 0x00 <b>5C</b>                     | IICD             |        |         |       | DA     | TA          |       |         |          |

| 0x00 <b>5D</b>                     | IICC2            | GCAEN  | ADEXT   | 0     | 0      | 0           | AD10  | AD9     | AD8      |

| 0x00 <b>5E</b> –<br>0x00 <b>5F</b> | Reserved         | _      | _       | _     | _      | _           | _     | _       | _        |

| 0x00 <b>60</b>                     | TPM2SC           | TOF    | TOIE    | CPWMS | CLKSB  | CLKSA       | PS2   | PS1     | PS0      |

| 0x00 <b>61</b>                     | TPM2CNTH         | Bit 15 | 14      | 13    | 12     | 11          | 10    | 9       | Bit 8    |

| 0x00 <b>62</b>                     | TPM2CNTL         | Bit 7  | 6       | 5     | 4      | 3           | 2     | 1       | Bit 0    |

| 0x00 <b>63</b>                     | TPM2MODH         | Bit 15 | 14      | 13    | 12     | 11          | 10    | 9       | Bit 8    |

| 0x00 <b>64</b>                     | TPM2MODL         | Bit 7  | 6       | 5     | 4      | 3           | 2     | 1       | Bit 0    |

| 0x00 <b>65</b>                     | TPM2C0SC         | CH0F   | CH0IE   | MS0B  | MS0A   | ELS0B       | ELS0A | 0       | 0        |

| 0x00 <b>66</b>                     | TPM2C0VH         | Bit 15 | 14      | 13    | 12     | 11          | 10    | 9       | Bit 8    |

| 0x00 <b>67</b>                     | TPM2C0VL         | Bit 7  | 6       | 5     | 4      | 3           | 2     | 1       | Bit 0    |

| 0x00 <b>68</b>                     | TPM2C1SC         | CH1F   | CH1IE   | MS1B  | MS1A   | ELS1B       | ELS1A | 0       | 0        |

MC9S08SG8 MCU Series Data Sheet, Rev. 8

Chapter 4 Memory

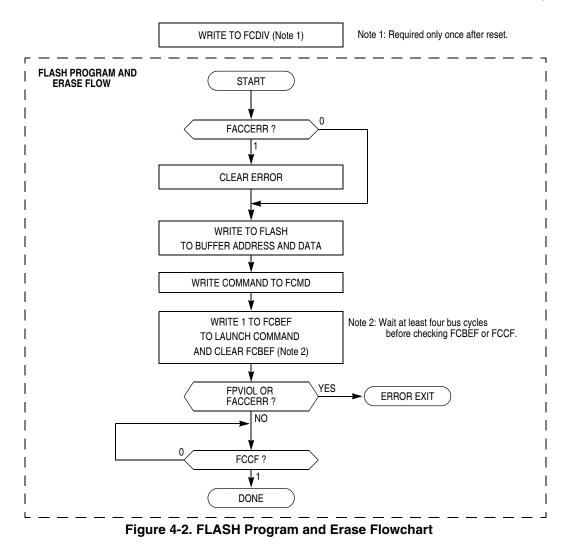

### 4.5.4 Burst Program Execution

The burst program command is used to program sequential bytes of data in less time than would be required using the standard program command. This is possible because the high voltage to the FLASH array does not need to be disabled between program operations. Ordinarily, when a program or erase command is issued, an internal charge pump associated with the FLASH memory must be enabled to supply high voltage to the array. Upon completion of the command, the charge pump is turned off. When a burst program command is issued, the charge pump is enabled and then remains enabled after completion of the burst program operation if these two conditions are met:

- The next burst program command has been queued before the current program operation has completed.

- The next sequential address selects a byte on the same physical row as the current byte being programmed. A row of FLASH memory consists of 64 bytes. A byte within a row is selected by addresses A5 through A0. A new row begins when addresses A5 through A0 are all zero.

# Chapter 5 Resets, Interrupts, and General System Control

# 5.1 Introduction

This section discusses basic reset and interrupt mechanisms and the various sources of reset and interrupt in the MC9S08SG8. Some interrupt sources from peripheral modules are discussed in greater detail within other sections of this data sheet. This section gathers basic information about all reset and interrupt sources in one place for easy reference. A few reset and interrupt sources, including the computer operating properly (COP) watchdog are not part of on-chip peripheral systems with their own chapters.

# 5.2 Features

Reset and interrupt features include:

- Multiple sources of reset for flexible system configuration and reliable operation

- Reset status register (SRS) to indicate source of most recent reset

- Separate interrupt vector for each module (reduces polling overhead) (see Table 5-2)

# 5.3 MCU Reset

Resetting the MCU provides a way to start processing from a known set of initial conditions. During reset, most control and status registers are forced to initial values and the program counter is loaded from the reset vector (0xFFFE:0xFFFF). On-chip peripheral modules are disabled and I/O pins are initially configured as general-purpose high-impedance inputs with pull-up devices disabled. The I bit in the condition code register (CCR) is set to block maskable interrupts so the user program has a chance to initialize the stack pointer (SP) and system control settings. SP is forced to 0x00FF at reset.

The MC9S08SG8 has the following sources for reset:

- Power-on reset (POR)

- External pin reset (PIN)

- Low-voltage detect (LVD)

- Computer operating properly (COP) timer

- Illegal opcode detect (ILOP)

- Illegal address detect (ILAD)

- Background debug forced reset

Each of these sources, with the exception of the background debug forced reset, has an associated bit in the system reset status register (SRS).

| Vector<br>Priority | Vector<br>Number | Address<br>(High/Low) | Vector<br>Name | Module            | Source                             | Enable                        | Description                                          |

|--------------------|------------------|-----------------------|----------------|-------------------|------------------------------------|-------------------------------|------------------------------------------------------|

|                    | 31               | 0xFFC0/0xFFC1         | —              | _                 |                                    | _                             | —                                                    |

| Lowest             | 30               | 0xFFC2/0xFFC3         | Vacmp          | ACMP              | ACF                                | ACIE                          | Analog comparator                                    |

|                    | 29               | 0xFFC4/0xFFC5         | —              | _                 | —                                  | —                             | —                                                    |

|                    | 28               | 0xFFC6/0xFFC7         | —              |                   | —                                  | —                             | —                                                    |

|                    | 27               | 0xFFC8/0xFFC9         | —              | _                 | —                                  | —                             | —                                                    |

|                    | 26               | 0xFFCA/0xFFCB         | Vmtim          | MTIM              | TOF                                | TOIE                          | MTIM overflow                                        |

|                    | 25               | 0xFFCC/0xFFCD         | Vrtc           | RTC               | RTIF                               | RTIE                          | Real-time interrupt                                  |

|                    | 24               | 0xFFCE/0xFFCF         | Viic           | IIC               | IICIF                              | IICIE                         | IIC control                                          |

|                    | 23               | 0xFFD0/0xFFD1         | Vadc           | ADC               | COCO                               | AIEN                          | ADC                                                  |

|                    | 22               | 0xFFD2/0xFFD3         | —              | _                 | —                                  | —                             | —                                                    |

|                    | 21               | 0xFFD4/0xFFD5         | Vportb         | Port B            | PTBIF                              | PTBIE                         | Port B Pins                                          |

|                    | 20               | 0xFFD6/0xFFD7         | Vporta         | Port A            | PTAIF                              | PTAIE                         | Port A Pins                                          |

|                    | 19               | 0xFFD8/0xFFD9         | —              |                   | —                                  | —                             | —                                                    |

|                    | 18               | 0xFFDA/0xFFDB         | Vscitx         | SCI               | TDRE, TC                           | TIE, TCIE                     | SCI transmit                                         |

|                    | 17               | 0xFFDC/0xFFDD         | Vscirx         | SCI               | IDLE, RDRF,<br>LBKDIF,<br>RXEDGIF  | ILIE, RIE, LBKDIE,<br>RXEDGIE | SCI receive                                          |

|                    | 16               | 0xFFDE/0xFFDF         | Vscierr        | SCI               | OR, NF,<br>FE, PF                  | ORIE, NFIE,<br>FEIE, PFIE     | SCI error                                            |

|                    | 15               | 0xFFE0/0xFFE1         | Vspi           | SPI               | SPIF, MODF,<br>SPTEF               | SPIE, SPIE, SPTIE             | SPI                                                  |

|                    | 14               | 0xFFE2/0xFFE3         | Vtpm2ovf       | TPM2              | TOF                                | TOIE                          | TPM2 overflow                                        |

|                    | 13               | 0xFFE4/0xFFE5         | Vtpm2ch1       | TPM2              | CH1F                               | CH1IE                         | TPM2 channel 1                                       |

|                    | 12               | 0xFFE6/0xFFE7         | Vtpm2ch0       | TPM2              | CH0F                               | CH0IE                         | TPM2 channel 0                                       |

|                    | 11               | 0xFFE8/0xFFE9         | Vtpm1ovf       | TPM1              | TOF                                | TOIE                          | TPM1 overflow                                        |

|                    | 10               | 0xFFEA/0xFFEB         | —              | —                 | —                                  | —                             | —                                                    |

|                    | 9                | 0xFFEC/0xFFED         | —              |                   | —                                  | —                             | —                                                    |

|                    | 8                | 0xFFEE/0xFFEF         | —              |                   | —                                  | —                             | —                                                    |

|                    | 7                | 0xFFF0/0xFFF1         | —              | —                 | —                                  | —                             | —                                                    |

|                    | 6                | 0xFFF2/0xFFF3         | Vtpm1ch1       | TPM1              | CH1F                               | CH1IE                         | TPM1 channel 1                                       |

|                    | 5                | 0xFFF4/0xFFF5         | Vtpm1ch0       | TPM1              | CH0F                               | CH0IE                         | TPM1 channel 0                                       |

|                    | 4                | 0xFFF6/0xFFF7         | —              | —                 | —                                  | —                             | —                                                    |

|                    | 3                | 0xFFF8/0xFFF9         | Vlvd           | System<br>control | LVWF                               | LVWIE                         | Low-voltage warning                                  |

|                    | 2                | 0xFFFA/0xFFFB         | —              |                   | —                                  | —                             | —                                                    |

|                    | 1                | 0xFFFC/0xFFFD         | Vswi           | Core              | SWI Instruction                    | —                             | Software interrupt                                   |

| ¥                  | 0                | 0xFFFE/0xFFFF         | Vreset         | System<br>control | COP,<br>LVD,<br>RESET pin,         | COPT<br>LVDRE<br>—            | Watchdog timer<br>Low-voltage detect<br>External pin |

| Highest            |                  |                       |                |                   | Illegal opcode,<br>Illegal address | —<br>—                        | Illegal opcode<br>Illegal address                    |

#### Table 5-2. Vector Summary

# 5.6 Low-Voltage Detect (LVD) System

The MC9S08SG8 includes a system to protect against low voltage conditions in order to protect memory contents and control MCU system states during supply voltage variations. The system is comprised of a power-on reset (POR) circuit and a LVD circuit with trip voltages for warning and detection. The LVD circuit is enabled when LVDE in SPMSC1 is set to 1. The LVD is disabled upon entering any of the stop modes unless LVDSE is set in SPMSC1. If LVDSE and LVDE are both set, then the MCU cannot enter stop2, and the current consumption in stop3 with the LVD enabled will be higher.

### 5.6.1 Power-On Reset Operation

When power is initially applied to the MCU, or when the supply voltage drops below the power-on reset rearm voltage level,  $V_{POR}$ , the POR circuit will cause a reset condition. As the supply voltage rises, the LVD circuit will hold the MCU in reset until the supply has risen above the low voltage detection low threshold,  $V_{LVDL}$ . Both the POR bit and the LVD bit in SRS are set following a POR.

#### 5.6.2 Low-Voltage Detection (LVD) Reset Operation

The LVD can be configured to generate a reset upon detection of a low voltage condition by setting LVDRE to 1. The low voltage detection threshold is determined by the LVDV bit. After an LVD reset has occurred, the LVD system will hold the MCU in reset until the supply voltage has risen above the low voltage detection threshold. The LVD bit in the SRS register is set following either an LVD reset or POR.

### 5.6.3 Low-Voltage Warning (LVW) Interrupt Operation

The LVD system has a low voltage warning flag to indicate to the user that the supply voltage is approaching the low voltage condition. When a low voltage warning condition is detected and is configured for interrupt operation (LVWIE set to 1), LVWF in SPMSC1 will be set and an LVW interrupt request will occur.

### 5.7 Reset, Interrupt, and System Control Registers and Control Bits

One 8-bit register in the direct page register space and eight 8-bit registers in the high-page register space are related to reset and interrupt systems.

Refer to Table 4-2 and Table 4-3 in Chapter 4, "Memory," of this data sheet for the absolute address assignments for all registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

Some control bits in the SOPT1 and SPMSC2 registers are related to modes of operation. Although brief descriptions of these bits are provided here, the related functions are discussed in greater detail in Chapter 3, "Modes of Operation."

#### Table 5-3. SRS Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>ILAD | Illegal Address — Reset was caused by an attempt to access either data or an instruction at an unimplemented memory address.         0       Reset not caused by an illegal address         1       Reset caused by an illegal address                              |

| 1<br>LVD  | <ul> <li>Low Voltage Detect — If the LVDRE bit is set and the supply drops below the LVD trip voltage, an LVD reset will occur. This bit is also set by POR.</li> <li>0 Reset not caused by LVD trip or POR.</li> <li>1 Reset caused by LVD trip or POR.</li> </ul> |

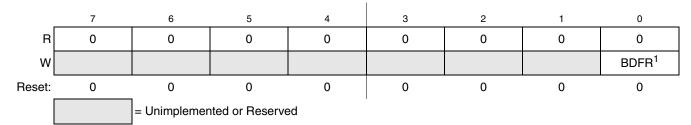

### 5.7.2 System Background Debug Force Reset Register (SBDFR)

This high page register contains a single write-only control bit. A serial background command such as WRITE\_BYTE must be used to write to SBDFR. Attempts to write this register from a user program are ignored. Reads always return 0x00.

<sup>1</sup> BDFR is writable only through serial background debug commands, not from user programs.

#### Figure 5-3. System Background Debug Force Reset Register (SBDFR)

#### Table 5-4. SBDFR Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BDFR  | <b>Background Debug Force Reset</b> — A serial background command such as WRITE_BYTE can be used to allow an external debug host to force a target system reset. Writing 1 to this bit forces an MCU reset. This bit cannot be written from a user program. |

#### Chapter 7 Central Processor Unit (S08CPUV2)

| Source<br>Form                                                                                                  | Operation                                                                                                                                                                                                                                                                                                                                                                                          | Address<br>Mode                                     | Object Code                                                                      | Cycles                          | Cyc-by-Cyc<br>Details                                    | -   | Affect<br>n CCR |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------|-----|-----------------|

| 1 Onn                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                    | Ρd                                                  |                                                                                  | ŝ                               | Details                                                  | VH  | INZC            |

| SUB #opr8i<br>SUB opr8a<br>SUB opr16a<br>SUB oprx16,X<br>SUB oprx8,X<br>SUB ,X<br>SUB oprx16,SP<br>SUB oprx8,SP | Subtract<br>A $\leftarrow$ (A) – (M)                                                                                                                                                                                                                                                                                                                                                               | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP2<br>SP1 | A0 ii<br>B0 dd<br>C0 hh ll<br>D0 ee ff<br>E0 ff<br>F0<br>9E D0 ee ff<br>9E E0 ff | 2<br>3<br>4<br>3<br>3<br>5<br>4 | pp<br>rpp<br>prpp<br>prpp<br>rpp<br>rfp<br>pprpp<br>prpp | Þ-  | - Þ Þ Þ         |

| swi                                                                                                             | Software Interrupt<br>PC $\leftarrow$ (PC) + 0x0001<br>Push (PCL); SP $\leftarrow$ (SP) - 0x0001<br>Push (PCH); SP $\leftarrow$ (SP) - 0x0001<br>Push (X); SP $\leftarrow$ (SP) - 0x0001<br>Push (A); SP $\leftarrow$ (SP) - 0x0001<br>Push (CCR); SP $\leftarrow$ (SP) - 0x0001<br>I $\leftarrow$ 1;<br>PCH $\leftarrow$ Interrupt Vector High Byte<br>PCL $\leftarrow$ Interrupt Vector Low Byte | INH                                                 | 83                                                                               | 11                              | ssssvvfppp                                               |     | 1 – – –         |

| ТАР                                                                                                             | Transfer Accumulator to CCR $CCR \leftarrow (A)$                                                                                                                                                                                                                                                                                                                                                   | INH                                                 | 84                                                                               | 1                               | p                                                        | ÞÞ  | ÞÞÞÞ            |

| ТАХ                                                                                                             | Transfer Accumulator to X (Index Register Low) $X \leftarrow (A)$                                                                                                                                                                                                                                                                                                                                  | INH                                                 | 97                                                                               | 1                               | р                                                        |     |                 |

| ТРА                                                                                                             | Transfer CCR to Accumulator $A \leftarrow (CCR)$                                                                                                                                                                                                                                                                                                                                                   | INH                                                 | 85                                                                               | 1                               | q                                                        |     |                 |

| TST opr8a<br>TSTA<br>TSTX<br>TST oprx8,X<br>TST ,X<br>TST oprx8,SP                                              | $ \begin{array}{ll} \mbox{Test for Negative or Zero} & (M) - 0x00 \\ & (A) - 0x00 \\ & (X) - 0x00 \\ & (M) - 0x00 \\ \end{array} $                                                                                                                                                                                                 | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 3D dd<br>4D<br>5D<br>6D ff<br>7D<br>9E 6D ff                                     | 4<br>1<br>4<br>3<br>5           | rfpp<br>p<br>rfpp<br>rfp<br>prfpp                        | 0 — | - þ þ -         |

| TSX                                                                                                             | Transfer SP to Index Reg.<br>H:X $\leftarrow$ (SP) + 0x0001                                                                                                                                                                                                                                                                                                                                        | INH                                                 | 95                                                                               | 2                               | fp                                                       |     |                 |

| ТХА                                                                                                             | Transfer X (Index Reg. Low) to Accumulator $A \leftarrow (X)$                                                                                                                                                                                                                                                                                                                                      | INH                                                 | 9F                                                                               | 1                               | р                                                        |     |                 |

| ADICLK | Selected Clock Source      |  |  |

|--------|----------------------------|--|--|

| 00     | Bus clock                  |  |  |

| 01     | Bus clock divided by 2     |  |  |

| 10     | Alternate clock (ALTCLK)   |  |  |

| 11     | Asynchronous clock (ADACK) |  |  |

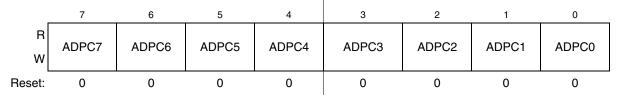

### 9.3.8 Pin Control 1 Register (APCTL1)

The pin control registers are used to disable the I/O port control of MCU pins used as analog inputs. APCTL1 is used to control the pins associated with channels 0–7 of the ADC module.

Figure 9-11. Pin Control 1 Register (APCTL1)

| Field      | Description                                                                                                                                                                          |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>ADPC7 | <ul> <li>ADC Pin Control 7 — ADPC7 is used to control the pin associated with channel AD7.</li> <li>0 AD7 pin I/O control enabled</li> <li>1 AD7 pin I/O control disabled</li> </ul> |  |

| 6<br>ADPC6 | <ul> <li>ADC Pin Control 6 — ADPC6 is used to control the pin associated with channel AD6.</li> <li>0 AD6 pin I/O control enabled</li> <li>1 AD6 pin I/O control disabled</li> </ul> |  |

| 5<br>ADPC5 | <ul> <li>ADC Pin Control 5 — ADPC5 is used to control the pin associated with channel AD5.</li> <li>0 AD5 pin I/O control enabled</li> <li>1 AD5 pin I/O control disabled</li> </ul> |  |

| 4<br>ADPC4 | <ul> <li>ADC Pin Control 4 — ADPC4 is used to control the pin associated with channel AD4.</li> <li>0 AD4 pin I/O control enabled</li> <li>1 AD4 pin I/O control disabled</li> </ul> |  |

| 3<br>ADPC3 | <ul> <li>ADC Pin Control 3 — ADPC3 is used to control the pin associated with channel AD3.</li> <li>0 AD3 pin I/O control enabled</li> <li>1 AD3 pin I/O control disabled</li> </ul> |  |

| 2<br>ADPC2 | <ul> <li>ADC Pin Control 2 — ADPC2 is used to control the pin associated with channel AD2.</li> <li>0 AD2 pin I/O control enabled</li> <li>1 AD2 pin I/O control disabled</li> </ul> |  |

#### Table 9-9. APCTL1 Register Field Descriptions

| Field      | Description                                                                                                                                                                          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>ADPC9 | <ul> <li>ADC Pin Control 9 — ADPC9 is used to control the pin associated with channel AD9.</li> <li>0 AD9 pin I/O control enabled</li> <li>1 AD9 pin I/O control disabled</li> </ul> |

| 0<br>ADPC8 | <ul> <li>ADC Pin Control 8 — ADPC8 is used to control the pin associated with channel AD8.</li> <li>0 AD8 pin I/O control enabled</li> <li>1 AD8 pin I/O control disabled</li> </ul> |

#### Table 9-10. APCTL2 Register Field Descriptions (continued)

# 9.3.10 Pin Control 3 Register (APCTL3)

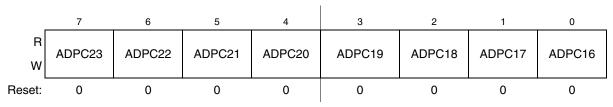

APCTL3 is used to control channels 16–23 of the ADC module.

Figure 9-13. Pin Control 3 Register (APCTL3)

#### Table 9-11. APCTL3 Register Field Descriptions

| Field       | Description                                                                                                                                                                               |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADPC23 | <ul> <li>ADC Pin Control 23 — ADPC23 is used to control the pin associated with channel AD23.</li> <li>0 AD23 pin I/O control enabled</li> <li>1 AD23 pin I/O control disabled</li> </ul> |

| 6<br>ADPC22 | <ul> <li>ADC Pin Control 22 — ADPC22 is used to control the pin associated with channel AD22.</li> <li>0 AD22 pin I/O control enabled</li> <li>1 AD22 pin I/O control disabled</li> </ul> |

| 5<br>ADPC21 | <ul> <li>ADC Pin Control 21 — ADPC21 is used to control the pin associated with channel AD21.</li> <li>0 AD21 pin I/O control enabled</li> <li>1 AD21 pin I/O control disabled</li> </ul> |

| 4<br>ADPC20 | <ul> <li>ADC Pin Control 20 — ADPC20 is used to control the pin associated with channel AD20.</li> <li>0 AD20 pin I/O control enabled</li> <li>1 AD20 pin I/O control disabled</li> </ul> |

| 3<br>ADPC19 | <ul> <li>ADC Pin Control 19 — ADPC19 is used to control the pin associated with channel AD19.</li> <li>0 AD19 pin I/O control enabled</li> <li>1 AD19 pin I/O control disabled</li> </ul> |

| 2<br>ADPC18 | <ul> <li>ADC Pin Control 18 — ADPC18 is used to control the pin associated with channel AD18.</li> <li>0 AD18 pin I/O control enabled</li> <li>1 AD18 pin I/O control disabled</li> </ul> |

#### Internal Clock Source (S08ICSV2)

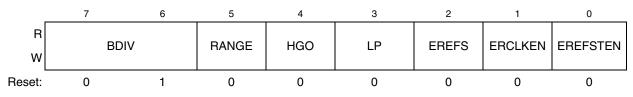

# 10.3.2 ICS Control Register 2 (ICSC2)

Figure 10-4. ICS Control Register 2 (ICSC2)

| Table 10-3. ICS Control Register 2 | Field Descriptions |

|------------------------------------|--------------------|

|------------------------------------|--------------------|

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6<br>BDIV   | Bus Frequency Divider — Selects the amount to divide down the clock source selected by the CLKS bits. This controls the bus frequency.         00       Encoding 0 — Divides selected clock by 1         01       Encoding 1 — Divides selected clock by 2 (reset default)         10       Encoding 2 — Divides selected clock by 4         11       Encoding 3 — Divides selected clock by 8 |

| 5<br>RANGE    | <ul> <li>Frequency Range Select — Selects the frequency range for the external oscillator.</li> <li>1 High frequency range selected for the external oscillator</li> <li>0 Low frequency range selected for the external oscillator</li> </ul>                                                                                                                                                 |

| 4<br>HGO      | <ul> <li>High Gain Oscillator Select — The HGO bit controls the external oscillator mode of operation.</li> <li>Configure external oscillator for high gain operation</li> <li>Configure external oscillator for low power operation</li> </ul>                                                                                                                                                |

| 3<br>LP       | <ul> <li>Low Power Select — The LP bit controls whether the FLL is disabled in FLL bypassed modes.</li> <li>1 FLL is disabled in bypass modes unless BDM is active</li> <li>0 FLL is not disabled in bypass mode</li> </ul>                                                                                                                                                                    |

| 2<br>EREFS    | <ul> <li>External Reference Select — The EREFS bit selects the source for the external reference clock.</li> <li>1 Oscillator requested</li> <li>0 External Clock Source requested</li> </ul>                                                                                                                                                                                                  |

| 1<br>ERCLKEN  | External Reference Enable — The ERCLKEN bit enables the external reference clock for use as ICSERCLK.<br>1 ICSERCLK active<br>0 ICSERCLK inactive                                                                                                                                                                                                                                              |

| 0<br>EREFSTEN | <ul> <li>External Reference Stop Enable — The EREFSTEN bit controls whether or not the external reference clock remains enabled when the ICS enters stop mode.</li> <li>1 External reference clock stays enabled in stop if ERCLKEN is set or if ICS is in FEE, FBE, or FBELP mode before entering stop</li> <li>0 External reference clock is disabled in stop</li> </ul>                     |

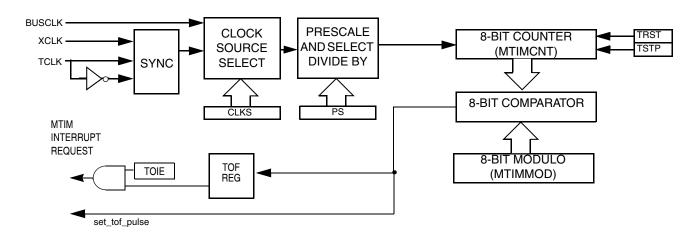

### 12.1.2 Features

Timer system features include:

- 8-bit up-counter

- Free-running or 8-bit modulo limit

- Software controllable interrupt on overflow

- Counter reset bit (TRST)

- Counter stop bit (TSTP)

- Four software selectable clock sources for input to prescaler:

- System bus clock rising edge

- Fixed frequency clock (XCLK) rising edge

- External clock source on the TCLK pin rising edge

- External clock source on the TCLK pin falling edge

- Nine selectable clock prescale values:

- Clock source divide by 1, 2, 4, 8, 16, 32, 64, 128, or 256

### 12.1.3 Modes of Operation

This section defines the MTIM's operation in stop, wait and background debug modes.

#### 12.1.3.1 MTIM in Wait Mode

The MTIM continues to run in wait mode if enabled before executing the WAIT instruction. Therefore, the MTIM can be used to bring the MCU out of wait mode if the timer overflow interrupt is enabled. For lowest possible current consumption, the MTIM should be stopped by software if not needed as an interrupt source during wait mode.

#### 12.1.3.2 MTIM in Stop Modes

The MTIM is disabled in all stop modes, regardless of the settings before executing the STOP instruction. Therefore, the MTIM cannot be used as a wake up source from stop modes.

Waking from stop1 and stop2 modes, the MTIM will be put into its reset state. If stop3 is exited with a reset, the MTIM will be put into its reset state. If stop3 is exited with an interrupt, the MTIM continues from the state it was in when stop3 was entered. If the counter was active upon entering stop3, the count will resume from the current value.

### 12.1.3.3 MTIM in Active Background Mode

The MTIM suspends all counting until the microcontroller returns to normal user operating mode. Counting resumes from the suspended value as long as an MTIM reset did not occur (TRST written to a 1 or MTIMMOD written).

Modulo Timer (S08MTIMV1)

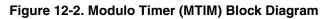

# 12.1.4 Block Diagram

The block diagram for the modulo timer module is shown Figure 12-2.

# 12.2 External Signal Description

The MTIM includes one external signal, TCLK, used to input an external clock when selected as the MTIM clock source. The signal properties of TCLK are shown in Table 12-1.

| Table 12-1. | Signal | Properties |

|-------------|--------|------------|

|-------------|--------|------------|

| Signal | Function                              | I/O |

|--------|---------------------------------------|-----|

| TCLK   | External clock source input into MTIM | Ι   |

The TCLK input must be synchronized by the bus clock. Also, variations in duty cycle and clock jitter must be accommodated. Therefore, the TCLK signal must be limited to one-fourth of the bus frequency.

The TCLK pin can be muxed with a general-purpose port pin. See the Pins and Connections chapter for the pin location and priority of this function.

# Chapter 13 Real-Time Counter (S08RTCV1)

# 13.1 Introduction

The RTC module consists of one 8-bit counter, one 8-bit comparator, several binary-based and decimal-based prescaler dividers, two clock sources, and one programmable periodic interrupt. This module can be used for time-of-day, calendar or any task scheduling functions. It can also serve as a cyclic wake up from low power modes without the need of external components.

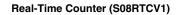

### 13.3.1 RTC Status and Control Register (RTCSC)

RTCSC contains the real-time interrupt status flag (RTIF), the clock select bits (RTCLKS), the real-time interrupt enable bit (RTIE), and the prescaler select bits (RTCPS).

Figure 13-3. RTC Status and Control Register (RTCSC)

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>RTIF     | <ul> <li>Real-Time Interrupt Flag This status bit indicates the RTC counter register reached the value in the RTC modulo register. Writing a logic 0 has no effect. Writing a logic 1 clears the bit and the real-time interrupt request. Reset clears RTIF.</li> <li>0 RTC counter has not reached the value in the RTC modulo register.</li> <li>1 RTC counter has reached the value in the RTC modulo register.</li> </ul>                                                                                                                     |

| 6–5<br>RTCLKS | Real-Time Clock Source Select. These two read/write bits select the clock source input to the RTC prescaler.<br>Changing the clock source clears the prescaler and RTCCNT counters. When selecting a clock source, ensure<br>that the clock source is properly enabled (if applicable) to ensure correct operation of the RTC. Reset clears<br>RTCLKS.<br>00 Real-time clock source is the 1-kHz low power oscillator (LPO)<br>01 Real-time clock source is the external clock (ERCLK)<br>1x Real-time clock source is the internal clock (IRCLK) |

| 4<br>RTIE     | <ul> <li>Real-Time Interrupt Enable. This read/write bit enables real-time interrupts. If RTIE is set, then an interrupt is generated when RTIF is set. Reset clears RTIE.</li> <li>Real-time interrupt requests are disabled. Use software polling.</li> <li>Real-time interrupt requests are enabled.</li> </ul>                                                                                                                                                                                                                                |

| 3–0<br>RTCPS  | Real-Time Clock Prescaler Select. These four read/write bits select binary-based or decimal-based divide-by values for the clock source. See Table 13-3. Changing the prescaler value clears the prescaler and RTCCNT counters. Reset clears RTCPS.                                                                                                                                                                                                                                                                                               |

Table 13-3. RTC Prescaler Divide-by values

| RTCLKS[0] |     |                 |                 |                 |                 |                 |                 |                 | RTCP            | S                 |                   |                 |                   |                   |                   |                   |

|-----------|-----|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-------------------|-------------------|-----------------|-------------------|-------------------|-------------------|-------------------|

|           | 0   | 1               | 2               | 3               | 4               | 5               | 6               | 7               | 8               | 9                 | 10                | 11              | 12                | 13                | 14                | 15                |

| 0         | Off | 2 <sup>3</sup>  | 2 <sup>5</sup>  | 2 <sup>6</sup>  | 2 <sup>7</sup>  | 2 <sup>8</sup>  | 2 <sup>9</sup>  | 2 <sup>10</sup> | 1               | 2                 | 2 <sup>2</sup>    | 10              | 2 <sup>4</sup>    | 10 <sup>2</sup>   | 5x10 <sup>2</sup> | 10 <sup>3</sup>   |

| 1         | Off | 2 <sup>10</sup> | 2 <sup>11</sup> | 2 <sup>12</sup> | 2 <sup>13</sup> | 2 <sup>14</sup> | 2 <sup>15</sup> | 2 <sup>16</sup> | 10 <sup>3</sup> | 2x10 <sup>3</sup> | 5x10 <sup>3</sup> | 10 <sup>4</sup> | 2x10 <sup>4</sup> | 5x10 <sup>4</sup> | 10 <sup>5</sup>   | 2x10 <sup>5</sup> |

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>WAKE | <ul> <li>Receiver Wakeup Method Select — Refer to Section 14.3.3.2, "Receiver Wakeup Operation" for more information.</li> <li>0 Idle-line wakeup.</li> <li>1 Address-mark wakeup.</li> </ul>                                                                                                                                                                                                                                     |

| 2<br>ILT  | Idle Line Type Select — Setting this bit to 1 ensures that the stop bit and logic 1 bits at the end of a character do not count toward the 10 or 11 bit times of logic high level needed by the idle line detection logic. Refer to Section 14.3.3.2.1, "Idle-Line Wakeup" for more information.         0       Idle character bit count starts after start bit.         1       Idle character bit count starts after stop bit. |

| 1<br>PE   | <ul> <li>Parity Enable — Enables hardware parity generation and checking. When parity is enabled, the most significant bit (MSB) of the data character (eighth or ninth data bit) is treated as the parity bit.</li> <li>0 No hardware parity generation or checking.</li> <li>1 Parity enabled.</li> </ul>                                                                                                                       |

| 0<br>PT   | <ul> <li>Parity Type — Provided parity is enabled (PE = 1), this bit selects even or odd parity. Odd parity means the total number of 1s in the data character, including the parity bit, is odd. Even parity means the total number of 1s in the data character, including the parity bit, is even.</li> <li>0 Even parity.</li> <li>1 Odd parity.</li> </ul>                                                                    |

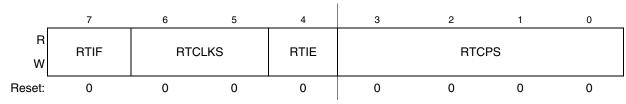

# 14.2.3 SCI Control Register 2 (SCIC2)

This register can be read or written at any time.

Figure 14-7. SCI Control Register 2 (SCIC2)

#### Table 14-4. SCIC2 Field Descriptions

| Field     | Description                                                                                                                                                                                   |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TIE  | Transmit Interrupt Enable (for TDRE)00111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111                                                  |

| 6<br>TCIE | <ul> <li>Transmission Complete Interrupt Enable (for TC)</li> <li>0 Hardware interrupts from TC disabled (use polling).</li> <li>1 Hardware interrupt requested when TC flag is 1.</li> </ul> |

| 5<br>RIE  | <ul> <li>Receiver Interrupt Enable (for RDRF)</li> <li>0 Hardware interrupts from RDRF disabled (use polling).</li> <li>1 Hardware interrupt requested when RDRF flag is 1.</li> </ul>        |

| 4<br>ILIE | Idle Line Interrupt Enable (for IDLE)00111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111 <td< td=""></td<>                               |

### 15.1.1 Features

Features of the SPI module include:

- Master or slave mode operation

- Full-duplex or single-wire bidirectional option

- Programmable transmit bit rate

- Double-buffered transmit and receive

- Serial clock phase and polarity options

- Slave select output

- Selectable MSB-first or LSB-first shifting

### 15.1.2 Block Diagrams

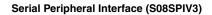

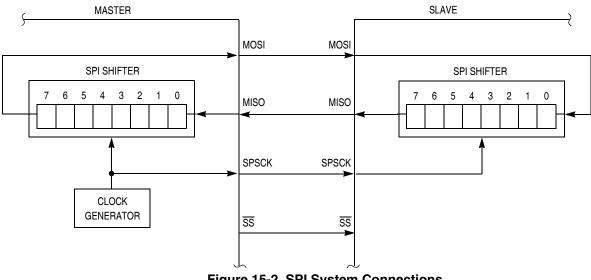

This section includes block diagrams showing SPI system connections, the internal organization of the SPI module, and the SPI clock dividers that control the master mode bit rate.

#### 15.1.2.1 SPI System Block Diagram

Figure 15-2 shows the SPI modules of two MCUs connected in a master-slave arrangement. The master device initiates all SPI data transfers. During a transfer, the master shifts data out (on the MOSI pin) to the slave while simultaneously shifting data in (on the MISO pin) from the slave. The transfer effectively exchanges the data that was in the SPI shift registers of the two SPI systems. The SPSCK signal is a clock output from the master and an input to the slave. The slave device must be selected by a low level on the slave select input ( $\overline{SS}$  pin). In this system, the master device has configured its  $\overline{SS}$  pin as an optional slave select output.

Figure 15-2. SPI System Connections

#### MC9S08SG8 MCU Series Data Sheet, Rev.8

Serial Peripheral Interface (S08SPIV3)

# 15.2 External Signal Description

The SPI optionally shares four port pins. The function of these pins depends on the settings of SPI control bits. When the SPI is disabled (SPE = 0), these four pins revert to being general-purpose port I/O pins that are not controlled by the SPI.

## 15.2.1 SPSCK — SPI Serial Clock

When the SPI is enabled as a slave, this pin is the serial clock input. When the SPI is enabled as a master, this pin is the serial clock output.

## 15.2.2 MOSI — Master Data Out, Slave Data In

When the SPI is enabled as a master and SPI pin control zero (SPC0) is 0 (not bidirectional mode), this pin is the serial data output. When the SPI is enabled as a slave and SPC0 = 0, this pin is the serial data input. If SPC0 = 1 to select single-wire bidirectional mode, and master mode is selected, this pin becomes the bidirectional data I/O pin (MOMI). Also, the bidirectional mode output enable bit determines whether the pin acts as an input (BIDIROE = 0) or an output (BIDIROE = 1). If SPC0 = 1 and slave mode is selected, this pin is not used by the SPI and reverts to being a general-purpose port I/O pin.

# 15.2.3 MISO — Master Data In, Slave Data Out

When the SPI is enabled as a master and SPI pin control zero (SPC0) is 0 (not bidirectional mode), this pin is the serial data input. When the SPI is enabled as a slave and SPC0 = 0, this pin is the serial data output. If SPC0 = 1 to select single-wire bidirectional mode, and slave mode is selected, this pin becomes the bidirectional data I/O pin (SISO) and the bidirectional mode output enable bit determines whether the pin acts as an input (BIDIROE = 0) or an output (BIDIROE = 1). If SPC0 = 1 and master mode is selected, this pin is not used by the SPI and reverts to being a general-purpose port I/O pin.

# 15.2.4 SS — Slave Select

When the SPI is enabled as a slave, this pin is the low-true slave select input. When the SPI is enabled as a master and mode fault enable is off (MODFEN = 0), this pin is not used by the SPI and reverts to being a general-purpose port I/O pin. When the SPI is enabled as a master and MODFEN = 1, the slave select output enable bit determines whether this pin acts as the mode fault input (SSOE = 0) or as the slave select output (SSOE = 1).

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>WS  | <ul> <li>Wait or Stop Status — When the target CPU is in wait or stop mode, most BDC commands cannot function. However, the BACKGROUND command can be used to force the target CPU out of wait or stop and into active background mode where all BDC commands work. Whenever the host forces the target MCU into active background mode, the host should issue a READ_STATUS command to check that BDMACT = 1 before attempting other BDC commands.</li> <li>0 Target CPU is running user application code or in active background mode (was not in wait or stop mode when background became active)</li> <li>1 Target CPU is in wait or stop mode, or a BACKGROUND command was used to change from wait or stop to active background mode</li> </ul> |

| 1<br>WSF | <ul> <li>Wait or Stop Failure Status — This status bit is set if a memory access command failed due to the target CPU executing a wait or stop instruction at or about the same time. The usual recovery strategy is to issue a BACKGROUND command to get out of wait or stop mode into active background mode, repeat the command that failed, then return to the user program. (Typically, the host would restore CPU registers and stack values and re-execute the wait or stop instruction.)</li> <li>Memory access did not conflict with a wait or stop instruction</li> <li>Memory access command failed because the CPU entered wait or stop mode</li> </ul>                                                                                   |

| 0<br>DVF | <ul> <li>Data Valid Failure Status — This status bit is not used in the MC9S08SG8 because it does not have any slow access memory.</li> <li>0 Memory access did not conflict with a slow memory access</li> <li>1 Memory access command failed because CPU was not finished with a slow memory access</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### Table 17-2. BDCSCR Register Field Descriptions (continued)

### 17.4.1.2 BDC Breakpoint Match Register (BDCBKPT)

This 16-bit register holds the address for the hardware breakpoint in the BDC. The BKPTEN and FTS control bits in BDCSCR are used to enable and configure the breakpoint logic. Dedicated serial BDC commands (READ\_BKPT and WRITE\_BKPT) are used to read and write the BDCBKPT register but is not accessible to user programs because it is not located in the normal memory map of the MCU. Breakpoints are normally set while the target MCU is in active background mode before running the user application program. For additional information about setup and use of the hardware breakpoint logic in the BDC, refer to Section 17.2.4, "BDC Hardware Breakpoint."

### 17.4.2 System Background Debug Force Reset Register (SBDFR)

This register contains a single write-only control bit. A serial background mode command such as WRITE\_BYTE must be used to write to SBDFR. Attempts to write this register from a user program are ignored. Reads always return 0x00.

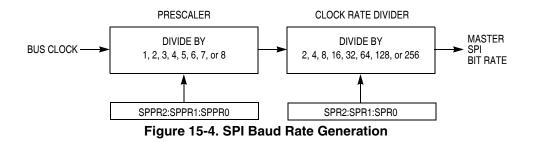

Figure A-6. Typical Run  $I_{DD}$  vs. Temperature (V<sub>DD</sub> = 5V;  $f_{bus}$  = 8MHz)

# A.12.3 SPI

Table A-15 and Figure A-14 through Figure A-17 describe the timing requirements for the SPI system.Table A-15. SPI Electrical Characteristic

| Num <sup>1</sup> C |   |                                              |                                          |                              |                                       | Unit                                 | Temp Rated <sup>3</sup> |                |  |

|--------------------|---|----------------------------------------------|------------------------------------------|------------------------------|---------------------------------------|--------------------------------------|-------------------------|----------------|--|

|                    | С | Rating <sup>2</sup>                          | Symbol                                   | Min                          | Мах                                   |                                      | Standard                | AEC Grade<br>0 |  |

| 1                  | D | Cycle time<br>Master<br>Slave                | t <sub>SCK</sub><br>t <sub>SCK</sub>     | 2<br>4                       | 2048<br>—                             | t <sub>cyc</sub><br>t <sub>cyc</sub> | х                       | x              |  |

| 2                  | D | Enable lead time<br>Master<br>Slave          | t <sub>Lead</sub><br>t <sub>Lead</sub>   | <br>1/2                      | 1/2                                   | t <sub>SCK</sub><br>t <sub>SCK</sub> | х                       | x              |  |

| 3                  | D | Enable lag time<br>Master<br>Slave           | t <sub>Lag</sub><br>t <sub>Lag</sub>     | <br>1/2                      | 1/2                                   | t <sub>SCK</sub><br>t <sub>SCK</sub> | х                       | x              |  |

| 4                  | D | Clock (SPSCK) high time<br>Master and Slave  | t <sub>SCKH</sub>                        | 1/2 t <sub>SCK</sub> – 25    | _                                     | ns                                   | х                       | x              |  |

| 5                  | D | Clock (SPSCK) low time<br>Master and Slave   | t <sub>SCKL</sub>                        | 1/2 t <sub>SCK</sub> – 25    | _                                     | ns                                   | х                       | x              |  |

| 6                  | D | Data setup time (inputs)<br>Master<br>Slave  | t <sub>SI(M)</sub><br>t <sub>SI(S)</sub> | 30<br>30                     |                                       | ns<br>ns                             | х                       | x              |  |

| 7                  | D | Data hold time (inputs)<br>Master<br>Slave   | t <sub>HI(M)</sub><br>t <sub>HI(S)</sub> | 30<br>30                     |                                       | ns<br>ns                             | х                       | x              |  |

| 8                  | D | Access time, slave <sup>4</sup>              | t <sub>A</sub>                           | 0                            | 40                                    | ns                                   | х                       | х              |  |

| 9                  | D | Disable time, slave <sup>5</sup>             | t <sub>dis</sub>                         | —                            | 40                                    | ns                                   | х                       | x              |  |

| 10                 | D | Data setup time (outputs)<br>Master<br>Slave | t <sub>SO</sub><br>t <sub>SO</sub>       | 25<br>25                     |                                       | ns<br>ns                             | х                       | x              |  |

| 11                 | D | Data hold time (outputs)<br>Master<br>Slave  | t <sub>HO</sub><br>t <sub>HO</sub>       | -10<br>-10                   |                                       | ns<br>ns                             | х                       | x              |  |

| 12                 | D | Operating frequency<br>Master<br>Slave       | f <sub>op</sub><br>f <sub>op</sub>       | f <sub>Bus</sub> /2048<br>dc | 5 <sup>6</sup><br>f <sub>Bus</sub> /4 | MHz                                  | х                       | x              |  |

<sup>1</sup> Refer to Figure A-14 through Figure A-17.

<sup>2</sup> All timing is shown with respect to 20% V<sub>DD</sub> and 70% V<sub>DD</sub>, unless noted; 100 pF load on all SPI pins. All timing assumes slew rate control disabled and high drive strength enabled for SPI output pins.

<sup>3</sup> Electrical characteristics only apply to the temperature rated devices marked with x.

<sup>4</sup> Time to data active from high-impedance state.

<sup>5</sup> Hold time to high-impedance state.

<sup>6</sup> Maximum baud rate must be limited to 5 MHz due to input filter characteristics.