Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 4                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 4x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                         |

| Supplier Device Package    | 8-SOIC                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08sg8e2csc |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Section Number**

Title

### Page

|      | 11.3.4 IIC Status Register (IICS)      |  |

|------|----------------------------------------|--|

|      | 11.3.5 IIC Data I/O Register (IICD)    |  |

|      | 11.3.6 IIC Control Register 2 (IICC2)  |  |

| 11.4 | Functional Description                 |  |

|      | 11.4.1 IIC Protocol                    |  |

|      | 11.4.2 10-bit Address                  |  |

|      | 11.4.3 General Call Address            |  |

| 11.5 | Resets                                 |  |

| 11.6 | Interrupts                             |  |

|      | 11.6.1 Byte Transfer Interrupt         |  |

|      | 11.6.2 Address Detect Interrupt        |  |

|      | 11.6.3 Arbitration Lost Interrupt      |  |

| 11.7 | Initialization/Application Information |  |

## Chapter 12 Modulo Timer (S08MTIMV1)

| 12.1 | Introduction                                       |  |

|------|----------------------------------------------------|--|

|      | 12.1.1 MTIM Configuration Information              |  |

|      | 12.1.2 Features                                    |  |

|      | 12.1.3 Modes of Operation                          |  |

|      | 12.1.4 Block Diagram                               |  |

| 12.2 | External Signal Description                        |  |

| 12.3 | Register Definition                                |  |

|      | 12.3.1 MTIM Status and Control Register (MTIMSC)   |  |

|      | 12.3.2 MTIM Clock Configuration Register (MTIMCLK) |  |

|      | 12.3.3 MTIM Counter Register (MTIMCNT)             |  |

|      | 12.3.4 MTIM Modulo Register (MTIMMOD)              |  |

| 12.4 | Functional Description                             |  |

|      | 12.4.1 MTIM Operation Example                      |  |

|      |                                                    |  |

## Chapter 13 Real-Time Counter (S08RTCV1)

| 13.1 | Introduction                                   |     |

|------|------------------------------------------------|-----|

|      | 13.1.1 Features                                | 191 |

|      | 13.1.2 Modes of Operation                      | 191 |

|      | 13.1.3 Block Diagram                           |     |

| 13.2 | External Signal Description                    |     |

| 13.3 | Register Definition                            |     |

|      | 13.3.1 RTC Status and Control Register (RTCSC) | 193 |

|      | 13.3.2 RTC Counter Register (RTCCNT)           | 194 |

|      | 13.3.3 RTC Modulo Register (RTCMOD)            |     |

| 13.4 | Functional Description                         | 194 |

|      |                                                |     |

## 2.2 Recommended System Connections

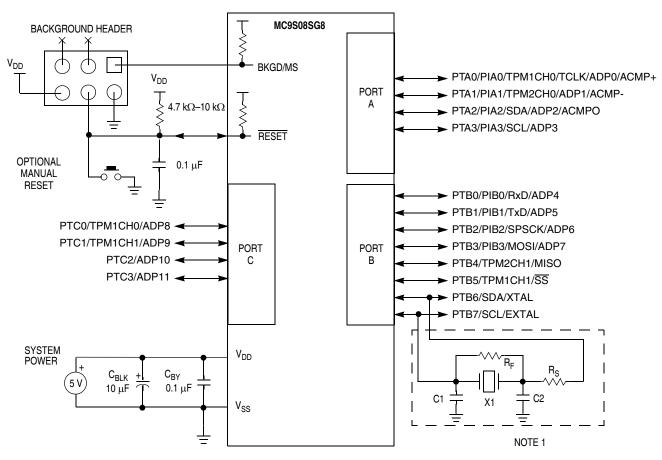

Figure 2-4 shows pin connections that are common to MC9S08SG8 application systems.

NOTES:

- 1. External crystal circuit not required if using the internal clock option.

- RESET pin can only be used to reset into user mode, you can not enter BDM using RESET pin. BDM can be entered by holding MS low during POR or writing a 1 to BDFR in SBDFR with MS low after issuing BDM command.

- 3. RC filter on RESET pin recommended for noisy environments.

#### Figure 2-4. Basic System Connections

### 2.2.1 Power

$V_{DD}$  and  $V_{SS}$  are the primary power supply pins for the MCU. This voltage source supplies power to all I/O buffer circuitry, ACMP and ADC modules, and to an internal voltage regulator. The internal voltage regulator provides regulated lower-voltage source to the CPU and other internal circuitry of the MCU.

Typically, application systems have two separate capacitors across the power pins. In this case, there should be a bulk electrolytic capacitor, such as a  $10-\mu$ F tantalum capacitor, to provide bulk charge storage

**Chapter 4 Memory**

Table 4-2. Direct-Page Register Summary (Sheet 1 of 3)

| Address                            | Register<br>Name | Bit 7  | 6       | 5      | 4      | 3      | 2      | 1      | Bit 0  |

|------------------------------------|------------------|--------|---------|--------|--------|--------|--------|--------|--------|

| 0x00 <b>00</b>                     | PTAD             | 0      | 0       | _      | _      | PTAD3  | PTAD2  | PTAD1  | PTAD0  |

| 0x00 <b>01</b>                     | PTADD            | 0      | 0       |        | _      | PTADD3 | PTADD2 | PTADD1 | PTADD0 |

| 0x00 <b>02</b>                     | PTBD             | PTBD7  | PTBD6   | PTBD5  | PTBD4  | PTBD3  | PTBD2  | PTBD1  | PTBD0  |

| 0x00 <b>03</b>                     | PTBDD            | PTBDD7 | PTBDD6  | PTBDD5 | PTBDD4 | PTBDD3 | PTBDD2 | PTBDD1 | PTBDD0 |

| 0x00 <b>04</b>                     | PTCD             | 0      | 0       | 0      | 0      | PTCD3  | PTCD2  | PTCD1  | PTCD0  |

| 0x00 <b>05</b>                     | PTCDD            | 0      | 0       | 0      | 0      | PTCDD3 | PTCDD2 | PTCDD1 | PTCDD0 |

| 0x00 <b>06</b> –<br>0x00 <b>0D</b> | Reserved         | _      | _       | _      | _      |        | _      | _      | —      |

| 0x00 <b>0E</b>                     | ACMPSC           | ACME   | ACBGS   | ACF    | ACIE   | ACO    | ACOPE  | ACMOD1 | ACMOD0 |

| 0x00 <b>0F</b>                     | Reserved         |        | _       |        | _      |        |        | —      | —      |

| 0x00 <b>10</b>                     | ADCSC1           | COCO   | AIEN    | ADCO   |        |        | ADCH   |        | •      |

| 0x00 <b>11</b>                     | ADCSC2           | ADACT  | ADTRG   | ACFE   | ACFGT  | —      | —      | —      | —      |

| 0x00 <b>12</b>                     | ADCRH            | 0      | 0       | 0      | 0      | 0      | 0      | ADR9   | ADR8   |

| 0x00 <b>13</b>                     | ADCRL            | ADR7   | ADR6    | ADR5   | ADR4   | ADR3   | ADR2   | ADR1   | ADR0   |

| 0x00 <b>14</b>                     | ADCVH            | 0      | 0       | 0      | 0      | 0      | 0      | ADCV9  | ADCV8  |

| 0x00 <b>15</b>                     | ADCVL            | ADCV7  | ADCV6   | ADCV5  | ADCV4  | ADCV3  | ADCV2  | ADCV1  | ADCV0  |

| 0x00 <b>16</b>                     | ADCFG            | ADLPC  | AD      | VIV    | ADLSMP | MODE   |        | ADICLK |        |

| 0x00 <b>17</b>                     | APCTL1           | ADPC7  | ADPC6   | ADPC5  | ADPC4  | ADPC3  | ADPC2  | ADPC1  | ADPC0  |

| 0x00 <b>18</b>                     | APCTL2           | 0      | 0       | 0      | 0      | ADPC11 | ADPC10 | ADPC9  | ADPC8  |

| 0x001 <b>9</b> –<br>0x001 <b>B</b> | Reserved         | _      | _       | _      | _      | _      | _      | _      | _      |

| 0x001 <b>C</b>                     | MTIMSC           | TOF    | TOIE    | TRST   | TSTP   | 0      | 0      | 0      | 0      |

| 0x001 <b>D</b>                     | MTIMCLK          | 0      | 0       | CL     | KS     |        | P      | S      |        |

| 0x001E                             | MTIMCNT          |        |         |        | CI     | NT     |        |        |        |

| 0x001F                             | MTIMMOD          | -      |         |        | МС     | DD     |        |        |        |

| 0x00 <b>20</b>                     | TPM1SC           | TOF    | TOIE    | CPWMS  | CLKSB  | CLKSA  | PS2    | PS1    | PS0    |

| 0x00 <b>21</b>                     | TPM1CNTH         | Bit 15 | 14      | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| 0x00 <b>22</b>                     | TPM1CNTL         | Bit 7  | 6       | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| 0x00 <b>23</b>                     | TPM1MODH         | Bit 15 | 14      | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| 0x00 <b>24</b>                     | TPM1MODL         | Bit 7  | 6       | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| 0x00 <b>25</b>                     | TPM1C0SC         | CH0F   | CH0IE   | MS0B   | MS0A   | ELS0B  | ELS0A  | 0      | 0      |

| 0x00 <b>26</b>                     | TPM1C0VH         | Bit 15 | 14      | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| 0x00 <b>27</b>                     | TPM1C0VL         | Bit 7  | 6       | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| 0x00 <b>28</b>                     | TPM1C1SC         | CH1F   | CH1IE   | MS1B   | MS1A   | ELS1B  | ELS1A  | 0      | 0      |

| 0x00 <b>29</b>                     | TPM1C1VH         | Bit 15 | 14      | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| 0x00 <b>2A</b>                     | TPM1C1VL         | Bit 7  | 6       | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| 0x00 <b>2B</b> –<br>0x00 <b>37</b> | Reserved         | —      | —       | —      | —      | —      | —      | _      | —      |

| 0x00 <b>38</b>                     | SCIBDH           | LBKDIE | RXEDGIE | 0      | SBR12  | SBR11  | SBR10  | SBR9   | SBR8   |

MC9S08SG8 MCU Series Data Sheet, Rev. 8

Chapter 6 Parallel Input/Output Control

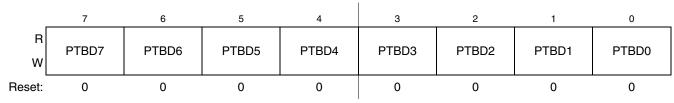

## 6.6.2 Port B Registers

Port B is controlled by the registers listed below.

### 6.6.2.1 Port B Data Register (PTBD)

### Figure 6-11. Port B Data Register (PTBD)

#### Table 6-10. PTBD Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBD[7:0] | Port B Data Register Bits — For port B pins that are inputs, reads return the logic level on the pin. For port B pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port B pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTBD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pull-ups/pull-downs disabled. |

### 6.6.2.2 Port B Data Direction Register (PTBDD)

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTBDD7 | PTBDD6 | PTBDD5 | PTBDD4 | PTBDD3 | PTBDD2 | PTBDD1 | PTBDD0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

#### Figure 6-12. Port B Data Direction Register (PTBDD)

### Table 6-11. PTBDD Register Field Descriptions

| Field             | Description                                                                                                                                                                         |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7:0<br>PTBDD[7:0] | <b>Data Direction for Port B Bits</b> — These read/write bits control the direction of port B pins and what is read for PTBD reads.                                                 |  |  |  |

|                   | <ul> <li>0 Input (output driver disabled) and reads return the pin value.</li> <li>1 Output driver enabled for port B bit n and PTBD reads return the contents of PTBDn.</li> </ul> |  |  |  |

# Chapter 9 Analog-to-Digital Converter (S08ADCV1)

## 9.1 Introduction

The 10-bit analog-to-digital converter (ADC) is a successive approximation ADC designed for operation within an integrated microcontroller system-on-chip.

### NOTE

The MC9S08SG8 Family of devices do not include stop1 mode.

The ADC channel assignments, alternate clock function, and hardware trigger function are configured as described below for the MC9S08SG8 family of devices.

### 9.1.1 Channel Assignments

The ADC channel assignments for the MC9S08SG8 devices are shown in Table 9-1. Reserved channels convert to an unknown value.

| ADCH  | Channel             | Input           |

|-------|---------------------|-----------------|

| 00000 | AD0                 | PTA0/ADP0       |

| 00001 | AD1                 | PTA1/ADP1       |

| 00010 | AD2                 | PTA2/ADP2       |

| 00011 | AD3                 | PTA3/ADP3       |

| 00100 | AD4                 | PTB0/ADP4       |

| 00101 | AD5                 | PTB1/ADP5       |

| 00110 | 00110 AD6 PTB2/ADP6 |                 |

| 00111 | AD7                 | PTB3/ADP7       |

| 01000 | AD8                 | PTC0/ADP8       |

| 01001 | AD9                 | PTC1/ADP9       |

| 01010 | AD10                | PTC2/ADP10      |

| 01011 | AD11                | PTC3/ADP11      |

| 01100 | AD12                | V <sub>SS</sub> |

| 01101 | AD13                | V <sub>SS</sub> |

| 01110 | AD14                | V <sub>SS</sub> |

| 01111 | AD15                | V <sub>SS</sub> |

| ADCH  | Channel           | Input                           |

|-------|-------------------|---------------------------------|

| 10000 | AD16              | V <sub>SS</sub>                 |

| 10001 | AD17              | V <sub>SS</sub>                 |

| 10010 | AD18              | V <sub>SS</sub>                 |

| 10011 | AD19              | V <sub>SS</sub>                 |

| 10100 | AD20              | V <sub>SS</sub>                 |

| 10101 | AD21              | Reserved                        |

| 10110 | AD22              | Reserved                        |

| 10111 | AD23              | Reserved                        |

| 11000 | AD24              | Reserved                        |

| 11001 | AD25              | Reserved                        |

| 11010 | AD26              | Temperature Sensor <sup>1</sup> |

| 11011 | AD27              | Internal Bandgap <sup>2</sup>   |

| 11100 | -                 | Reserved                        |

| 11101 | V <sub>REFH</sub> | V <sub>DD</sub>                 |

| 11110 | V <sub>REFL</sub> | V <sub>SS</sub>                 |

| 11111 | Module Disabled   | None                            |

<sup>1</sup> For information, see Section 9.1.4, "Temperature Sensor".

<sup>2</sup> Requires BGBE =1 in SPMSC1 see Section 5.7.7, "System Power Management Status and Control 2 Register (SPMSC2)". For value of bandgap voltage reference see A.6, "DC Characteristics".

#### Chapter 9 Analog-to-Digital Converter (S08ADCV1)

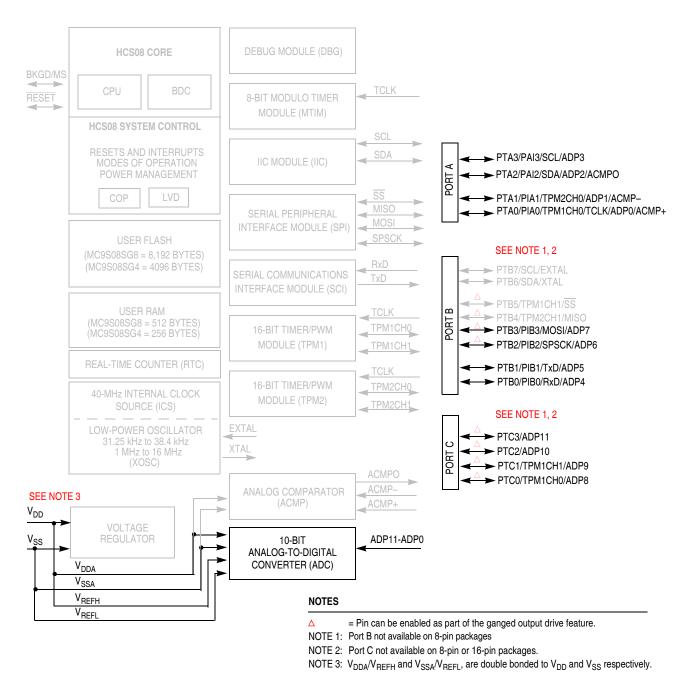

Figure 9-1. MC9S08SG8 Block Diagram with ADC Module Highlighted

| ADICLK | Selected Clock Source      |  |

|--------|----------------------------|--|

| 00     | Bus clock                  |  |

| 01     | Bus clock divided by 2     |  |

| 10     | Alternate clock (ALTCLK)   |  |

| 11     | Asynchronous clock (ADACK) |  |

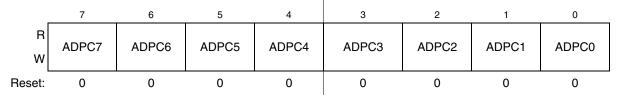

## 9.3.8 Pin Control 1 Register (APCTL1)

The pin control registers are used to disable the I/O port control of MCU pins used as analog inputs. APCTL1 is used to control the pins associated with channels 0–7 of the ADC module.

Figure 9-11. Pin Control 1 Register (APCTL1)

| Field      | Field Description                                                                                                                                                                    |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>ADPC7 | <ul> <li>ADC Pin Control 7 — ADPC7 is used to control the pin associated with channel AD7.</li> <li>0 AD7 pin I/O control enabled</li> <li>1 AD7 pin I/O control disabled</li> </ul> |  |

| 6<br>ADPC6 | <ul> <li>ADC Pin Control 6 — ADPC6 is used to control the pin associated with channel AD6.</li> <li>0 AD6 pin I/O control enabled</li> <li>1 AD6 pin I/O control disabled</li> </ul> |  |

| 5<br>ADPC5 | <ul> <li>ADC Pin Control 5 — ADPC5 is used to control the pin associated with channel AD5.</li> <li>0 AD5 pin I/O control enabled</li> <li>1 AD5 pin I/O control disabled</li> </ul> |  |

| 4<br>ADPC4 | <ul> <li>ADC Pin Control 4 — ADPC4 is used to control the pin associated with channel AD4.</li> <li>0 AD4 pin I/O control enabled</li> <li>1 AD4 pin I/O control disabled</li> </ul> |  |

| 3<br>ADPC3 | <ul> <li>ADC Pin Control 3 — ADPC3 is used to control the pin associated with channel AD3.</li> <li>0 AD3 pin I/O control enabled</li> <li>1 AD3 pin I/O control disabled</li> </ul> |  |

| 2<br>ADPC2 | <ul> <li>ADC Pin Control 2 — ADPC2 is used to control the pin associated with channel AD2.</li> <li>0 AD2 pin I/O control enabled</li> <li>1 AD2 pin I/O control disabled</li> </ul> |  |

#### Table 9-9. APCTL1 Register Field Descriptions

| Field      | Description                                                                                                                                                                          |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1<br>ADPC9 | <ul> <li>ADC Pin Control 9 — ADPC9 is used to control the pin associated with channel AD9.</li> <li>0 AD9 pin I/O control enabled</li> <li>1 AD9 pin I/O control disabled</li> </ul> |  |

| 0<br>ADPC8 | <ul> <li>ADC Pin Control 8 — ADPC8 is used to control the pin associated with channel AD8.</li> <li>0 AD8 pin I/O control enabled</li> <li>1 AD8 pin I/O control disabled</li> </ul> |  |

#### Table 9-10. APCTL2 Register Field Descriptions (continued)

## 9.3.10 Pin Control 3 Register (APCTL3)

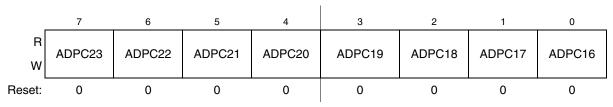

APCTL3 is used to control channels 16–23 of the ADC module.

Figure 9-13. Pin Control 3 Register (APCTL3)

#### Table 9-11. APCTL3 Register Field Descriptions

| Field       | Description                                                                                                                                                                               |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>ADPC23 | <ul> <li>ADC Pin Control 23 — ADPC23 is used to control the pin associated with channel AD23.</li> <li>0 AD23 pin I/O control enabled</li> <li>1 AD23 pin I/O control disabled</li> </ul> |  |

| 6<br>ADPC22 | <ul> <li>ADC Pin Control 22 — ADPC22 is used to control the pin associated with channel AD22.</li> <li>0 AD22 pin I/O control enabled</li> <li>1 AD22 pin I/O control disabled</li> </ul> |  |

| 5<br>ADPC21 | <ul> <li>ADC Pin Control 21 — ADPC21 is used to control the pin associated with channel AD21.</li> <li>0 AD21 pin I/O control enabled</li> <li>1 AD21 pin I/O control disabled</li> </ul> |  |

| 4<br>ADPC20 | <ul> <li>ADC Pin Control 20 — ADPC20 is used to control the pin associated with channel AD20.</li> <li>0 AD20 pin I/O control enabled</li> <li>1 AD20 pin I/O control disabled</li> </ul> |  |

| 3<br>ADPC19 | <ul> <li>ADC Pin Control 19 — ADPC19 is used to control the pin associated with channel AD19.</li> <li>0 AD19 pin I/O control enabled</li> <li>1 AD19 pin I/O control disabled</li> </ul> |  |

| 2<br>ADPC18 | <ul> <li>ADC Pin Control 18 — ADPC18 is used to control the pin associated with channel AD18.</li> <li>0 AD18 pin I/O control enabled</li> <li>1 AD18 pin I/O control disabled</li> </ul> |  |

are too fast, then the clock must be divided to the appropriate frequency. This divider is specified by the ADIV bits and can be divide-by 1, 2, 4, or 8.

## 9.4.2 Input Select and Pin Control

The pin control registers (APCTL3, APCTL2, and APCTL1) are used to disable the I/O port control of the pins used as analog inputs. When a pin control register bit is set, the following conditions are forced for the associated MCU pin:

- The output buffer is forced to its high impedance state.

- The input buffer is disabled. A read of the I/O port returns a zero for any pin with its input buffer disabled.

- The pullup is disabled.

### 9.4.3 Hardware Trigger

The ADC module has a selectable asynchronous hardware conversion trigger, ADHWT, that is enabled when the ADTRG bit is set. This source is not available on all MCUs. Consult the module introduction for information on the ADHWT source specific to this MCU.

When ADHWT source is available and hardware trigger is enabled (ADTRG=1), a conversion is initiated on the rising edge of ADHWT. If a conversion is in progress when a rising edge occurs, the rising edge is ignored. In continuous convert configuration, only the initial rising edge to launch continuous conversions is observed. The hardware trigger function operates in conjunction with any of the conversion modes and configurations.

## 9.4.4 Conversion Control

Conversions can be performed in either 10-bit mode or 8-bit mode as determined by the MODE bits. Conversions can be initiated by either a software or hardware trigger. In addition, the ADC module can be configured for low power operation, long sample time, continuous conversion, and automatic compare of the conversion result to a software determined compare value.

### 9.4.4.1 Initiating Conversions

A conversion is initiated:

- Following a write to ADCSC1 (with ADCH bits not all 1s) if software triggered operation is selected.

- Following a hardware trigger (ADHWT) event if hardware triggered operation is selected.

- Following the transfer of the result to the data registers when continuous conversion is enabled.

If continuous conversions are enabled a new conversion is automatically initiated after the completion of the current conversion. In software triggered operation, continuous conversions begin after ADCSC1 is written and continue until aborted. In hardware triggered operation, continuous conversions begin after a hardware trigger event and continue until aborted.

### 10.4.1.5 FLL Bypassed External (FBE)

The FLL bypassed external (FBE) mode is entered when all the following conditions occur:

- CLKS bits are written to 10.

- IREFS bit is written to 0.

- BDM mode is active or LP bit is written to 0.

In FLL bypassed external mode, the ICSOUT clock is derived from the external reference clock. The FLL clock is controlled by the external reference clock, and the FLL loop will lock the FLL frequency to 1024 times the reference frequency, as selected by the RDIV bits, so that the ICSLCLK will be available for BDC communications, and the external reference clock is enabled.

### 10.4.1.6 FLL Bypassed External Low Power (FBELP)

The FLL bypassed external low power (FBELP) mode is entered when all the following conditions occur:

- CLKS bits are written to 10.

- IREFS bit is written to 0.

- BDM mode is not active and LP bit is written to 1.

In FLL bypassed external low power mode, the ICSOUT clock is derived from the external reference clock and the FLL is disabled. The ICSLCLK will be not be available for BDC communications. The external reference clock is enabled.

### 10.4.1.7 Stop

Stop mode is entered whenever the MCU enters a STOP state. In this mode, all ICS clock signals are static except in the following cases:

ICSIRCLK will be active in stop mode when all the following conditions occur:

- IRCLKEN bit is written to 1

- IREFSTEN bit is written to 1

ICSERCLK will be active in stop mode when all the following conditions occur:

- ERCLKEN bit is written to 1

- EREFSTEN bit is written to 1

### 10.4.2 Mode Switching

When switching between FLL engaged internal (FEI) and FLL engaged external (FEE) modes the IREFS bit can be changed at anytime, but the RDIV bits must be changed simultaneously so that the resulting frequency stays in the range of 31.25 kHz to 39.0625 kHz. After a change in the IREFS value the FLL will begin locking again after a few full cycles of the resulting divided reference frequency. The completion of the switch is shown by the IREFST bit.

#### Table 11-7. IICS Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>TCF   | <ul> <li>Transfer Complete Flag. This bit is set on the completion of a byte transfer. This bit is only valid during or immediately following a transfer to the IIC module or from the IIC module. The TCF bit is cleared by reading the IICD register in receive mode or writing to the IICD in transmit mode.</li> <li>0 Transfer in progress</li> <li>1 Transfer complete</li> </ul>                           |  |

| 6<br>IAAS  | <ul> <li>Addressed as a Slave. The IAAS bit is set when the calling address matches the programmed slave address or when the GCAEN bit is set and a general call is received. Writing the IICC register clears this bit.</li> <li>0 Not addressed</li> <li>1 Addressed as a slave</li> </ul>                                                                                                                      |  |

| 5<br>BUSY  | <ul> <li>Bus Busy. The BUSY bit indicates the status of the bus regardless of slave or master mode. The BUSY bit is set when a start signal is detected and cleared when a stop signal is detected.</li> <li>0 Bus is idle</li> <li>1 Bus is busy</li> </ul>                                                                                                                                                      |  |

| 4<br>ARBL  | <ul> <li>Arbitration Lost. This bit is set by hardware when the arbitration procedure is lost. The ARBL bit must be cleared by software by writing a 1 to it.</li> <li>0 Standard bus operation</li> <li>1 Loss of arbitration</li> </ul>                                                                                                                                                                         |  |

| 2<br>SRW   | <ul> <li>Slave Read/Write. When addressed as a slave, the SRW bit indicates the value of the R/W command bit of the calling address sent to the master.</li> <li>O Slave receive, master writing to slave</li> <li>1 Slave transmit, master reading from slave</li> </ul>                                                                                                                                         |  |

| 1<br>IICIF | <ul> <li>IIC Interrupt Flag. The IICIF bit is set when an interrupt is pending. This bit must be cleared by software, by writing a 1 to it in the interrupt routine. One of the following events can set the IICIF bit:</li> <li>One byte transfer completes</li> <li>Match of slave address to calling address</li> <li>Arbitration lost</li> <li>0 No interrupt pending</li> <li>1 Interrupt pending</li> </ul> |  |

| 0<br>RXAK  | <ul> <li>Receive Acknowledge. When the RXAK bit is low, it indicates an acknowledge signal has been received after the completion of one byte of data transmission on the bus. If the RXAK bit is high it means that no acknowledge signal is detected.</li> <li>0 Acknowledge received</li> <li>1 No acknowledge received</li> </ul>                                                                             |  |

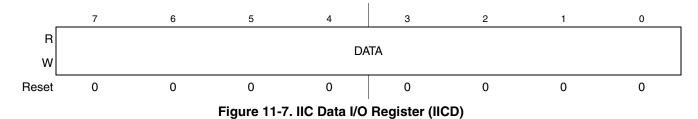

## 11.3.5 IIC Data I/O Register (IICD)

Inter-Integrated Circuit (S08IICV2)

| Table 11-8. IICD | <b>Field Descriptions</b> |

|------------------|---------------------------|

|------------------|---------------------------|

| Field       | Field Description                                                                                                                                                                                                                          |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7–0<br>DATA | <b>Data</b> — In master transmit mode, when data is written to the IICD, a data transfer is initiated. The most significant bit is sent first. In master receive mode, reading this register initiates receiving of the next byte of data. |  |

### NOTE

When transitioning out of master receive mode, the IIC mode should be switched before reading the IICD register to prevent an inadvertent initiation of a master receive data transfer.

In slave mode, the same functions are available after an address match has occurred.

The TX bit in IICC must correctly reflect the desired direction of transfer in master and slave modes for the transmission to begin. For instance, if the IIC is configured for master transmit but a master receive is desired, reading the IICD does not initiate the receive.

Reading the IICD returns the last byte received while the IIC is configured in master receive or slave receive modes. The IICD does not reflect every byte transmitted on the IIC bus, nor can software verify that a byte has been written to the IICD correctly by reading it back.

In master transmit mode, the first byte of data written to IICD following assertion of MST is used for the address transfer and should comprise of the calling address (in bit 7 to bit 1) concatenated with the required  $R/\overline{W}$  bit (in position bit 0).

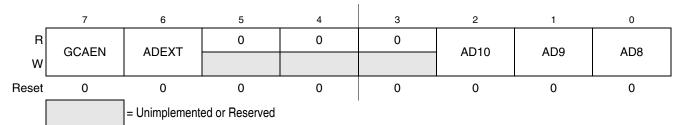

## 11.3.6 IIC Control Register 2 (IICC2)

Figure 11-8. IIC Control Register (IICC2)

### Table 11-9. IICC2 Field Descriptions

| Field           | Description                                                                                                                                                                                     |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>GCAEN      | <ul> <li>General Call Address Enable. The GCAEN bit enables or disables general call address.</li> <li>0 General call address is disabled</li> <li>1 General call address is enabled</li> </ul> |  |

| 6<br>ADEXT      | <ul> <li>Address Extension. The ADEXT bit controls the number of bits used for the slave address.</li> <li>0 7-bit address scheme</li> <li>1 10-bit address scheme</li> </ul>                   |  |

| 2–0<br>AD[10:8] | Slave Address. The AD[10:8] field contains the upper three bits of the slave address in the 10-bit address scheme. This field is only valid when the ADEXT bit is set.                          |  |

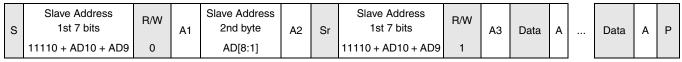

#### MC9S08SG8 MCU Series Data Sheet, Rev. 8

After a repeated start condition (Sr), all other slave devices also compare the first seven bits of the first byte of the slave address with their own addresses and test the eighth  $(R/\overline{W})$  bit. However, none of them are addressed because  $R/\overline{W} = 1$  (for 10-bit devices) or the 11110XX slave address (for 7-bit devices) does not match.

Table 11-11. Master-Receiver Addresses a Slave-Transmitter with a 10-bit Address

After the master-receiver has sent the first byte of the 10-bit address, the slave-transmitter sees an IIC interrupt. Software must ensure the contents of IICD are ignored and not treated as valid data for this interrupt.

## 11.4.3 General Call Address

General calls can be requested in 7-bit address or 10-bit address. If the GCAEN bit is set, the IIC matches the general call address as well as its own slave address. When the IIC responds to a general call, it acts as a slave-receiver and the IAAS bit is set after the address cycle. Software must read the IICD register after the first byte transfer to determine whether the address matches is its own slave address or a general call. If the value is 00, the match is a general call. If the GCAEN bit is clear, the IIC ignores any data supplied from a general call address by not issuing an acknowledgement.

## 11.5 Resets

The IIC is disabled after reset. The IIC cannot cause an MCU reset.

## 11.6 Interrupts

The IIC generates a single interrupt.

An interrupt from the IIC is generated when any of the events in Table 11-12 occur, provided the IICIE bit is set. The interrupt is driven by bit IICIF (of the IIC status register) and masked with bit IICIE (of the IIC control register). The IICIF bit must be cleared by software by writing a 1 to it in the interrupt routine. You can determine the interrupt type by reading the status register.

| Interrupt Source                  | Status | Flag  | Local Enable |

|-----------------------------------|--------|-------|--------------|

| Complete 1-byte transfer          | TCF    | IICIF | IICIE        |

| Match of received calling address | IAAS   | IICIF | IICIE        |

| Arbitration Lost                  | ARBL   | IICIF | IICIE        |

Table 11-12. Interrupt Summary

### 11.6.1 Byte Transfer Interrupt

The TCF (transfer complete flag) bit is set at the falling edge of the ninth clock to indicate the completion of byte transfer.

Inter-Integrated Circuit (S08IICV2)

## 11.6.2 Address Detect Interrupt

When the calling address matches the programmed slave address (IIC address register) or when the GCAEN bit is set and a general call is received, the IAAS bit in the status register is set. The CPU is interrupted, provided the IICIE is set. The CPU must check the SRW bit and set its Tx mode accordingly.

## 11.6.3 Arbitration Lost Interrupt

The IIC is a true multi-master bus that allows more than one master to be connected on it. If two or more masters try to control the bus at the same time, the relative priority of the contending masters is determined by a data arbitration procedure. The IIC module asserts this interrupt when it loses the data arbitration process and the ARBL bit in the status register is set.

Arbitration is lost in the following circumstances:

- SDA sampled as a low when the master drives a high during an address or data transmit cycle.

- SDA sampled as a low when the master drives a high during the acknowledge bit of a data receive cycle.

- A start cycle is attempted when the bus is busy.

- A repeated start cycle is requested in slave mode.

- A stop condition is detected when the master did not request it.

This bit must be cleared by software writing a 1 to it.

Real-Time Counter (S08RTCV1)

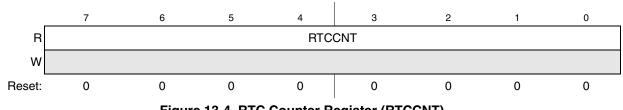

# 13.3.2 RTC Counter Register (RTCCNT)

RTCCNT is the read-only value of the current RTC count of the 8-bit counter.

Figure 13-4. RTC Counter Register (RTCCNT)

#### Table 13-4. RTCCNT Field Descriptions

| Field | Description                                                                                                                                                                                                                      |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|       | RTC Count. These eight read-only bits contain the current value of the 8-bit counter. Writes have no effect to this register. Reset, writing to RTCMOD, or writing different values to RTCLKS and RTCPS clear the count to 0x00. |  |

## 13.3.3 RTC Modulo Register (RTCMOD)

Table 13-5. RTCMOD Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                              |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:0<br>RTCMOD | RTC Modulo. These eight read/write bits contain the modulo value used to reset the count to 0x00 upon a compare match and set the RTIF status bit. A value of 0x00 sets the RTIF bit on each rising edge of the prescaler output. Writing to RTCMOD resets the prescaler and the RTCCNT counters to 0x00. Reset sets the modulo to 0x00. |  |

## 13.4 Functional Description

The RTC is composed of a main 8-bit up-counter with an 8-bit modulo register, a clock source selector, and a prescaler block with binary-based and decimal-based selectable values. The module also contains software selectable interrupt logic.

After any MCU reset, the counter is stopped and reset to 0x00, the modulus register is set to 0x00, and the prescaler is off. The 1-kHz internal oscillator clock is selected as the default clock source. To start the prescaler, write any value other than zero to the prescaler select bits (RTCPS).

Three clock sources are software selectable: the low power oscillator clock (LPO), the external clock (ERCLK), and the internal clock (IRCLK). The RTC clock select bits (RTCLKS) select the desired clock source. If a different value is written to RTCLKS, the prescaler and RTCCNT counters are reset to 0x00.

Serial Peripheral Interface (S08SPIV3)

| SPPR2:SPPR1:SPPR0 | Prescaler Divisor |

|-------------------|-------------------|

| 0:0:0             | 1                 |

| 0:0:1             | 2                 |

| 0:1:0             | 3                 |

| 0:1:1             | 4                 |

| 1:0:0             | 5                 |

| 1:0:1             | 6                 |

| 1:1:0             | 7                 |

| 1:1:1             | 8                 |

#### Table 15-5. SPI Baud Rate Prescaler Divisor

#### Table 15-6. SPI Baud Rate Divisor

| SPR2:SPR1:SPR0 | Rate Divisor |  |  |  |  |  |

|----------------|--------------|--|--|--|--|--|

| 0:0:0          | 2            |  |  |  |  |  |

| 0:0:1          | 4            |  |  |  |  |  |

| 0:1:0          | 8            |  |  |  |  |  |

| 0:1:1          | 16           |  |  |  |  |  |

| 1:0:0          | 32           |  |  |  |  |  |

| 1:0:1          | 64           |  |  |  |  |  |

| 1:1:0          | 128          |  |  |  |  |  |

| 1:1:1          | 256          |  |  |  |  |  |

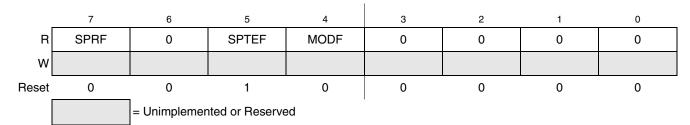

## 15.4.4 SPI Status Register (SPIS)

This register has three read-only status bits. Bits 6, 3, 2, 1, and 0 are not implemented and always read 0. Writes have no meaning or effect.

Figure 15-8. SPI Status Register (SPIS)

# 17.3 On-Chip Debug System (DBG)

Because HCS08 devices do not have external address and data buses, the most important functions of an in-circuit emulator have been built onto the chip with the MCU. The debug system consists of an 8-stage FIFO that can store address or data bus information, and a flexible trigger system to decide when to capture bus information and what information to capture. The system relies on the single-wire background debug system to access debug control registers and to read results out of the eight stage FIFO.

The debug module includes control and status registers that are accessible in the user's memory map. These registers are located in the high register space to avoid using valuable direct page memory space.

Most of the debug module's functions are used during development, and user programs rarely access any of the control and status registers for the debug module. The one exception is that the debug system can provide the means to implement a form of ROM patching. This topic is discussed in greater detail in Section 17.3.6, "Hardware Breakpoints."

## 17.3.1 Comparators A and B

Two 16-bit comparators (A and B) can optionally be qualified with the R/W signal and an opcode tracking circuit. Separate control bits allow you to ignore R/W for each comparator. The opcode tracking circuitry optionally allows you to specify that a trigger will occur only if the opcode at the specified address is actually executed as opposed to only being read from memory into the instruction queue. The comparators are also capable of magnitude comparisons to support the inside range and outside range trigger modes. Comparators are disabled temporarily during all BDC accesses.

The A comparator is always associated with the 16-bit CPU address. The B comparator compares to the CPU address or the 8-bit CPU data bus, depending on the trigger mode selected. Because the CPU data bus is separated into a read data bus and a write data bus, the RWAEN and RWA control bits have an additional purpose, in full address plus data comparisons they are used to decide which of these buses to use in the comparator B data bus comparisons. If RWAEN = 1 (enabled) and RWA = 0 (write), the CPU's write data bus is used. Otherwise, the CPU's read data bus is used.

The currently selected trigger mode determines what the debugger logic does when a comparator detects a qualified match condition. A match can cause:

- Generation of a breakpoint to the CPU

- Storage of data bus values into the FIFO

- Starting to store change-of-flow addresses into the FIFO (begin type trace)

- Stopping the storage of change-of-flow addresses into the FIFO (end type trace)

## 17.3.2 Bus Capture Information and FIFO Operation

The usual way to use the FIFO is to setup the trigger mode and other control options, then arm the debugger. When the FIFO has filled or the debugger has stopped storing data into the FIFO, you would read the information out of it in the order it was stored into the FIFO. Status bits indicate the number of words of valid information that are in the FIFO as data is stored into it. If a trace run is manually halted by writing 0 to ARM before the FIFO is full (CNT = 1:0:0:0), the information is shifted by one position and

Appendix A Electrical Characteristics

# A.6 DC Characteristics

This section includes information about power supply requirements and I/O pin characteristics.

### Table A-6. DC Characteristics

|     |   |                                                               | Symbol           | Condition                                                    | Min                    | Typ <sup>1</sup> | Max                    | Unit | Temp Rated <sup>2</sup> |                   |

|-----|---|---------------------------------------------------------------|------------------|--------------------------------------------------------------|------------------------|------------------|------------------------|------|-------------------------|-------------------|

| Num | С | Characteristic                                                |                  |                                                              |                        |                  |                        |      | Stand<br>ard            | AEC<br>Grade<br>0 |

| 1   | _ | Operating voltage                                             | V <sub>DD</sub>  | —                                                            | 2.7                    | _                | 5.5                    | V    | х                       | х                 |

|     | С | All I/O pins,                                                 | V <sub>OH</sub>  | 5 V, I <sub>Load</sub> = -4 mA                               | V <sub>DD</sub> – 1.5  |                  | —                      | V    | х                       | х                 |

|     | Ρ | low-drive strength                                            |                  | 5 V, I <sub>Load</sub> = -2 mA                               | V <sub>DD</sub> – 0.8  |                  | —                      |      | х                       | x                 |

| 2   | С | Output high                                                   |                  | 3 V, I <sub>Load</sub> = -1 mA                               | V <sub>DD</sub> – 0.8  |                  | —                      |      | х                       | х                 |

|     | С | voltage                                                       |                  | 5 V, I <sub>Load</sub> = -20 mA                              | V <sub>DD</sub> – 1.5  |                  | —                      |      | х                       | х                 |

|     | Ρ | All I/O pins,                                                 |                  | 5 V, I <sub>Load</sub> = -10 mA                              | V <sub>DD</sub> - 0.8  |                  | —                      |      | х                       | x                 |

|     | С | high-drive strength                                           |                  | 3 V, I <sub>Load</sub> = -5 mA                               | V <sub>DD</sub> – 0.8  | —                | —                      |      | х                       | x                 |

| 2   | с | Output high Max total I <sub>OH</sub> for                     | I <sub>OHT</sub> | V <sub>OUT</sub> < V <sub>DD</sub>                           | 0                      | _                | -100                   | mA   | Х                       |                   |

| 3   | C | current all ports                                             |                  |                                                              |                        |                  | -50                    |      |                         | х                 |

|     | С | All I/O pins                                                  |                  | 5 V, I <sub>Load</sub> = 4 mA                                | —                      | _                | 1.5                    |      | х                       | х                 |

|     | Ρ | low-drive strength                                            |                  | 5 V, I <sub>Load</sub> = 2 mA                                | —                      |                  | 0.8                    |      | х                       | х                 |

| 4   | С | Output low                                                    |                  | 3 V, I <sub>Load</sub> = 1 mA                                | —                      | _                | 0.8                    | V    | х                       | х                 |

| 4   | С | voltage                                                       |                  | 5 V, I <sub>Load</sub> = 20 mA                               | —                      |                  | 1.5                    |      | х                       | х                 |

|     | Ρ | All I/O pins                                                  |                  | 5 V, I <sub>Load</sub> = 10 mA                               | —                      |                  | 0.8                    |      | х                       | х                 |

|     | С | high-drive strength                                           |                  | 3 V, I <sub>Load</sub> = 5 mA                                | —                      |                  | 0.8                    |      | х                       | x                 |

| 5   | с | Output low Max total I <sub>OL</sub> for<br>current all ports | I <sub>OLT</sub> | V <sub>OUT</sub> > V <sub>SS</sub>                           | 0                      | _                | 100<br>50              | mA   | x                       | x                 |

|     | Р | Input high voltage; all digital inputs                        | V <sub>IH</sub>  | 5V                                                           | 0.65 x V <sub>DD</sub> |                  | _                      | V    | х                       | x                 |

| 6   | С |                                                               |                  | 3V                                                           | 0.7 x V <sub>DD</sub>  | _                |                        |      | х                       | х                 |

|     | Р | Input low voltage; all digital inputs                         | V <sub>IL</sub>  | 5V                                                           |                        |                  | 0.35 x V <sub>DD</sub> | V    | х                       | х                 |

| 7   | С |                                                               |                  | 3V                                                           | —                      | _                | 0.35 x V <sub>DD</sub> | 1    | х                       | х                 |

| 0   | C | C Input hysteresis                                            |                  |                                                              | 0.06 x V <sub>DD</sub> |                  |                        | V    | х                       | x                 |

| 8   | C | input hysteresis                                              | V <sub>hys</sub> |                                                              | 0.00 X V <sub>DD</sub> |                  |                        | v    | х                       | x                 |

| 0   | Р | Input leakage current (per pin)                               | I <sub>In</sub>  | $V_{In} = V_{DD} \text{ or } V_{SS}$                         | _                      | 0.1              | 1                      | μA   | х                       |                   |

| 9   | • | input leakage current (per pin)                               |                  | temperature > 125 °C                                         |                        |                  | 2                      |      |                         | x                 |

|     | Ρ | Hi-Z (off-state) leakage current (per pin)                    |                  |                                                              |                        |                  |                        |      |                         |                   |

| 10  |   | input/output port pins                                        | I <sub>OZ</sub>  | $V_{In} = V_{DD} \text{ or } V_{SS},$                        | —                      | 0.1              | 1                      | μA   | х                       | <br>              |

|     |   | PTB6/SDA/XTAL, RESET                                          |                  | $V_{In} = V_{DD} \text{ or } V_{SS}$                         | —                      | 0.2              | 2                      | μA   | х                       |                   |

|     |   | input/output port pins                                        |                  | $V_{ln} = V_{DD} \text{ or } V_{SS}$<br>temperature > 125 °C |                        | 0.2              | 2                      | μA   |                         | х                 |

**Appendix A Electrical Characteristics**

| Num | с      | Characteristic                                                                                                       |                         | Symbol                                              | Condition                         | Min          | Typ <sup>1</sup> | Max          | Unit | Temp Rated <sup>2</sup> |                   |

|-----|--------|----------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------|-----------------------------------|--------------|------------------|--------------|------|-------------------------|-------------------|

|     |        |                                                                                                                      |                         |                                                     |                                   |              |                  |              |      | Stand<br>ard            | AEC<br>Grade<br>0 |

|     |        | Pullup or Pulldown <sup>3</sup> resistors; when                                                                      |                         |                                                     |                                   |              |                  |              |      |                         |                   |

| 11  | Р      | enabled                                                                                                              |                         |                                                     |                                   | 17           | 37               | 52           | kΩ   | v                       | v                 |

|     | г<br>С | I/O pins<br>RESET <sup>4</sup>                                                                                       |                         | R <sub>PU</sub> ,R <sub>PD</sub><br>R <sub>PU</sub> |                                   | 17           | 37               | 52           | kΩ   | x<br>x                  | X<br>X            |

|     |        | DC injection current <sup>5, 6, 7, 8</sup>                                                                           |                         | 110                                                 |                                   |              | 07               | 52           | 1122 | ^                       | ^                 |

|     | D      | Single pin limit                                                                                                     |                         | I <sub>IC</sub>                                     | $V_{IN} > V_{DD}$                 | 0            |                  | 2            | mA   | x                       | х                 |

|     |        | Total MCU limit,<br>includes                                                                                         |                         |                                                     | V <sub>IN</sub> < V <sub>SS</sub> | 0            | —                | -0.2         | mA   | x                       | x                 |

| 12  |        |                                                                                                                      |                         |                                                     | $V_{IN} > V_{DD}$                 | 0            | —                | 25           | mA   | x                       | х                 |

|     |        | sum of all stressed<br>pins                                                                                          |                         |                                                     | $V_{IN} < V_{SS}$                 | 0            | _                | -5           | mA   | x                       | x                 |

| 13  | D      | Input Capacitanc                                                                                                     | e, all pins             | C <sub>In</sub>                                     |                                   | —            | —                | 8            | pF   | х                       | х                 |

| 14  | D      | RAM retention vo                                                                                                     | -                       | V <sub>RAM</sub>                                    |                                   | —            | 0.6              | 1.0          | V    | х                       | х                 |

| 15  | D      | POR re-arm volta                                                                                                     | -                       | V <sub>POR</sub>                                    |                                   | 0.9          | 1.4              | 2.0          | V    | х                       | х                 |

| 16  | D      | POR re-arm time                                                                                                      | 10                      | t <sub>POR</sub>                                    |                                   | 10           | —                |              | μS   | х                       | х                 |

| 17  | Ρ      | Low-voltage<br>detection<br>threshold —<br>high range                                                                | V <sub>DD</sub> falling | V <sub>LVD1</sub>                                   |                                   | 3.9<br>3.88  | 4.0<br>4.0       | 4.1<br>4.12  | v    | x                       | x                 |

|     |        |                                                                                                                      | V <sub>DD</sub> rising  |                                                     |                                   | 4.0<br>3.98  | 4.1<br>4.1       | 4.2<br>4.22  |      | x                       | x                 |

|     | Ρ      | Low-voltage detection threshold —<br>low range <sup>11,12</sup><br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising |                         |                                                     |                                   |              |                  |              |      |                         |                   |

| 18  |        |                                                                                                                      |                         | V <sub>LVD0</sub>                                   |                                   | 2.48<br>2.54 | 2.56<br>2.62     | 2.64<br>2.70 | V    | x<br>x                  | x<br>x            |

| 19  | Ρ      | Low-voltage V <sub>DD</sub> falling<br>warning<br>threshold —<br>high range 1 V <sub>DD</sub> rising                 | V <sub>DD</sub> falling | V                                                   |                                   | 4.5<br>4.48  | 4.6<br>4.6       | 4.7<br>4.72  |      | x                       | x                 |

|     |        |                                                                                                                      | V <sub>LVW3</sub>       |                                                     | 4.6<br>4.58                       | 4.7<br>4.7   | 4.8<br>4.82      | V            | x    | x                       |                   |

| 20  | Ρ      | Low-voltage V <sub>DD</sub> falling varning threshold — high range 0 V <sub>DD</sub> rising                          | V <sub>LVW2</sub>       |                                                     | 4.2<br>4.18                       | 4.3<br>4.3   | 4.4<br>4.42      |              | x    | x                       |                   |

|     |        |                                                                                                                      |                         |                                                     | 4.3<br>4.28                       | 4.4<br>4.4   | 4.5<br>4.52      | V            | x    | x                       |                   |

| 21  | Ρ      | Low-voltage warning threshold<br>low range 1<br>V <sub>DD</sub> falling<br>V <sub>DD</sub> rising                    |                         | V <sub>LVW1</sub>                                   |                                   | 2.84<br>2.90 | 2.92<br>2.98     | 3.00<br>3.06 | v    | x<br>x                  | x<br>x            |

| 22  | Р      | Low-voltage warning threshold —<br>low range 0<br>V <sub>DD</sub> falling                                            |                         | V <sub>LVW0</sub>                                   |                                   | 2.66         | 2.74             | 2.82         |      | x                       | x                 |

|     |        |                                                                                                                      | V <sub>DD</sub> rising  | * LVW0                                              |                                   | 2.72         | 2.80             | 2.88         | V    | x                       | x                 |

### Table A-6. DC Characteristics (continued)

**Appendix A Electrical Characteristics**

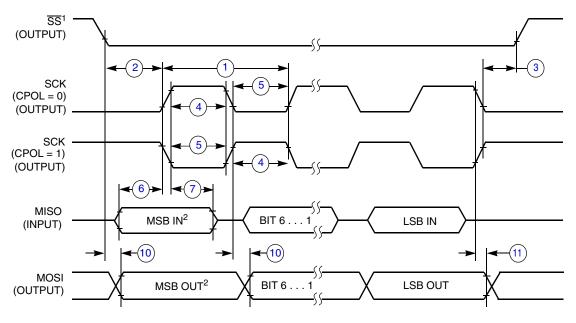

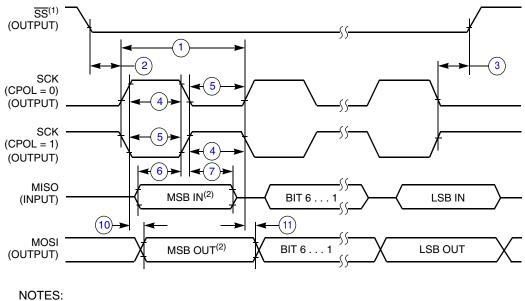

NOTES:

1.  $\overline{SS}$  output mode (MODFEN = 1, SSOE = 1).

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

1.  $\overline{SS}$  output mode (MODFEN = 1, SSOE = 1).

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

MC9S08SG8 MCU Series Data Sheet, Rev. 8