Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                     |

|----------------------------|------------------------------------------------------------|

| Core Processor             | S08                                                        |

| Core Size                  | 8-Bit                                                      |

| Speed                      | 40MHz                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                         |

| Peripherals                | LVD, POR, PWM, WDT                                         |

| Number of I/O              | 4                                                          |

| Program Memory Size        | 8KB (8K x 8)                                               |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 512 x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                |

| Data Converters            | A/D 4x10b                                                  |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                              |

| Supplier Device Package    | 8-SOIC                                                     |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=s9s08sg8e2msc |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

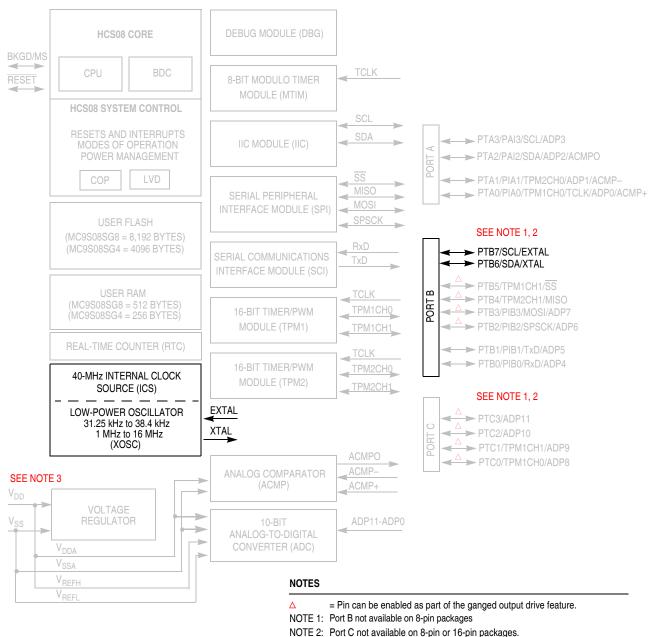

# MC9S08SG8 Features

#### 8-Bit HCS08 Central Processor Unit (CPU)

- 40 MHz HCS08 CPU (central processor unit)

- 36 MHz HCS08 CPU for temperatures greater than 125 °C

- HC08 instruction set with added BGND instruction

- · Support for up to 32 interrupt/reset sources

#### **On-Chip Memory**

- Flash read/program/erase over full operating voltage and temperature

- Random-access memory (RAM)

#### **Power-Saving Modes**

- Two very low power stop modes

- Reduced power wait mode

- Very low power real time interrupt for use in run, wait, and stop

#### **Clock Source Options**

- Oscillator (XOSC) Loop-control Pierce oscillator; Crystal or ceramic resonator range of 31.25 kHz to 38.4 kHz or 1 MHz to 16MHz

- Internal Clock Source (ICS) Internal clock source module containing a frequency-locked loop (FLL) controlled by internal or external reference; precision trimming of internal reference allows 0.2% resolution and 1.5% deviation over temperature –40 to 125 °C or 3% deviation for temperature > 125 °C and voltage; supports bus frequencies from 2 MHz to 20MHz.

#### **System Protection**

- Watchdog computer operating properly (COP) reset with option to run from dedicated 1-kHz internal clock source or bus clock

- Low-voltage detection with reset or interrupt; selectable trip points

- · Illegal opcode detection with reset

- Illegal address detection with reset

- FLASH block protect

#### **Development Support**

- · Single-wire background debug interface

- Breakpoint capability to allow single breakpoint setting during in-circuit debugging (plus two more breakpoints in on-chip debug module)

- On-chip, in-circuit emulation (ICE) debug module containing two comparators and nine trigger modes. Eight deep FIFO for storing change-of-flow address and event-only data. Debug module supports both tag and force breakpoints.

#### Peripherals

- ADC 12-channel, 10-bit resolution, 2.5 μs conversion time, automatic compare function, temperature sensor, internal bandgap reference channel; runs in stop3

- ACMP Analog comparator with selectable interrupt on rising, falling, or either edge of comparator output; compare option to fixed internal bandgap reference voltage; output can be optionally routed to TPM module; runs in stop3

- SCI Full duplex non-return to zero (NRZ); LIN master extended break generation; LIN slave extended break detection; wake up on active edge

- **SPI** Full-duplex or single-wire bidirectional; Double-buffered transmit and receive; Master or Slave mode; MSB-first or LSB-first shifting

- **IIC** Up to 100 kbps with maximum bus loading; Multi-master operation; Programmable slave address; Interrupt driven byte-by-byte data transfer; supports broadcast mode and 10-bit addressing

- MTIM 8-bit modulo counter with 8-bit prescaler and overflow interrupt

- TPMx Two 2-channel timer pwm modules (TPM1, TPM2); Selectable input capture, output compare, or buffered edge- or center-aligned PWM on each channel

- RTC (Real-time counter) 8-bit modulus counter with binary or decimal based prescaler; External clock source for precise time base, time-of-day, calendar or task scheduling functions; Free running on-chip low power oscillator (1 kHz) for cyclic wake-up without external components, runs in all MCU modes

#### Input/Output

- 16 general purpose I/O pins (GPIOs)

- · 8 interrupt pins with selectable polarity

- Ganged output option for PTB[5:2] and PTC[3:0]; allows single write to change state of multiple pins

- Hysteresis and configurable pull up device on all input pins; Configurable slew rate and drive strength on all output pins.

#### **Package Options**

- 20-TSSOP (not available on high-temperature rated devices)

- 16-TSSOP

- 8-SOIC (not available on high-temperature rated devices)

# MC9S08SG8 Data Sheet

Covers MC9S08SG8 MC9S08SG4

> MC9S08SG8 Rev. 8 1/2014

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

© Freescale Semiconductor, Inc., 2006-2014. All rights reserved.

**Section Number**

|      | 13.4.1 RTC Operation Example                             |  |

|------|----------------------------------------------------------|--|

| 13.5 | Initialization/Application Information                   |  |

|      | Chapter 14<br>Serial Communications Interface (S08SCIV4) |  |

| 14.1 | Introduction                                             |  |

|      | 14.1.1 Features                                          |  |

|      | 14.1.2 Modes of Operation                                |  |

| 14.2 | 14.1.3 Block Diagram                                     |  |

| 14.2 | Register Definition                                      |  |

|      | 14.2.1 SCI Baud Kate Registers (SCIBDIT, SCIBDL)         |  |

|      | 14.2.3 SCI Control Register 2 (SCIC2)                    |  |

|      | 14.2.4 SCI Status Register 1 (SCIS1)                     |  |

|      | 14.2.5 SCI Status Register 2 (SCIS2)                     |  |

|      | 14.2.6 SCI Control Register 3 (SCIC3)                    |  |

|      | 14.2.7 SCI Data Register (SCID)                          |  |

| 14.3 | Functional Description                                   |  |

|      | 14.3.1 Baud Rate Generation                              |  |

|      | 14.3.2 Transmitter Functional Description                |  |

|      | 14.3.3 Receiver Functional Description                   |  |

|      | 14.3.4 Interrupts and Status Flags                       |  |

|      | 14.3.5 Additional SCI Functions                          |  |

# Chapter 15 Serial Peripheral Interface (S08SPIV3)

| 15.1 | Introduction                                 | 219 |

|------|----------------------------------------------|-----|

|      | 15.1.1 Features                              | 221 |

|      | 15.1.2 Block Diagrams                        | 221 |

|      | 15.1.3 SPI Baud Rate Generation              | 223 |

| 15.2 | External Signal Description                  | 224 |

|      | 15.2.1 SPSCK — SPI Serial Clock              | 224 |

|      | 15.2.2 MOSI — Master Data Out, Slave Data In | 224 |

|      | 15.2.3 MISO — Master Data In, Slave Data Out | 224 |

|      | 15.2.4 $\overline{SS}$ — Slave Select        | 224 |

| 15.3 | Modes of Operation                           | 225 |

|      | 15.3.1 SPI in Stop Modes                     | 225 |

| 15.4 | Register Definition                          | 225 |

|      | 15.4.1 SPI Control Register 1 (SPIC1)        |     |

|      | 15.4.2 SPI Control Register 2 (SPIC2)        | 226 |

|      | 15.4.3 SPI Baud Rate Register (SPIBR)        | 227 |

|      | 15.4.4 SPI Status Register (SPIS)            | 228 |

|      |                                              |     |

Page

# Title

**Chapter 2 Pins and Connections**

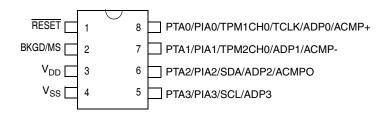

Figure 2-3. 8-Pin SOIC

#### **Chapter 3 Modes of Operation**

Most background commands are not available in stop mode. The memory-access-with-status commands do not allow memory access, but they report an error indicating that the MCU is in either stop or wait mode. The BACKGROUND command can be used to wake the MCU from stop and enter active background mode if the ENBDM bit is set. After entering background debug mode, all background commands are available.

### 3.6.2 Stop2 Mode

Stop2 mode is entered by executing a STOP instruction under the conditions as shown in Table 3-1. Most of the internal circuitry of the MCU is powered off in stop2 with the exception of the RAM. Upon entering stop2, all I/O pin control signals are latched so that the pins retain their states during stop2.

Exit from stop2 is performed by asserting the wake-up pin ( $\overline{\text{RESET}}$ ) on the MCU.

In addition, the real-time counter (RTC) can wake the MCU from stop2, if enabled.

Upon wake-up from stop2 mode, the MCU starts up as from a power-on reset (POR):

- All module control and status registers are reset

- The LVD reset function is enabled and the MCU remains in the reset state if V<sub>DD</sub> is below the LVD trip point (low trip point selected due to POR)

- The CPU takes the reset vector

In addition to the above, upon waking up from stop2, the PPDF bit in SPMSC2 is set. This flag is used to direct user code to go to a stop2 recovery routine. PPDF remains set and the I/O pin states remain latched until a 1 is written to PPDACK in SPMSC2.

To maintain I/O states for pins that were configured as general-purpose I/O before entering stop2, the user must restore the contents of the I/O port registers, which have been saved in RAM, to the port registers before writing to the PPDACK bit. If the port registers are not restored from RAM before writing to PPDACK, then the pins will switch to their reset states when PPDACK is written.

For pins that were configured as peripheral I/O, the user must reconfigure the peripheral module that interfaces to the pin before writing to the PPDACK bit. If the peripheral module is not enabled before writing to PPDACK, the pins will be controlled by their associated port control registers when the I/O latches are opened.

### 3.6.3 On-Chip Peripheral Modules in Stop Modes

When the MCU enters any stop mode, system clocks to the internal peripheral modules are stopped. Even in the exception case (ENBDM = 1), where clocks to the background debug logic continue to operate, clocks to the peripheral systems are halted to reduce power consumption. Refer to Section 3.6.2, "Stop2 Mode," and Section 3.6.1, "Stop3 Mode," for specific information on system behavior in stop modes.

### 4.5.1 Features

Features of the FLASH memory include:

- FLASH size

- MC9S08SG8: 8,192 bytes (16 pages of 512 bytes each)

- MC9S08SG4: 4,096 bytes (8 pages of 512 bytes each)

- Single power supply program and erase

- Command interface for fast program and erase operation

- Up to 100,000 program/erase cycles at typical voltage and temperature

- Flexible block protection

- Security feature for FLASH and RAM

- Auto power-down for low-frequency read accesses

### 4.5.2 Program and Erase Times

Before any program or erase command can be accepted, the FLASH clock divider register (FCDIV) must be written to set the internal clock for the FLASH module to a frequency ( $f_{FCLK}$ ) between 150 kHz and 200 kHz (see Section 4.7.1, "FLASH Clock Divider Register (FCDIV)"). This register can be written only once, so normally this write is done during reset initialization. FCDIV cannot be written if the access error flag, FACCERR in FSTAT, is set. The user must ensure that FACCERR is not set before writing to the FCDIV register. One period of the resulting clock ( $1/f_{FCLK}$ ) is used by the command processor to time program and erase pulses. An integer number of these timing pulses are used by the command processor to complete a program or erase command.

Table 4-5 shows program and erase times. The bus clock frequency and FCDIV determine the frequency of FCLK ( $f_{FCLK}$ ). The time for one cycle of FCLK is  $t_{FCLK} = 1/f_{FCLK}$ . The times are shown as a number of cycles of FCLK and as an absolute time for the case where  $t_{FCLK} = 5 \ \mu$ s. Program and erase times shown include overhead for the command state machine and enabling and disabling of program and erase voltages.

| Parameter            | Cycles of FCLK | Time if FCLK = 200 kHz |

|----------------------|----------------|------------------------|

| Byte program         | 9              | 45 μs                  |

| Byte program (burst) | 4              | 20 μs <sup>1</sup>     |

| Page erase           | 4000           | 20 ms                  |

| Mass erase           | 20,000         | 100 ms                 |

#### Table 4-5. Program and Erase Times

<sup>1</sup> Excluding start/end overhead

Chapter 4 Memory

## 4.5.3 **Program and Erase Command Execution**

The steps for executing any of the commands are listed below. The FCDIV register must be initialized and any error flags cleared before beginning command execution. The command execution steps are:

1. Write a data value to an address in the FLASH array. The address and data information from this write is latched into the FLASH interface. This write is a required first step in any command sequence. For erase and blank check commands, the value of the data is not important. For page erase commands, the address may be any address in the 512-byte page of FLASH to be erased. For mass erase and blank check commands, the address can be any address in the FLASH memory. Whole pages of 512 bytes are the smallest block of FLASH that may be erased.

### NOTE

Do not program any byte in the FLASH more than once after a successful erase operation. Reprogramming bits to a byte that is already programmed is not allowed without first erasing the page in which the byte resides or mass erasing the entire FLASH memory. Programming without first erasing may disturb data stored in the FLASH.

- 2. Write the command code for the desired command to FCMD. The five valid commands are blank check (0x05), byte program (0x20), burst program (0x25), page erase (0x40), and mass erase (0x41). The command code is latched into the command buffer.

- 3. Write a 1 to the FCBEF bit in FSTAT to clear FCBEF and launch the command (including its address and data information).

A partial command sequence can be aborted manually by writing a 0 to FCBEF any time after the write to the memory array and before writing the 1 that clears FCBEF and launches the complete command. Aborting a command in this way sets the FACCERR access error flag, which must be cleared before starting a new command.

A strictly monitored procedure must be obeyed or the command will not be accepted. This minimizes the possibility of any unintended changes to the FLASH memory contents. The command complete flag (FCCF) indicates when a command is complete. The command sequence must be completed by clearing FCBEF to launch the command. Figure 4-2 is a flowchart for executing all of the commands except for burst programming. The FCDIV register must be initialized before using any FLASH commands. This must be done only once following a reset.

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>FACCERR | Access Error Flag — FACCERR is set automatically when the proper command sequence is not obeyed exactly (the erroneous command is ignored), if a program or erase operation is attempted before the FCDIV register has been initialized, or if the MCU enters stop while a command was in progress. For a more detailed discussion of the exact actions that are considered access errors, see Section 4.5.5, "Access Errors." FACCERR is cleared by writing a 1 to FACCERR. Writing a 0 to FACCERR has no meaning or effect.<br>0 No access error.<br>1 An access error has occurred. |

| 2<br>FBLANK  | <ul> <li>FLASH Verified as All Blank (erased) Flag — FBLANK is set automatically at the conclusion of a blank check command if the entire FLASH array was verified to be erased. FBLANK is cleared by clearing FCBEF to write a new valid command. Writing to FBLANK has no meaning or effect.</li> <li>0 After a blank check command is completed and FCCF = 1, FBLANK = 0 indicates the FLASH array is not completely erased.</li> <li>1 After a blank check command is completed and FCCF = 1, FBLANK = 1 indicates the FLASH array is completely erased (all 0xFF).</li> </ul>     |

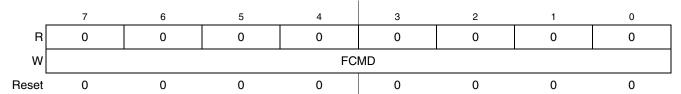

# 4.7.6 FLASH Command Register (FCMD)

Only five command codes are recognized in normal user modes as shown in Table 4-13. Refer to Section 4.5.3, "Program and Erase Command Execution," for a detailed discussion of FLASH programming and erase operations.

Figure 4-10. FLASH Command Register (FCMD)

| Command                     | FCMD | Equate File Label |

|-----------------------------|------|-------------------|

| Blank check                 | 0x05 | mBlank            |

| Byte program                | 0x20 | mByteProg         |

| Byte program — burst mode   | 0x25 | mBurstProg        |

| Page erase (512 bytes/page) | 0x40 | mPageErase        |

| Mass erase (all FLASH)      | 0x41 | mMassErase        |

Table 4-13. FLASH Commands

All other command codes are illegal and generate an access error.

It is not necessary to perform a blank check command after a mass erase operation. Only blank check is required as part of the security unlocking mechanism.

Chapter 5 Resets, Interrupts, and General System Control

# 5.4 Computer Operating Properly (COP) Watchdog

The COP watchdog is intended to force a system reset when the application software fails to execute as expected. To prevent a system reset from the COP timer (when it is enabled), application software must reset the COP counter periodically. If the application program gets lost and fails to reset the COP counter before it times out, a system reset is generated to force the system back to a known starting point.

After any reset, the COP watchdog is enabled (see Section 5.7.3, "System Options Register 1 (SOPT1)," for additional information). If the COP watchdog is not used in an application, it can be disabled by clearing COPT bits in SOPT1.

The COP counter is reset by writing 0x0055 and 0x00AA (in this order) to the address of SRS during the selected timeout period. Writes do not affect the data in the read-only SRS. As soon as the write sequence is done, the COP timeout period is restarted. If the program fails to do this during the time-out period, the MCU will reset. Also, if any value other than 0x0055 or 0x00AA is written to SRS, the MCU is immediately reset.

The COPCLKS bit in SOPT2 (see Section 5.7.4, "System Options Register 2 (SOPT2)," for additional information) selects the clock source used for the COP timer. The clock source options are either the bus clock or an internal 1-kHz clock source. With each clock source, there are three associated time-outs controlled by the COPT bits in SOPT1. Table 5-1 summaries the control functions of the COPCLKS and COPT bits. The COP watchdog defaults to operation from the 1-kHz clock source and the longest time-out (2<sup>10</sup> cycles).

| Control Bits |           | - Clock Source | COP Window <sup>1</sup> Opens |                                                |  |

|--------------|-----------|----------------|-------------------------------|------------------------------------------------|--|

| COPCLKS      | COPT[1:0] | Clock Source   | (COPW = 1)                    | COP Overflow Count                             |  |

| N/A          | 0:0       | N/A            | N/A                           | COP is disabled                                |  |

| 0            | 0:1       | 1 kHz          | N/A                           | 2 <sup>5</sup> cycles (32 ms <sup>2</sup> )    |  |

| 0            | 1:0       | 1 kHz          | N/A                           | 2 <sup>8</sup> cycles (256 ms <sup>1</sup> )   |  |

| 0            | 1:1       | 1 kHz          | N/A                           | 2 <sup>10</sup> cycles (1.024 s <sup>1</sup> ) |  |

| 1            | 0:1       | Bus            | 6144 cycles                   | 2 <sup>13</sup> cycles                         |  |

| 1            | 1:0       | Bus            | 49,152 cycles                 | 2 <sup>16</sup> cycles                         |  |

| 1            | 1:1       | Bus            | 196,608 cycles                | 2 <sup>18</sup> cycles                         |  |

### Table 5-1. COP Configuration Options

<sup>1</sup> Windowed COP operation requires the user to clear the COP timer in the last 25% of the selected timeout period. This column displays the minimum number of clock counts required before the COP timer can be reset hen in windowed COP mode (COPW = 1).

<sup>2</sup> Values shown in milliseconds based on  $t_{LPO} = 1$  ms. See  $t_{LPO}$  in the appendix Section A.12.1, "Control Timing," for the tolerance of this value.

When the bus clock source is selected, windowed COP operation is available by setting COPW in the SOPT2 register. In this mode, writes to the SRS register to clear the COP timer must occur in the last 25% of the selected timeout period. A premature write immediately resets the MCU. When the 1-kHz clock source is selected, windowed COP operation is not available.

Chapter 6 Parallel Input/Output Control

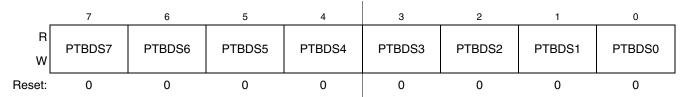

# 6.6.2.5 Port B Drive Strength Selection Register (PTBDS)

Figure 6-15. Drive Strength Selection for Port B Register (PTBDS)

#### Table 6-14. PTBDS Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTBDS[7:0] | <ul> <li>Output Drive Strength Selection for Port B Bits — Each of these control bits selects between low and high output drive for the associated PTB pin. For port B pins that are configured as inputs, these bits have no effect.</li> <li>0 Low output drive strength selected for port B bit n.</li> <li>1 High output drive strength selected for port B bit n.</li> </ul> |

### 6.6.2.6 Port B Interrupt Status and Control Register (PTBSC)

|        | 7 | 6 | 5 | 4 | 3     | 2      | 1     | 0        |

|--------|---|---|---|---|-------|--------|-------|----------|

| R      | 0 | 0 | 0 | 0 | PTBIF | 0      | PTBIE | PTBMOD   |

| W      |   |   |   |   |       | PTBACK | FIDIC | FIDIVIOD |

| Reset: | 0 | 0 | 0 | 0 | 0     | 0      | 0     | 0        |

Figure 6-16. Port B Interrupt Status and Control Register (PTBSC)

#### Table 6-15. PTBSC Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3<br>PTBIF  | <ul> <li>Port B Interrupt Flag — PTBIF indicates when a Port B interrupt is detected. Writes have no effect on PTBIF.</li> <li>0 No Port B interrupt detected.</li> <li>1 Port B interrupt detected.</li> </ul>                         |

| 2<br>PTBACK | <b>Port B Interrupt Acknowledge</b> — Writing a 1 to PTBACK is part of the flag clearing mechanism. PTBACK always reads as 0.                                                                                                           |

| 1<br>PTBIE  | <ul> <li>Port B Interrupt Enable — PTBIE determines whether a port B interrupt is requested.</li> <li>0 Port B interrupt request not enabled.</li> <li>1 Port B interrupt request enabled.</li> </ul>                                   |

| 0<br>PTBMOD | <ul> <li>Port B Detection Mode — PTBMOD (along with the PTBES bits) controls the detection mode of the port B interrupt pins.</li> <li>0 Port B pins detect edges only.</li> <li>1 Port B pins detect both edges and levels.</li> </ul> |

# Chapter 8 5-V Analog Comparator (S08ACMPV2)

# 8.1 Introduction

The analog comparator module (ACMP) provides a circuit for comparing two analog input voltages or for comparing one analog input voltage to an internal reference voltage. The comparator circuit is designed to operate across the full range of the supply voltage (rail-to-rail operation).

Figure 8-1 shows the MC9S08SG8 block diagram with the ACMP module highlighted.

# 8.1.1 ACMP Configuration Information

When using the bandgap reference voltage for input to ACMP+, the user must enable the bandgap buffer by setting BGBE =1 in SPMSC1 see Section 5.7.6, "System Power Management Status and Control 1 Register (SPMSC1)". For value of bandgap voltage reference see Section A.6, "DC Characteristics".

# 8.1.2 ACMP in Stop3 Mode

S08ACMPV2 continues to operate in stop3 mode if enabled. If ACOPE is enabled, comparator output will operate as in the normal operating mode and will control ACMPO pin. The MCU is brought out of stop when a compare event occurs and ACIE is enabled; ACF flag sets accordingly.

# 8.1.3 ACMP/TPM Configuration Information

The ACMP module can be configured to connect the output of the analog comparator to TPM1 input capture channel 0 by setting ACIC in SOPT2. With ACIC set, the TPM1CH0 pin is not available externally regardless of the configuration of the TPM1 module for channel 0.

Chapter 9 Analog-to-Digital Converter (S08ADCV1)

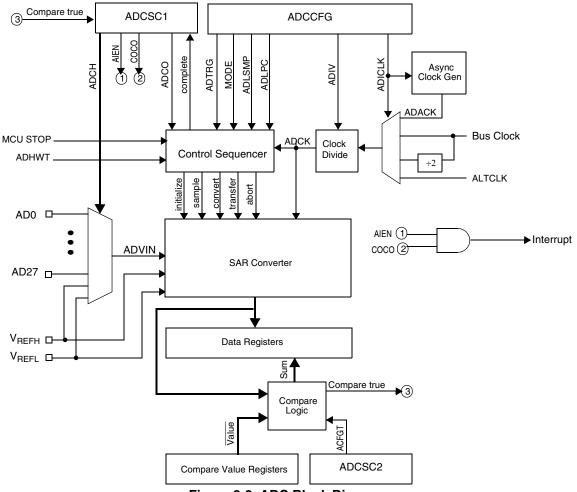

# 9.1.2 Alternate Clock

The ADC module is capable of performing conversions using the MCU bus clock, the bus clock divided by two, the local asynchronous clock (ADACK) within the module, or the alternate clock, ALTCLK. The alternate clock for the MC9S08SG8 MCU devices is the external reference clock (ICSERCLK).

The selected clock source must run at a frequency such that the ADC conversion clock (ADCK) runs at a frequency within its specified range ( $f_{ADCK}$ ) after being divided down from the ALTCLK input as determined by the ADIV bits.

ALTCLK is active while the MCU is in wait mode provided the conditions described above are met. This allows ALTCLK to be used as the conversion clock source for the ADC while the MCU is in wait mode.

ALTCLK cannot be used as the ADC conversion clock source while the MCU is in either stop2 or stop3.

# 9.1.3 Hardware Trigger

The ADC hardware trigger, ADHWT, is the output from the real time counter (RTC). The RTC counter can be clocked by either ICSERCLK, ICSIRCLK or a nominal 1 kHz clock source.

The period of the RTC is determined by the input clock frequency, the RTCPS bits, and the RTCMOD register. When the ADC hardware trigger is enabled, a conversion is initiated upon an RTC counter overflow. The RTIE does not have to be set for RTC to cause a hardware trigger.

The RTC can be configured to cause a hardware trigger in MCU run, wait, and stop3.

### 9.1.4 Temperature Sensor

To use the on-chip temperature sensor, the user must perform the following:

- Configure ADC for long sample with a maximum of 1 MHz clock

- Convert the bandgap voltage reference channel (AD27)

- By converting the digital value of the bandgap voltage reference channel using the value of  $V_{BG}$  the user can determine  $V_{DD}$ . For value of bandgap voltage, see Section A.6, "DC Characteristics".

- Convert the temperature sensor channel (AD26)

- By using the calculated value of  $V_{DD}$ , convert the digital value of AD26 into a voltage,  $V_{TEMP}$

Equation 9-1 provides an approximate transfer function of the on-chip temperature sensor.

where:

- V<sub>TEMP</sub> is the voltage of the temperature sensor channel at the ambient temperature.

- $V_{\text{TEMP25}}$  is the voltage of the temperature sensor channel at 25°C.

- m is the hot or cold voltage versus temperature slope in  $V/^{\circ}C$ .

MC9S08SG8 MCU Series Data Sheet, Rev. 8

For temperature calculations, use the V<sub>TEMP25</sub> and m values from the ADC Electricals table.

In application code, the user reads the temperature sensor channel, calculates  $V_{TEMP}$ , and compares to  $V_{TEMP25}$ . If  $V_{TEMP}$  is greater than  $V_{TEMP25}$ , the cold slope value is applied in Equation 9-1. If  $V_{TEMP}$  is less than  $V_{TEMP25}$ , the hot slope value is applied in Equation 9-1. To improve accuracy, calibrate the bandgap voltage reference and temperature sensor.

Calibrating at 25°C will improve accuracy to  $\pm 4.5$ °C.

Calibration at 3 points, -40°C, 25°C, and 125°C will improve accuracy to  $\pm 2.5$ °C. Once calibration has been completed, the user will need to calculate the slope for both hot and cold. In application code, the user would then calculate the temperature using Equation 9-1 as detailed above and then determine if the temperature is above or below 25°C. Once determined if the temperature is above or below 25°C, the user can recalculate the temperature using the hot or cold slope value obtained during calibration.

Figure 9-1 shows the MC9S08SG8 block diagram with the ADC module highlighted.

#### Analog-to-Digital Converter (S08ADCV1)

Figure 9-2. ADC Block Diagram

# 9.2 External Signal Description

The ADC module supports up to 28 separate analog inputs. It also requires four supply/reference/ground connections.

| Name              | Function               |

|-------------------|------------------------|

| AD27–AD0          | Analog Channel inputs  |

| V <sub>REFH</sub> | High reference voltage |

| V <sub>REFL</sub> | Low reference voltage  |

| V <sub>DDAD</sub> | Analog power supply    |

| V <sub>SSAD</sub> | Analog ground          |

#### **Table 9-2. Signal Properties**

#### Chapter 10 Internal Clock Source (S08ICSV2)

NOTE 3: V<sub>DDA</sub>/V<sub>REFH</sub> and V<sub>SSA</sub>/V<sub>REFL</sub>, are double bonded to V<sub>DD</sub> and V<sub>SS</sub> respectively.

### 10.4.1.5 FLL Bypassed External (FBE)

The FLL bypassed external (FBE) mode is entered when all the following conditions occur:

- CLKS bits are written to 10.

- IREFS bit is written to 0.

- BDM mode is active or LP bit is written to 0.

In FLL bypassed external mode, the ICSOUT clock is derived from the external reference clock. The FLL clock is controlled by the external reference clock, and the FLL loop will lock the FLL frequency to 1024 times the reference frequency, as selected by the RDIV bits, so that the ICSLCLK will be available for BDC communications, and the external reference clock is enabled.

### 10.4.1.6 FLL Bypassed External Low Power (FBELP)

The FLL bypassed external low power (FBELP) mode is entered when all the following conditions occur:

- CLKS bits are written to 10.

- IREFS bit is written to 0.

- BDM mode is not active and LP bit is written to 1.

In FLL bypassed external low power mode, the ICSOUT clock is derived from the external reference clock and the FLL is disabled. The ICSLCLK will be not be available for BDC communications. The external reference clock is enabled.

### 10.4.1.7 Stop

Stop mode is entered whenever the MCU enters a STOP state. In this mode, all ICS clock signals are static except in the following cases:

ICSIRCLK will be active in stop mode when all the following conditions occur:

- IRCLKEN bit is written to 1

- IREFSTEN bit is written to 1

ICSERCLK will be active in stop mode when all the following conditions occur:

- ERCLKEN bit is written to 1

- EREFSTEN bit is written to 1

### 10.4.2 Mode Switching

When switching between FLL engaged internal (FEI) and FLL engaged external (FEE) modes the IREFS bit can be changed at anytime, but the RDIV bits must be changed simultaneously so that the resulting frequency stays in the range of 31.25 kHz to 39.0625 kHz. After a change in the IREFS value the FLL will begin locking again after a few full cycles of the resulting divided reference frequency. The completion of the switch is shown by the IREFST bit.

#### Real-Time Counter (S08RTCV1)

{

```

#pragma TRAP_PROC

void RTC_ISR(void)

/* Clear the interrupt flag */

RTCSC.byte = RTCSC.byte | 0x80;

/* RTC interrupts every 1 Second */

Seconds++;

/* 60 seconds in a minute */

if (Seconds > 59)

Minutes++;

Seconds = 0;

}

/* 60 minutes in an hour */

if (Minutes > 59) {

Hours++;

Minutes = 0;

}

/* 24 hours in a day */

if (Hours > 23) {

Days ++;

Hours = 0;

}

```

### 14.1.1 Features

Features of SCI module include:

- Full-duplex, standard non-return-to-zero (NRZ) format

- Double-buffered transmitter and receiver with separate enables

- Programmable baud rates (13-bit modulo divider)

- Interrupt-driven or polled operation:

- Transmit data register empty and transmission complete

- Receive data register full

- Receive overrun, parity error, framing error, and noise error

- Idle receiver detect

- Active edge on receive pin

- Break detect supporting LIN

- Hardware parity generation and checking

- Programmable 8-bit or 9-bit character length

- Receiver wakeup by idle-line or address-mark

- Optional 13-bit break character generation / 11-bit break character detection

- Selectable transmitter output polarity

### 14.1.2 Modes of Operation

See Section 14.3, "Functional Description," For details concerning SCI operation in these modes:

- 8- and 9-bit data modes

- Stop mode operation

- Loop mode

- Single-wire mode

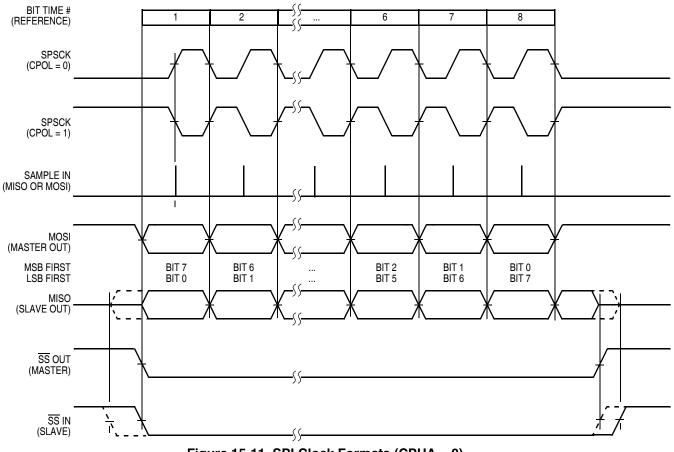

#### Serial Peripheral Interface (S08SPIV3)

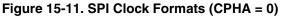

in LSBFE. Both variations of SPSCK polarity are shown, but only one of these waveforms applies for a specific transfer, depending on the value in CPOL. The SAMPLE IN waveform applies to the MOSI input of a slave or the MISO input of a master. The MOSI waveform applies to the MOSI output pin from a master and the MISO waveform applies to the MISO output from a slave. The  $\overline{SS}$  OUT waveform applies to the slave select output from a master (provided MODFEN and SSOE = 1). The master  $\overline{SS}$  output goes to active low at the start of the first bit time of the transfer and goes back high one-half SPSCK cycle after the end of the eighth bit time of the transfer. The  $\overline{SS}$  IN waveform applies to the slave select input of a slave.

When CPHA = 0, the slave begins to drive its MISO output with the first data bit value (MSB or LSB depending on LSBFE) when  $\overline{SS}$  goes to active low. The first SPSCK edge causes both the master and the slave to sample the data bit values on their MISO and MOSI inputs, respectively. At the second SPSCK edge, the SPI shifter shifts one bit position which shifts in the bit value that was just sampled and shifts the second data bit value out the other end of the shifter to the MOSI and MISO outputs of the master and slave, respectively. When CPHA = 0, the slave's  $\overline{SS}$  input must go to its inactive high level between transfers.

When no debugger pod is connected to the 6-pin BDM interface connector, the internal pullup on BKGD chooses normal operating mode. When a debug pod is connected to BKGD it is possible to force the MCU into active background mode after reset. The specific conditions for forcing active background depend upon the HCS08 derivative (refer to the introduction to this Development Support section). It is not necessary to reset the target MCU to communicate with it through the background debug interface.

# 17.2.2 Communication Details

The BDC serial interface requires the external controller to generate a falling edge on the BKGD pin to indicate the start of each bit time. The external controller provides this falling edge whether data is transmitted or received.

BKGD is a pseudo-open-drain pin that can be driven either by an external controller or by the MCU. Data is transferred MSB first at 16 BDC clock cycles per bit (nominal speed). The interface times out if 512 BDC clock cycles occur between falling edges from the host. Any BDC command that was in progress when this timeout occurs is aborted without affecting the memory or operating mode of the target MCU system.

The custom serial protocol requires the debug pod to know the target BDC communication clock speed.

The clock switch (CLKSW) control bit in the BDC status and control register allows the user to select the BDC clock source. The BDC clock source can either be the bus or the alternate BDC clock source.

The BKGD pin can receive a high or low level or transmit a high or low level. The following diagrams show timing for each of these cases. Interface timing is synchronous to clocks in the target BDC, but asynchronous to the external host. The internal BDC clock signal is shown for reference in counting cycles.