Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 16                                                                    |

| Program Memory Size        | 8KB (8K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                       |

| Supplier Device Package    | 20-TSSOP                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08sg8e2mtj |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Chapter 2 Pins and Connections**

The MC9S08SG8 devices contain a ganged output drive feature that allows a safe and reliable method of allowing pins to be tied together externally to produce a higher output current drive. See Section 6.3, "Ganged Output" for more information for configuring the port pins for ganged output drive.

### NOTE

To avoid extra current drain from floating input pins, the reset initialization routine in the application program should either enable on-chip pull-up devices or change the direction of unused pins to outputs so they do not float.

When using the 8-pin devices, the user must either enable on-chip pullup devices or change the direction of non-bonded out port B and port C pins to outputs so the pins do not float.

When using the 16-pin devices, the user must either enable on-chip pullup devices or change the direction of non-bonded out port C pins to outputs so the pins do not float.

#### **Chapter 4 Memory**

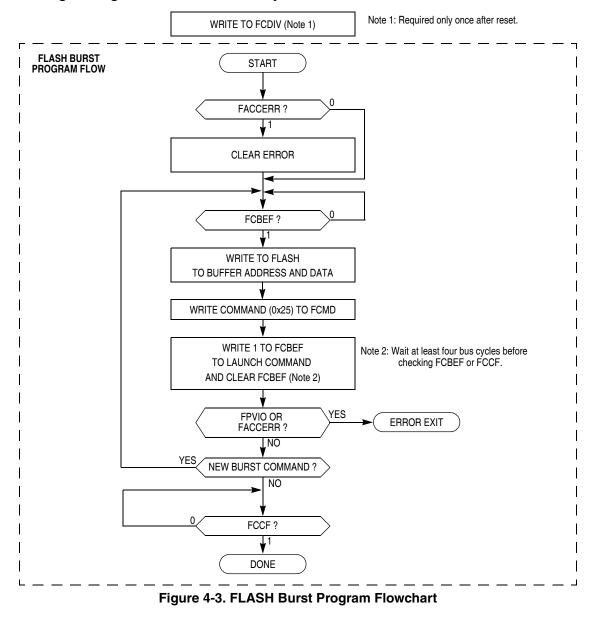

The first byte of a series of sequential bytes being programmed in burst mode will take the same amount of time to program as a byte programmed in standard mode. Subsequent bytes will program in the burst program time provided that the conditions above are met. In the case the next sequential address is the beginning of a new row, the program time for that byte will be the standard time instead of the burst time. This is because the high voltage to the array must be disabled and then enabled again. If a new burst command has not been queued before the current command completes, then the charge pump will be disabled and high voltage removed from the array.

Chapter 5 Resets, Interrupts, and General System Control

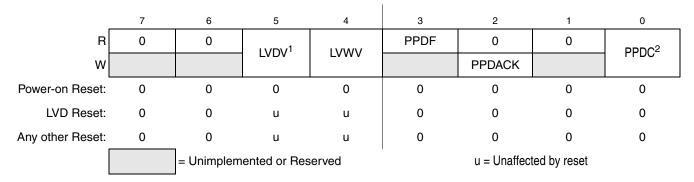

# 5.7.7 System Power Management Status and Control 2 Register (SPMSC2)

This register is used to report the status of the low voltage warning function, and to configure the stop mode behavior of the MCU.

<sup>1</sup> This bit can be written only one time after power-on reset. Additional writes are ignored.

<sup>2</sup> This bit can be written only one time after reset. Additional writes are ignored.

#### Figure 5-9. System Power Management Status and Control 2 Register (SPMSC2)

#### Table 5-10. SPMSC2 Register Field Descriptions

| Field       | Description                                                                                                                                                                                                               |  |  |  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 5<br>LVDV   | <b>Low-Voltage Detect Voltage Select</b> — This write-once bit selects the low voltage detect (LVD) trip point setting. It also selects the warning voltage range. See Table 5-11.                                        |  |  |  |  |  |  |

| 4<br>LVWV   | <b>Low-Voltage Warning Voltage Select</b> — This bit selects the low voltage warning (LVW) trip point voltage. See Table 5-11.                                                                                            |  |  |  |  |  |  |

| 3<br>PPDF   | <ul> <li>Partial Power Down Flag — This read-only status bit indicates that the MCU has recovered from stop2 mode.</li> <li>0 MCU has not recovered from stop2 mode.</li> <li>1 MCU recovered from stop2 mode.</li> </ul> |  |  |  |  |  |  |

| 2<br>PPDACK | Partial Power Down Acknowledge — Writing a 1 to PPDACK clears the PPDF bit                                                                                                                                                |  |  |  |  |  |  |

| 0<br>PPDC   | <ul> <li>Partial Power Down Control — This write-once bit controls whether stop2 or stop3 mode is selected.</li> <li>0 Stop3 mode enabled.</li> <li>1 Stop2, partial power down, mode enabled.</li> </ul>                 |  |  |  |  |  |  |

### Table 5-11. LVD and LVW trip point typical values<sup>1</sup>

| LVDV:LVWV | LVW Trip Point             | LVD Trip Point             |

|-----------|----------------------------|----------------------------|

| 0:0       | V <sub>LVW0</sub> = 2.74 V | V <sub>LVD0</sub> = 2.56 V |

| 0:1       | V <sub>LVW1</sub> = 2.92 V |                            |

| 1:0       | V <sub>LVW2</sub> = 4.3 V  | V <sub>LVD1</sub> = 4.0 V  |

| 1:1       | V <sub>LVW3</sub> = 4.6 V  |                            |

<sup>1</sup> See Electrical Characteristics appendix for minimum and maximum values.

# Chapter 7 Central Processor Unit (S08CPUV2)

# 7.1 Introduction

This section provides summary information about the registers, addressing modes, and instruction set of the CPU of the HCS08 Family. For a more detailed discussion, refer to the *HCS08 Family Reference Manual, volume 1,* Freescale Semiconductor document order number HCS08RMV1/D.

The HCS08 CPU is fully source- and object-code-compatible with the M68HC08 CPU. Several instructions and enhanced addressing modes were added to improve C compiler efficiency and to support a new background debug system which replaces the monitor mode of earlier M68HC08 microcontrollers (MCU).

# 7.1.1 Features

Features of the HCS08 CPU include:

- Object code fully upward-compatible with M68HC05 and M68HC08 Families

- All registers and memory are mapped to a single 64-Kbyte address space

- 16-bit stack pointer (any size stack anywhere in 64-Kbyte address space)

- 16-bit index register (H:X) with powerful indexed addressing modes

- 8-bit accumulator (A)

- Many instructions treat X as a second general-purpose 8-bit register

- Seven addressing modes:

- Inherent Operands in internal registers

- Relative 8-bit signed offset to branch destination

- Immediate Operand in next object code byte(s)

- Direct Operand in memory at 0x0000–0x00FF

- Extended Operand anywhere in 64-Kbyte address space

- Indexed relative to H:X Five submodes including auto increment

- Indexed relative to SP Improves C efficiency dramatically

- Memory-to-memory data move instructions with four address mode combinations

- Overflow, half-carry, negative, zero, and carry condition codes support conditional branching on the results of signed, unsigned, and binary-coded decimal (BCD) operations

- Efficient bit manipulation instructions

- Fast 8-bit by 8-bit multiply and 16-bit by 8-bit divide instructions

- STOP and WAIT instructions to invoke low-power operating modes

Chapter 7 Central Processor Unit (S08CPUV2)

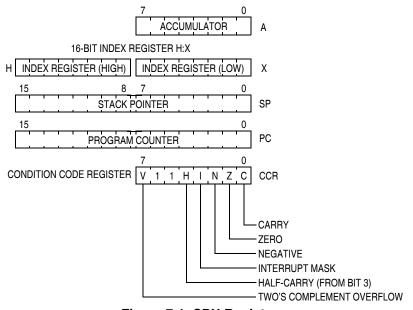

# 7.2 Programmer's Model and CPU Registers

Figure 7-1 shows the five CPU registers. CPU registers are not part of the memory map.

Figure 7-1. CPU Registers

# 7.2.1 Accumulator (A)

The A accumulator is a general-purpose 8-bit register. One operand input to the arithmetic logic unit (ALU) is connected to the accumulator and the ALU results are often stored into the A accumulator after arithmetic and logical operations. The accumulator can be loaded from memory using various addressing modes to specify the address where the loaded data comes from, or the contents of A can be stored to memory using various addressing modes to specify the address where the specify the address where data from A will be stored.

Reset has no effect on the contents of the A accumulator.

# 7.2.2 Index Register (H:X)

This 16-bit register is actually two separate 8-bit registers (H and X), which often work together as a 16-bit address pointer where H holds the upper byte of an address and X holds the lower byte of the address. All indexed addressing mode instructions use the full 16-bit value in H:X as an index reference pointer; however, for compatibility with the earlier M68HC05 Family, some instructions operate only on the low-order 8-bit half (X).

Many instructions treat X as a second general-purpose 8-bit register that can be used to hold 8-bit data values. X can be cleared, incremented, decremented, complemented, negated, shifted, or rotated. Transfer instructions allow data to be transferred from A or transferred to A where arithmetic and logical operations can then be performed.

For compatibility with the earlier M68HC05 Family, H is forced to 0x00 during reset. Reset has no effect on the contents of X.

# Chapter 9 Analog-to-Digital Converter (S08ADCV1)

# 9.1 Introduction

The 10-bit analog-to-digital converter (ADC) is a successive approximation ADC designed for operation within an integrated microcontroller system-on-chip.

### NOTE

The MC9S08SG8 Family of devices do not include stop1 mode.

The ADC channel assignments, alternate clock function, and hardware trigger function are configured as described below for the MC9S08SG8 family of devices.

### 9.1.1 Channel Assignments

The ADC channel assignments for the MC9S08SG8 devices are shown in Table 9-1. Reserved channels convert to an unknown value.

| ADCH  | Channel | Input           |

|-------|---------|-----------------|

| 00000 | AD0     | PTA0/ADP0       |

| 00001 | AD1     | PTA1/ADP1       |

| 00010 | AD2     | PTA2/ADP2       |

| 00011 | AD3     | PTA3/ADP3       |

| 00100 | AD4     | PTB0/ADP4       |

| 00101 | AD5     | PTB1/ADP5       |

| 00110 | AD6     | PTB2/ADP6       |

| 00111 | AD7     | PTB3/ADP7       |

| 01000 | AD8     | PTC0/ADP8       |

| 01001 | AD9     | PTC1/ADP9       |

| 01010 | AD10    | PTC2/ADP10      |

| 01011 | AD11    | PTC3/ADP11      |

| 01100 | AD12    | V <sub>SS</sub> |

| 01101 | AD13    | V <sub>SS</sub> |

| 01110 | AD14    | V <sub>SS</sub> |

| 01111 | AD15    | V <sub>SS</sub> |

| ADCH  | Channel           | Input                           |

|-------|-------------------|---------------------------------|

| 10000 | AD16              | V <sub>SS</sub>                 |

| 10001 | AD17              | V <sub>SS</sub>                 |

| 10010 | AD18              | V <sub>SS</sub>                 |

| 10011 | AD19              | V <sub>SS</sub>                 |

| 10100 | AD20              | V <sub>SS</sub>                 |

| 10101 | AD21              | Reserved                        |

| 10110 | AD22              | Reserved                        |

| 10111 | AD23              | Reserved                        |

| 11000 | AD24              | Reserved                        |

| 11001 | AD25              | Reserved                        |

| 11010 | AD26              | Temperature Sensor <sup>1</sup> |

| 11011 | AD27              | Internal Bandgap <sup>2</sup>   |

| 11100 | -                 | Reserved                        |

| 11101 | V <sub>REFH</sub> | V <sub>DD</sub>                 |

| 11110 | V <sub>REFL</sub> | V <sub>SS</sub>                 |

| 11111 | Module Disabled   | None                            |

<sup>1</sup> For information, see Section 9.1.4, "Temperature Sensor".

<sup>2</sup> Requires BGBE =1 in SPMSC1 see Section 5.7.7, "System Power Management Status and Control 2 Register (SPMSC2)". For value of bandgap voltage reference see A.6, "DC Characteristics".

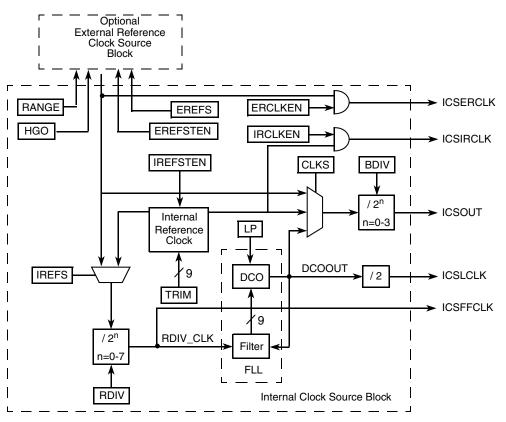

Internal Clock Source (S08ICSV2)

Figure 10-2. Internal Clock Source (ICS) Block Diagram

### 10.1.4 Modes of Operation

There are seven modes of operation for the ICS: FEI, FEE, FBI, FBILP, FBE, FBELP, and stop.

### 10.1.4.1 FLL Engaged Internal (FEI)

In FLL engaged internal mode, which is the default mode, the ICS supplies a clock derived from the FLL which is controlled by the internal reference clock. The BDC clock is supplied from the FLL.

### 10.1.4.2 FLL Engaged External (FEE)

In FLL engaged external mode, the ICS supplies a clock derived from the FLL which is controlled by an external reference clock. The BDC clock is supplied from the FLL.

### 10.1.4.3 FLL Bypassed Internal (FBI)

In FLL bypassed internal mode, the FLL is enabled and controlled by the internal reference clock, but is bypassed. The ICS supplies a clock derived from the internal reference clock. The BDC clock is supplied from the FLL.

If EREFSTEN is set and the ERCLKEN bit is written to 1, the external reference clock will keep running during stop mode in order to provide a fast recovery upon exiting stop.

# 10.4.7 Fixed Frequency Clock

The ICS presents the divided FLL reference clock as ICSFFCLK for use as an additional clock source for peripheral modules. The ICS provides an output signal (ICSFFE) which indicates when the ICS is providing ICSOUT frequencies four times or greater than the divided FLL reference clock (ICSFFCLK). In FLL Engaged mode (FEI and FEE) this is always true and ICSFFE is always high. In ICS Bypass modes, ICSFFE will get asserted for the following combinations of BDIV and RDIV values:

- BDIV=00 (divide by 1), RDIV  $\ge$  010

- BDIV=01 (divide by 2), RDIV  $\ge$  011

- BDIV=10 (divide by 4), RDIV  $\geq$  100

- BDIV=11 (divide by 8), RDIV  $\geq$  101

Inter-Integrated Circuit (S08IICV2)

| Table 11-8. IICD | <b>Field Descriptions</b> |

|------------------|---------------------------|

|------------------|---------------------------|

| Field       | Description                                                                                                                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0<br>DATA | <b>Data</b> — In master transmit mode, when data is written to the IICD, a data transfer is initiated. The most significant bit is sent first. In master receive mode, reading this register initiates receiving of the next byte of data. |

### NOTE

When transitioning out of master receive mode, the IIC mode should be switched before reading the IICD register to prevent an inadvertent initiation of a master receive data transfer.

In slave mode, the same functions are available after an address match has occurred.

The TX bit in IICC must correctly reflect the desired direction of transfer in master and slave modes for the transmission to begin. For instance, if the IIC is configured for master transmit but a master receive is desired, reading the IICD does not initiate the receive.

Reading the IICD returns the last byte received while the IIC is configured in master receive or slave receive modes. The IICD does not reflect every byte transmitted on the IIC bus, nor can software verify that a byte has been written to the IICD correctly by reading it back.

In master transmit mode, the first byte of data written to IICD following assertion of MST is used for the address transfer and should comprise of the calling address (in bit 7 to bit 1) concatenated with the required  $R/\overline{W}$  bit (in position bit 0).

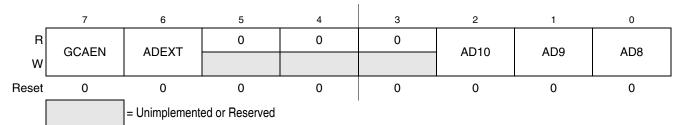

# 11.3.6 IIC Control Register 2 (IICC2)

Figure 11-8. IIC Control Register (IICC2)

#### Table 11-9. IICC2 Field Descriptions

| Field           | Description                                                                                                                                                                                     |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>GCAEN      | <ul> <li>General Call Address Enable. The GCAEN bit enables or disables general call address.</li> <li>0 General call address is disabled</li> <li>1 General call address is enabled</li> </ul> |

| 6<br>ADEXT      | <ul> <li>Address Extension. The ADEXT bit controls the number of bits used for the slave address.</li> <li>0 7-bit address scheme</li> <li>1 10-bit address scheme</li> </ul>                   |

| 2–0<br>AD[10:8] | Slave Address. The AD[10:8] field contains the upper three bits of the slave address in the 10-bit address scheme. This field is only valid when the ADEXT bit is set.                          |

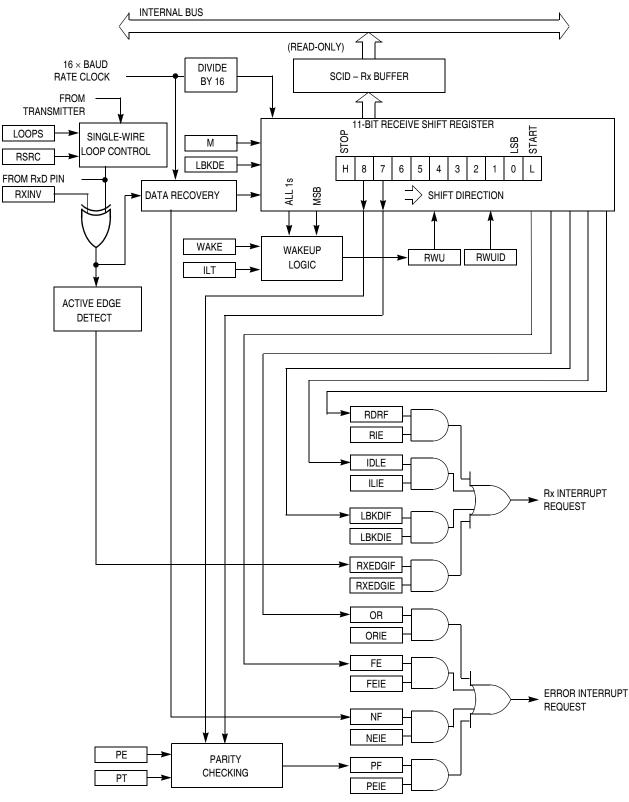

Figure 14-3 shows the receiver portion of the SCI.

Figure 14-3. SCI Receiver Block Diagram

Serial Communications Interface (S08SCIV4)

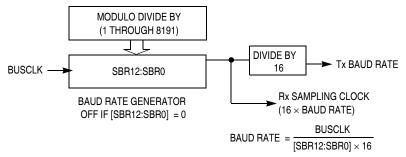

Figure 14-12. SCI Baud Rate Generation

SCI communications require the transmitter and receiver (which typically derive baud rates from independent clock sources) to use the same baud rate. Allowed tolerance on this baud frequency depends on the details of how the receiver synchronizes to the leading edge of the start bit and how bit sampling is performed.

The MCU resynchronizes to bit boundaries on every high-to-low transition, but in the worst case, there are no such transitions in the full 10- or 11-bit time character frame so any mismatch in baud rate is accumulated for the whole character time. For a Freescale Semiconductor SCI system whose bus frequency is driven by a crystal, the allowed baud rate mismatch is about  $\pm 4.5$  percent for 8-bit data format and about  $\pm 4$  percent for 9-bit data format. Although baud rate modulo divider settings do not always produce baud rates that exactly match standard rates, it is normally possible to get within a few percent, which is acceptable for reliable communications.

# 14.3.2 Transmitter Functional Description

This section describes the overall block diagram for the SCI transmitter, as well as specialized functions for sending break and idle characters. The transmitter block diagram is shown in Figure 14-2.

The transmitter output (TxD) idle state defaults to logic high (TXINV = 0 following reset). The transmitter output is inverted by setting TXINV = 1. The transmitter is enabled by setting the TE bit in SCIC2. This queues a preamble character that is one full character frame of the idle state. The transmitter then remains idle until data is available in the transmit data buffer. Programs store data into the transmit data buffer by writing to the SCI data register (SCID).

The central element of the SCI transmitter is the transmit shift register that is either 10 or 11 bits long depending on the setting in the M control bit. For the remainder of this section, we will assume M = 0, selecting the normal 8-bit data mode. In 8-bit data mode, the shift register holds a start bit, eight data bits, and a stop bit. When the transmit shift register is available for a new SCI character, the value waiting in the transmit data register is transferred to the shift register (synchronized with the baud rate clock) and the transmit data register empty (TDRE) status flag is set to indicate another character may be written to the transmit data buffer at SCID.

If no new character is waiting in the transmit data buffer after a stop bit is shifted out the TxD pin, the transmitter sets the transmit complete flag and enters an idle mode, with TxD high, waiting for more characters to transmit.

# 15.3 Modes of Operation

# 15.3.1 SPI in Stop Modes

The SPI is disabled in all stop modes, regardless of the settings before executing the STOP instruction. During either stop1 or stop2 mode, the SPI module will be fully powered down. Upon wake-up from stop1 or stop2 mode, the SPI module will be in the reset state. During stop3 mode, clocks to the SPI module are halted. No registers are affected. If stop3 is exited with a reset, the SPI will be put into its reset state. If stop3 is exited with an interrupt, the SPI continues from the state it was in when stop3 was entered.

# 15.4 Register Definition

The SPI has five 8-bit registers to select SPI options, control baud rate, report SPI status, and for transmit/receive data.

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all SPI registers. This section refers to registers and control bits only by their names, and a Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

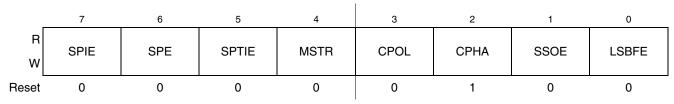

# 15.4.1 SPI Control Register 1 (SPIC1)

This read/write register includes the SPI enable control, interrupt enables, and configuration options.

Figure 15-5. SPI Control Register 1 (SPIC1)

| Field      | Description                                                                                                                                                                                                                                                                                                      |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SPIE  | <ul> <li>SPI Interrupt Enable (for SPRF and MODF) — This is the interrupt enable for SPI receive buffer full (SPRF) and mode fault (MODF) events.</li> <li>Interrupts from SPRF and MODF inhibited (use polling)</li> <li>When SPRF or MODF is 1, request a hardware interrupt</li> </ul>                        |

| 6<br>SPE   | <ul> <li>SPI System Enable — Disabling the SPI halts any transfer that is in progress, clears data buffers, and initializes internal state machines. SPRF is cleared and SPTEF is set to indicate the SPI transmit data buffer is empty.</li> <li>O SPI system inactive</li> <li>1 SPI system enabled</li> </ul> |

| 5<br>SPTIE | <ul> <li>SPI Transmit Interrupt Enable — This is the interrupt enable bit for SPI transmit buffer empty (SPTEF).</li> <li>Interrupts from SPTEF inhibited (use polling)</li> <li>When SPTEF is 1, hardware interrupt requested</li> </ul>                                                                        |

When a channel is configured for edge-aligned PWM (CPWMS=0, MSnB=1 and ELSnB:ELSnA not = 0:0), the data direction is overridden, the TPMxCHn pin is forced to be an output controlled by the TPM, and ELSnA controls the polarity of the PWM output signal on the pin. When ELSnB:ELSnA=1:0, the TPMxCHn pin is forced high at the start of each new period (TPMxCNT=0x0000), and the pin is forced low when the channel value register matches the timer counter. When ELSnA=1, the TPMxCHn pin is forced high when the channel value register matches the timer counter.

TPMxMODH:TPMxMODL = 0x0008 TPMxMODH:TPMxMODL = 0x0005

| TPMxCNTH:TPMxCNTL      | 0         | 1 | 2 | 3 | 4 | 5          | 6 | 7 | 8 | 0    | 1 | 2 |  |

|------------------------|-----------|---|---|---|---|------------|---|---|---|------|---|---|--|

| TPMxCHn ——<br>CHnF BIT | <br>      |   |   |   |   |            |   |   |   | <br> |   |   |  |

| TOF BIT                | <br> <br> |   |   |   |   | 1<br> <br> |   |   |   |      |   |   |  |

Figure 16-3. High-True Pulse of an Edge-Aligned PWM

| TPMxCNTH:TPMxCNTL | 0        | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 0 | 1 | 2 |  |

|-------------------|----------|---|---|---|---|---|---|---|---|---|---|---|--|

| TPMxCHn           | 1        |   |   |   |   |   |   |   |   | 1 |   |   |  |

|                   | <u> </u> |   |   |   |   |   |   |   |   |   |   |   |  |

| CHnF BIT          | 1        |   |   |   |   |   |   |   |   | 1 |   |   |  |

|                   |          |   |   |   |   |   |   |   |   |   |   |   |  |

| TOF BIT           |          |   |   |   |   | 1 |   |   |   |   |   |   |  |

Figure 16-4. Low-True Pulse of an Edge-Aligned PWM

TPMxMODH:TPMxMODL = 0x0008 TPMxMODH:TPMxMODL = 0x0005

# 16.3 Register Definition

This section consists of register descriptions in address order.

# 16.3.1 TPM Status and Control Register (TPMxSC)

TPMxSC contains the overflow status flag and control bits used to configure the interrupt enable, TPM configuration, clock source, and prescale factor. These controls relate to all channels within this timer module.

Figure 16-7. TPM Status and Control Register (TPMxSC)

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TOF         | Timer overflow flag. This read/write flag is set when the TPM counter resets to 0x0000 after reaching the modulo value programmed in the TPM counter modulo registers. Clear TOF by reading the TPM status and control register when TOF is set and then writing a logic 0 to TOF. If another TPM overflow occurs before the clearing sequence is complete, the sequence is reset so TOF would remain set after the clear sequence was completed for the earlier TOF. This is done so a TOF interrupt request cannot be lost during the clearing sequence for a previous TOF. Reset clears TOF. Writing a logic 1 to TOF has no effect.<br>0 TPM counter has not reached modulo value or overflow<br>1 TPM counter has overflowed |

| 6<br>TOIE        | Timer overflow interrupt enable. This read/write bit enables TPM overflow interrupts. If TOIE is set, an interrupt is generated when TOF equals one. Reset clears TOIE.<br>0 TOF interrupts inhibited (use for software polling)<br>1 TOF interrupts enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5<br>CPWMS       | <ul> <li>Center-aligned PWM select. When present, this read/write bit selects CPWM operating mode. By default, the TPM operates in up-counting mode for input capture, output compare, and edge-aligned PWM functions. Setting CPWMS reconfigures the TPM to operate in up/down counting mode for CPWM functions. Reset clears CPWMS.</li> <li>0 All channels operate as input capture, output compare, or edge-aligned PWM mode as selected by the MSnB:MSnA control bits in each channel's status and control register.</li> <li>1 All channels operate in center-aligned PWM mode.</li> </ul>                                                                                                                                  |

| 4–3<br>CLKS[B:A] | Clock source selects. As shown in Table 16-6, this 2-bit field is used to disable the TPM system or select one of three clock sources to drive the counter prescaler. The fixed system clock source is only meaningful in systems with a PLL-based system clock. When there is no PLL, the fixed-system clock source is the same as the bus rate clock. The external source is synchronized to the bus clock by TPM module, and the fixed system clock source (when a PLL is present) is synchronized to the bus clock by an on-chip synchronization circuit. When a PLL is present but not enabled, the fixed-system clock source is the same as the bus-rate clock.                                                             |

| 2–0<br>PS[2:0]   | Prescale factor select. This 3-bit field selects one of 8 division factors for the TPM clock input as shown in Table 16-7. This prescaler is located after any clock source synchronization or clock source selection so it affects the clock source selected to drive the TPM system. The new prescale factor will affect the clock source on the next system clock cycle after the new value is updated into the register bits.                                                                                                                                                                                                                                                                                                 |

#### Table 16-5. TPMxSC Field Descriptions

are used for PWM & output compare operation once normal execution resumes. Writes to the channel registers while BDM is active do not interfere with partial completion of a coherency sequence. After the coherency mechanism has been fully exercised, the channel registers are updated using the buffered values written (while BDM was not active) by the user.

# 16.4 Functional Description

All TPM functions are associated with a central 16-bit counter which allows flexible selection of the clock source and prescale factor. There is also a 16-bit modulo register associated with the main counter.

The CPWMS control bit chooses between center-aligned PWM operation for all channels in the TPM (CPWMS=1) or general purpose timing functions (CPWMS=0) where each channel can independently be configured to operate in input capture, output compare, or edge-aligned PWM mode. The CPWMS control bit is located in the main TPM status and control register because it affects all channels within the TPM and influences the way the main counter operates. (In CPWM mode, the counter changes to an up/down mode rather than the up-counting mode used for general purpose timer functions.)

The following sections describe the main counter and each of the timer operating modes (input capture, output compare, edge-aligned PWM, and center-aligned PWM). Because details of pin operation and interrupt activity depend upon the operating mode, these topics will be covered in the associated mode explanation sections.

# 16.4.1 Counter

All timer functions are based on the main 16-bit counter (TPMxCNTH:TPMxCNTL). This section discusses selection of the clock source, end-of-count overflow, up-counting vs. up/down counting, and manual counter reset.

### 16.4.1.1 Counter Clock Source

The 2-bit field, CLKSB:CLKSA, in the timer status and control register (TPMxSC) selects one of three possible clock sources or OFF (which effectively disables the TPM). See Table 16-6. After any MCU reset, CLKSB:CLKSA=0:0 so no clock source is selected, and the TPM is in a very low power state. These control bits may be read or written at any time and disabling the timer (writing 00 to the CLKSB:CLKSA field) does not affect the values in the counter or other timer registers.

the TPM counter is a free-running counter then the update is made when the TPM counter changes from 0xFFFE to 0xFFFF.

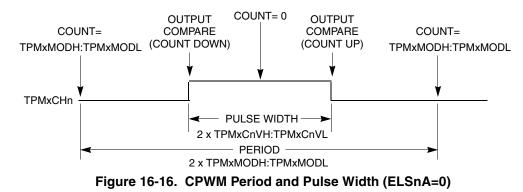

### 16.4.2.4 Center-Aligned PWM Mode

This type of PWM output uses the up/down counting mode of the timer counter (CPWMS=1). The output compare value in TPMxCnVH:TPMxCnVL determines the pulse width (duty cycle) of the PWM signal while the period is determined by the value in TPMxMODH:TPMxMODL. TPMxMODH:TPMxMODL should be kept in the range of 0x0001 to 0x7FFF because values outside this range can produce ambiguous results. ELSnA will determine the polarity of the CPWM output.

pulse width = 2 x (TPMxCnVH:TPMxCnVL)

period = 2 x (TPMxMODH:TPMxMODL); TPMxMODH:TPMxMODL=0x0001-0x7FFF

If the channel-value register TPMxCnVH:TPMxCnVL is zero or negative (bit 15 set), the duty cycle will be 0%. If TPMxCnVH:TPMxCnVL is a positive value (bit 15 clear) and is greater than the (non-zero) modulus setting, the duty cycle will be 100% because the duty cycle compare will never occur. This implies the usable range of periods set by the modulus register is 0x0001 through 0x7FFE (0x7FFF if you do not need to generate 100% duty cycle). This is not a significant limitation. The resulting period would be much longer than required for normal applications.

TPMxMODH:TPMxMODL=0x0000 is a special case that should not be used with center-aligned PWM mode. When CPWMS=0, this case corresponds to the counter running free from 0x0000 through 0xFFFF, but when CPWMS=1 the counter needs a valid match to the modulus register somewhere other than at 0x0000 in order to change directions from up-counting to down-counting.

The output compare value in the TPM channel registers (times 2) determines the pulse width (duty cycle) of the CPWM signal (Figure 16-16). If ELSnA=0, a compare occurred while counting up forces the CPWM output signal low and a compare occurred while counting down forces the output high. The counter counts up until it reaches the modulo setting in TPMxMODH:TPMxMODL, then counts down until it reaches zero. This sets the period equal to two times TPMxMODH:TPMxMODL.

Center-aligned PWM outputs typically produce less noise than edge-aligned PWMs because fewer I/O pin transitions are lined up at the same system clock edge. This type of PWM is also required for some types of motor drives.

A force-type breakpoint waits for the current instruction to finish and then acts upon the breakpoint request. The usual action in response to a breakpoint is to go to active background mode rather than continuing to the next instruction in the user application program.

The tag vs. force terminology is used in two contexts within the debug module. The first context refers to breakpoint requests from the debug module to the CPU. The second refers to match signals from the comparators to the debugger control logic. When a tag-type break request is sent to the CPU, a signal is entered into the instruction queue along with the opcode so that if/when this opcode ever executes, the CPU will effectively replace the tagged opcode with a BGND opcode so the CPU goes to active background mode rather than executing the tagged instruction. When the TRGSEL control bit in the DBGT register is set to select tag-type operation, the output from comparator A or B is qualified by a block of logic in the debug module that tracks opcodes and only produces a trigger to the debugger if the opcode at the compare address is actually executed. There is separate opcode tracking logic for each comparator so more than one compare event can be tracked through the instruction queue at a time.

# 17.3.5 Trigger Modes

The trigger mode controls the overall behavior of a debug run. The 4-bit TRG field in the DBGT register selects one of nine trigger modes. When TRGSEL = 1 in the DBGT register, the output of the comparator must propagate through an opcode tracking circuit before triggering FIFO actions. The BEGIN bit in DBGT chooses whether the FIFO begins storing data when the qualified trigger is detected (begin trace), or the FIFO stores data in a circular fashion from the time it is armed until the qualified trigger is detected (end trigger).

A debug run is started by writing a 1 to the ARM bit in the DBGC register, which sets the ARMF flag and clears the AF and BF flags and the CNT bits in DBGS. A begin-trace debug run ends when the FIFO gets full. An end-trace run ends when the selected trigger event occurs. Any debug run can be stopped manually by writing a 0 to ARM or DBGEN in DBGC.

In all trigger modes except event-only modes, the FIFO stores change-of-flow addresses. In event-only trigger modes, the FIFO stores data in the low-order eight bits of the FIFO.

The BEGIN control bit is ignored in event-only trigger modes and all such debug runs are begin type traces. When TRGSEL = 1 to select opcode fetch triggers, it is not necessary to use R/W in comparisons because opcode tags would only apply to opcode fetches that are always read cycles. It would also be unusual to specify TRGSEL = 1 while using a full mode trigger because the opcode value is normally known at a particular address.

The following trigger mode descriptions only state the primary comparator conditions that lead to a trigger. Either comparator can usually be further qualified with R/W by setting RWAEN (RWBEN) and the corresponding RWA (RWB) value to be matched against R/W. The signal from the comparator with optional R/W qualification is used to request a CPU breakpoint if BRKEN = 1 and TAG determines whether the CPU request will be a tag request or a force request.

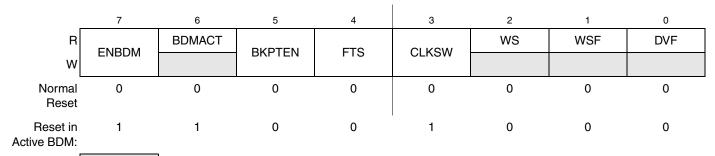

# 17.4.1.1 BDC Status and Control Register (BDCSCR)

This register can be read or written by serial BDC commands (READ\_STATUS and WRITE\_CONTROL) but is not accessible to user programs because it is not located in the normal memory map of the MCU.

= Unimplemented or Reserved

#### Figure 17-5. BDC Status and Control Register (BDCSCR)

#### Table 17-2. BDCSCR Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ENBDM  | <ul> <li>Enable BDM (Permit Active Background Mode) — Typically, this bit is written to 1 by the debug host shortly after the beginning of a debug session or whenever the debug host resets the target and remains 1 until a normal reset clears it.</li> <li>0 BDM cannot be made active (non-intrusive commands still allowed)</li> <li>1 BDM can be made active to allow active background mode commands</li> </ul>                                                                                                                                                                                                                                                |

| 6<br>BDMACT | Background Mode Active Status — This is a read-only status bit.0 BDM not active (user application program running)1 BDM active and waiting for serial commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5<br>BKPTEN | <ul> <li>BDC Breakpoint Enable — If this bit is clear, the BDC breakpoint is disabled and the FTS (force tag select) control bit and BDCBKPT match register are ignored.</li> <li>0 BDC breakpoint disabled</li> <li>1 BDC breakpoint enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4<br>FTS    | <ul> <li>Force/Tag Select — When FTS = 1, a breakpoint is requested whenever the CPU address bus matches the BDCBKPT match register. When FTS = 0, a match between the CPU address bus and the BDCBKPT register causes the fetched opcode to be tagged. If this tagged opcode ever reaches the end of the instruction queue, the CPU enters active background mode rather than executing the tagged opcode.</li> <li>0 Tag opcode at breakpoint address and enter active background mode if CPU attempts to execute that instruction</li> <li>1 Breakpoint match forces active background mode at next instruction boundary (address need not be an opcode)</li> </ul> |

| 3<br>CLKSW  | Select Source for BDC Communications Clock — CLKSW defaults to 0, which selects the alternate BDC clock source.         0       Alternate BDC clock source         1       MCU bus clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH **Technical Information Center** Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Asia/Pacific: Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2006-2014. All rights reserved.

MC9S08SG8 Rev. 8 1/2014