### NXP USA Inc. - S9S08SG8E2VTGR Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 12                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 512 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                        |

| Supplier Device Package    | 16-TSSOP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08sg8e2vtgr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

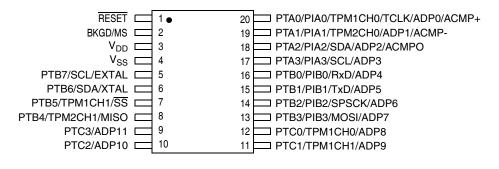

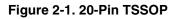

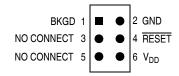

# Chapter 2 Pins and Connections

This section describes signals that connect to package pins. It includes pinout diagrams, recommended system connections, and detailed discussions of signals.

## 2.1 Device Pin Assignment

Figure 2-1 - Figure 2-3 shows the pin assignments for the MC9S08SG8 devices.

### NOTE

20-pin TSSOP package and 8-pin SOIC package are not available for the AEC Grade 0 high-temperature rated devices.

Figure 2-2. 16-Pin TSSOP

MC9S08SG8 MCU Series Data Sheet, Rev. 8

The voltage measured on the internally pulled up  $\overline{\text{RESET}}$  pin will not be pulled to  $V_{DD}$ . The internal gates connected to this pin are pulled to  $V_{DD}$ . If the  $\overline{\text{RESET}}$  pin is required to drive to a  $V_{DD}$  level an external pullup should be used.

### NOTE

In EMC-sensitive applications, an external RC filter is recommended on the  $\overline{\text{RESET}}$ . See Figure 2-4 for an example.

## 2.2.4 Background / Mode Select (BKGD/MS)

During a power-on-reset (POR) or background debug force reset (see Section 5.7.2, "System Background Debug Force Reset Register (SBDFR)," for more information), the BKGD/MS pin functions as a mode select pin. Immediately after any reset, the pin functions as the background pin and can be used for background debug communication. The BKGD/MS pin contains an internal pullup device.

If nothing is connected to this pin, the MCU will enter normal operating mode at the rising edge of the internal reset after a POR or force BDC reset. If a debug system is connected to the 6-pin standard background debug header, it can hold BKGD/MS low during a POR or immediately after issuing a background debug force reset, which will force the MCU to active background mode.

The BKGD pin is used primarily for background debug controller (BDC) communications using a custom protocol that uses 16 clock cycles of the target MCU's BDC clock per bit time. The target MCU's BDC clock could be as fast as the maximum bus clock rate, so there must never be any significant capacitance connected to the BKGD/MS pin that could interfere with background serial communications.

Although the BKGD pin is a pseudo open-drain pin, the background debug communication protocol provides brief, actively driven, high speedup pulses to ensure fast rise times. Small capacitances from cables and the absolute value of the internal pullup device play almost no role in determining rise and fall times on the BKGD pin.

## 2.2.5 General-Purpose I/O and Peripheral Ports

The MC9S08SG8 series of MCUs support up to 16 general-purpose I/O pins which are shared with on-chip peripheral functions (timers, serial I/O, ADC, etc.).

When a port pin is configured as a general-purpose output or a peripheral uses the port pin as an output, software can select one of two drive strengths and enable or disable slew rate control. When a port pin is configured as a general-purpose input or a peripheral uses the port pin as an input, software can enable a pull-up device. Immediately after reset, all of these pins are configured as high-impedance general-purpose inputs with internal pull-up devices disabled.

When an on-chip peripheral system is controlling a pin, data direction control bits still determine what is read from port data registers even though the peripheral module controls the pin direction by controlling the enable for the pin's output buffer. For information about controlling these pins as general-purpose I/O pins, see Chapter 6, "Parallel Input/Output Control."

**Chapter 2 Pins and Connections**

The MC9S08SG8 devices contain a ganged output drive feature that allows a safe and reliable method of allowing pins to be tied together externally to produce a higher output current drive. See Section 6.3, "Ganged Output" for more information for configuring the port pins for ganged output drive.

### NOTE

To avoid extra current drain from floating input pins, the reset initialization routine in the application program should either enable on-chip pull-up devices or change the direction of unused pins to outputs so they do not float.

When using the 8-pin devices, the user must either enable on-chip pullup devices or change the direction of non-bonded out port B and port C pins to outputs so the pins do not float.

When using the 16-pin devices, the user must either enable on-chip pullup devices or change the direction of non-bonded out port C pins to outputs so the pins do not float.

**Chapter 3 Modes of Operation**

Table 3-1 shows all of the control bits that affect stop mode selection and the mode selected under various conditions. The selected mode is entered following the execution of a STOP instruction.

| STOPE | ENBDM <sup>1</sup> | LVDE                | LVDSE   | PPDC | Stop Mode                                                              |

|-------|--------------------|---------------------|---------|------|------------------------------------------------------------------------|

| 0     | х                  | x                   |         | х    | Stop modes disabled; illegal opcode reset if STOP instruction executed |

| 1     | 1                  | )                   | ĸ       | х    | Stop3 with BDM enabled <sup>2</sup>                                    |

| 1     | 0                  | Both bits must be 1 |         | х    | Stop3 with voltage regulator active                                    |

| 1     | 0                  | Either              | bit a 0 | 0    | Stop3                                                                  |

| 1     | 0                  | Either              | bit a 0 | 1    | Stop2                                                                  |

Table 3-1. Stop Mode Selection

<sup>1</sup> ENBDM is located in the BDCSCR, which is only accessible through BDC commands, see Section 17.4.1.1, "BDC Status and Control Register (BDCSCR)".

$^2$  When in Stop3 mode with BDM enabled, The S<sub>IDD</sub> will be near R<sub>IDD</sub> levels because internal clocks are enabled.

## 3.6.1 Stop3 Mode

Stop3 mode is entered by executing a STOP instruction under the conditions as shown in Table 3-1. The states of all of the internal registers and logic, RAM contents, and I/O pin states are maintained.

Stop3 can be exited by asserting  $\overline{\text{RESET}}$ , or by an interrupt from one of the following sources: the real-time counter (RTC), LVD system, ACMP, ADC, SCI, or any pin interrupts.

If stop3 is exited by means of the  $\overline{\text{RESET}}$  pin, then the MCU is reset and operation will resume after taking the reset vector. Exit by means of one of the internal interrupt sources results in the MCU taking the appropriate interrupt vector.

## 3.6.1.1 LVD Enabled in Stop Mode

The LVD system is capable of generating either an interrupt or a reset when the supply voltage drops below the LVD voltage. For configuring the LVD system for interrupt or reset, refer to 5.6, "Low-Voltage Detect (LVD) System". If the LVD is enabled in stop (LVDE and LVDSE bits in SPMSC1 both set) at the time the CPU executes a STOP instruction, then the voltage regulator remains active during stop mode.

For the ADC to operate in stop mode, the LVD must be enabled when entering stop3.

For the ACMP to operate in stop mode with compare to internal bandgap option, the LVD must be enabled when entering stop3.

## 3.6.1.2 Active BDM Enabled in Stop Mode

Entry into the active background mode from run mode is enabled if ENBDM in BDCSCR is set. This register is described in Chapter 17, "Development Support." If ENBDM is set when the CPU executes a STOP instruction, the system clocks to the background debug logic remain active when the MCU enters stop mode. Because of this, background debug communication remains possible. In addition, the voltage regulator does not enter its low-power standby state but maintains full internal regulation.

**Chapter 4 Memory**

Table 4-2. Direct-Page Register Summary (Sheet 1 of 3)

| Address                            | Register<br>Name | Bit 7  | 6       | 5      | 4      | 3      | 2      | 1      | Bit 0  |

|------------------------------------|------------------|--------|---------|--------|--------|--------|--------|--------|--------|

| 0x00 <b>00</b>                     | PTAD             | 0      | 0       | _      | _      | PTAD3  | PTAD2  | PTAD1  | PTAD0  |

| 0x00 <b>01</b>                     | PTADD            | 0      | 0       |        | _      | PTADD3 | PTADD2 | PTADD1 | PTADD0 |

| 0x00 <b>02</b>                     | PTBD             | PTBD7  | PTBD6   | PTBD5  | PTBD4  | PTBD3  | PTBD2  | PTBD1  | PTBD0  |

| 0x00 <b>03</b>                     | PTBDD            | PTBDD7 | PTBDD6  | PTBDD5 | PTBDD4 | PTBDD3 | PTBDD2 | PTBDD1 | PTBDD0 |

| 0x00 <b>04</b>                     | PTCD             | 0      | 0       | 0      | 0      | PTCD3  | PTCD2  | PTCD1  | PTCD0  |

| 0x00 <b>05</b>                     | PTCDD            | 0      | 0       | 0      | 0      | PTCDD3 | PTCDD2 | PTCDD1 | PTCDD0 |

| 0x00 <b>06</b> –<br>0x00 <b>0D</b> | Reserved         | _      | _       | _      | _      |        | _      | _      | —      |

| 0x00 <b>0E</b>                     | ACMPSC           | ACME   | ACBGS   | ACF    | ACIE   | ACO    | ACOPE  | ACMOD1 | ACMOD0 |

| 0x00 <b>0F</b>                     | Reserved         |        | _       |        | _      |        |        | —      | —      |

| 0x00 <b>10</b>                     | ADCSC1           | COCO   | AIEN    | ADCO   |        |        | ADCH   |        | •      |

| 0x00 <b>11</b>                     | ADCSC2           | ADACT  | ADTRG   | ACFE   | ACFGT  | —      | —      | —      | —      |

| 0x00 <b>12</b>                     | ADCRH            | 0      | 0       | 0      | 0      | 0      | 0      | ADR9   | ADR8   |

| 0x00 <b>13</b>                     | ADCRL            | ADR7   | ADR6    | ADR5   | ADR4   | ADR3   | ADR2   | ADR1   | ADR0   |

| 0x00 <b>14</b>                     | ADCVH            | 0      | 0       | 0      | 0      | 0      | 0      | ADCV9  | ADCV8  |

| 0x00 <b>15</b>                     | ADCVL            | ADCV7  | ADCV6   | ADCV5  | ADCV4  | ADCV3  | ADCV2  | ADCV1  | ADCV0  |

| 0x00 <b>16</b>                     | ADCFG            | ADLPC  | AD      | VIV    | ADLSMP | MC     | DE     | ADICLK |        |

| 0x00 <b>17</b>                     | APCTL1           | ADPC7  | ADPC6   | ADPC5  | ADPC4  | ADPC3  | ADPC2  | ADPC1  | ADPC0  |

| 0x00 <b>18</b>                     | APCTL2           | 0      | 0       | 0      | 0      | ADPC11 | ADPC10 | ADPC9  | ADPC8  |

| 0x001 <b>9</b> –<br>0x001 <b>B</b> | Reserved         | _      | _       | _      | _      | _      | _      | _      | _      |

| 0x001 <b>C</b>                     | MTIMSC           | TOF    | TOIE    | TRST   | TSTP   | 0      | 0      | 0      | 0      |

| 0x001 <b>D</b>                     | MTIMCLK          | 0      | 0       | CL     | KS     |        | P      | S      |        |

| 0x001E                             | MTIMCNT          |        |         |        | CI     | NT     |        |        |        |

| 0x001F                             | MTIMMOD          | -      |         |        | МС     | DD     |        |        |        |

| 0x00 <b>20</b>                     | TPM1SC           | TOF    | TOIE    | CPWMS  | CLKSB  | CLKSA  | PS2    | PS1    | PS0    |

| 0x00 <b>21</b>                     | TPM1CNTH         | Bit 15 | 14      | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| 0x00 <b>22</b>                     | TPM1CNTL         | Bit 7  | 6       | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| 0x00 <b>23</b>                     | TPM1MODH         | Bit 15 | 14      | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| 0x00 <b>24</b>                     | TPM1MODL         | Bit 7  | 6       | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| 0x00 <b>25</b>                     | TPM1C0SC         | CH0F   | CH0IE   | MS0B   | MS0A   | ELS0B  | ELS0A  | 0      | 0      |

| 0x00 <b>26</b>                     | TPM1C0VH         | Bit 15 | 14      | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| 0x00 <b>27</b>                     | TPM1C0VL         | Bit 7  | 6       | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| 0x00 <b>28</b>                     | TPM1C1SC         | CH1F   | CH1IE   | MS1B   | MS1A   | ELS1B  | ELS1A  | 0      | 0      |

| 0x00 <b>29</b>                     | TPM1C1VH         | Bit 15 | 14      | 13     | 12     | 11     | 10     | 9      | Bit 8  |

| 0x00 <b>2A</b>                     | TPM1C1VL         | Bit 7  | 6       | 5      | 4      | 3      | 2      | 1      | Bit 0  |

| 0x00 <b>2B</b> –<br>0x00 <b>37</b> | Reserved         | —      | —       | —      | —      | —      | —      | _      | —      |

| 0x00 <b>38</b>                     | SCIBDH           | LBKDIE | RXEDGIE | 0      | SBR12  | SBR11  | SBR10  | SBR9   | SBR8   |

MC9S08SG8 MCU Series Data Sheet, Rev. 8

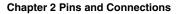

## 6.6.2.7 Port B Interrupt Pin Select Register (PTBPS)

Figure 6-17. Port B Interrupt Pin Select Register (PTBPS)

#### Table 6-16. PTBPS Register Field Descriptions

| Field             | Description                                                                                                                                                                                             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>PTBPS[3:0] | <ul> <li>Port B Interrupt Pin Selects — Each of the PTBPSn bits enable the corresponding port B interrupt pin.</li> <li>0 Pin not enabled as interrupt.</li> <li>1 Pin enabled as interrupt.</li> </ul> |

## 6.6.2.8 Port B Interrupt Edge Select Register (PTBES)

|        | 7 | 6 | 5 | 4 | 3      | 2      | 1      | 0      |

|--------|---|---|---|---|--------|--------|--------|--------|

| R      | 0 | 0 | 0 | 0 | PTBES3 | PTBES2 | PTBES1 | PTBES0 |

| w      |   |   |   |   | FIDESS | FIDE32 | FIDESI | FIDEOU |

| Reset: | 0 | 0 | 0 | 0 | 0      | 0      | 0      | 0      |

### Figure 6-18. Port B Edge Select Register (PTBES)

### Table 6-17. PTBES Register Field Descriptions

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>Port B Edge Selects — Each of the PTBESn bits serves a dual purpose by selecting the polarity of the active interrupt edge as well as selecting a pull-up or pull-down device if enabled.</li> <li>0 A pull-up device is connected to the associated pin and detects falling edge/low level for interrupt generation.</li> <li>1 A pull-down device is connected to the associated pin and detects rising edge/high level for interrupt generation.</li> </ul> |

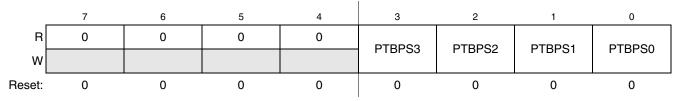

#### Analog-to-Digital Converter (S08ADCV1)

| Figure 9-3. Status and Control Register (ADCSC1 | Figure 9-3. | Status and | I Control | Register | (ADCSC1 | ) |

|-------------------------------------------------|-------------|------------|-----------|----------|---------|---|

|-------------------------------------------------|-------------|------------|-----------|----------|---------|---|

| Table 9-3. | ADCSC1 | Register | Field | Descriptions |

|------------|--------|----------|-------|--------------|

|------------|--------|----------|-------|--------------|

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>COCO   | <ul> <li>Conversion Complete Flag — The COCO flag is a read-only bit which is set each time a conversion is completed when the compare function is disabled (ACFE = 0). When the compare function is enabled (ACFE = 1) the COCO flag is set upon completion of a conversion only if the compare result is true. This bit is cleared whenever ADCSC1 is written or whenever ADCRL is read.</li> <li>0 Conversion not completed</li> <li>1 Conversion completed</li> </ul>                                                                                                                                                                                                                                                                           |

| 6<br>AIEN   | Interrupt Enable — AIEN is used to enable conversion complete interrupts. When COCO becomes set while       AIEN is high, an interrupt is asserted.         0       Conversion complete interrupt disabled         1       Conversion complete interrupt enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5<br>ADCO   | <ul> <li>Continuous Conversion Enable — ADCO is used to enable continuous conversions.</li> <li>One conversion following a write to the ADCSC1 when software triggered operation is selected, or one conversion following assertion of ADHWT when hardware triggered operation is selected.</li> <li>Continuous conversions initiated following a write to ADCSC1 when software triggered operation is selected. Continuous conversions are initiated by an ADHWT event when hardware triggered operation is selected.</li> </ul>                                                                                                                                                                                                                   |

| 4:0<br>ADCH | Input Channel Select — The ADCH bits form a 5-bit field which is used to select one of the input channels. The input channels are detailed in Figure 9-4.<br>The successive approximation converter subsystem is turned off when the channel select bits are all set to 1.<br>This feature allows for explicit disabling of the ADC and isolation of the input channel from all sources.<br>Terminating continuous conversions this way will prevent an additional, single conversion from being performed.<br>It is not necessary to set the channel select bits to all 1s to place the ADC in a low-power state when continuous conversion are not enabled because the module automatically enters a low-power state when a conversion completes. |

### Figure 9-4. Input Channel Select

| ADCH  | Input Select |

|-------|--------------|

| 00000 | AD0          |

| 00001 | AD1          |

| 00010 | AD2          |

| 00011 | AD3          |

| 00100 | AD4          |

| 00101 | AD5          |

| 00110 | AD6          |

| 00111 | AD7          |

| ADCH  | Input Select |

|-------|--------------|

| 10000 | AD16         |

| 10001 | AD17         |

| 10010 | AD18         |

| 10011 | AD19         |

| 10100 | AD20         |

| 10101 | AD21         |

| 10110 | AD22         |

| 10111 | AD23         |

### MC9S08SG8 MCU Series Data Sheet, Rev. 8

| ADICLK | Selected Clock Source         |  |  |  |  |  |  |

|--------|-------------------------------|--|--|--|--|--|--|

| 00     | Bus clock                     |  |  |  |  |  |  |

| 01     | Bus clock divided by 2        |  |  |  |  |  |  |

| 10     | Alternate clock (ALTCLK)      |  |  |  |  |  |  |

| 11     | 11 Asynchronous clock (ADACK) |  |  |  |  |  |  |

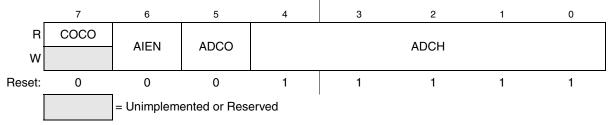

## 9.3.8 Pin Control 1 Register (APCTL1)

The pin control registers are used to disable the I/O port control of MCU pins used as analog inputs. APCTL1 is used to control the pins associated with channels 0–7 of the ADC module.

Figure 9-11. Pin Control 1 Register (APCTL1)

| Field      | Description                                                                                                                                                                          |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>ADPC7 | <ul> <li>ADC Pin Control 7 — ADPC7 is used to control the pin associated with channel AD7.</li> <li>0 AD7 pin I/O control enabled</li> <li>1 AD7 pin I/O control disabled</li> </ul> |  |

| 6<br>ADPC6 | <ul> <li>ADC Pin Control 6 — ADPC6 is used to control the pin associated with channel AD6.</li> <li>0 AD6 pin I/O control enabled</li> <li>1 AD6 pin I/O control disabled</li> </ul> |  |

| 5<br>ADPC5 | <ul> <li>ADC Pin Control 5 — ADPC5 is used to control the pin associated with channel AD5.</li> <li>0 AD5 pin I/O control enabled</li> <li>1 AD5 pin I/O control disabled</li> </ul> |  |

| 4<br>ADPC4 | <ul> <li>ADC Pin Control 4 — ADPC4 is used to control the pin associated with channel AD4.</li> <li>0 AD4 pin I/O control enabled</li> <li>1 AD4 pin I/O control disabled</li> </ul> |  |

| 3<br>ADPC3 | <ul> <li>ADC Pin Control 3 — ADPC3 is used to control the pin associated with channel AD3.</li> <li>0 AD3 pin I/O control enabled</li> <li>1 AD3 pin I/O control disabled</li> </ul> |  |

| 2<br>ADPC2 | <ul> <li>ADC Pin Control 2 — ADPC2 is used to control the pin associated with channel AD2.</li> <li>0 AD2 pin I/O control enabled</li> <li>1 AD2 pin I/O control disabled</li> </ul> |  |

### Table 9-9. APCTL1 Register Field Descriptions

## 10.1.2 Features

Key features of the ICS module follow. For device specific information, refer to the ICS Characteristics in the Electricals section of the documentation.

- Frequency-locked loop (FLL) is trimmable for accuracy

- 0.2% resolution using internal 32kHz reference

- 1.5% deviation over voltage and temperature using internal 32kHz reference

- Internal or external reference clocks up to 5MHz can be used to control the FLL

- 3 bit select for reference divider is provided

- Internal reference clock has 9 trim bits available

- Internal or external reference clocks can be selected as the clock source for the MCU

- Whichever clock is selected as the source can be divided down

- 2 bit select for clock divider is provided

- Allowable dividers are: 1, 2, 4, 8

- BDC clock is provided as a constant divide by 2 of the DCO output

- Control signals for a low power oscillator as the external reference clock are provided — HGO, RANGE, EREFS, ERCLKEN, EREFSTEN

- FLL Engaged Internal mode is automatically selected out of reset

## 10.1.3 Block Diagram

Figure 10-2 is the ICS block diagram.

## 10.1.4.4 FLL Bypassed Internal Low Power (FBILP)

In FLL bypassed internal low power mode, the FLL is disabled and bypassed, and the ICS supplies a clock derived from the internal reference clock. The BDC clock is not available.

## 10.1.4.5 FLL Bypassed External (FBE)

In FLL bypassed external mode, the FLL is enabled and controlled by an external reference clock, but is bypassed. The ICS supplies a clock derived from the external reference clock. The external reference clock can be an external crystal/resonator supplied by an OSC controlled by the ICS, or it can be another external clock source. The BDC clock is supplied from the FLL.

## 10.1.4.6 FLL Bypassed External Low Power (FBELP)

In FLL bypassed external low power mode, the FLL is disabled and bypassed, and the ICS supplies a clock derived from the external reference clock. The external reference clock can be an external crystal/resonator supplied by an OSC controlled by the ICS, or it can be another external clock source. The BDC clock is not available.

## 10.1.4.7 Stop (STOP)

In stop mode the FLL is disabled and the internal or external reference clocks can be selected to be enabled or disabled. The BDC clock is not available and the ICS does not provide an MCU clock source.

## **10.2 External Signal Description**

There are no ICS signals that connect off chip.

## **10.3 Register Definition**

Figure 10-1 is a summary of ICS registers.

| Name     |   | 7    | 6    | 5       | 4      | 3    | 2     | 1        | 0         |

|----------|---|------|------|---------|--------|------|-------|----------|-----------|

| ICSC1    | R | C    | CLKS |         | RDIV   |      | IREFS | IRCLKEN  | IREFSTEN  |

|          | W | CLK5 |      |         | norv   |      |       | INCEREN  |           |

| ICSC2    | R | BDIV |      | RANGE   | HGO    | LP   | EREFS | ERCLKEN  | EREFSTEN  |

|          | W |      |      | HANGE   | nao    | LF   | ENERS | ENGLINEN |           |

| ICSTRM   | R |      |      |         |        | TRIM |       |          |           |

| ICSTRIVI | W |      |      | ואווח ו |        |      |       |          |           |

| ICSSC    | R | 0    | 0    | 0       | IREFST | CL   | KST   | OSCINIT  | FTRIM     |

|          | W |      |      |         |        |      |       |          | ואווררד ד |

```

Table 10-1. ICS Register Summary

```

| Field | Description                                                                                                                                                                                                                                                                                                                      |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | <b>OSC Initialization</b> — If the external reference clock is selected by ERCLKEN or by the ICS being in FEE, FBE, or FBELP mode, and if EREFS is set, then this bit is set after the initialization cycles of the external oscillator clock have completed. This bit is only cleared when either ERCLKEN or EREFS are cleared. |

| 0     | <b>ICS Fine Trim</b> — The FTRIM bit controls the smallest adjustment of the internal reference clock frequency. Setting FTRIM will increase the period and clearing FTRIM will decrease the period by the smallest amount possible.                                                                                             |

Table 10-5. ICS Status and Control Register Field Descriptions (continued)

# 10.4 Functional Description

## 10.4.1 Operational Modes

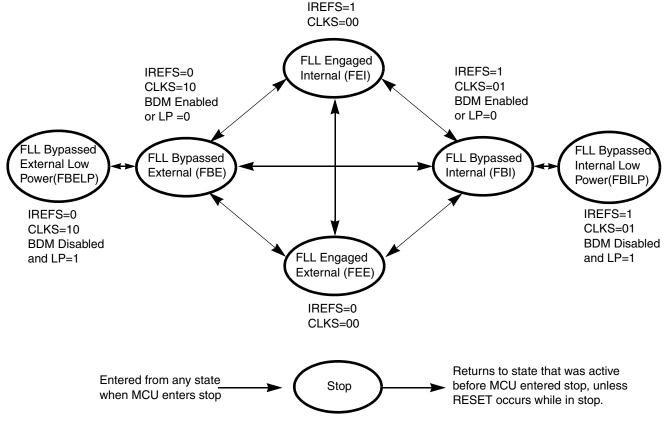

Figure 10-7. Clock Switching Modes

The seven states of the ICS are shown as a state diagram and are described below. The arrows indicate the allowed movements between the states.

### 10.4.1.1 FLL Engaged Internal (FEI)

FLL engaged internal (FEI) is the default mode of operation and is entered when all the following conditions occur:

Inter-Integrated Circuit (S08IICV2)

# 11.3.3 IIC Control Register (IICC1)

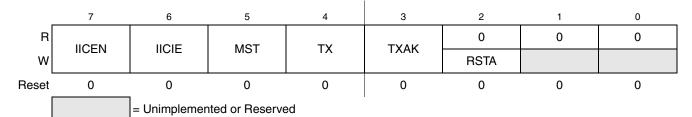

Figure 11-5. IIC Control Register (IICC1)

### Table 11-6. IICC1 Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>IICEN | IIC Enable. The IICEN bit determines whether the IIC module is enabled.         0 IIC is not enabled         1 IIC is enabled                                                                                                                                                                                                                                               |

| 6<br>IICIE | <ul> <li>IIC Interrupt Enable. The IICIE bit determines whether an IIC interrupt is requested.</li> <li>0 IIC interrupt request not enabled</li> <li>1 IIC interrupt request enabled</li> </ul>                                                                                                                                                                             |

| 5<br>MST   | <ul> <li>Master Mode Select. The MST bit changes from a 0 to a 1 when a start signal is generated on the bus and master mode is selected. When this bit changes from a 1 to a 0 a stop signal is generated and the mode of operation changes from master to slave.</li> <li>0 Slave mode</li> <li>1 Master mode</li> </ul>                                                  |

| 4<br>TX    | <b>Transmit Mode Select.</b> The TX bit selects the direction of master and slave transfers. In master mode, this bit should be set according to the type of transfer required. Therefore, for address cycles, this bit is always high. When addressed as a slave, this bit should be set by software according to the SRW bit in the status register. 0 Receive 1 Transmit |

| 3<br>TXAK  | Transmit Acknowledge Enable. This bit specifies the value driven onto the SDA during data acknowledge<br>cycles for master and slave receivers.0An acknowledge signal is sent out to the bus after receiving one data byte<br>11No acknowledge signal response is sent                                                                                                      |

| 2<br>RSTA  | <b>Repeat start.</b> Writing a 1 to this bit generates a repeated start condition provided it is the current master. This bit is always read as cleared. Attempting a repeat at the wrong time results in loss of arbitration.                                                                                                                                              |

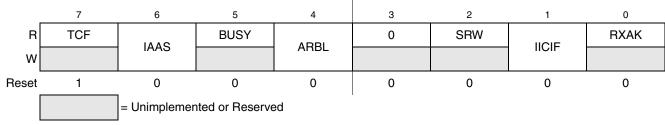

## 11.3.4 IIC Status Register (IICS)

MC9S08SG8 MCU Series Data Sheet, Rev. 8

Inter-Integrated Circuit (S08IICV2)

## 11.4.1.8 Handshaking

The clock synchronization mechanism can be used as a handshake in data transfer. Slave devices may hold the SCL low after completion of one byte transfer (9 bits). In such a case, it halts the bus clock and forces the master clock into wait states until the slave releases the SCL line.

## 11.4.1.9 Clock Stretching

The clock synchronization mechanism can be used by slaves to slow down the bit rate of a transfer. After the master has driven SCL low the slave can drive SCL low for the required period and then release it. If the slave SCL low period is greater than the master SCL low period then the resulting SCL bus signal low period is stretched.

## 11.4.2 10-bit Address

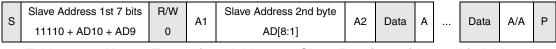

For 10-bit addressing, 0x11110 is used for the first 5 bits of the first address byte. Various combinations of read/write formats are possible within a transfer that includes 10-bit addressing.

## 11.4.2.1 Master-Transmitter Addresses a Slave-Receiver

The transfer direction is not changed (see Table 11-10). When a 10-bit address follows a start condition, each slave compares the first seven bits of the first byte of the slave address (11110XX) with its own address and tests whether the eighth bit (R/W direction bit) is 0. More than one device can find a match and generate an acknowledge (A1). Then, each slave that finds a match compares the eight bits of the second byte of the slave address with its own address. Only one slave finds a match and generates an acknowledge (A2). The matching slave remains addressed by the master until it receives a stop condition (P) or a repeated start condition (Sr) followed by a different slave address.

Table 11-10. Master-Transmitter Addresses Slave-Receiver with a 10-bit Address

After the master-transmitter has sent the first byte of the 10-bit address, the slave-receiver sees an IIC interrupt. Software must ensure the contents of IICD are ignored and not treated as valid data for this interrupt.

### 11.4.2.2 Master-Receiver Addresses a Slave-Transmitter

The transfer direction is changed after the second R/W bit (see Table 11-11). Up to and including acknowledge bit A2, the procedure is the same as that described for a master-transmitter addressing a slave-receiver. After the repeated start condition (Sr), a matching slave remembers that it was addressed before. This slave then checks whether the first seven bits of the first byte of the slave address following Sr are the same as they were after the start condition (S) and tests whether the eighth (R/W) bit is 1. If there is a match, the slave considers that it has been addressed as a transmitter and generates acknowledge A3. The slave-transmitter remains addressed until it receives a stop condition (P) or a repeated start condition (Sr) followed by a different slave address.

Writing 0 to TE does not immediately release the pin to be a general-purpose I/O pin. Any transmit activity that is in progress must first be completed. This includes data characters in progress, queued idle characters, and queued break characters.

## 14.3.2.1 Send Break and Queued Idle

The SBK control bit in SCIC2 is used to send break characters which were originally used to gain the attention of old teletype receivers. Break characters are a full character time of logic 0 (10 bit times including the start and stop bits). A longer break of 13 bit times can be enabled by setting BRK13 = 1. Normally, a program would wait for TDRE to become set to indicate the last character of a message has moved to the transmit shifter, then write 1 and then write 0 to the SBK bit. This action queues a break character to be sent as soon as the shifter is available. If SBK is still 1 when the queued break moves into the shifter (synchronized to the baud rate clock), an additional break character is queued. If the receiving device is another Freescale Semiconductor SCI, the break characters will be received as 0s in all eight data bits and a framing error (FE = 1) occurs.

When idle-line wakeup is used, a full character time of idle (logic 1) is needed between messages to wake up any sleeping receivers. Normally, a program would wait for TDRE to become set to indicate the last character of a message has moved to the transmit shifter, then write 0 and then write 1 to the TE bit. This action queues an idle character to be sent as soon as the shifter is available. As long as the character in the shifter does not finish while TE = 0, the SCI transmitter never actually releases control of the TxD pin. If there is a possibility of the shifter finishing while TE = 0, set the general-purpose I/O controls so the pin that is shared with TxD is an output driving a logic 1. This ensures that the TxD line will look like a normal idle line even if the SCI loses control of the port pin between writing 0 and then 1 to TE.

The length of the break character is affected by the BRK13 and M bits as shown below.

| BRK13 | М                | Break Character Length |  |  |  |  |

|-------|------------------|------------------------|--|--|--|--|

| 0     | 0                | 10 bit times           |  |  |  |  |

| 0     | 1                | 11 bit times           |  |  |  |  |

| 1     | 0                | 13 bit times           |  |  |  |  |

| 1     | 1 1 14 bit times |                        |  |  |  |  |

Table 14-8. Break Character Length

## 14.3.3 Receiver Functional Description

In this section, the receiver block diagram (Figure 14-3) is used as a guide for the overall receiver functional description. Next, the data sampling technique used to reconstruct receiver data is described in more detail. Finally, two variations of the receiver wakeup function are explained.

The receiver input is inverted by setting RXINV = 1. The receiver is enabled by setting the RE bit in SCIC2. Character frames consist of a start bit of logic 0, eight (or nine) data bits (LSB first), and a stop bit of logic 1. For information about 9-bit data mode, refer to Section 14.3.5.1, "8- and 9-Bit Data Modes." For the remainder of this discussion, we assume the SCI is configured for normal 8-bit data mode.

After receiving the stop bit into the receive shifter, and provided the receive data register is not already full, the data character is transferred to the receive data register and the receive data register full (RDRF)

### Table 16-8. TPMxCnSC Field Descriptions (continued)

| Field                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>MSnA             | <ul> <li>Mode select A for TPM channel n. When CPWMS=0 and MSnB=0, MSnA configures TPM channel n for input-capture mode or output compare mode. Refer to Table 16-9 for a summary of channel mode and setup controls.</li> <li>Note: If the associated port pin is not stable for at least two bus clock cycles before changing to input capture mode, it is possible to get an unexpected indication of an edge trigger.</li> </ul>                                                                                                                                                                                                                                                                                                  |

| 3–2<br>ELSnB<br>ELSnA | Edge/level select bits. Depending upon the operating mode for the timer channel as set by CPWMS:MSnB:MSnA and shown in Table 16-9, these bits select the polarity of the input edge that triggers an input capture event, select the level that will be driven in response to an output compare match, or select the polarity of the PWM output. Setting ELSnB:ELSnA to 0:0 configures the related timer pin as a general purpose I/O pin not related to any timer functions. This function is typically used to temporarily disable an input capture channel or to make the timer pin available as a general purpose I/O pin when the associated timer channel is set up as a software timer that does not require the use of a pin. |

| CPWMS | MSnB:MSnA | ELSnB:ELSnA | Mode                  | Configuration                                                                    |  |  |  |  |

|-------|-----------|-------------|-----------------------|----------------------------------------------------------------------------------|--|--|--|--|

| х     | XX        | 00          |                       | Pin not used for TPM - revert to general purpose I/O or other peripheral control |  |  |  |  |

| 0     | 00        | 01          | Input capture         | Capture on rising edge only                                                      |  |  |  |  |

|       |           | 10          |                       | Capture on falling edge only                                                     |  |  |  |  |

|       |           | 11          |                       | Capture on rising or<br>falling edge                                             |  |  |  |  |

|       | 01        | 01          | Output compare        | Toggle output on<br>compare                                                      |  |  |  |  |

|       |           | 10          |                       | Clear output on<br>compare                                                       |  |  |  |  |

|       |           | 11          |                       | Set output on compare                                                            |  |  |  |  |

|       | 1X        | 10          | Edge-aligned<br>PWM   | High-true pulses (clear<br>output on compare)                                    |  |  |  |  |

|       |           | X1          |                       | Low-true pulses (set output on compare)                                          |  |  |  |  |

| 1     | XX        | 10          | Center-aligned<br>PWM | High-true pulses (clear output on compare-up)                                    |  |  |  |  |

|       |           | X1          |                       | Low-true pulses (set output on compare-up)                                       |  |  |  |  |

## 16.3.5 TPM Channel Value Registers (TPMxCnVH:TPMxCnVL)

These read/write registers contain the captured TPM counter value of the input capture function or the output compare value for the output compare or PWM functions. The channel registers are cleared by reset.

# Chapter 17 Development Support

# 17.1 Introduction

Development support systems in the HCS08 include the background debug controller (BDC) and the on-chip debug module (DBG). The BDC provides a single-wire debug interface to the target MCU that provides a convenient interface for programming the on-chip FLASH and other nonvolatile memories. The BDC is also the primary debug interface for development and allows non-intrusive access to memory data and traditional debug features such as CPU register modify, breakpoints, and single instruction trace commands.

In the HCS08 Family, address and data bus signals are not available on external pins (not even in test modes). Debug is done through commands fed into the target MCU via the single-wire background debug interface. The debug module provides a means to selectively trigger and capture bus information so an external development system can reconstruct what happened inside the MCU on a cycle-by-cycle basis without having external access to the address and data signals.

## 17.1.1 Forcing Active Background

The method for forcing active background mode depends on the specific HCS08 derivative. For the MC9S08SG8, you can force active background after a power-on reset by holding the BKGD pin low as the device exits the reset condition. You can also force active background by driving BKGD low immediately after a serial background command that writes a one to the BDFR bit in the SBDFR register. Other causes of reset including an external pin reset or an internally generated error reset ignore the state of the BKGD pin and reset into normal user mode. If no debug pod is connected to the BKGD pin, the MCU will always reset into normal operating mode.

• Non-intrusive commands can be executed at any time even while the user's program is running. Non-intrusive commands allow a user to read or write MCU memory locations or access status and control registers within the background debug controller.

Typically, a relatively simple interface pod is used to translate commands from a host computer into commands for the custom serial interface to the single-wire background debug system. Depending on the development tool vendor, this interface pod may use a standard RS-232 serial port, a parallel printer port, or some other type of communications such as a universal serial bus (USB) to communicate between the host PC and the pod. The pod typically connects to the target system with ground, the BKGD pin, RESET, and sometimes  $V_{DD}$ . An open-drain connection to reset allows the host to force a target system reset, which is useful to regain control of a lost target system or to control startup of a target system before the on-chip nonvolatile memory has been programmed. Sometimes  $V_{DD}$  can be used to allow the pod to use power from the target system to avoid the need for a separate power supply. However, if the pod is powered separately, it can be connected to a running target system without forcing a target system reset or otherwise disturbing the running application program.

Figure 17-1. BDM Tool Connector

## 17.2.1 BKGD Pin Description

BKGD is the single-wire background debug interface pin. The primary function of this pin is for bidirectional serial communication of active background mode commands and data. During reset, this pin is used to select between starting in active background mode or starting the user's application program. This pin is also used to request a timed sync response pulse to allow a host development tool to determine the correct clock frequency for background debug serial communications.

BDC serial communications use a custom serial protocol first introduced on the M68HC12 Family of microcontrollers. This protocol assumes the host knows the communication clock rate that is determined by the target BDC clock rate. All communication is initiated and controlled by the host that drives a high-to-low edge to signal the beginning of each bit time. Commands and data are sent most significant bit first (MSB first). For a detailed description of the communications protocol, refer to Section 17.2.2, "Communication Details."

If a host is attempting to communicate with a target MCU that has an unknown BDC clock rate, a SYNC command may be sent to the target MCU to request a timed sync response signal from which the host can determine the correct communication speed.

BKGD is a pseudo-open-drain pin and there is an on-chip pullup so no external pullup resistor is required. Unlike typical open-drain pins, the external RC time constant on this pin, which is influenced by external capacitance, plays almost no role in signal rise time. The custom protocol provides for brief, actively driven speedup pulses to force rapid rise times on this pin without risking harmful drive level conflicts. Refer to Section 17.2.2, "Communication Details," for more detail.

The SYNC command is unlike other BDC commands because the host does not necessarily know the correct communications speed to use for BDC communications until after it has analyzed the response to the SYNC command.

To issue a SYNC command, the host:

- Drives the BKGD pin low for at least 128 cycles of the slowest possible BDC clock (The slowest clock is normally the reference oscillator/64 or the self-clocked rate/64.)

- Drives BKGD high for a brief speedup pulse to get a fast rise time (This speedup pulse is typically one cycle of the fastest clock in the system.)

- Removes all drive to the BKGD pin so it reverts to high impedance

- Monitors the BKGD pin for the sync response pulse

The target, upon detecting the SYNC request from the host (which is a much longer low time than would ever occur during normal BDC communications):

- Waits for BKGD to return to a logic high

- Delays 16 cycles to allow the host to stop driving the high speedup pulse

- Drives BKGD low for 128 BDC clock cycles

- Drives a 1-cycle high speedup pulse to force a fast rise time on BKGD

- Removes all drive to the BKGD pin so it reverts to high impedance

The host measures the low time of this 128-cycle sync response pulse and determines the correct speed for subsequent BDC communications. Typically, the host can determine the correct communication speed within a few percent of the actual target speed and the communication protocol can easily tolerate speed errors of several percent.

## 17.2.4 BDC Hardware Breakpoint

The BDC includes one relatively simple hardware breakpoint that compares the CPU address bus to a 16-bit match value in the BDCBKPT register. This breakpoint can generate a forced breakpoint or a tagged breakpoint. A forced breakpoint causes the CPU to enter active background mode at the first instruction boundary following any access to the breakpoint address. The tagged breakpoint causes the instruction opcode at the breakpoint address to be tagged so that the CPU will enter active background mode rather than executing that instruction if and when it reaches the end of the instruction queue. This implies that tagged breakpoints can only be placed at the address of an instruction opcode while forced breakpoints can be set at any address.

The breakpoint enable (BKPTEN) control bit in the BDC status and control register (BDCSCR) is used to enable the breakpoint logic (BKPTEN = 1). When BKPTEN = 0, its default value after reset, the breakpoint logic is disabled and no BDC breakpoints are requested regardless of the values in other BDC breakpoint registers and control bits. The force/tag select (FTS) control bit in BDCSCR is used to select forced (FTS = 1) or tagged (FTS = 0) type breakpoints.

The on-chip debug module (DBG) includes circuitry for two additional hardware breakpoints that are more flexible than the simple breakpoint in the BDC module.

## 17.4.3.5 Debug FIFO High Register (DBGFH)

This register provides read-only access to the high-order eight bits of the FIFO. Writes to this register have no meaning or effect. In the event-only trigger modes, the FIFO only stores data into the low-order byte of each FIFO word, so this register is not used and will read 0x00.

Reading DBGFH does not cause the FIFO to shift to the next word. When reading 16-bit words out of the FIFO, read DBGFH before reading DBGFL because reading DBGFL causes the FIFO to advance to the next word of information.

## 17.4.3.6 Debug FIFO Low Register (DBGFL)

This register provides read-only access to the low-order eight bits of the FIFO. Writes to this register have no meaning or effect.

Reading DBGFL causes the FIFO to shift to the next available word of information. When the debug module is operating in event-only modes, only 8-bit data is stored into the FIFO (high-order half of each FIFO word is unused). When reading 8-bit words out of the FIFO, simply read DBGFL repeatedly to get successive bytes of data from the FIFO. It isn't necessary to read DBGFH in this case.

Do not attempt to read data from the FIFO while it is still armed (after arming but before the FIFO is filled or ARMF is cleared) because the FIFO is prevented from advancing during reads of DBGFL. This can interfere with normal sequencing of reads from the FIFO.

Reading DBGFL while the debugger is not armed causes the address of the most-recently fetched opcode to be stored to the last location in the FIFO. By reading DBGFH then DBGFL periodically, external host software can develop a profile of program execution. After eight reads from the FIFO, the ninth read will return the information that was stored as a result of the first read. To use the profiling feature, read the FIFO eight times without using the data to prime the sequence and then begin using the data to get a delayed picture of what addresses were being executed. The information stored into the FIFO on reads of DBGFL (while the FIFO is not armed) is the address of the most-recently fetched opcode.

|                                                | Conditions                                   |          | Symb                    | Min | Typ <sup>1</sup> | Max  | Unit             | Temp Rated <sup>2</sup> |                   |                                           |  |

|------------------------------------------------|----------------------------------------------|----------|-------------------------|-----|------------------|------|------------------|-------------------------|-------------------|-------------------------------------------|--|

| Characteristic                                 |                                              | С        |                         |     |                  |      |                  | Stand<br>ard            | AEC<br>Grade<br>0 | Comment                                   |  |

| Conversion                                     | Short sample<br>(ADLSMP=0)                   | D        | t <sub>ADC</sub>        | _   | 20               | _    | ADCK<br>cycles   | х                       | х                 |                                           |  |

| time (including sample time)                   | Long sample<br>(ADLSMP=1)                    |          |                         | _   | 40               | _    |                  | х                       | х                 | See ADC<br>Chapter<br>for                 |  |

| Sample time                                    | Short sample<br>(ADLSMP=0)                   | D        | t <sub>ADS</sub>        | _   | 3.5              | _    | ADCK             | х                       | х                 | conversion<br>time<br>variances           |  |

| Sample line                                    | Long sample<br>(ADLSMP=1)                    |          |                         | _   | 23.5             | _    | cycles           | х                       | х                 | variances                                 |  |

| Total                                          | 10 bit mode                                  |          |                         | _   | ±1.5             | ±3.5 | LSB <sup>2</sup> | х                       | х                 |                                           |  |

| unadjusted<br>error (Includes<br>quantization) | 8 bit mode                                   | Р        | E <sub>TUE</sub>        | _   | ±0.7             | ±1.5 | LSB <sup>3</sup> | х                       | x                 |                                           |  |

|                                                | 10 bit mode                                  |          | DNL                     | _   | ±0.5             | ±1.0 | LSB <sup>3</sup> | х                       | х                 |                                           |  |

| Differential<br>Non-Linearity                  | 8 bit mode                                   | - P      |                         | _   | ±0.3             | ±0.5 |                  | х                       | х                 |                                           |  |

|                                                | Monotonicity and No-Missing-Codes guaranteed |          |                         |     |                  |      |                  |                         |                   |                                           |  |

| Integral                                       | 10 bit mode                                  | -        | INL                     |     | ±0.5             | ±1.0 | LSB <sup>3</sup> | х                       | х                 |                                           |  |

| non-linearity                                  | 8 bit mode                                   | — Т      |                         | _   | ±0.3             | ±0.5 |                  | х                       | х                 |                                           |  |

| Zero-scale                                     | 10 bit mode                                  | — Р      | E <sub>ZS</sub>         | _   | ±1.5             | ±2.5 | LSB <sup>3</sup> | х                       | х                 |                                           |  |

| error                                          | 8 bit mode                                   |          |                         | _   | ±0.5             | ±0.7 |                  | х                       | х                 |                                           |  |

| Full-scale error                               | 10 bit mode                                  | _ т      | E <sub>FS</sub>         | 0   | ±1.0             | ±1.5 | LSB <sup>3</sup> | х                       | х                 |                                           |  |

| $(V_{ADIN} = V_{DD})$                          | 8 bit mode                                   |          |                         | 0   | ±0.5             | ±0.5 |                  | х                       | х                 |                                           |  |

| Quantization                                   | 10 bit mode                                  | D        | EQ                      | —   | —                | ±0.5 | LSB <sup>3</sup> | х                       | х                 |                                           |  |

| error                                          | 8 bit mode                                   |          |                         | —   | —                | ±0.5 |                  | х                       | х                 |                                           |  |

| Input leakage                                  | 10 bit mode                                  |          | EIL                     | 0   | ±0.2             | ±2.5 | LSB <sup>3</sup> | х                       | х                 | Pad                                       |  |

| error                                          | 8 bit mode                                   | D        |                         | 0   | ±0.1             | ±1   |                  | х                       | х                 | leakage <sup>3</sup> *<br>R <sub>AS</sub> |  |

| Temp sensor<br>slope                           | –40°C to 25°C                                | <u> </u> | m                       | _   | 3.266            | _    | mV/°C –          | х                       | х                 |                                           |  |

|                                                | 25°C to 125°C                                | — D      |                         |     | 3.638            | —    |                  | х                       | х                 |                                           |  |

| Temp sensor<br>voltage                         | 25°C                                         | D        | V <sub>TEMP</sub><br>25 | _   | 1.396            | _    | V                | х                       | х                 |                                           |  |

### Table A-12. ADC Characteristics (continued)

<sup>1</sup> Typical values assume V<sub>DD</sub> = 5.0 V, Temp = 25°C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2</sup> Electrical characteristics only apply to the temperature rated devices marked with x.

<sup>3</sup> Based on input pad leakage current. Refer to pad electricals.