Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | S08                                                         |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 40MHz                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                          |

| Peripherals                | LVD, POR, PWM, WDT                                          |

| Number of I/O              | 16                                                          |

| Program Memory Size        | 8KB (8K x 8)                                                |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 512 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | A/D 12x10b                                                  |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 105°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                             |

| Supplier Device Package    | 20-TSSOP                                                    |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=s9s08sg8e2vtjr |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Section Number**

#### Title

#### Page

|     | 4.5.3    | Program and Erase Command Execution          | 50 |

|-----|----------|----------------------------------------------|----|

|     | 4.5.4    | Burst Program Execution                      | 51 |

|     | 4.5.5    | Access Errors                                | 53 |

|     | 4.5.6    | FLASH Block Protection                       | 53 |

|     | 4.5.7    | Vector Redirection                           | 54 |

| 4.6 | Security | 7                                            | 54 |

| 4.7 | FLASH    | Registers and Control Bits                   | 55 |

|     | 4.7.1    | FLASH Clock Divider Register (FCDIV)         | 56 |

|     | 4.7.2    | FLASH Options Register (FOPT and NVOPT)      | 57 |

|     | 4.7.3    | FLASH Configuration Register (FCNFG)         |    |

|     | 4.7.4    | FLASH Protection Register (FPROT and NVPROT) |    |

|     | 4.7.5    | FLASH Status Register (FSTAT)                | 59 |

|     | 4.7.6    | FLASH Command Register (FCMD)                | 60 |

|     |          |                                              |    |

## Chapter 5 Resets, Interrupts, and General System Control

| 5.1 | Introdu  | ction                                                          | 61 |

|-----|----------|----------------------------------------------------------------|----|

| 5.2 | Feature  | s                                                              | 61 |

| 5.3 | MCU R    | leset                                                          | 61 |

| 5.4 | Compu    | ter Operating Properly (COP) Watchdog                          | 62 |

| 5.5 | Interrup | ots                                                            | 63 |

|     | 5.5.1    | Interrupt Stack Frame                                          | 64 |

|     | 5.5.2    | Interrupt Vectors, Sources, and Local Masks                    | 65 |

| 5.6 | Low-Vo   | bltage Detect (LVD) System                                     | 67 |

|     | 5.6.1    | Power-On Reset Operation                                       | 67 |

|     | 5.6.2    | Low-Voltage Detection (LVD) Reset Operation                    | 67 |

|     | 5.6.3    | Low-Voltage Warning (LVW) Interrupt Operation                  | 67 |

| 5.7 | Reset, I | nterrupt, and System Control Registers and Control Bits        | 67 |

|     | 5.7.1    | System Reset Status Register (SRS)                             | 68 |

|     | 5.7.2    | System Background Debug Force Reset Register (SBDFR)           | 69 |

|     | 5.7.3    | System Options Register 1 (SOPT1)                              |    |

|     | 5.7.4    | System Options Register 2 (SOPT2)                              | 71 |

|     | 5.7.5    | System Device Identification Register (SDIDH, SDIDL)           | 72 |

|     | 5.7.6    | System Power Management Status and Control 1 Register (SPMSC1) | 73 |

|     | 5.7.7    | System Power Management Status and Control 2 Register (SPMSC2) | 74 |

|     |          |                                                                |    |

## Chapter 6 Parallel Input/Output Control

| 6.1 | Port Data and Data Direction           |  |

|-----|----------------------------------------|--|

|     | Pull-up, Slew Rate, and Drive Strength |  |

|     | Ganged Output                          |  |

|     | Pin Interrupts                         |  |

| 0.1 |                                        |  |

Chapter 1 Device Overview

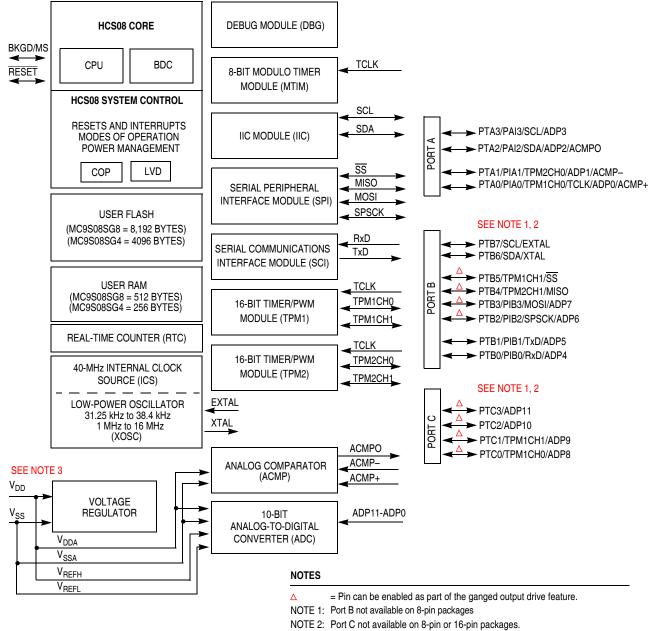

# 1.2 MCU Block Diagram

The block diagram in Figure 1-1 shows the structure of the MC9S08SG8 MCU.

NOTE 3: V<sub>DDA</sub>/V<sub>BEEH</sub> and V<sub>SSA</sub>/V<sub>BEEI</sub>, are double bonded to V<sub>DD</sub> and V<sub>SS</sub> respectively.

Figure 1-1. MC9S08SG8 Block Diagram

|        |         |       |          |                      | Prior                | rity              |                   |                    |  |

|--------|---------|-------|----------|----------------------|----------------------|-------------------|-------------------|--------------------|--|

| Pi     | in Numb | er    | L        | owest                |                      | Highest           |                   |                    |  |

| 20-pin | 16-pin  | 8-pin | Port Pin | Alt 1 Alt 2          |                      | Alt 3             | Alt 4             | Alt5               |  |

| 1      | 1       | 1     |          |                      |                      |                   |                   | RESET              |  |

| 2      | 2       | 2     |          |                      |                      |                   | BKGD              | MS                 |  |

| 3      | 3       | 3     |          |                      |                      |                   |                   | V <sub>DD</sub>    |  |

| 4      | 4       | 4     |          |                      |                      |                   |                   | V <sub>SS</sub>    |  |

| 5      | 5       |       | PTB7     | SCL <sup>1</sup>     | EXTAL                |                   |                   |                    |  |

| 6      | 6       |       | PTB6     | SDA <sup>1</sup>     | XTAL                 |                   |                   |                    |  |

| 7      | 7       | _     | PTB5     | TPM1CH1 <sup>2</sup> | SS                   | PTC0 <sup>3</sup> |                   |                    |  |

| 8      | 8       | _     | PTB4     | TPM2CH1              | MISO                 | PTC0 <sup>3</sup> |                   |                    |  |

| 9      | —       | _     | PTC3     |                      |                      | PTC0 <sup>3</sup> | ADP11             |                    |  |

| 10     | —       | _     | PTC2     |                      |                      | PTC0 <sup>3</sup> | ADP10             |                    |  |

| 11     | —       | _     | PTC1     |                      | TPM1CH1 <sup>2</sup> | PTC0 <sup>3</sup> | ADP9              |                    |  |

| 12     | —       | _     | PTC0     |                      | TPM1CH0 <sup>2</sup> | PTC0 <sup>3</sup> | ADP8              |                    |  |

| 13     | 9       | _     | PTB3     | PIB3                 | MOSI                 | PTC0 <sup>3</sup> | ADP7              |                    |  |

| 14     | 10      | _     | PTB2     | PIB2                 | SPSCK                | PTC0 <sup>3</sup> | ADP6              |                    |  |

| 15     | 11      | _     | PTB1     | PIB1                 | TxD                  |                   | ADP5              |                    |  |

| 16     | 12      | _     | PTB0     | PIB0                 | RxD                  |                   | ADP4              |                    |  |

| 17     | 13      | 5     | PTA3     | PIA3                 | SCL <sup>1</sup>     |                   | ADP3              |                    |  |

| 18     | 14      | 6     | PTA2     | PIA2                 | SDA <sup>1</sup>     |                   | ADP2              | ACMPO              |  |

| 19     | 15      | 7     | PTA1     | PIA1                 | TPM2CH0              |                   | ADP1 <sup>4</sup> | ACMP-4             |  |

| 20     | 16      | 8     | PTA0     | PIA0                 | TPM1CH0 <sup>2</sup> | TCLK              | ADP0 <sup>4</sup> | ACMP+ <sup>4</sup> |  |

<sup>1</sup> IIC pins can be repositioned using IICPS in SOPT2, default reset locations are on PTA2 and PTA3.

<sup>2</sup> TPM1CHx pins can be repositioned using TPM1PS in SOPT2, default reset locations are on PTA0 and PTB5.

<sup>3</sup> This port pin is part of the ganged output feature. When pin is enabled for ganged output, it will have priority over all digital modules. The output data, drive strength and slew-rate control of this port pin will follow the configuration for the PTC0 pin, even in 16-pin packages where PTC0 doesn't bond out. Ganged output not available in 8-pin packages.

<sup>4</sup> If ACMP and ADC are both enabled, both will have access to the pin.

# Chapter 5 Resets, Interrupts, and General System Control

# 5.1 Introduction

This section discusses basic reset and interrupt mechanisms and the various sources of reset and interrupt in the MC9S08SG8. Some interrupt sources from peripheral modules are discussed in greater detail within other sections of this data sheet. This section gathers basic information about all reset and interrupt sources in one place for easy reference. A few reset and interrupt sources, including the computer operating properly (COP) watchdog are not part of on-chip peripheral systems with their own chapters.

## 5.2 Features

Reset and interrupt features include:

- Multiple sources of reset for flexible system configuration and reliable operation

- Reset status register (SRS) to indicate source of most recent reset

- Separate interrupt vector for each module (reduces polling overhead) (see Table 5-2)

## 5.3 MCU Reset

Resetting the MCU provides a way to start processing from a known set of initial conditions. During reset, most control and status registers are forced to initial values and the program counter is loaded from the reset vector (0xFFFE:0xFFFF). On-chip peripheral modules are disabled and I/O pins are initially configured as general-purpose high-impedance inputs with pull-up devices disabled. The I bit in the condition code register (CCR) is set to block maskable interrupts so the user program has a chance to initialize the stack pointer (SP) and system control settings. SP is forced to 0x00FF at reset.

The MC9S08SG8 has the following sources for reset:

- Power-on reset (POR)

- External pin reset (PIN)

- Low-voltage detect (LVD)

- Computer operating properly (COP) timer

- Illegal opcode detect (ILOP)

- Illegal address detect (ILAD)

- Background debug forced reset

Each of these sources, with the exception of the background debug forced reset, has an associated bit in the system reset status register (SRS).

Chapter 7 Central Processor Unit (S08CPUV2)

## 7.4.3 Wait Mode Operation

The WAIT instruction enables interrupts by clearing the I bit in the CCR. It then halts the clocks to the CPU to reduce overall power consumption while the CPU is waiting for the interrupt or reset event that will wake the CPU from wait mode. When an interrupt or reset event occurs, the CPU clocks will resume and the interrupt or reset event will be processed normally.

If a serial BACKGROUND command is issued to the MCU through the background debug interface while the CPU is in wait mode, CPU clocks will resume and the CPU will enter active background mode where other serial background commands can be processed. This ensures that a host development system can still gain access to a target MCU even if it is in wait mode.

## 7.4.4 Stop Mode Operation

Usually, all system clocks, including the crystal oscillator (when used), are halted during stop mode to minimize power consumption. In such systems, external circuitry is needed to control the time spent in stop mode and to issue a signal to wake the target MCU when it is time to resume processing. Unlike the earlier M68HC05 and M68HC08 MCUs, the HCS08 can be configured to keep a minimum set of clocks running in stop mode. This optionally allows an internal periodic signal to wake the target MCU from stop mode.

When a host debug system is connected to the background debug pin (BKGD) and the ENBDM control bit has been set by a serial command through the background interface (or because the MCU was reset into active background mode), the oscillator is forced to remain active when the MCU enters stop mode. In this case, if a serial BACKGROUND command is issued to the MCU through the background debug interface while the CPU is in stop mode, CPU clocks will resume and the CPU will enter active background mode where other serial background commands can be processed. This ensures that a host development system can still gain access to a target MCU even if it is in stop mode.

Recovery from stop mode depends on the particular HCS08 and whether the oscillator was stopped in stop mode. Refer to the Modes of Operation chapter for more details.

## 7.4.5 BGND Instruction

The BGND instruction is new to the HCS08 compared to the M68HC08. BGND would not be used in normal user programs because it forces the CPU to stop processing user instructions and enter the active background mode. The only way to resume execution of the user program is through reset or by a host debug system issuing a GO, TRACE1, or TAGGO serial command through the background debug interface.

Software-based breakpoints can be set by replacing an opcode at the desired breakpoint address with the BGND opcode. When the program reaches this breakpoint address, the CPU is forced to active background mode rather than continuing the user program.

| Source<br>Form | Operation                                                            | Address<br>Mode | Object Code | ycles | Cyc-by-Cyc<br>Details | Affect<br>on CCR |      |

|----------------|----------------------------------------------------------------------|-----------------|-------------|-------|-----------------------|------------------|------|

|                |                                                                      | PA              |             | Ú.    |                       | VH               | INZC |

| TXS            | Transfer Index Reg. to SP SP $\leftarrow$ (H:X) – 0x0001             | INH             | 94          | 2     | fp                    |                  |      |

| WAIT           | Enable Interrupts; Wait for Interrupt I bit $\leftarrow$ 0; Halt CPU | INH             | 8 F         | 2+    | fp                    |                  | 0    |

**Source Form:** Everything in the source forms columns, *except expressions in italic characters*, is literal information which must appear in the assembly source file exactly as shown. The initial 3- to 5-letter mnemonic and the characters (# , () and +) are always a literal characters.

*n* Any label or expression that evaluates to a single integer in the range 0-7.

*opr8i* Any label or expression that evaluates to an 8-bit immediate value.

opr16i Any label or expression that evaluates to a 16-bit immediate value.

opr8a Any label or expression that evaluates to an 8-bit direct-page address (0x00xx).

opr16a Any label or expression that evaluates to a 16-bit address.

oprx8 Any label or expression that evaluates to an unsigned 8-bit value, used for indexed addressing.

oprx16 Any label or expression that evaluates to a 16-bit value, used for indexed addressing.

rel Any label or expression that refers to an address that is within -128 to +127 locations from the start of the next instruction.

#### **Operation Symbols:**

| A | Accumulator |

|---|-------------|

|   |             |

- CCR Condition code register

- H Index register high byte

- M Memory location

- n Any bit

- opr Operand (one or two bytes)

- PC Program counter

- PCH Program counter high byte

- PCL Program counter low byte

- rel Relative program counter offset byte

- SP Stack pointer

- SPL Stack pointer low byte

- X Index register low byte

- & Logical AND

- Logical OR

- Logical EXCLUSIVE OR

- () Contents of

- + Add

- Subtract, Negation (two's complement)

- × Multiply

- ÷ Divide

- # Immediate value

- $\leftarrow \qquad \text{Loaded with} \qquad$

- : Concatenated with

#### CCR Bits:

- V Overflow bit

- H Half-carry bit

- I Interrupt mask

- N Negative bit

- Z Zero bit

- C Carry/borrow bit

#### Addressing Modes:

- DIR Direct addressing mode

- EXT Extended addressing mode

- IMM Immediate addressing mode

- INH Inherent addressing mode

- IX Indexed, no offset addressing mode

- IX1 Indexed, 8-bit offset addressing mode

- IX2 Indexed, 16-bit offset addressing mode

- IX+ Indexed, no offset, post increment addressing mode

- IX1+ Indexed, 8-bit offset, post increment addressing mode

- REL Relative addressing mode

- SP1 Stack pointer, 8-bit offset addressing mode

- SP2 Stack pointer 16-bit offset addressing mode

#### Cycle-by-Cycle Codes:

- f Free cycle. This indicates a cycle where the CPU does not require use of the system buses. An f cycle is always one cycle of the system bus clock and is always a read cycle.

- p Progryam fetch; read from next consecutive location in program memory

- r Read 8-bit operand

- s Push (write) one byte onto stack

- u Pop (read) one byte from stack

- v Read vector from 0xFFxx (high byte first)

- w Write 8-bit operand

#### CCR Effects:

- Þ Set or cleared

- Not affected

- U Undefined

#### 9.1.5 Features

Features of the ADC module include:

- Linear successive approximation algorithm with 10 bits resolution.

- Up to 28 analog inputs.

- Output formatted in 10- or 8-bit right-justified format.

- Single or continuous conversion (automatic return to idle after single conversion).

- Configurable sample time and conversion speed/power.

- Conversion complete flag and interrupt.

- Input clock selectable from up to four sources.

- Operation in wait or stop3 modes for lower noise operation.

- Asynchronous clock source for lower noise operation.

- Selectable asynchronous hardware conversion trigger.

- Automatic compare with interrupt for less-than, or greater-than or equal-to, programmable value.

#### 9.1.6 Block Diagram

Figure 9-2 provides a block diagram of the ADC module

#### 10.1.4.4 FLL Bypassed Internal Low Power (FBILP)

In FLL bypassed internal low power mode, the FLL is disabled and bypassed, and the ICS supplies a clock derived from the internal reference clock. The BDC clock is not available.

## 10.1.4.5 FLL Bypassed External (FBE)

In FLL bypassed external mode, the FLL is enabled and controlled by an external reference clock, but is bypassed. The ICS supplies a clock derived from the external reference clock. The external reference clock can be an external crystal/resonator supplied by an OSC controlled by the ICS, or it can be another external clock source. The BDC clock is supplied from the FLL.

### 10.1.4.6 FLL Bypassed External Low Power (FBELP)

In FLL bypassed external low power mode, the FLL is disabled and bypassed, and the ICS supplies a clock derived from the external reference clock. The external reference clock can be an external crystal/resonator supplied by an OSC controlled by the ICS, or it can be another external clock source. The BDC clock is not available.

### 10.1.4.7 Stop (STOP)

In stop mode the FLL is disabled and the internal or external reference clocks can be selected to be enabled or disabled. The BDC clock is not available and the ICS does not provide an MCU clock source.

## **10.2 External Signal Description**

There are no ICS signals that connect off chip.

## **10.3 Register Definition**

Figure 10-1 is a summary of ICS registers.

| Name   |   | 7    | 6 | 5     | 4      | 3    | 2      | 1       | 0           |

|--------|---|------|---|-------|--------|------|--------|---------|-------------|

| ICSC1  | R | CLKS |   | RDIV  |        |      | IREFS  | IRCLKEN | IREFSTEN    |

|        | W |      |   |       |        |      |        |         | IREFOLEN    |

| ICSC2  | R | BDIV |   | RANGE | HGO    | LP   | EREFS  | ERCLKEN | EREFSTEN    |

| 10302  | W |      |   | HANGE | 100    | LI   | LITELO | LHOLKLN |             |

| ICSTRM | R |      |   |       |        | TRIM |        |         |             |

|        | W |      |   |       |        |      |        |         |             |

| ICSSC  | R | 0    | 0 | 0     | IREFST | CL   | KST    | OSCINIT | FTRIM       |

|        | W |      |   |       |        |      |        |         | 1 1 1 11101 |

```

Table 10-1. ICS Register Summary

```

#### Internal Clock Source (S08ICSV2)

The CLKS bits can also be changed at anytime, but the RDIV bits must be changed simultaneously so that the resulting frequency stays in the range of 31.25 kHz to 39.0625 kHz. The actual switch to the newly selected clock will not occur until after a few full cycles of the new clock. If the newly selected clock is not available, the previous clock will remain selected.

### 10.4.3 Bus Frequency Divider

The BDIV bits can be changed at anytime and the actual switch to the new frequency will occur immediately.

### 10.4.4 Low Power Bit Usage

The low power bit (LP) is provided to allow the FLL to be disabled and thus conserve power when it is not being used. However, in some applications it may be desirable to enable the FLL and allow it to lock for maximum accuracy before switching to an FLL engaged mode. Do this by writing the LP bit to 0.

### 10.4.5 Internal Reference Clock

When IRCLKEN is set the internal reference clock signal will be presented as ICSIRCLK, which can be used as an additional clock source. The ICSIRCLK frequency can be re-targeted by trimming the period of the internal reference clock. This can be done by writing a new value to the TRIM bits in the ICSTRM register. Writing a larger value will slow down the ICSIRCLK frequency, and writing a smaller value to the ICSTRM register will speed up the ICSIRCLK frequency. The TRIM bits will effect the ICSOUT frequency if the ICS is in FLL engaged internal (FEI), FLL bypassed internal (FBI), or FLL bypassed internal low power (FBILP) mode. The TRIM and FTRIM value will not be affected by a reset.

Until ICSIRCLK is trimmed, programming low reference divider (RDIV) factors may result in ICSOUT frequencies that exceed the maximum chip-level frequency and violate the chip-level clock timing specifications (see the Device Overview chapter).

If IREFSTEN is set and the IRCLKEN bit is written to 1, the internal reference clock will keep running during stop mode in order to provide a fast recovery upon exiting stop.

All MCU devices are factory programmed with a trim value in a reserved memory location. This value can be copied to the ICSTRM register during reset initialization. The factory trim value does not include the FTRIM bit. For finer precision, the user can trim the internal oscillator in the application and set the FTRIM bit accordingly.

### 10.4.6 Optional External Reference Clock

The ICS module can support an external reference clock with frequencies between 31.25 kHz to 5 MHz in all modes. When the ERCLKEN is set, the external reference clock signal will be presented as ICSERCLK, which can be used as an additional clock source. When IREFS = 1, the external reference clock will not be used by the FLL and will only be used as ICSERCLK. In these modes, the frequency can be equal to the maximum frequency the chip-level timing specifications will support (see the Device Overview chapter).

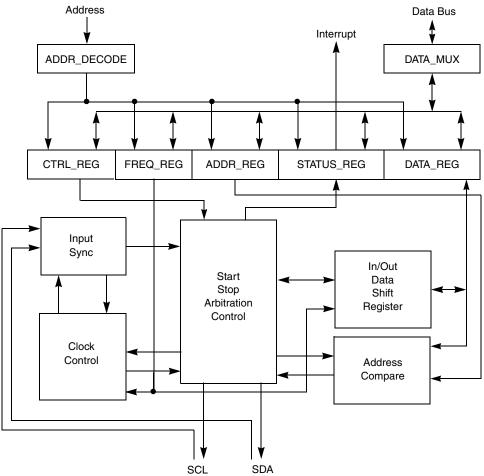

Inter-Integrated Circuit (S08IICV2)

Figure 11-2. IIC Functional Block Diagram

# 11.2 External Signal Description

This section describes each user-accessible pin signal.

### 11.2.1 SCL — Serial Clock Line

The bidirectional SCL is the serial clock line of the IIC system.

### 11.2.2 SDA — Serial Data Line

The bidirectional SDA is the serial data line of the IIC system.

## **11.3 Register Definition**

This section consists of the IIC register descriptions in address order.

Refer to the direct-page register summary in the memory chapter of this document for the absolute address assignments for all IIC registers. This section refers to registers and control bits only by their names. A

Inter-Integrated Circuit (S08IICV2)

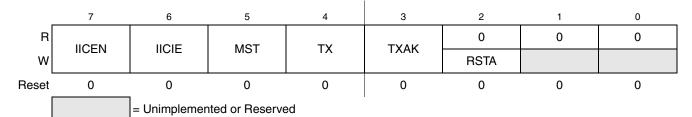

# 11.3.3 IIC Control Register (IICC1)

Figure 11-5. IIC Control Register (IICC1)

#### Table 11-6. IICC1 Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                       |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>IICEN | <ul> <li>IIC Enable. The IICEN bit determines whether the IIC module is enabled.</li> <li>0 IIC is not enabled</li> <li>1 IIC is enabled</li> </ul>                                                                                                                                                                                                                               |

| 6<br>IICIE | <ul> <li>IIC Interrupt Enable. The IICIE bit determines whether an IIC interrupt is requested.</li> <li>0 IIC interrupt request not enabled</li> <li>1 IIC interrupt request enabled</li> </ul>                                                                                                                                                                                   |

| 5<br>MST   | <ul> <li>Master Mode Select. The MST bit changes from a 0 to a 1 when a start signal is generated on the bus and master mode is selected. When this bit changes from a 1 to a 0 a stop signal is generated and the mode of operation changes from master to slave.</li> <li>0 Slave mode</li> <li>1 Master mode</li> </ul>                                                        |

| 4<br>TX    | <b>Transmit Mode Select.</b> The TX bit selects the direction of master and slave transfers. In master mode, this bit should be set according to the type of transfer required. Therefore, for address cycles, this bit is always high. When addressed as a slave, this bit should be set by software according to the SRW bit in the status register.<br>0 Receive<br>1 Transmit |

| 3<br>ТХАК  | <ul> <li>Transmit Acknowledge Enable. This bit specifies the value driven onto the SDA during data acknowledge cycles for master and slave receivers.</li> <li>0 An acknowledge signal is sent out to the bus after receiving one data byte</li> <li>1 No acknowledge signal response is sent</li> </ul>                                                                          |

| 2<br>RSTA  | <b>Repeat start.</b> Writing a 1 to this bit generates a repeated start condition provided it is the current master. This bit is always read as cleared. Attempting a repeat at the wrong time results in loss of arbitration.                                                                                                                                                    |

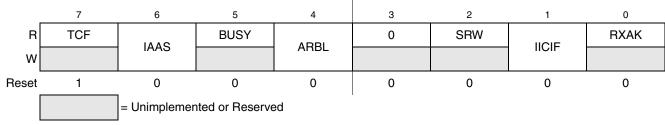

## 11.3.4 IIC Status Register (IICS)

MC9S08SG8 MCU Series Data Sheet, Rev. 8

| Real-Time Counter (S08RTCV1)   |      |      |      |      |      |      |  |  |  |  |

|--------------------------------|------|------|------|------|------|------|--|--|--|--|

| Internal 1-kHz<br>Clock Source |      | nnn  | nnn  |      |      |      |  |  |  |  |

| RTC Clock<br>(RTCPS = 0xA)     |      |      |      |      |      |      |  |  |  |  |

| RTCCNT                         | 0x52 | 0x53 | 0x54 | 0x55 | 0x00 | 0x01 |  |  |  |  |

|                                |      |      |      |      |      |      |  |  |  |  |

| RTIF                           |      |      |      |      |      |      |  |  |  |  |

| RTCMOD                         |      |      | 0x   | 55   |      |      |  |  |  |  |

Figure 13-6. RTC Counter Overflow Example

In the example of Figure 13-6, the selected clock source is the 1-kHz internal oscillator clock source. The prescaler (RTCPS) is set to 0xA or divide-by-4. The modulo value in the RTCMOD register is set to 0x55. When the counter, RTCCNT, reaches the modulo value of 0x55, the counter overflows to 0x00 and continues counting. The real-time interrupt flag, RTIF, sets when the counter value changes from 0x55 to 0x00. A real-time interrupt is generated when RTIF is set, if RTIE is set.

# 13.5 Initialization/Application Information

This section provides example code to give some basic direction to a user on how to initialize and configure the RTC module. The example software is implemented in C language.

The example below shows how to implement time of day with the RTC using the 1-kHz clock source to achieve the lowest possible power consumption. Because the 1-kHz clock source is not as accurate as a crystal, software can be added for any adjustments. For accuracy without adjustments at the expense of additional power consumption, the external clock (ERCLK) or the internal clock (IRCLK) can be selected with appropriate prescaler and modulo values.

MC9S08SG8 MCU Series Data Sheet, Rev. 8

Writing 0 to TE does not immediately release the pin to be a general-purpose I/O pin. Any transmit activity that is in progress must first be completed. This includes data characters in progress, queued idle characters, and queued break characters.

### 14.3.2.1 Send Break and Queued Idle

The SBK control bit in SCIC2 is used to send break characters which were originally used to gain the attention of old teletype receivers. Break characters are a full character time of logic 0 (10 bit times including the start and stop bits). A longer break of 13 bit times can be enabled by setting BRK13 = 1. Normally, a program would wait for TDRE to become set to indicate the last character of a message has moved to the transmit shifter, then write 1 and then write 0 to the SBK bit. This action queues a break character to be sent as soon as the shifter is available. If SBK is still 1 when the queued break moves into the shifter (synchronized to the baud rate clock), an additional break character is queued. If the receiving device is another Freescale Semiconductor SCI, the break characters will be received as 0s in all eight data bits and a framing error (FE = 1) occurs.

When idle-line wakeup is used, a full character time of idle (logic 1) is needed between messages to wake up any sleeping receivers. Normally, a program would wait for TDRE to become set to indicate the last character of a message has moved to the transmit shifter, then write 0 and then write 1 to the TE bit. This action queues an idle character to be sent as soon as the shifter is available. As long as the character in the shifter does not finish while TE = 0, the SCI transmitter never actually releases control of the TxD pin. If there is a possibility of the shifter finishing while TE = 0, set the general-purpose I/O controls so the pin that is shared with TxD is an output driving a logic 1. This ensures that the TxD line will look like a normal idle line even if the SCI loses control of the port pin between writing 0 and then 1 to TE.

The length of the break character is affected by the BRK13 and M bits as shown below.

| BRK13 | М | Break Character Length |

|-------|---|------------------------|

| 0     | 0 | 10 bit times           |

| 0     | 1 | 11 bit times           |

| 1     | 0 | 13 bit times           |

| 1     | 1 | 14 bit times           |

Table 14-8. Break Character Length

### 14.3.3 Receiver Functional Description

In this section, the receiver block diagram (Figure 14-3) is used as a guide for the overall receiver functional description. Next, the data sampling technique used to reconstruct receiver data is described in more detail. Finally, two variations of the receiver wakeup function are explained.

The receiver input is inverted by setting RXINV = 1. The receiver is enabled by setting the RE bit in SCIC2. Character frames consist of a start bit of logic 0, eight (or nine) data bits (LSB first), and a stop bit of logic 1. For information about 9-bit data mode, refer to Section 14.3.5.1, "8- and 9-Bit Data Modes." For the remainder of this discussion, we assume the SCI is configured for normal 8-bit data mode.

After receiving the stop bit into the receive shifter, and provided the receive data register is not already full, the data character is transferred to the receive data register and the receive data register full (RDRF)

#### Serial Peripheral Interface (S08SPIV3)

The most common uses of the SPI system include connecting simple shift registers for adding input or output ports or connecting small peripheral devices such as serial A/D or D/A converters. Although Figure 15-2 shows a system where data is exchanged between two MCUs, many practical systems involve simpler connections where data is unidirectionally transferred from the master MCU to a slave or from a slave to the master MCU.

#### 15.1.2.2 SPI Module Block Diagram

Figure 15-3 is a block diagram of the SPI module. The central element of the SPI is the SPI shift register. Data is written to the double-buffered transmitter (write to SPID) and gets transferred to the SPI shift register at the start of a data transfer. After shifting in a byte of data, the data is transferred into the double-buffered receiver where it can be read (read from SPID). Pin multiplexing logic controls connections between MCU pins and the SPI module.

When the SPI is configured as a master, the clock output is routed to the SPSCK pin, the shifter output is routed to MOSI, and the shifter input is routed from the MISO pin.

When the SPI is configured as a slave, the SPSCK pin is routed to the clock input of the SPI, the shifter output is routed to MISO, and the shifter input is routed from the MOSI pin.

In the external SPI system, simply connect all SPSCK pins to each other, all MISO pins together, and all MOSI pins together. Peripheral devices often use slightly different names for these pins.

# 15.3 Modes of Operation

## 15.3.1 SPI in Stop Modes

The SPI is disabled in all stop modes, regardless of the settings before executing the STOP instruction. During either stop1 or stop2 mode, the SPI module will be fully powered down. Upon wake-up from stop1 or stop2 mode, the SPI module will be in the reset state. During stop3 mode, clocks to the SPI module are halted. No registers are affected. If stop3 is exited with a reset, the SPI will be put into its reset state. If stop3 is exited with an interrupt, the SPI continues from the state it was in when stop3 was entered.

# 15.4 Register Definition

The SPI has five 8-bit registers to select SPI options, control baud rate, report SPI status, and for transmit/receive data.

Refer to the direct-page register summary in the Memory chapter of this data sheet for the absolute address assignments for all SPI registers. This section refers to registers and control bits only by their names, and a Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

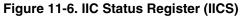

# 15.4.1 SPI Control Register 1 (SPIC1)

This read/write register includes the SPI enable control, interrupt enables, and configuration options.

Figure 15-5. SPI Control Register 1 (SPIC1)

| Field      | Description                                                                                                                                                                                                                                                                                                      |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SPIE  | <ul> <li>SPI Interrupt Enable (for SPRF and MODF) — This is the interrupt enable for SPI receive buffer full (SPRF) and mode fault (MODF) events.</li> <li>Interrupts from SPRF and MODF inhibited (use polling)</li> <li>When SPRF or MODF is 1, request a hardware interrupt</li> </ul>                        |

| 6<br>SPE   | <ul> <li>SPI System Enable — Disabling the SPI halts any transfer that is in progress, clears data buffers, and initializes internal state machines. SPRF is cleared and SPTEF is set to indicate the SPI transmit data buffer is empty.</li> <li>O SPI system inactive</li> <li>1 SPI system enabled</li> </ul> |

| 5<br>SPTIE | <ul> <li>SPI Transmit Interrupt Enable — This is the interrupt enable bit for SPI transmit buffer empty (SPTEF).</li> <li>Interrupts from SPTEF inhibited (use polling)</li> <li>When SPTEF is 1, hardware interrupt requested</li> </ul>                                                                        |

are used for PWM & output compare operation once normal execution resumes. Writes to the channel registers while BDM is active do not interfere with partial completion of a coherency sequence. After the coherency mechanism has been fully exercised, the channel registers are updated using the buffered values written (while BDM was not active) by the user.

## 16.4 Functional Description

All TPM functions are associated with a central 16-bit counter which allows flexible selection of the clock source and prescale factor. There is also a 16-bit modulo register associated with the main counter.

The CPWMS control bit chooses between center-aligned PWM operation for all channels in the TPM (CPWMS=1) or general purpose timing functions (CPWMS=0) where each channel can independently be configured to operate in input capture, output compare, or edge-aligned PWM mode. The CPWMS control bit is located in the main TPM status and control register because it affects all channels within the TPM and influences the way the main counter operates. (In CPWM mode, the counter changes to an up/down mode rather than the up-counting mode used for general purpose timer functions.)

The following sections describe the main counter and each of the timer operating modes (input capture, output compare, edge-aligned PWM, and center-aligned PWM). Because details of pin operation and interrupt activity depend upon the operating mode, these topics will be covered in the associated mode explanation sections.

## 16.4.1 Counter

All timer functions are based on the main 16-bit counter (TPMxCNTH:TPMxCNTL). This section discusses selection of the clock source, end-of-count overflow, up-counting vs. up/down counting, and manual counter reset.

#### 16.4.1.1 Counter Clock Source

The 2-bit field, CLKSB:CLKSA, in the timer status and control register (TPMxSC) selects one of three possible clock sources or OFF (which effectively disables the TPM). See Table 16-6. After any MCU reset, CLKSB:CLKSA=0:0 so no clock source is selected, and the TPM is in a very low power state. These control bits may be read or written at any time and disabling the timer (writing 00 to the CLKSB:CLKSA field) does not affect the values in the counter or other timer registers.

## 17.2.3 BDC Commands

BDC commands are sent serially from a host computer to the BKGD pin of the target HCS08 MCU. All commands and data are sent MSB-first using a custom BDC communications protocol. Active background mode commands require that the target MCU is currently in the active background mode while non-intrusive commands may be issued at any time whether the target MCU is in active background mode or running a user application program.

Table 17-1 shows all HCS08 BDC commands, a shorthand description of their coding structure, and the meaning of each command.

#### **Coding Structure Nomenclature**

This nomenclature is used in Table 17-1 to describe the coding structure of the BDC commands.

Commands begin with an 8-bit hexadecimal command code in the host-to-target direction (most significant bit first)

- / = separates parts of the command

- d = delay 16 target BDC clock cycles

- AAAA = a 16-bit address in the host-to-target direction

- RD = 8 bits of read data in the target-to-host direction

- WD = 8 bits of write data in the host-to-target direction

- RD16 = 16 bits of read data in the target-to-host direction

- WD16 = 16 bits of write data in the host-to-target direction

- SS = the contents of BDCSCR in the target-to-host direction (STATUS)

- CC = 8 bits of write data for BDCSCR in the host-to-target direction (CONTROL)

- RBKP = 16 bits of read data in the target-to-host direction (from BDCBKPT breakpoint register)

- WBKP = 16 bits of write data in the host-to-target direction (for BDCBKPT breakpoint register)

**Appendix A Electrical Characteristics**

|     |        |                                                |                                                   |                   |                                   |              |                  |              |                                                                                                                                                                                                                                                                                                                   | Temp Rated <sup>2</sup>                                                                     |                   |

|-----|--------|------------------------------------------------|---------------------------------------------------|-------------------|-----------------------------------|--------------|------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------|

| Num | С      | Chara                                          | oteristic                                         | Symbol            | Condition                         | Min          | Typ <sup>1</sup> | Мах          | Unit                                                                                                                                                                                                                                                                                                              | Stand<br>ard                                                                                | AEC<br>Grade<br>0 |

|     |        |                                                | /n <sup>3</sup> resistors; when                   |                   |                                   |              |                  |              |                                                                                                                                                                                                                                                                                                                   |                                                                                             |                   |

| 11  | Р      | enabled                                        | I/O pipe                                          |                   |                                   | 17           | 27               | 50           | ko                                                                                                                                                                                                                                                                                                                | v                                                                                           | v                 |

|     | г<br>С |                                                | -                                                 |                   |                                   |              |                  |              |                                                                                                                                                                                                                                                                                                                   |                                                                                             | x<br>x            |

|     |        | DC injection curre                             |                                                   | 110               |                                   |              | 07               | 52           | 1122                                                                                                                                                                                                                                                                                                              | ^                                                                                           | ^                 |

|     | D      |                                                | Single pin limit                                  |                   | $V_{IN} > V_{DD}$                 | 0            |                  | 2            | mA                                                                                                                                                                                                                                                                                                                | x                                                                                           | х                 |

|     |        |                                                | 0 1                                               | I <sub>IC</sub>   | V <sub>IN</sub> < V <sub>SS</sub> | 0            | —                | -0.2         | mA                                                                                                                                                                                                                                                                                                                | x                                                                                           | x                 |

| 12  |        |                                                | Total MCU limit,<br>includes                      |                   | $V_{IN} > V_{DD}$                 | 0            | —                | 25           | mA                                                                                                                                                                                                                                                                                                                | x                                                                                           | х                 |

|     |        |                                                | sum of all stressed pins                          |                   | $V_{IN} < V_{SS}$                 | 0            | _                | -5           | mA                                                                                                                                                                                                                                                                                                                | Stand<br>ard<br>x<br>x<br>x<br>x                                                            | x                 |

| 13  | D      | Input Capacitanc                               | e, all pins                                       | C <sub>In</sub>   |                                   | —            | —                | 8            | pF                                                                                                                                                                                                                                                                                                                | х                                                                                           | х                 |

| 14  | D      |                                                | -                                                 | V <sub>RAM</sub>  |                                   | —            | 0.6              | 1.0          |                                                                                                                                                                                                                                                                                                                   | х                                                                                           | х                 |

| 15  | D      |                                                | -                                                 |                   |                                   |              | 1.4              | 2.0          |                                                                                                                                                                                                                                                                                                                   |                                                                                             | х                 |

| 16  | D      | POR re-arm time                                | 10                                                | t <sub>POR</sub>  |                                   | 10           | —                |              | μS                                                                                                                                                                                                                                                                                                                | х                                                                                           | х                 |

| 17  | Ρ      | Low-voltage<br>detection<br>threshold —        | V <sub>DD</sub> falling                           | V <sub>LVD1</sub> |                                   | 3.9<br>3.88  | 4.0<br>4.0       | 4.1<br>4.12  |                                                                                                                                                                                                                                                                                                                   | x                                                                                           | x                 |

|     |        | high range                                     | V <sub>DD</sub> rising                            |                   |                                   | 4.0<br>3.98  | 4.1<br>4.1       | 4.2<br>4.22  |                                                                                                                                                                                                                                                                                                                   | Stand<br>ardxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx                                 | x                 |

|     |        | -                                              | ction threshold —                                 |                   |                                   |              |                  |              |                                                                                                                                                                                                                                                                                                                   | x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x<br>x |                   |

| 18  | Ρ      | low range <sup>11</sup> , <sup>12</sup>        | V <sub>DD</sub> falling<br>V <sub>DD</sub> rising | V <sub>LVD0</sub> |                                   | 2.48<br>2.54 | 2.56<br>2.62     | 2.64<br>2.70 | V                                                                                                                                                                                                                                                                                                                 |                                                                                             | x<br>x            |

| 19  | Р      | Low-voltage<br>warning<br>throspold            | V <sub>DD</sub> falling                           | V                 |                                   | 4.5<br>4.48  | 4.6<br>4.6       | 4.7<br>4.72  | ax       Unit         2 $k\Omega$ 2 $k\Omega$ 2 $mA$ 2 $mA$ 5 $mA$ 5 $mA$ 5 $mA$ 5 $mA$ 5 $mA$ 6 $V$ .0 $V$ .0 $V$ .0 $V$ .1 $V$ .2 $V$ .3 $V$ .4 $V$ .5 $V$ .4 $V$ .4 $V$ .5 $V$ .4 $V$ .5 $V$ .5 $V$ .63 $V$ .7 $V$ .7 $V$ .7 $V$ <td>x</td> <td>x</td> | x                                                                                           | x                 |

|     |        | high range 1                                   | V <sub>DD</sub> rising                            | VLVW3             |                                   | 4.6<br>4.58  | 4.7<br>4.7       | 4.8<br>4.82  | V                                                                                                                                                                                                                                                                                                                 | x                                                                                           | x                 |

| 20  | Р      | Low-voltage<br>warning<br>threshold            | $ \frac{1}{10000000000000000000000000000000000$   |                   | x                                 | x            |                  |              |                                                                                                                                                                                                                                                                                                                   |                                                                                             |                   |

|     |        | high range 0                                   | V <sub>DD</sub> rising                            | VLVW2             |                                   |              |                  |              | V                                                                                                                                                                                                                                                                                                                 | x                                                                                           | x                 |

| 21  | Ρ      | Low-voltage warr<br>low range 1                | V <sub>DD</sub> falling                           | V <sub>LVW1</sub> |                                   |              |                  |              | v                                                                                                                                                                                                                                                                                                                 |                                                                                             | x<br>x            |

| 22  | Р      | Low-voltage warning threshold —<br>low range 0 |                                                   | Vinavo            |                                   |              |                  |              |                                                                                                                                                                                                                                                                                                                   |                                                                                             | x                 |

|     |        |                                                |                                                   | * LVW0            |                                   |              |                  |              | V                                                                                                                                                                                                                                                                                                                 |                                                                                             | x                 |

#### Table A-6. DC Characteristics (continued)

Appendix A Electrical Characteristics

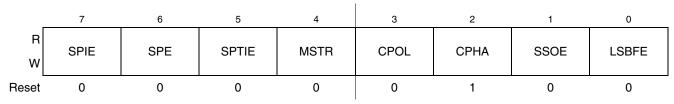

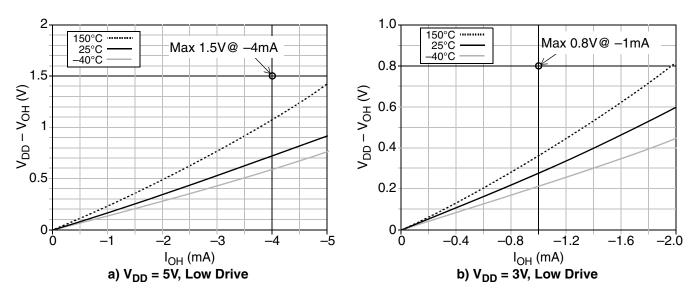

Figure A-3. Typical  $V_{DD} - V_{OH}$  vs I<sub>OH</sub>, High Drive Strength

Figure A-4. Typical  $V_{DD} - V_{OH}$  vs I<sub>OH</sub>, Low Drive Strength

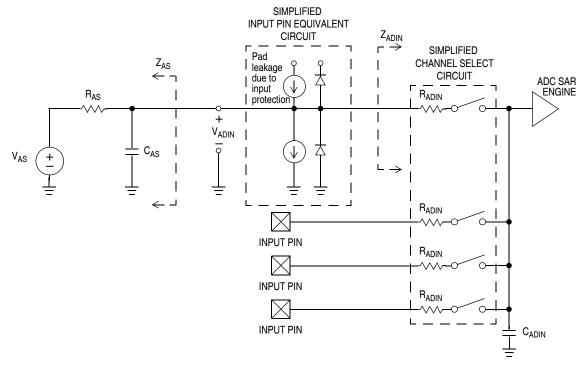

Figure A-9. ADC Input Impedance Equivalency Diagram

|                                     | Conditions                    | c | Symb                                   | Min  | Typ <sup>1</sup> | Max | Unit | Temp Rated <sup>2</sup> |                   |                        |  |

|-------------------------------------|-------------------------------|---|----------------------------------------|------|------------------|-----|------|-------------------------|-------------------|------------------------|--|

| Characteristic                      |                               |   |                                        |      |                  |     |      | Stand<br>ard            | AEC<br>Grade<br>0 | Comment                |  |

| Supply current                      | ADLPC=1<br>ADLSMP=1<br>ADCO=1 | т | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 133              | _   | μA   | x                       | x                 | ADC<br>current<br>only |  |

| Supply current                      | ADLPC=1<br>ADLSMP=0<br>ADCO=1 | т | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 218              | _   | μA   | x                       | x                 | ADC<br>current<br>only |  |

| Supply current                      | ADLPC=0<br>ADLSMP=1<br>ADCO=1 | т | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 327              | _   | μA   | x                       | х                 | ADC<br>current<br>only |  |

| Supply current                      | ADLPC=0<br>ADLSMP=0<br>ADCO=1 | Р | I <sub>DD</sub> +<br>I <sub>DDAD</sub> | _    | 0.582            | 1   | mA   | x                       | x                 | ADC<br>current<br>only |  |

| ADC<br>asynchronous<br>clock source | High speed<br>(ADLPC=0)       | P | fadack                                 | 2    | 3.3              | 5   | MHz  | x                       | x                 | t <sub>ADACK</sub> =   |  |

|                                     | Low power<br>(ADLPC=1)        |   |                                        | 1.25 | 2                | 3.3 |      | х                       | х                 | 1/f <sub>ADACK</sub>   |  |

**Table A-12. ADC Characteristics**