### NXP USA Inc. - S9S08SG8E2WTG Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | S08                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 40MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 12                                                                    |

| Program Memory Size        | 8KB (8K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 512 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 8x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                       |

| Supplier Device Package    | 16-TSSOP                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08sg8e2wtg |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MC9S08SG8 Data Sheet

Covers MC9S08SG8 MC9S08SG4

> MC9S08SG8 Rev. 8 1/2014

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

© Freescale Semiconductor, Inc., 2006-2014. All rights reserved.

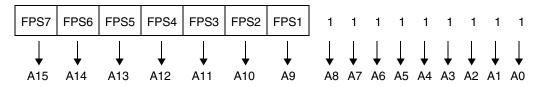

must be programmed to logic 0 to enable block protection. Therefore the value 0xF8 must be programmed into NVPROT to protect addresses 0xFA00 through 0xFFFF.

### Figure 4-4. Block Protection Mechanism

One use for block protection is to block protect an area of FLASH memory for a bootloader program. This bootloader program then can be used to erase the rest of the FLASH memory and reprogram it. Because the bootloader is protected, it remains intact even if MCU power is lost in the middle of an erase and reprogram operation.

# 4.5.7 Vector Redirection

Whenever any block protection is enabled, the reset and interrupt vectors will be protected. Vector redirection allows users to modify interrupt vector information without unprotecting bootloader and reset vector space. Vector redirection is enabled by programming the FNORED bit in the NVOPT register located at address 0xFFBF to zero. For redirection to occur, at least some portion but not all of the FLASH memory must be block protected by programming the NVPROT register located at address 0xFFBD. All of the interrupt vectors (memory locations 0xFFC0–0xFFFD) are redirected, though the reset vector (0xFFFE:FFFF) is not.

For example, if 512 bytes of FLASH are protected, the protected address region is from 0xFE00 through 0xFFFF. The interrupt vectors (0xFFC0–0xFFFD) are redirected to the locations 0xFDC0–0xFDFD. Now, if an SPI interrupt is taken for instance, the values in the locations 0xFDE0:FDE1 are used for the vector instead of the values in the locations 0xFFE0:FFE1. This allows the user to reprogram the unprotected portion of the FLASH with new program code including new interrupt vector values while leaving the protected area, which includes the default vector locations, unchanged.

# 4.6 Security

The MC9S08SG8 includes circuitry to prevent unauthorized access to the contents of FLASH and RAM memory. When security is engaged, FLASH and RAM are considered secure resources. Direct-page registers, high-page registers, and the background debug controller are considered unsecured resources. Programs executing within secure memory have normal access to any MCU memory locations and resources. Attempts to access a secure memory location with a program executing from an unsecured memory space or through the background debug interface are blocked (writes are ignored and reads return all 0s).

Security is engaged or disengaged based on the state of two nonvolatile register bits (SEC01:SEC00) in the FOPT register. During reset, the contents of the nonvolatile location NVOPT are copied from FLASH into the working FOPT register in high-page register space. A user engages security by programming the NVOPT location which can be done at the same time the FLASH memory is programmed. The 1:0 state disengages security and the other three combinations engage security. Notice the erased state (1:1) makes

the MCU secure. During development, whenever the FLASH is erased, it is good practice to immediately program the SEC00 bit to 0 in NVOPT so SEC01:SEC00 = 1:0. This would allow the MCU to remain unsecured after a subsequent reset.

The on-chip debug module cannot be enabled while the MCU is secure. The separate background debug controller can still be used for background memory access commands of unsecured resources.

A user can choose to allow or disallow a security unlocking mechanism through an 8-byte backdoor security key. If the nonvolatile KEYEN bit in NVOPT/FOPT is 0, the backdoor key is disabled and there is no way to disengage security without completely erasing all FLASH locations. If KEYEN is 1, a secure user program can temporarily disengage security by:

- 1. Writing 1 to KEYACC in the FCNFG register. This makes the FLASH module interpret writes to the backdoor comparison key locations (NVBACKKEY through NVBACKKEY+7) as values to be compared against the key rather than as the first step in a FLASH program or erase command.

- 2. Writing the user-entered key values to the NVBACKKEY through NVBACKKEY+7 locations. These writes must be done in order starting with the value for NVBACKKEY and ending with NVBACKKEY+7. STHX should not be used for these writes because these writes cannot be done on adjacent bus cycles. User software normally would get the key codes from outside the MCU system through a communication interface such as a serial I/O.

- 3. Writing 0 to KEYACC in the FCNFG register. If the 8-byte key that was just written matches the key stored in the FLASH locations, SEC01:SEC00 are automatically changed to 1:0 and security will be disengaged until the next reset.

The security key can be written only from secure memory (either RAM or FLASH), so it cannot be entered through background commands without the cooperation of a secure user program.

The backdoor comparison key (NVBACKKEY through NVBACKKEY+7) is located in FLASH memory locations in the nonvolatile register space so users can program these locations exactly as they would program any other FLASH memory location. The nonvolatile registers are in the same 512-byte block of FLASH as the reset and interrupt vectors, so block protecting that space also block protects the backdoor comparison key. Block protects cannot be changed from user application programs, so if the vector space is block protected, the backdoor security key mechanism cannot permanently change the block protect, security settings, or the backdoor key.

Security can always be disengaged through the background debug interface by taking these steps:

- 1. Disable any block protections by writing FPROT. FPROT can be written only with background debug commands, not from application software.

- 2. Mass erase FLASH if necessary.

- 3. Blank check FLASH. Provided FLASH is completely erased, security is disengaged until the next reset.

To avoid returning to secure mode after the next reset, program NVOPT so SEC01:SEC00 = 1:0.

# 4.7 FLASH Registers and Control Bits

The FLASH module has nine 8-bit registers in the high-page register space, two locations (NVOPT, NVPROT) in the nonvolatile register space in FLASH memory are copied into corresponding high-page

| f <sub>Bus</sub> | PRDIV8<br>(Binary) | DIV<br>(Decimal) | f <sub>FCLK</sub> Program/Erase Timing Pu<br>(5 μs Min, 6.7 μs Max) |        |  |

|------------------|--------------------|------------------|---------------------------------------------------------------------|--------|--|

| 20 MHz           | 1                  | 12               | 192.3 kHz 5.2 μs                                                    |        |  |

| 10 MHz           | 0                  | 49               | 200 kHz                                                             | 5 μs   |  |

| 8 MHz            | 0                  | 39               | 200 kHz                                                             | 5 μs   |  |

| 4 MHz            | 0                  | 19               | 200 kHz                                                             | 5 μs   |  |

| 2 MHz            | 0                  | 9                | 200 kHz                                                             | 5 μs   |  |

| 1 MHz            | 0                  | 4                | 200 kHz                                                             | 5 μs   |  |

| 200 kHz          | 0                  | 0                | 200 kHz                                                             | 5 μs   |  |

| 150 kHz          | 0                  | 0                | 150 kHz                                                             | 6.7 μs |  |

#### Table 4-7. FLASH Clock Divider Settings

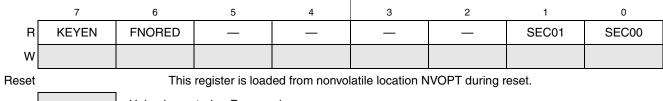

# 4.7.2 FLASH Options Register (FOPT and NVOPT)

During reset, the contents of the nonvolatile location NVOPT are copied from FLASH into FOPT. To change the value in this register, erase and reprogram the NVOPT location in FLASH memory as usual and then issue a new MCU reset.

= Unimplemented or Reserved

#### Figure 4-6. FLASH Options Register (FOPT)

#### Table 4-8. FOPT Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>KEYEN       | <ul> <li>Backdoor Key Mechanism Enable — When this bit is 0, the backdoor key mechanism cannot be used to disengage security. The backdoor key mechanism is accessible only from user (secured) firmware. BDM commands cannot be used to write key comparison values that would unlock the backdoor key. For more detailed information about the backdoor key mechanism, refer to Section 4.6, "Security."</li> <li>0 No backdoor key access allowed.</li> <li>1 If user firmware writes an 8-byte value that matches the nonvolatile backdoor key (NVBACKKEY through NVBACKKEY+7 in that order), security is temporarily disengaged until the next MCU reset.</li> </ul> |

| 6<br>FNORED      | <ul> <li>Vector Redirection Disable — When this bit is 1, then vector redirection is disabled.</li> <li>0 Vector redirection enabled.</li> <li>1 Vector redirection disabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1:0<br>SEC0[1:0] | Security State Code — This 2-bit field determines the security state of the MCU as shown in Table 4-9. When the MCU is secure, the contents of RAM and FLASH memory cannot be accessed by instructions from any unsecured source including the background debug interface. SEC01:SEC00 changes to 1:0 after successful backdoor key entry or a successful blank check of FLASH. For more detailed information about security, refer to Section 4.6, "Security."                                                                                                                                                                                                           |

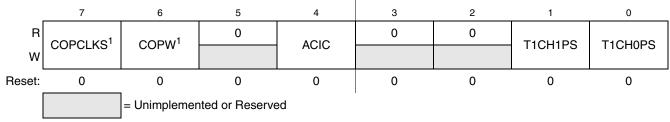

# 5.7.4 System Options Register 2 (SOPT2)

This high page register contains bits to configure MCU specific features on the MC9S08SG8 devices.

### Figure 5-5. System Options Register 2 (SOPT2)

<sup>1</sup> This bit can be written only one time after reset. Additional writes are ignored.

### Table 5-6. SOPT2 Register Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7<br>COPCLKS | <ul> <li>COP Watchdog Clock Select — This write-once bit selects the clock source of the COP watchdog.</li> <li>Internal 1-kHz clock is source to COP.</li> <li>Bus clock is source to COP.</li> </ul>                                                                                                                                                                                 |  |  |

| 6<br>COPW    | <ul> <li>COP Window — This write-once bit selects the COP operation mode. When set, the 0x55-0xAA write sequence to the SRS register must occur in the last 25% of the selected period. Any write to the SRS register during the first 75% of the selected period will reset the MCU.</li> <li>0 Normal COP operation</li> <li>1 Window COP operation (only if COPCLKS = 1)</li> </ul> |  |  |

| 4<br>ACIC    | <ul> <li>Analog Comparator to Input Capture Enable— This bit connects the output of ACMP to TPM1 input channel 0.</li> <li>0 ACMP output not connected to TPM1 input channel 0.</li> <li>1 ACMP output connected to TPM1 input channel 0.</li> </ul>                                                                                                                                   |  |  |

| 1<br>T1CH1PS | <ul> <li>TPM1CH1 Pin Select— This bit selects the location of the TPM1CH1 pin of the TPM1 module.</li> <li>TPM1CH1 on PTB5.</li> <li>TPM1CH1 on PTC1.</li> </ul>                                                                                                                                                                                                                       |  |  |

| 0<br>T1CH0PS | <ul> <li>TPM1CH0 Pin Select— This bit selects the location of the TPM1CH0 pin of the TPM1 module.</li> <li>0 TPM1CH0 on PTA0.</li> <li>1 TPM1CH0 on PTC0.</li> </ul>                                                                                                                                                                                                                   |  |  |

# 6.3 Ganged Output

The MC9S08SG8 devices contain a feature that allows for up to eight port pins to be tied together externally to allow higher output current drive. The ganged output drive control register (GNGC) is a write-once register that is used to enabled the ganged output feature and select which port pins will be used as ganged outputs. The GNGEN bit in GNGC enables ganged output. The GNGPS[7:1] bits are used to select which pin will be part of the ganged output.

When GNGEN is set, any pin that is enabled as a ganged output will be automatically configured as an output and follow the data, drive strength and slew rate control of PTC0. The ganged output drive pin mapping is shown in Table 6-1.

### NOTE

See the DC characteristics in the electrical section for maximum Port I/O currents allowed for this MCU.

When a pin is enabled as ganged output, this feature will have priority over any digital module. An enabled analog function will have priority over the ganged output pin. See Table 2-1 for information on pin priority.

|                           | GNGC Register Bits                                |                                                                                 |          |             |                 |             |        |                    |

|---------------------------|---------------------------------------------------|---------------------------------------------------------------------------------|----------|-------------|-----------------|-------------|--------|--------------------|

|                           | GNGPS7                                            | GNGPS6                                                                          | GNGPS5   | GNGPS4      | GNGPS3          | GNGPS2      | GNGPS1 | GNGEN <sup>1</sup> |

| Port Pin <sup>2</sup>     | PTB5                                              | PTB4                                                                            | PTB3     | PTB2        | PTC3            | PTC2        | PTC1   | PTC0               |

| Data Direction<br>Control |                                                   | Pin is automatically configured as output when pin is enabled as ganged output. |          |             |                 |             |        |                    |

| Data<br>Control           | PTCD0 in PTCD controls data value of output       |                                                                                 |          |             |                 |             |        |                    |

| Drive Strength<br>Control | PTCDS0 in PTCDS controls drive strength of output |                                                                                 |          |             |                 |             |        |                    |

| Slew Rate<br>Control      |                                                   |                                                                                 | PTCSE0 i | n PTCSE con | trols slew rate | e of output |        |                    |

Table 6-1. Ganged Output Pin Enable

<sup>1</sup> Ganged output not available on 8-pin packages. PTC3-PTC0 not available on 16-pin packages, however PTC0 control registers are still used to control ganged output.

<sup>2</sup> When GNGEN = 1, PTC0 is forced to an output, regardless of the value in PTCDD0 in PTCDD.

Chapter 6 Parallel Input/Output Control

# 6.6.1 Port A Registers

Port A is controlled by the registers listed below.

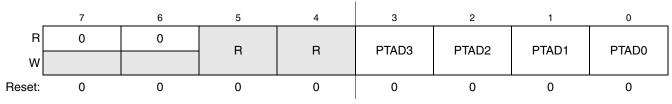

# 6.6.1.1 Port A Data Register (PTAD)

### Figure 6-3. Port A Data Register (PTAD)

#### Table 6-2. PTAD Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5:4<br>Reserved  | <b>Reserved Bits</b> — These bits are unused on this MCU, writes have no affect and could read as 1s or 0s.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3:0<br>PTAD[3:0] | Port A Data Register Bits — For port A pins that are inputs, reads return the logic level on the pin. For port A pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port A pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTAD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pull-ups/pull-downs disabled. |

# 6.6.1.2 Port A Data Direction Register (PTADD)

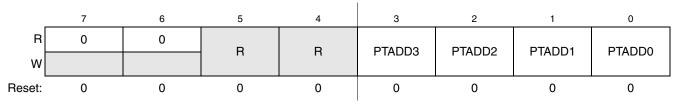

### Figure 6-4. Port A Data Direction Register (PTADD)

#### Table 6-3. PTADD Register Field Descriptions

| Field             | Description                                                                                                                                                                                                                                                                                                           |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5:4<br>Reserved   | <b>Reserved Bits</b> — These bits are unused on this MCU, writes have no affect and could read as 1s or 0s.                                                                                                                                                                                                           |

| 3:0<br>PTADD[3:0] | <ul> <li>Data Direction for Port A Bits — These read/write bits control the direction of port A pins and what is read for PTAD reads.</li> <li>Input (output driver disabled) and reads return the pin value.</li> <li>Output driver enabled for port A bit n and PTAD reads return the contents of PTADn.</li> </ul> |

#### MC9S08SG8 MCU Series Data Sheet, Rev. 8

Chapter 7 Central Processor Unit (S08CPUV2)

# 7.2 Programmer's Model and CPU Registers

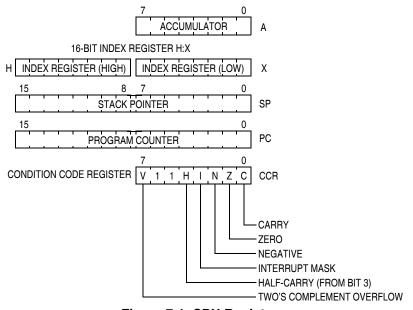

Figure 7-1 shows the five CPU registers. CPU registers are not part of the memory map.

Figure 7-1. CPU Registers

# 7.2.1 Accumulator (A)

The A accumulator is a general-purpose 8-bit register. One operand input to the arithmetic logic unit (ALU) is connected to the accumulator and the ALU results are often stored into the A accumulator after arithmetic and logical operations. The accumulator can be loaded from memory using various addressing modes to specify the address where the loaded data comes from, or the contents of A can be stored to memory using various addressing modes to specify the address where the specify the address where data from A will be stored.

Reset has no effect on the contents of the A accumulator.

# 7.2.2 Index Register (H:X)

This 16-bit register is actually two separate 8-bit registers (H and X), which often work together as a 16-bit address pointer where H holds the upper byte of an address and X holds the lower byte of the address. All indexed addressing mode instructions use the full 16-bit value in H:X as an index reference pointer; however, for compatibility with the earlier M68HC05 Family, some instructions operate only on the low-order 8-bit half (X).

Many instructions treat X as a second general-purpose 8-bit register that can be used to hold 8-bit data values. X can be cleared, incremented, decremented, complemented, negated, shifted, or rotated. Transfer instructions allow data to be transferred from A or transferred to A where arithmetic and logical operations can then be performed.

For compatibility with the earlier M68HC05 Family, H is forced to 0x00 during reset. Reset has no effect on the contents of X.

| ADCH  | Input Select |

|-------|--------------|

| 01000 | AD8          |

| 01001 | AD9          |

| 01010 | AD10         |

| 01011 | AD11         |

| 01100 | AD12         |

| 01101 | AD13         |

| 01110 | AD14         |

| 01111 | AD15         |

| ADCH  | Input Select      |

|-------|-------------------|

| 11000 | AD24              |

| 11001 | AD25              |

| 11010 | AD26              |

| 11011 | AD27              |

| 11100 | Reserved          |

| 11101 | V <sub>REFH</sub> |

| 11110 | V <sub>REFL</sub> |

| 11111 | Module disabled   |

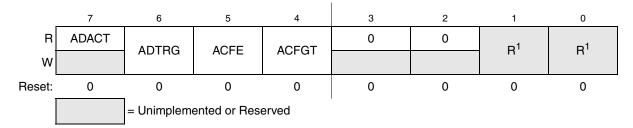

# 9.3.2 Status and Control Register 2 (ADCSC2)

The ADCSC2 register is used to control the compare function, conversion trigger and conversion active of the ADC module.

<sup>1</sup> Bits 1 and 0 are reserved bits that must always be written to 0.

### Figure 9-5. Status and Control Register 2 (ADCSC2)

#### Table 9-4. ADCSC2 Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADACT | <ul> <li>Conversion Active — ADACT indicates that a conversion is in progress. ADACT is set when a conversion is initiated and cleared when a conversion is completed or aborted.</li> <li>Conversion not in progress</li> <li>Conversion in progress</li> </ul>                                                                                                                                                                                                                                  |

| 6<br>ADTRG | <ul> <li>Conversion Trigger Select — ADTRG is used to select the type of trigger to be used for initiating a conversion.</li> <li>Two types of trigger are selectable: software trigger and hardware trigger. When software trigger is selected, a conversion is initiated following a write to ADCSC1. When hardware trigger is selected, a conversion is initiated following the assertion of the ADHWT input.</li> <li>Software trigger selected</li> <li>Hardware trigger selected</li> </ul> |

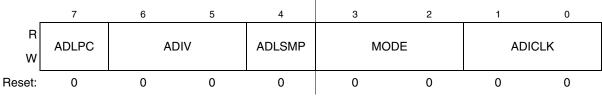

Figure 9-10. Configuration Register (ADCCFG)

### Table 9-5. ADCCFG Register Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADLPC    | <ul> <li>Low Power Configuration — ADLPC controls the speed and power configuration of the successive approximation converter. This is used to optimize power consumption when higher sample rates are not required.</li> <li>0 High speed configuration</li> <li>1 Low power configuration: {FC31}The power is reduced at the expense of maximum clock speed.</li> </ul>                                                                                                    |

| 6:5<br>ADIV   | <b>Clock Divide Select</b> — ADIV select the divide ratio used by the ADC to generate the internal clock ADCK.<br>Table 9-6 shows the available clock configurations.                                                                                                                                                                                                                                                                                                        |

| 4<br>ADLSMP   | <ul> <li>Long Sample Time Configuration — ADLSMP selects between long and short sample time. This adjusts the sample period to allow higher impedance inputs to be accurately sampled or to maximize conversion speed for lower impedance inputs. Longer sample times can also be used to lower overall power consumption when continuous conversions are enabled if high conversion rates are not required.</li> <li>Short sample time</li> <li>Long sample time</li> </ul> |

| 3:2<br>MODE   | <b>Conversion Mode Selection</b> — MODE bits are used to select between 10- or 8-bit operation. See Table 9-7.                                                                                                                                                                                                                                                                                                                                                               |

| 1:0<br>ADICLK | Input Clock Select — ADICLK bits select the input clock source to generate the internal clock ADCK. See Table 9-8.                                                                                                                                                                                                                                                                                                                                                           |

#### Table 9-6. Clock Divide Select

| ADIV | Divide Ratio | Clock Rate      |

|------|--------------|-----------------|

| 00   | 1            | Input clock     |

| 01   | 2            | Input clock ÷ 2 |

| 10   | 4            | Input clock ÷ 4 |

| 11   | 8            | Input clock ÷ 8 |

### Table 9-7. Conversion Modes

| MODE | Mode Description         |  |

|------|--------------------------|--|

| 00   | 8-bit conversion (N=8)   |  |

| 01   | Reserved                 |  |

| 10   | 10-bit conversion (N=10) |  |

| 11   | Reserved                 |  |

| Field      | Description                                                                                                                                                                          |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1<br>ADPC9 | <ul> <li>ADC Pin Control 9 — ADPC9 is used to control the pin associated with channel AD9.</li> <li>0 AD9 pin I/O control enabled</li> <li>1 AD9 pin I/O control disabled</li> </ul> |  |  |

| 0<br>ADPC8 | <ul> <li>ADC Pin Control 8 — ADPC8 is used to control the pin associated with channel AD8.</li> <li>0 AD8 pin I/O control enabled</li> <li>1 AD8 pin I/O control disabled</li> </ul> |  |  |

#### Table 9-10. APCTL2 Register Field Descriptions (continued)

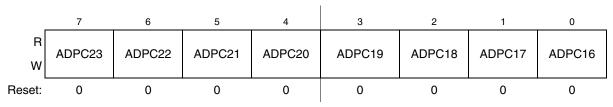

# 9.3.10 Pin Control 3 Register (APCTL3)

APCTL3 is used to control channels 16–23 of the ADC module.

Figure 9-13. Pin Control 3 Register (APCTL3)

### Table 9-11. APCTL3 Register Field Descriptions

| Field       | Description                                                                                                                                                                               |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7<br>ADPC23 | <ul> <li>ADC Pin Control 23 — ADPC23 is used to control the pin associated with channel AD23.</li> <li>0 AD23 pin I/O control enabled</li> <li>1 AD23 pin I/O control disabled</li> </ul> |  |  |

| 6<br>ADPC22 | <ul> <li>ADC Pin Control 22 — ADPC22 is used to control the pin associated with channel AD22.</li> <li>0 AD22 pin I/O control enabled</li> <li>1 AD22 pin I/O control disabled</li> </ul> |  |  |

| 5<br>ADPC21 | <ul> <li>ADC Pin Control 21 — ADPC21 is used to control the pin associated with channel AD21.</li> <li>0 AD21 pin I/O control enabled</li> <li>1 AD21 pin I/O control disabled</li> </ul> |  |  |

| 4<br>ADPC20 | <ul> <li>ADC Pin Control 20 — ADPC20 is used to control the pin associated with channel AD20.</li> <li>0 AD20 pin I/O control enabled</li> <li>1 AD20 pin I/O control disabled</li> </ul> |  |  |

| 3<br>ADPC19 | <ul> <li>ADC Pin Control 19 — ADPC19 is used to control the pin associated with channel AD19.</li> <li>0 AD19 pin I/O control enabled</li> <li>1 AD19 pin I/O control disabled</li> </ul> |  |  |

| 2<br>ADPC18 | ADC Pin Control 18 — ADPC18 is used to control the pin associated with channel AD18.         0 AD18 pin I/O control enabled         1 AD18 pin I/O control disabled                       |  |  |

#### Analog-to-Digital Converter (S08ADCV1)

In cases where separate power supplies are used for analog and digital power, the ground connection between these supplies must be at the  $V_{SSAD}$  pin. This should be the only ground connection between these supplies if possible. The  $V_{SSAD}$  pin makes a good single point ground location.

# 9.6.1.2 Analog Reference Pins

In addition to the analog supplies, the ADC module has connections for two reference voltage inputs. The high reference is  $V_{REFH}$ , which may be shared on the same pin as  $V_{DDAD}$  on some devices. The low reference is  $V_{REFL}$ , which may be shared on the same pin as  $V_{SSAD}$  on some devices.

When available on a separate pin,  $V_{REFH}$  may be connected to the same potential as  $V_{DDAD}$ , or may be driven by an external source that is between the minimum  $V_{DDAD}$  spec and the  $V_{DDAD}$  potential ( $V_{REFH}$  must never exceed  $V_{DDAD}$ ). When available on a separate pin,  $V_{REFL}$  must be connected to the same voltage potential as  $V_{SSAD}$ . Both  $V_{REFH}$  and  $V_{REFL}$  must be routed carefully for maximum noise immunity and bypass capacitors placed as near as possible to the package.

AC current in the form of current spikes required to supply charge to the capacitor array at each successive approximation step is drawn through the  $V_{REFH}$  and  $V_{REFL}$  loop. The best external component to meet this current demand is a 0.1  $\mu$ F capacitor with good high frequency characteristics. This capacitor is connected between  $V_{REFH}$  and  $V_{REFL}$  and must be placed as near as possible to the package pins. Resistance in the path is not recommended because the current will cause a voltage drop which could result in conversion errors. Inductance in this path must be minimum (parasitic only).

# 9.6.1.3 Analog Input Pins

The external analog inputs are typically shared with digital I/O pins on MCU devices. The pin I/O control is disabled by setting the appropriate control bit in one of the pin control registers. Conversions can be performed on inputs without the associated pin control register bit set. It is recommended that the pin control register bit always be set when using a pin as an analog input. This avoids problems with contention because the output buffer will be in its high impedance state and the pullup is disabled. Also, the input buffer draws dc current when its input is not at either  $V_{DD}$  or  $V_{SS}$ . Setting the pin control register bits for all pins used as analog inputs should be done to achieve lowest operating current.

Empirical data shows that capacitors on the analog inputs improve performance in the presence of noise or when the source impedance is high. Use of 0.01  $\mu$ F capacitors with good high-frequency characteristics is sufficient. These capacitors are not necessary in all cases, but when used they must be placed as near as possible to the package pins and be referenced to V<sub>SSA</sub>.

For proper conversion, the input voltage must fall between  $V_{REFH}$  and  $V_{REFL}$ . If the input is equal to or exceeds  $V_{REFH}$ , the converter circuit converts the signal to \$3FF (full scale 10-bit representation) or \$FF (full scale 8-bit representation). If the input is equal to or less than  $V_{REFL}$ , the converter circuit converts it to \$000. Input voltages between  $V_{REFH}$  and  $V_{REFL}$  are straight-line linear conversions. There will be a brief current associated with  $V_{REFL}$  when the sampling capacitor is charging. The input is sampled for 3.5 cycles of the ADCK source when ADLSMP is low, or 23.5 cycles when ADLSMP is high.

For minimal loss of accuracy due to current injection, pins adjacent to the analog input pins should not be transitioning during conversions.

#### Internal Clock Source (S08ICSV2)

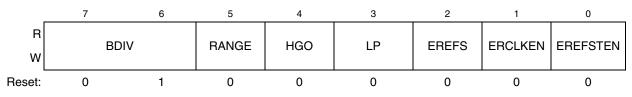

# 10.3.2 ICS Control Register 2 (ICSC2)

Figure 10-4. ICS Control Register 2 (ICSC2)

| Table 10-3. ICS Control Register 2 | Field Descriptions |

|------------------------------------|--------------------|

|------------------------------------|--------------------|

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7:6<br>BDIV   | Bus Frequency Divider — Selects the amount to divide down the clock source selected by the CLKS bits. This controls the bus frequency.         00       Encoding 0 — Divides selected clock by 1         01       Encoding 1 — Divides selected clock by 2 (reset default)         10       Encoding 2 — Divides selected clock by 4         11       Encoding 3 — Divides selected clock by 8 |  |  |

| 5<br>RANGE    | <ul> <li>Frequency Range Select — Selects the frequency range for the external oscillator.</li> <li>1 High frequency range selected for the external oscillator</li> <li>0 Low frequency range selected for the external oscillator</li> </ul>                                                                                                                                                 |  |  |

| 4<br>HGO      | <ul> <li>High Gain Oscillator Select — The HGO bit controls the external oscillator mode of operation.</li> <li>1 Configure external oscillator for high gain operation</li> <li>0 Configure external oscillator for low power operation</li> </ul>                                                                                                                                            |  |  |

| 3<br>LP       | <ul> <li>Low Power Select — The LP bit controls whether the FLL is disabled in FLL bypassed modes.</li> <li>1 FLL is disabled in bypass modes unless BDM is active</li> <li>0 FLL is not disabled in bypass mode</li> </ul>                                                                                                                                                                    |  |  |

| 2<br>EREFS    | <ul> <li>External Reference Select — The EREFS bit selects the source for the external reference clock.</li> <li>1 Oscillator requested</li> <li>0 External Clock Source requested</li> </ul>                                                                                                                                                                                                  |  |  |

| 1<br>ERCLKEN  | External Reference Enable — The ERCLKEN bit enables the external reference clock for use as ICSERCLK.<br>1 ICSERCLK active<br>0 ICSERCLK inactive                                                                                                                                                                                                                                              |  |  |

| 0<br>EREFSTEN |                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Field | Description                                                                                                                                                                                                                                                                                                                      |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1     | <b>OSC Initialization</b> — If the external reference clock is selected by ERCLKEN or by the ICS being in FEE, FBE, or FBELP mode, and if EREFS is set, then this bit is set after the initialization cycles of the external oscillator clock have completed. This bit is only cleared when either ERCLKEN or EREFS are cleared. |  |  |

| 0     | <b>ICS Fine Trim</b> — The FTRIM bit controls the smallest adjustment of the internal reference clock frequency. Setting FTRIM will increase the period and clearing FTRIM will decrease the period by the smallest amount possible.                                                                                             |  |  |

Table 10-5. ICS Status and Control Register Field Descriptions (continued)

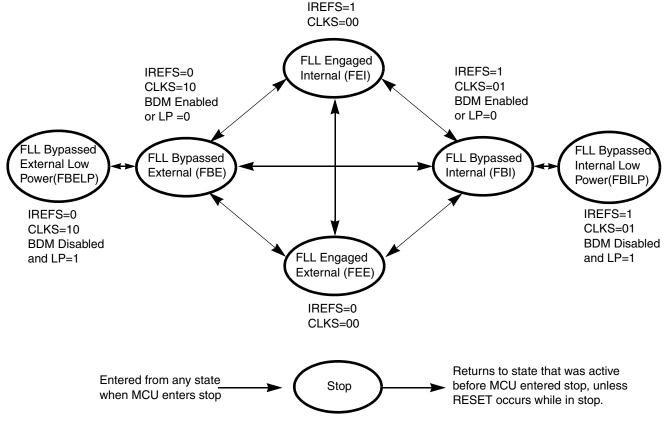

# 10.4 Functional Description

# 10.4.1 Operational Modes

Figure 10-7. Clock Switching Modes

The seven states of the ICS are shown as a state diagram and are described below. The arrows indicate the allowed movements between the states.

# 10.4.1.1 FLL Engaged Internal (FEI)

FLL engaged internal (FEI) is the default mode of operation and is entered when all the following conditions occur:

# 11.7 Initialization/Application Information

| Module Initialization (Slave)            |                                                                                |                                                                    |  |  |  |

|------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|

| 1.                                       | Write: 1                                                                       |                                                                    |  |  |  |

|                                          | — to e                                                                         | nable or disable general call                                      |  |  |  |

|                                          | — to s                                                                         | elect 10-bit or 7-bit addressing mode                              |  |  |  |

| 2.                                       | Write: 1                                                                       | IICA                                                               |  |  |  |

|                                          | - to s                                                                         | set the slave address                                              |  |  |  |

| 3.                                       | Write: I                                                                       | IICC1                                                              |  |  |  |

|                                          | — to e                                                                         | enable IIC and interrupts                                          |  |  |  |

| 4.                                       | Initializ                                                                      | ze RAM variables (IICEN = 1 and IICIE = 1) for transmit data       |  |  |  |

| 5.                                       | Initializ                                                                      | ze RAM variables used to achieve the routine shown in Figure 11-12 |  |  |  |

|                                          |                                                                                |                                                                    |  |  |  |

|                                          |                                                                                | Module Initialization (Master)                                     |  |  |  |

| 1.                                       | Write: 1                                                                       | IICF                                                               |  |  |  |

|                                          | - to s                                                                         | set the IIC baud rate (example provided in this chapter)           |  |  |  |

| 2.                                       | Write: I                                                                       | IICC1                                                              |  |  |  |

|                                          | — to e                                                                         | enable IIC and interrupts                                          |  |  |  |

| 3.                                       | Initializ                                                                      | ze RAM variables (IICEN = 1 and IICIE = 1) for transmit data $($   |  |  |  |

| 4.                                       | Initializ                                                                      | ze RAM variables used to achieve the routine shown in Figure 11-12 |  |  |  |

| 5.                                       | Write: I                                                                       | IICC1                                                              |  |  |  |

|                                          | — to e                                                                         | - to enable TX                                                     |  |  |  |

|                                          |                                                                                |                                                                    |  |  |  |

|                                          |                                                                                | Register Model                                                     |  |  |  |

|                                          |                                                                                |                                                                    |  |  |  |

|                                          | IICA                                                                           |                                                                    |  |  |  |

|                                          | When addressed as a slave (in slave mode), the module responds to this address |                                                                    |  |  |  |

|                                          | Baud rate = BUSCLK / (2 x MULT x (SCL DIVIDER))                                |                                                                    |  |  |  |

| IICC1 IICEN IICIE MST TX TXAK RSTA 0 0   |                                                                                |                                                                    |  |  |  |

|                                          | Module configuration                                                           |                                                                    |  |  |  |

| IICS TCF IAAS BUSY ARBL 0 SRW IICIF RXAK |                                                                                |                                                                    |  |  |  |

|                                          | Module status flags                                                            |                                                                    |  |  |  |

|                                          | IICD DATA                                                                      |                                                                    |  |  |  |

|                                          | Data register; Write to transmit IIC data read to read IIC data                |                                                                    |  |  |  |

|                                          | IICC2                                                                          |                                                                    |  |  |  |

|                                          |                                                                                | Address configuration                                              |  |  |  |

Figure 11-11. IIC Module Quick Start

MC9S08SG8 MCU Series Data Sheet, Rev. 8

# 12.1.2 Features

Timer system features include:

- 8-bit up-counter

- Free-running or 8-bit modulo limit

- Software controllable interrupt on overflow

- Counter reset bit (TRST)

- Counter stop bit (TSTP)

- Four software selectable clock sources for input to prescaler:

- System bus clock rising edge

- Fixed frequency clock (XCLK) rising edge

- External clock source on the TCLK pin rising edge

- External clock source on the TCLK pin falling edge

- Nine selectable clock prescale values:

- Clock source divide by 1, 2, 4, 8, 16, 32, 64, 128, or 256

# 12.1.3 Modes of Operation

This section defines the MTIM's operation in stop, wait and background debug modes.

# 12.1.3.1 MTIM in Wait Mode

The MTIM continues to run in wait mode if enabled before executing the WAIT instruction. Therefore, the MTIM can be used to bring the MCU out of wait mode if the timer overflow interrupt is enabled. For lowest possible current consumption, the MTIM should be stopped by software if not needed as an interrupt source during wait mode.

# 12.1.3.2 MTIM in Stop Modes

The MTIM is disabled in all stop modes, regardless of the settings before executing the STOP instruction. Therefore, the MTIM cannot be used as a wake up source from stop modes.

Waking from stop1 and stop2 modes, the MTIM will be put into its reset state. If stop3 is exited with a reset, the MTIM will be put into its reset state. If stop3 is exited with an interrupt, the MTIM continues from the state it was in when stop3 was entered. If the counter was active upon entering stop3, the count will resume from the current value.

# 12.1.3.3 MTIM in Active Background Mode

The MTIM suspends all counting until the microcontroller returns to normal user operating mode. Counting resumes from the suspended value as long as an MTIM reset did not occur (TRST written to a 1 or MTIMMOD written).

#### Real-Time Counter (S08RTCV1)

{

```

#pragma TRAP_PROC

void RTC_ISR(void)

/* Clear the interrupt flag */

RTCSC.byte = RTCSC.byte | 0x80;

/* RTC interrupts every 1 Second */

Seconds++;

/* 60 seconds in a minute */

if (Seconds > 59)

Minutes++;

Seconds = 0;

}

/* 60 minutes in an hour */

if (Minutes > 59) {

Hours++;

Minutes = 0;

}

/* 24 hours in a day */

if (Hours > 23) {

Days ++;

Hours = 0;

}

```

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3<br>WAKE | <ul> <li>Receiver Wakeup Method Select — Refer to Section 14.3.3.2, "Receiver Wakeup Operation" for more information.</li> <li>0 Idle-line wakeup.</li> <li>1 Address-mark wakeup.</li> </ul>                                                                                                                                                                                                                                    |  |  |

| 2<br>ILT  | Idle Line Type Select — Setting this bit to 1 ensures that the stop bit and logic 1 bits at the end of a characte do not count toward the 10 or 11 bit times of logic high level needed by the idle line detection logic. Refer to Section 14.3.3.2.1, "Idle-Line Wakeup" for more information.         0       Idle character bit count starts after start bit.         1       Idle character bit count starts after stop bit. |  |  |

| 1<br>PE   | <ul> <li>Parity Enable — Enables hardware parity generation and checking. When parity is enabled, the most significant bit (MSB) of the data character (eighth or ninth data bit) is treated as the parity bit.</li> <li>0 No hardware parity generation or checking.</li> <li>1 Parity enabled.</li> </ul>                                                                                                                      |  |  |

| 0<br>PT   | <ul> <li>Parity Type — Provided parity is enabled (PE = 1), this bit selects even or odd parity. Odd parity means the total number of 1s in the data character, including the parity bit, is odd. Even parity means the total number of 1s in the data character, including the parity bit, is even.</li> <li>0 Even parity.</li> <li>1 Odd parity.</li> </ul>                                                                   |  |  |

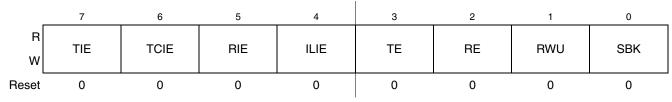

# 14.2.3 SCI Control Register 2 (SCIC2)

This register can be read or written at any time.

Figure 14-7. SCI Control Register 2 (SCIC2)

#### Table 14-4. SCIC2 Field Descriptions

| Field     | Description                                                                                                                                                                         |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>TIE  | Transmit Interrupt Enable (for TDRE)00111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111                                        |  |

| 6<br>TCIE | Transmission Complete Interrupt Enable (for TC)         0       Hardware interrupts from TC disabled (use polling).         1       Hardware interrupt requested when TC flag is 1. |  |

| 5<br>RIE  | Receiver Interrupt Enable (for RDRF)0Hardware interrupts from RDRF disabled (use polling).1Hardware interrupt requested when RDRF flag is 1.                                        |  |

| 4<br>ILIE | Idle Line Interrupt Enable (for IDLE)00111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111111 <td< td=""></td<>                     |  |

All TPM interrupts are listed in Table 16-11 which shows the interrupt name, the name of any local enable that can block the interrupt request from leaving the TPM and getting recognized by the separate interrupt processing logic.

| Interrupt | Local<br>Enable | Source           | Description                                                                                                            |

|-----------|-----------------|------------------|------------------------------------------------------------------------------------------------------------------------|

| TOF       | TOIE            | Counter overflow | Set each time the timer counter reaches its terminal count (at transition to next count value which is usually 0x0000) |

| CHnF      | CHnIE           | Channel event    | An input capture or output compare event took place on channel n                                                       |

The TPM module will provide a high-true interrupt signal. Vectors and priorities are determined at chip integration time in the interrupt module so refer to the user's guide for the interrupt module or to the chip's complete documentation for details.

# 16.6.2 Description of Interrupt Operation

For each interrupt source in the TPM, a flag bit is set upon recognition of the interrupt condition such as timer overflow, channel-input capture, or output-compare events. This flag may be read (polled) by software to determine that the action has occurred, or an associated enable bit (TOIE or CHnIE) can be set to enable hardware interrupt generation. While the interrupt enable bit is set, a static interrupt will generate whenever the associated interrupt flag equals one. The user's software must perform a sequence of steps to clear the interrupt flag before returning from the interrupt-service routine.

TPM interrupt flags are cleared by a two-step process including a read of the flag bit while it is set (1) followed by a write of zero (0) to the bit. If a new event is detected between these two steps, the sequence is reset and the interrupt flag remains set after the second step to avoid the possibility of missing the new event.

### 16.6.2.1 Timer Overflow Interrupt (TOF) Description

The meaning and details of operation for TOF interrupts varies slightly depending upon the mode of operation of the TPM system (general purpose timing functions versus center-aligned PWM operation). The flag is cleared by the two step sequence described above.

### 16.6.2.1.1 Normal Case

Normally TOF is set when the timer counter changes from 0xFFFF to 0x0000. When the TPM is not configured for center-aligned PWM (CPWMS=0), TOF gets set when the timer counter changes from the terminal count (the value in the modulo register) to 0x0000. This case corresponds to the normal meaning of counter overflow.

| Num | с | Characteristic                               | Symbol           | Condition | Min  | Typ <sup>1</sup> | Max  | Unit | Temp Rated <sup>2</sup> |                   |

|-----|---|----------------------------------------------|------------------|-----------|------|------------------|------|------|-------------------------|-------------------|

|     |   |                                              |                  |           |      |                  |      |      | Stand<br>ard            | AEC<br>Grade<br>0 |

| 23  |   | Low-voltage inhibit reset/recover hysteresis | V <sub>hys</sub> | 5 V       |      | 100              |      | mV   | х                       | х                 |

|     |   |                                              |                  | 3 V       | _    | 60               | _    |      | х                       | х                 |

| 24  | Ρ | Bandgap Voltage Reference <sup>13</sup>      | V <sub>BG</sub>  |           | 1.18 | 1.20             | 1.21 | V    | х                       |                   |

|     |   |                                              |                  |           | 1.17 | 1.20             | 1.22 | V    |                         | х                 |

### Table A-6. DC Characteristics (continued)

<sup>1</sup> Typical values are measured at 25°C. Characterized, not tested.

- <sup>2</sup> Electrical characteristics only apply to the temperature rated devices marked with x.

- <sup>3</sup> When a pin interrupt is configured to detect rising edges, pulldown resistors are used in place of pullup resistors.

- <sup>4</sup> The specified resistor value is the actual value internal to the device. The pullup value may measure higher when measured externally on the pin.

- <sup>5</sup> Power supply must maintain regulation within operating  $V_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{In} > V_{DD}$ ) is greater than  $I_{DD}$ , the injection current may flow out of  $V_{DD}$  and could result in external power supply going out of regulation. Ensure external  $V_{DD}$  load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if clock rate is very low (which would reduce overall power consumption).

- $^{6}\,$  All functional non-supply pins are internally clamped to  $V_{SS}$  and  $V_{DD}$

- <sup>7</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

- $^{8}$  The RESET pin does not have a clamp diode to V<sub>DD</sub>. Do not drive this pin above V<sub>DD</sub>.

- <sup>9</sup> Maximum is highest voltage that POR will occur.

- <sup>10</sup> Simulated, not tested

- <sup>11</sup> Device functionality is guaranteed between the LVD threshold VLVD0 and VDD Min.When VDD is below the minimum operating voltage (VDD Min), the analog parameters for the IO pins, ACMP and ADC, are not guaranteed to meet data sheet performance parameters.

- <sup>12</sup> In addition to LVD, it is recommended to also use the LVW feature. LVW can trigger an interrupt and be used as an indicator to warn that the VDD is dropping, so that the software can take actions accordingly before the VDD drops below VDD Min

- <sup>13</sup> Factory trimmed at  $V_{DD} = 5.0 \text{ V}$