Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0                  |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | S08                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 40MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, LINbus, SCI, SPI                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 16                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 256 x 8                                                                |

| RAM Size                   | 512 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 12x10b                                                             |

| Oscillator Type            | External                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-TSSOP (0.173", 4.40mm Width)                                        |

| Supplier Device Package    | 20-TSSOP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08sl8f1ctjr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Section Number**

Title

## Page

|     | 6.4.1 | Edge Only Sensitivity         | 78 |

|-----|-------|-------------------------------|----|

|     |       | Edge and Level Sensitivity    |    |

|     |       | Pull-up/Pull-down Resistors   |    |

|     |       | Pin Interrupt Initialization  |    |

| 6.5 |       | avior in Stop Modes           |    |

|     |       | I/O and Pin Control Registers |    |

|     |       | Port A Registers              |    |

|     |       | Port B Registers              |    |

|     |       | Port C Registers              |    |

# Chapter 7 Central Processor Unit (S08CPUV2)

| 7.1 | Introdu | ction                           | 91 |

|-----|---------|---------------------------------|----|

|     | 7.1.1   | Features                        | 91 |

| 7.2 | Program | nmer's Model and CPU Registers  | 92 |

|     | 7.2.1   | Accumulator (A)                 |    |

|     | 7.2.2   | Index Register (H:X)            | 92 |

|     | 7.2.3   | Stack Pointer (SP)              | 93 |

|     | 7.2.4   | Program Counter (PC)            | 93 |

|     | 7.2.5   | Condition Code Register (CCR)   | 93 |

| 7.3 | Address | sing Modes                      | 94 |

|     | 7.3.1   | Inherent Addressing Mode (INH)  | 95 |

|     | 7.3.2   | Relative Addressing Mode (REL)  | 95 |

|     | 7.3.3   | Immediate Addressing Mode (IMM) | 95 |

|     | 7.3.4   | Direct Addressing Mode (DIR)    | 95 |

|     | 7.3.5   | Extended Addressing Mode (EXT)  | 95 |

|     | 7.3.6   | Indexed Addressing Mode         | 95 |

| 7.4 | Special | Operations                      | 96 |

|     | 7.4.1   | Reset Sequence                  | 97 |

|     | 7.4.2   | Interrupt Sequence              | 97 |

|     | 7.4.3   | Wait Mode Operation             |    |

|     | 7.4.4   | Stop Mode Operation             | 98 |

|     | 7.4.5   | BGND Instruction                | 98 |

| 7.5 | HCS08   | Instruction Set Summary         | 99 |

# Chapter 8 5-V Analog Comparator (S08ACMPV2)

| 8.1 | Introdu | ction                              |  |

|-----|---------|------------------------------------|--|

|     | 8.1.1   | ACMP Configuration Information     |  |

|     |         | ACMP in Stop3 Mode                 |  |

|     |         | ACMP/TPM Configuration Information |  |

|     |         | Features                           |  |

|     |         |                                    |  |

### MC9S08SG8 MCU Series Data Sheet, Rev. 8

# **Section Number**

Title

|     | 8.1.5 | Modes of Operation    | 113 |

|-----|-------|-----------------------|-----|

|     |       | Block Diagram         |     |

| 8.2 |       | l Signal Description  |     |

|     |       | / Map                 |     |

|     |       | Register Descriptions |     |

| 8.4 |       | nal Description       |     |

## Chapter 9 Analog-to-Digital Converter (S08ADCV1)

| 9.1 | Introduc | ction                                       | 119 |

|-----|----------|---------------------------------------------|-----|

|     | 9.1.1    | Channel Assignments                         | 119 |

|     | 9.1.2    | Alternate Clock                             | 120 |

|     | 9.1.3    | Hardware Trigger                            | 120 |

|     | 9.1.4    | Temperature Sensor                          | 120 |

|     | 9.1.5    | Features                                    | 123 |

|     | 9.1.6    | Block Diagram                               | 123 |

| 9.2 | Externa  | l Signal Description                        | 124 |

|     | 9.2.1    | Analog Power (V <sub>DDAD</sub> )           | 125 |

|     | 9.2.2    | Analog Ground (V <sub>SSAD</sub> )          | 125 |

|     | 9.2.3    | Voltage Reference High (V <sub>REFH</sub> ) | 125 |

|     | 9.2.4    | Voltage Reference Low (V <sub>REFL</sub> )  |     |

|     | 9.2.5    | Analog Channel Inputs (ADx)                 |     |

| 9.3 | Register | r Definition                                |     |

|     | 9.3.1    | Status and Control Register 1 (ADCSC1)      |     |

|     | 9.3.2    | Status and Control Register 2 (ADCSC2)      |     |

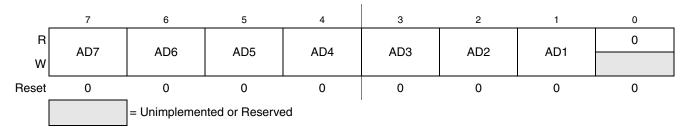

|     | 9.3.3    | Data Result High Register (ADCRH)           | 128 |

|     | 9.3.4    | Data Result Low Register (ADCRL)            | 128 |

|     | 9.3.5    | Compare Value High Register (ADCCVH)        |     |

|     | 9.3.6    | Compare Value Low Register (ADCCVL)         | 129 |

|     | 9.3.7    | Configuration Register (ADCCFG)             |     |

|     | 9.3.8    | Pin Control 1 Register (APCTL1)             |     |

|     | 9.3.9    | Pin Control 2 Register (APCTL2)             | 132 |

|     | 9.3.10   | Pin Control 3 Register (APCTL3)             | 133 |

| 9.4 | Functio  | nal Description                             |     |

|     | 9.4.1    | Clock Select and Divide Control             | 134 |

|     | 9.4.2    | Input Select and Pin Control                | 135 |

|     | 9.4.3    | Hardware Trigger                            | 135 |

|     | 9.4.4    | Conversion Control                          | 135 |

|     | 9.4.5    | Automatic Compare Function                  | 138 |

|     | 9.4.6    | MCU Wait Mode Operation                     | 138 |

|     | 9.4.7    | MCU Stop3 Mode Operation                    | 138 |

|     | 9.4.8    | MCU Stop1 and Stop2 Mode Operation          | 139 |

## **Section Number**

Title

| 9.5 | Initializ | ation Information                 |     |

|-----|-----------|-----------------------------------|-----|

|     |           | ADC Module Initialization Example |     |

| 9.6 | Applica   | tion Information                  | 141 |

|     | 9.6.1     | External Pins and Routing         | 141 |

|     | 9.6.2     | Sources of Error                  | 143 |

# Chapter 10 Internal Clock Source (S08ICSV2)

| 10.1 | Introduction                             | 147 |

|------|------------------------------------------|-----|

|      | 10.1.1 Module Configuration              | 147 |

|      | 10.1.2 Features                          |     |

|      | 10.1.3 Block Diagram                     | 149 |

|      | 10.1.4 Modes of Operation                | 150 |

| 10.2 | External Signal Description              | 151 |

| 10.3 | Register Definition                      | 151 |

|      | 10.3.1 ICS Control Register 1 (ICSC1)    | 152 |

|      | 10.3.2 ICS Control Register 2 (ICSC2)    |     |

|      | 10.3.3 ICS Trim Register (ICSTRM)        | 154 |

|      | 10.3.4 ICS Status and Control (ICSSC)    | 154 |

| 10.4 | Functional Description                   | 155 |

|      | 10.4.1 Operational Modes                 |     |

|      | 10.4.2 Mode Switching                    | 157 |

|      | 10.4.3 Bus Frequency Divider             | 158 |

|      | 10.4.4 Low Power Bit Usage               | 158 |

|      | 10.4.5 Internal Reference Clock          | 158 |

|      | 10.4.6 Optional External Reference Clock | 158 |

|      | 10.4.7 Fixed Frequency Clock             | 159 |

# Chapter 11 Inter-Integrated Circuit (S08IICV2)

| 161 |

|-----|

| 101 |

| 163 |

| 163 |

| 163 |

| 164 |

| 164 |

| 164 |

| 164 |

| 165 |

| 165 |

| 168 |

|     |

Chapter 4 Memory

| Address           | Register Name | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

|-------------------|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x1845            | PTAPS         | 0      | 0      | 0      | 0      | PTAPS3 | PTAPS2 | PTAPS1 | PTAPS0 |

| 0x1846            | PTAES         | 0      | 0      | 0      | 0      | PTAES3 | PTAES2 | PTAES1 | PTAES0 |

| 0x1847            | Reserved      | —      | _      | _      | _      | —      | _      | _      | —      |

| 0x1848            | PTBPE         | PTBPE7 | PTBPE6 | PTBPE5 | PTBPE4 | PTBPE3 | PTBPE2 | PTBPE1 | PTBPE0 |

| 0x1849            | PTBSE         | PTBSE7 | PTBSE6 | PTBSE5 | PTBSE4 | PTBSE3 | PTBSE2 | PTBSE1 | PTBSE0 |

| 0x184A            | PTBDS         | PTBDS7 | PTBDS6 | PTBDS5 | PTBDS4 | PTBDS3 | PTBDS2 | PTBDS1 | PTBDS0 |

| 0x184B            | Reserved      | —      | _      | _      | _      | _      | _      |        | —      |

| 0x184C            | PTBSC         | 0      | 0      | 0      | 0      | PTBIF  | PTBACK | PTBIE  | PTBMOD |

| 0x184D            | PTBPS         | 0      | 0      | 0      | 0      | PTBPS3 | PTBPS2 | PTBPS1 | PTBPS0 |

| 0x184E            | PTBES         | 0      | 0      | 0      | 0      | PTBES3 | PTBES2 | PTBES1 | PTBES0 |

| 0x184F            | Reserved      | —      | _      | _      | _      | _      | _      |        | —      |

| 0x1850            | PTCPE         | 0      | 0      | 0      | 0      | PTCPE3 | PTCPE2 | PTCPE1 | PTCPE0 |

| 0x1851            | PTCSE         | 0      | 0      | 0      | 0      | PTCSE3 | PTCSE2 | PTCSE1 | PTCSE0 |

| 0x1852            | PTCDS         | 0      | 0      | 0      | 0      | PTCDS3 | PTCDS2 | PTCDS1 | PTCDS0 |

| 0x1853            | GNGC          | GNGPS7 | GNGPS6 | GNGPS5 | GNGPS4 | GNGPS3 | GNGPS2 | GNGPS1 | GNGEN  |

| 0x1854–<br>0x185F | Reserved      |        | —      |        |        |        |        |        |        |

### Table 4-3. High-Page Register Summary (Sheet 2 of 2)

Chapter 4 Memory

# 4.5.3 **Program and Erase Command Execution**

The steps for executing any of the commands are listed below. The FCDIV register must be initialized and any error flags cleared before beginning command execution. The command execution steps are:

1. Write a data value to an address in the FLASH array. The address and data information from this write is latched into the FLASH interface. This write is a required first step in any command sequence. For erase and blank check commands, the value of the data is not important. For page erase commands, the address may be any address in the 512-byte page of FLASH to be erased. For mass erase and blank check commands, the address can be any address in the FLASH memory. Whole pages of 512 bytes are the smallest block of FLASH that may be erased.

### NOTE

Do not program any byte in the FLASH more than once after a successful erase operation. Reprogramming bits to a byte that is already programmed is not allowed without first erasing the page in which the byte resides or mass erasing the entire FLASH memory. Programming without first erasing may disturb data stored in the FLASH.

- 2. Write the command code for the desired command to FCMD. The five valid commands are blank check (0x05), byte program (0x20), burst program (0x25), page erase (0x40), and mass erase (0x41). The command code is latched into the command buffer.

- 3. Write a 1 to the FCBEF bit in FSTAT to clear FCBEF and launch the command (including its address and data information).

A partial command sequence can be aborted manually by writing a 0 to FCBEF any time after the write to the memory array and before writing the 1 that clears FCBEF and launches the complete command. Aborting a command in this way sets the FACCERR access error flag, which must be cleared before starting a new command.

A strictly monitored procedure must be obeyed or the command will not be accepted. This minimizes the possibility of any unintended changes to the FLASH memory contents. The command complete flag (FCCF) indicates when a command is complete. The command sequence must be completed by clearing FCBEF to launch the command. Figure 4-2 is a flowchart for executing all of the commands except for burst programming. The FCDIV register must be initialized before using any FLASH commands. This must be done only once following a reset.

the MCU secure. During development, whenever the FLASH is erased, it is good practice to immediately program the SEC00 bit to 0 in NVOPT so SEC01:SEC00 = 1:0. This would allow the MCU to remain unsecured after a subsequent reset.

The on-chip debug module cannot be enabled while the MCU is secure. The separate background debug controller can still be used for background memory access commands of unsecured resources.

A user can choose to allow or disallow a security unlocking mechanism through an 8-byte backdoor security key. If the nonvolatile KEYEN bit in NVOPT/FOPT is 0, the backdoor key is disabled and there is no way to disengage security without completely erasing all FLASH locations. If KEYEN is 1, a secure user program can temporarily disengage security by:

- 1. Writing 1 to KEYACC in the FCNFG register. This makes the FLASH module interpret writes to the backdoor comparison key locations (NVBACKKEY through NVBACKKEY+7) as values to be compared against the key rather than as the first step in a FLASH program or erase command.

- 2. Writing the user-entered key values to the NVBACKKEY through NVBACKKEY+7 locations. These writes must be done in order starting with the value for NVBACKKEY and ending with NVBACKKEY+7. STHX should not be used for these writes because these writes cannot be done on adjacent bus cycles. User software normally would get the key codes from outside the MCU system through a communication interface such as a serial I/O.

- 3. Writing 0 to KEYACC in the FCNFG register. If the 8-byte key that was just written matches the key stored in the FLASH locations, SEC01:SEC00 are automatically changed to 1:0 and security will be disengaged until the next reset.

The security key can be written only from secure memory (either RAM or FLASH), so it cannot be entered through background commands without the cooperation of a secure user program.

The backdoor comparison key (NVBACKKEY through NVBACKKEY+7) is located in FLASH memory locations in the nonvolatile register space so users can program these locations exactly as they would program any other FLASH memory location. The nonvolatile registers are in the same 512-byte block of FLASH as the reset and interrupt vectors, so block protecting that space also block protects the backdoor comparison key. Block protects cannot be changed from user application programs, so if the vector space is block protected, the backdoor security key mechanism cannot permanently change the block protect, security settings, or the backdoor key.

Security can always be disengaged through the background debug interface by taking these steps:

- 1. Disable any block protections by writing FPROT. FPROT can be written only with background debug commands, not from application software.

- 2. Mass erase FLASH if necessary.

- 3. Blank check FLASH. Provided FLASH is completely erased, security is disengaged until the next reset.

To avoid returning to secure mode after the next reset, program NVOPT so SEC01:SEC00 = 1:0.

# 4.7 FLASH Registers and Control Bits

The FLASH module has nine 8-bit registers in the high-page register space, two locations (NVOPT, NVPROT) in the nonvolatile register space in FLASH memory are copied into corresponding high-page

| Vector<br>Priority | Vector<br>Number | Address<br>(High/Low) | Vector<br>Name | Module            | Source                             | Enable                        | Description                                          |

|--------------------|------------------|-----------------------|----------------|-------------------|------------------------------------|-------------------------------|------------------------------------------------------|

|                    | 31               | 0xFFC0/0xFFC1         | —              | _                 |                                    | _                             | —                                                    |

| Lowest             | 30               | 0xFFC2/0xFFC3         | Vacmp          | ACMP              | ACF                                | ACIE                          | Analog comparator                                    |

|                    | 29               | 0xFFC4/0xFFC5         | —              | _                 | —                                  | —                             | —                                                    |

|                    | 28               | 0xFFC6/0xFFC7         | —              | _                 | —                                  | —                             | —                                                    |

|                    | 27               | 0xFFC8/0xFFC9         | —              | _                 | —                                  | —                             | —                                                    |

|                    | 26               | 0xFFCA/0xFFCB         | Vmtim          | MTIM              | TOF                                | TOIE                          | MTIM overflow                                        |

|                    | 25               | 0xFFCC/0xFFCD         | Vrtc           | RTC               | RTIF                               | RTIE                          | Real-time interrupt                                  |

|                    | 24               | 0xFFCE/0xFFCF         | Viic           | IIC               | IICIF                              | IICIE                         | IIC control                                          |

|                    | 23               | 0xFFD0/0xFFD1         | Vadc           | ADC               | COCO                               | AIEN                          | ADC                                                  |

|                    | 22               | 0xFFD2/0xFFD3         | —              | _                 | —                                  | —                             | —                                                    |

|                    | 21               | 0xFFD4/0xFFD5         | Vportb         | Port B            | PTBIF                              | PTBIE                         | Port B Pins                                          |

|                    | 20               | 0xFFD6/0xFFD7         | Vporta         | Port A            | PTAIF                              | PTAIE                         | Port A Pins                                          |

|                    | 19               | 0xFFD8/0xFFD9         | —              | _                 | —                                  | —                             | —                                                    |

|                    | 18               | 0xFFDA/0xFFDB         | Vscitx         | SCI               | TDRE, TC                           | TIE, TCIE                     | SCI transmit                                         |

|                    | 17               | 0xFFDC/0xFFDD         | Vscirx         | SCI               | IDLE, RDRF,<br>LBKDIF,<br>RXEDGIF  | ILIE, RIE, LBKDIE,<br>RXEDGIE | SCI receive                                          |

|                    | 16               | 0xFFDE/0xFFDF         | Vscierr        | SCI               | OR, NF,<br>FE, PF                  | ORIE, NFIE,<br>FEIE, PFIE     | SCI error                                            |

|                    | 15               | 0xFFE0/0xFFE1         | Vspi           | SPI               | SPIF, MODF,<br>SPTEF               | SPIE, SPIE, SPTIE             | SPI                                                  |

|                    | 14               | 0xFFE2/0xFFE3         | Vtpm2ovf       | TPM2              | TOF                                | TOIE                          | TPM2 overflow                                        |

|                    | 13               | 0xFFE4/0xFFE5         | Vtpm2ch1       | TPM2              | CH1F                               | CH1IE                         | TPM2 channel 1                                       |

|                    | 12               | 0xFFE6/0xFFE7         | Vtpm2ch0       | TPM2              | CH0F                               | CH0IE                         | TPM2 channel 0                                       |

|                    | 11               | 0xFFE8/0xFFE9         | Vtpm1ovf       | TPM1              | TOF                                | TOIE                          | TPM1 overflow                                        |

|                    | 10               | 0xFFEA/0xFFEB         | —              | —                 | —                                  | —                             | —                                                    |

|                    | 9                | 0xFFEC/0xFFED         | —              |                   | —                                  | —                             | —                                                    |

|                    | 8                | 0xFFEE/0xFFEF         | —              |                   | —                                  | —                             | —                                                    |

|                    | 7                | 0xFFF0/0xFFF1         | —              | —                 | —                                  | —                             | —                                                    |

|                    | 6                | 0xFFF2/0xFFF3         | Vtpm1ch1       | TPM1              | CH1F                               | CH1IE                         | TPM1 channel 1                                       |

|                    | 5                | 0xFFF4/0xFFF5         | Vtpm1ch0       | TPM1              | CH0F                               | CH0IE                         | TPM1 channel 0                                       |

|                    | 4                | 0xFFF6/0xFFF7         | —              | —                 | —                                  | —                             | —                                                    |

|                    | 3                | 0xFFF8/0xFFF9         | Vlvd           | System<br>control | LVWF                               | LVWIE                         | Low-voltage warning                                  |

|                    | 2                | 0xFFFA/0xFFFB         | —              |                   | —                                  | —                             | —                                                    |

|                    | 1                | 0xFFFC/0xFFFD         | Vswi           | Core              | SWI Instruction                    | —                             | Software interrupt                                   |

| ¥                  | 0                | 0xFFFE/0xFFFF         | Vreset         | System<br>control | COP,<br>LVD,<br>RESET pin,         | COPT<br>LVDRE<br>—            | Watchdog timer<br>Low-voltage detect<br>External pin |

| Highest            |                  |                       |                |                   | Illegal opcode,<br>Illegal address | —<br>—                        | Illegal opcode<br>Illegal address                    |

### Table 5-2. Vector Summary

Chapter 5 Resets, Interrupts, and General System Control

# 5.7.1 System Reset Status Register (SRS)

This high page register includes read-only status flags to indicate the source of the most recent reset. When a debug host forces reset by writing 1 to BDFR in the SBDFR register, none of the status bits in SRS will be set. Writing any value to this register address causes a COP reset when the COP is enabled except the values 0x55 and 0xAA. Writing a 0x55-0xAA sequence to this address clears the COP watchdog timer without affecting the contents of this register. The reset state of these bits depends on what caused the MCU to reset.

|                     | 7                | 6                   | 5                   | 4                   | 3                   | 2            | 1    | 0 |

|---------------------|------------------|---------------------|---------------------|---------------------|---------------------|--------------|------|---|

| R                   | POR              | PIN                 | COP                 | ILOP                | ILAD                | 0            | LVD  | 0 |

| w                   |                  | Wi                  | iting 0x55, 0xA     | A to SRS addr       | ess clears CO       | vatchdog tim | ier. |   |

| POR:                | 1                | 0                   | 0                   | 0                   | 0                   | 0            | 1    | 0 |

| LVR:                | u <sup>(1)</sup> | 0                   | 0                   | 0                   | 0                   | 0            | 1    | 0 |

| Any other<br>reset: | 0                | Note <sup>(2)</sup> | Note <sup>(2)</sup> | Note <sup>(2)</sup> | Note <sup>(2)</sup> | 0            | 0    | 0 |

<sup>1</sup> u = unaffected

<sup>2</sup> Any of these reset sources that are active at the time of reset entry will cause the corresponding bit(s) to be set; bits corresponding to sources that are not active at the time of reset entry will be cleared.

### Figure 5-2. System Reset Status (SRS)

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>POR  | <ul> <li>Power-On Reset — Reset was caused by the power-on detection logic. Because the internal supply voltage was ramping up at the time, the low-voltage reset (LVR) status bit is also set to indicate that the reset occurred while the internal supply was below the LVR threshold.</li> <li>0 Reset not caused by POR.</li> <li>1 POR caused reset.</li> </ul>                                                                     |

| 6<br>PIN  | <ul> <li>External Reset Pin — Reset was caused by an active-low level on the external reset pin.</li> <li>0 Reset not caused by external reset pin.</li> <li>1 Reset came from external reset pin.</li> </ul>                                                                                                                                                                                                                             |

| 5<br>COP  | <ul> <li>Computer Operating Properly (COP) Watchdog — Reset was caused by the COP watchdog timer timing out. This reset source can be blocked by COPT bits = 0:0.</li> <li>0 Reset not caused by COP timeout.</li> <li>1 Reset caused by COP timeout.</li> </ul>                                                                                                                                                                          |

| 4<br>ILOP | <ul> <li>Illegal Opcode — Reset was caused by an attempt to execute an unimplemented or illegal opcode. The STOP instruction is considered illegal if stop is disabled by STOPE = 0 in the SOPT register. The BGND instruction is considered illegal if active background mode is disabled by ENBDM = 0 in the BDCSC register.</li> <li>0 Reset not caused by an illegal opcode.</li> <li>1 Reset caused by an illegal opcode.</li> </ul> |

# Chapter 6 Parallel Input/Output Control

This section explains software controls related to parallel input/output (I/O) and pin control. The MC9S08SG8 has three parallel I/O ports which include a total of 16 I/O pins. See Chapter 2, "Pins and Connections," for more information about pin assignments and external hardware considerations of these pins.

Many of these pins are shared with on-chip peripherals such as timer systems, communication systems, or pin interrupts as shown in Table 2-1. The peripheral modules have priority over the general-purpose I/O functions so that when a peripheral is enabled, the I/O functions associated with the shared pins are disabled.

After reset, the shared peripheral functions are disabled and the pins are configured as inputs (PTxDDn = 0). The pin control functions for each pin are configured as follows: slew rate disabled (PTxSEn = 0), low drive strength selected (PTxDSn = 0), and internal pull-ups disabled (PTxPEn = 0).

### NOTE

Not all general-purpose I/O pins are available on all packages. To avoid extra current drain from floating input pins, the user's reset initialization routine in the application program must either enable on-chip pull-up devices or change the direction of unconnected pins to outputs so the pins do not float.

# 6.1 Port Data and Data Direction

Reading and writing of parallel I/Os are performed through the port data registers. The direction, either input or output, is controlled through the port data direction registers. The parallel I/O port function for an individual pin is illustrated in the block diagram shown in Figure 6-1.

The data direction control bit (PTxDDn) determines whether the output buffer for the associated pin is enabled, and also controls the source for port data register reads. The input buffer for the associated pin is always enabled unless the pin is enabled as an analog function or is an output-only pin.

When a shared digital function is enabled for a pin, the output buffer is controlled by the shared function. However, the data direction register bit will continue to control the source for reads of the port data register.

When a shared analog function is enabled for a pin, both the input and output buffers are disabled. A value of 0 is read for any port data bit where the bit is an input (PTxDDn = 0) and the input buffer is disabled. In general, whenever a pin is shared with both an alternate digital function and an analog function, the analog function has priority such that if both the digital and analog functions are enabled, the analog function controls the pin.

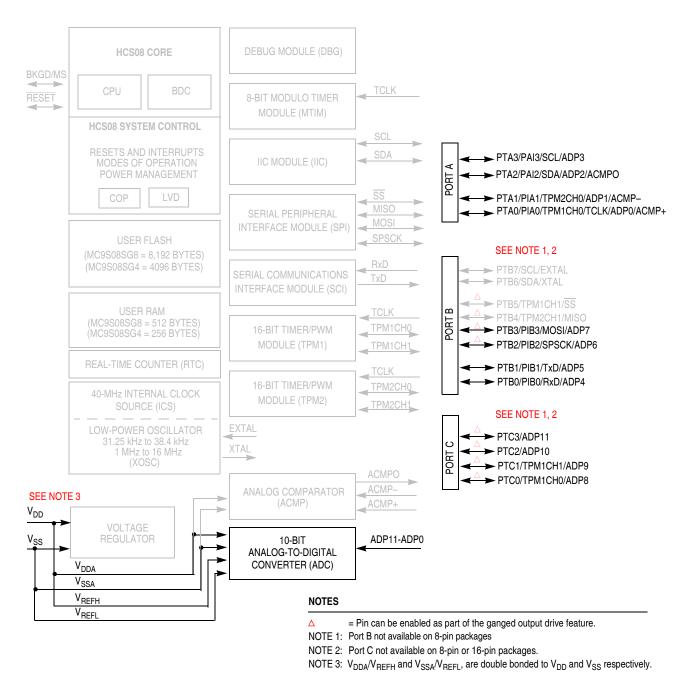

#### Chapter 9 Analog-to-Digital Converter (S08ADCV1)

Figure 9-1. MC9S08SG8 Block Diagram with ADC Module Highlighted

#### Analog-to-Digital Converter (S08ADCV1)

- Average the result by converting the analog input many times in succession and dividing the sum of the results. Four samples are required to eliminate the effect of a 1LSB, one-time error.

- Reduce the effect of synchronous noise by operating off the asynchronous clock (ADACK) and averaging. Noise that is synchronous to ADCK cannot be averaged out.

## 9.6.2.4 Code Width and Quantization Error

The ADC quantizes the ideal straight-line transfer function into 1024 steps (in 10-bit mode). Each step ideally has the same height (1 code) and width. The width is defined as the delta between the transition points to one code and the next. The ideal code width for an N bit converter (in this case N can be 8 or 10), defined as 1LSB, is:

## $1LSB = (V_{REFH} - V_{REFL}) / 2^{N} \qquad Eqn. 9-2$

There is an inherent quantization error due to the digitization of the result. For 8-bit or 10-bit conversions the code will transition when the voltage is at the midpoint between the points where the straight line transfer function is exactly represented by the actual transfer function. Therefore, the quantization error will be  $\pm 1/2$ LSB in 8- or 10-bit mode. As a consequence, however, the code width of the first (\$000) conversion is only 1/2LSB and the code width of the last (\$FF or \$3FF) is 1.5LSB.

## 9.6.2.5 Linearity Errors

The ADC may also exhibit non-linearity of several forms. Every effort has been made to reduce these errors but the system should be aware of them because they affect overall accuracy. These errors are:

- Zero-scale error (E<sub>ZS</sub>) (sometimes called offset) This error is defined as the difference between the actual code width of the first conversion and the ideal code width (1/2LSB). Note, if the first conversion is \$001, then the difference between the actual \$001 code width and its ideal (1LSB) is used.

- Full-scale error  $(E_{FS})$  This error is defined as the difference between the actual code width of the last conversion and the ideal code width (1.5LSB). Note, if the last conversion is \$3FE, then the difference between the actual \$3FE code width and its ideal (1LSB) is used.

- Differential non-linearity (DNL) This error is defined as the worst-case difference between the actual code width and the ideal code width for all conversions.

- Integral non-linearity (INL) This error is defined as the highest-value the (absolute value of the) running sum of DNL achieves. More simply, this is the worst-case difference of the actual transition voltage to a given code and its corresponding ideal transition voltage, for all codes.

- Total unadjusted error (TUE) This error is defined as the difference between the actual transfer function and the ideal straight-line transfer function, and therefore includes all forms of error.

## 9.6.2.6 Code Jitter, Non-Monotonicity and Missing Codes

Analog-to-digital converters are susceptible to three special forms of error. These are code jitter, non-monotonicity, and missing codes.

Code jitter is when, at certain points, a given input voltage converts to one of two values when sampled repeatedly. Ideally, when the input voltage is infinitesimally smaller than the transition voltage, the

converter yields the lower code (and vice-versa). However, even very small amounts of system noise can cause the converter to be indeterminate (between two codes) for a range of input voltages around the transition voltage. This range is normally around  $\pm 1/2$  LSB and will increase with noise. This error may be reduced by repeatedly sampling the input and averaging the result. Additionally the techniques discussed in Section 9.6.2.3 will reduce this error.

Non-monotonicity is defined as when, except for code jitter, the converter converts to a lower code for a higher input voltage. Missing codes are those values which are never converted for any input value.

In 8-bit or 10-bit mode, the ADC is guaranteed to be monotonic and to have no missing codes.

# 10.1.2 Features

Key features of the ICS module follow. For device specific information, refer to the ICS Characteristics in the Electricals section of the documentation.

- Frequency-locked loop (FLL) is trimmable for accuracy

- 0.2% resolution using internal 32kHz reference

- 1.5% deviation over voltage and temperature using internal 32kHz reference

- Internal or external reference clocks up to 5MHz can be used to control the FLL

- 3 bit select for reference divider is provided

- Internal reference clock has 9 trim bits available

- Internal or external reference clocks can be selected as the clock source for the MCU

- Whichever clock is selected as the source can be divided down

- 2 bit select for clock divider is provided

- Allowable dividers are: 1, 2, 4, 8

- BDC clock is provided as a constant divide by 2 of the DCO output

- Control signals for a low power oscillator as the external reference clock are provided — HGO, RANGE, EREFS, ERCLKEN, EREFSTEN

- FLL Engaged Internal mode is automatically selected out of reset

## 10.1.3 Block Diagram

Figure 10-2 is the ICS block diagram.

Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

# 11.3.1 IIC Address Register (IICA)

Figure 11-3. IIC Address Register (IICA)

Table 11-2. IICA Field Descriptions

| Field | Description                                                                                                                                                                                            |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Slave Address.</b> The AD[7:1] field contains the slave address to be used by the IIC module. This field is used on the 7-bit address scheme and the lower seven bits of the 10-bit address scheme. |

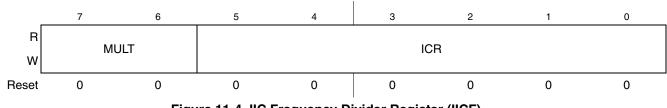

# 11.3.2 IIC Frequency Divider Register (IICF)

Figure 11-4. IIC Frequency Divider Register (IICF)

# 11.7 Initialization/Application Information

|    | Module Initialization (Slave) |                                                                            |       |  |  |  |  |  |  |  |  |

|----|-------------------------------|----------------------------------------------------------------------------|-------|--|--|--|--|--|--|--|--|

| 1. | Write: 1                      |                                                                            |       |  |  |  |  |  |  |  |  |

|    | — to e                        | enable or disable general call                                             |       |  |  |  |  |  |  |  |  |

|    | — to s                        | select 10-bit or 7-bit addressing mode                                     |       |  |  |  |  |  |  |  |  |

| 2. | Write: 1                      | IICA                                                                       |       |  |  |  |  |  |  |  |  |

|    | - to s                        | set the slave address                                                      |       |  |  |  |  |  |  |  |  |

| 3. | Write: I                      | IICC1                                                                      |       |  |  |  |  |  |  |  |  |

|    | — to e                        | enable IIC and interrupts                                                  |       |  |  |  |  |  |  |  |  |

| 4. | Initializ                     | e RAM variables (IICEN = 1 and IICIE = 1) for transmit data                |       |  |  |  |  |  |  |  |  |

| 5. | Initializ                     | ze RAM variables used to achieve the routine shown in Figure 11            | -12   |  |  |  |  |  |  |  |  |

|    |                               |                                                                            |       |  |  |  |  |  |  |  |  |

|    |                               | Module Initialization (Master)                                             |       |  |  |  |  |  |  |  |  |

| 1. | Write: 1                      | IICF                                                                       |       |  |  |  |  |  |  |  |  |

|    | - to s                        | set the IIC baud rate (example provided in this chapter)                   |       |  |  |  |  |  |  |  |  |

| 2. | Write: I                      | IICC1                                                                      |       |  |  |  |  |  |  |  |  |

|    | — to e                        | enable IIC and interrupts                                                  |       |  |  |  |  |  |  |  |  |

| 3. | Initializ                     | ze RAM variables (IICEN = 1 and IICIE = 1) for transmit data               |       |  |  |  |  |  |  |  |  |

| 4. | Initializ                     | ze RAM variables used to achieve the routine shown in Figure 11            | 1-12  |  |  |  |  |  |  |  |  |

| 5. | Write: I                      | IICC1                                                                      |       |  |  |  |  |  |  |  |  |

|    | — to e                        | enable TX                                                                  |       |  |  |  |  |  |  |  |  |

|    |                               |                                                                            |       |  |  |  |  |  |  |  |  |

|    |                               | Register Model                                                             |       |  |  |  |  |  |  |  |  |

|    |                               | AD[7:4]                                                                    |       |  |  |  |  |  |  |  |  |

|    | IICA                          |                                                                            | 0     |  |  |  |  |  |  |  |  |

|    | IICF                          | When addressed as a slave (in slave mode), the module responds to this add | aress |  |  |  |  |  |  |  |  |

|    | lion                          | Baud rate = BUSCLK / (2 x MULT x (SCL DIVIDER))                            |       |  |  |  |  |  |  |  |  |

|    | IICC1                         | IICEN IICIE MST TX TXAK RSTA 0                                             | 0     |  |  |  |  |  |  |  |  |

|    | 1001                          | Module configuration                                                       |       |  |  |  |  |  |  |  |  |

|    | IICS                          |                                                                            | XAK   |  |  |  |  |  |  |  |  |

|    |                               | Module status flags                                                        | i     |  |  |  |  |  |  |  |  |

|    | IICD                          |                                                                            |       |  |  |  |  |  |  |  |  |

|    |                               | Data register; Write to transmit IIC data read to read IIC data            |       |  |  |  |  |  |  |  |  |

|    | IICC2                         |                                                                            | 08    |  |  |  |  |  |  |  |  |

|    |                               | Address configuration                                                      |       |  |  |  |  |  |  |  |  |

Figure 11-11. IIC Module Quick Start

MC9S08SG8 MCU Series Data Sheet, Rev. 8

#### Chapter 16 Timer Pulse-Width Modulator (S08TPMV3)

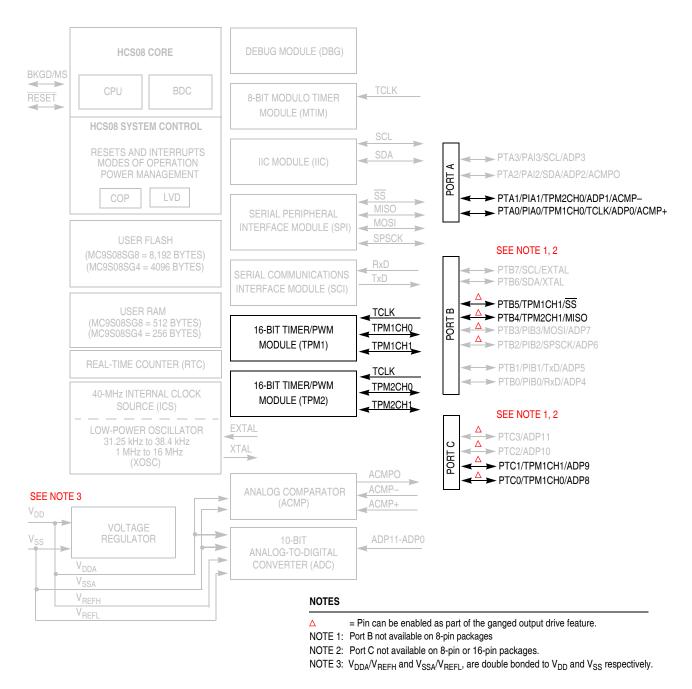

Figure 16-1. MC9S08SG8 Block Diagram with TPM Modules Highlighted

## 16.1.3 TPMV3 Differences from Previous Versions

The TPMV3 is the latest version of the Timer/PWM module that addresses errata found in previous versions. The following section outlines the differences between TPMV3 and TPMV2 modules, and any considerations that should be taken when porting code.

### Table 16-8. TPMxCnSC Field Descriptions (continued)

| Field                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>MSnA             | <ul> <li>Mode select A for TPM channel n. When CPWMS=0 and MSnB=0, MSnA configures TPM channel n for input-capture mode or output compare mode. Refer to Table 16-9 for a summary of channel mode and setup controls.</li> <li>Note: If the associated port pin is not stable for at least two bus clock cycles before changing to input capture mode, it is possible to get an unexpected indication of an edge trigger.</li> </ul>                                                                                                                                                                                                                                                                                                  |

| 3–2<br>ELSnB<br>ELSnA | Edge/level select bits. Depending upon the operating mode for the timer channel as set by CPWMS:MSnB:MSnA and shown in Table 16-9, these bits select the polarity of the input edge that triggers an input capture event, select the level that will be driven in response to an output compare match, or select the polarity of the PWM output. Setting ELSnB:ELSnA to 0:0 configures the related timer pin as a general purpose I/O pin not related to any timer functions. This function is typically used to temporarily disable an input capture channel or to make the timer pin available as a general purpose I/O pin when the associated timer channel is set up as a software timer that does not require the use of a pin. |

| CPWMS | MSnB:MSnA | ELSnB:ELSnA | Mode                  | Configuration                                       |

|-------|-----------|-------------|-----------------------|-----------------------------------------------------|

| х     | XX        | 00          |                       | TPM - revert to general<br>other peripheral control |

| 0     | 00        | 01          | Input capture         | Capture on rising edge only                         |

|       |           | 10          |                       | Capture on falling edge only                        |

|       |           | 11          |                       | Capture on rising or<br>falling edge                |

|       | 01        | 01          | Output compare        | Toggle output on<br>compare                         |

|       |           | 10          |                       | Clear output on compare                             |

|       |           | 11          |                       | Set output on compare                               |

|       | 1X        | 10          | Edge-aligned<br>PWM   | High-true pulses (clear<br>output on compare)       |

|       |           | X1          |                       | Low-true pulses (set output on compare)             |

| 1     | XX        | 10          | Center-aligned<br>PWM | High-true pulses (clear output on compare-up)       |

|       |           | X1          |                       | Low-true pulses (set output on compare-up)          |

# 16.3.5 TPM Channel Value Registers (TPMxCnVH:TPMxCnVL)

These read/write registers contain the captured TPM counter value of the input capture function or the output compare value for the output compare or PWM functions. The channel registers are cleared by reset.

| Num | с                                                              | Parameter                                                                | Symbol                   | V <sub>DD</sub><br>(V) | Typ <sup>1</sup> | Max <sup>2</sup> | Unit | Temp Rated <sup>3</sup> |                |

|-----|----------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------|------------------------|------------------|------------------|------|-------------------------|----------------|

|     |                                                                |                                                                          |                          |                        |                  |                  |      | Standard                | AEC<br>Grade 0 |

| 6   | C                                                              | C RTC adder to stop2 or stop3 <sup>7</sup>                               | S23I <sub>DDR</sub>      | 5                      | 300              | 500              | nA   | х                       |                |

| 0   | U                                                              |                                                                          | TI                       | 3                      | 300              | 500              | nA   | х                       |                |

| 7   | C LVD adder to stop3 (LVDE = LVDSE $= 1$ ) S3I <sub>DDLV</sub> |                                                                          | 631                      | 5                      | 110              | 180              | μΑ   | х                       |                |

| ,   |                                                                |                                                                          | 3                        | 90                     | 160              | μA               | х    |                         |                |

|     | с                                                              | C Adder to stop3 for oscillator<br>enabled <sup>8</sup><br>(EREFSTEN =1) | S3I <sub>DDOS</sub><br>c | 5,<br>3                | 5                |                  | _    | х                       |                |

| 8   |                                                                |                                                                          |                          |                        |                  | 8                | μA   | х                       |                |

Table A-7. Supply Current Characteristics (continued)

<sup>1</sup> Typical values are based on characterization data at 25°C. See Figure A-5 through Figure A-7 for typical curves across voltage/temperature.

<sup>2</sup> Max values in this column apply for the full operating temperature range of the device unless otherwise noted.

<sup>3</sup> Electrical characteristics only apply to the temperature rated devices marked with x.

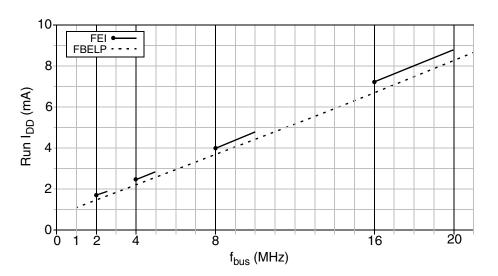

<sup>4</sup> All modules except ADC active, ICS configured for FBE, and does not include any dc loads on port pins.

<sup>5</sup> All modules except ADC active, ICS configured for FEI, and does not include any dc loads on port pins.

<sup>6</sup> Stop currents are tested in production for 25°C on all parts. Tests at other temperatures depend upon the part number suffix and maturity of the product. Freescale may eliminate a test insertion at a particular temperature from the production test flow once sufficient data has been collected and is approved.

<sup>7</sup> Most customers are expected to find that auto-wakeup from stop2 or stop3 can be used instead of the higher current wait mode.

<sup>8</sup> Values given under the following conditions: low range operation (RANGE = 0) with a 32.768kHz crystal and low power mode (HGO = 0).

Figure A-5. Typical Run  $I_{DD}$  vs. Bus Frequency ( $V_{DD} = 5V$ )

MC9S08SG8 MCU Series Data Sheet, Rev. 8

# A.10 Analog Comparator (ACMP) Electricals

|     | с | Rating                                    | Symbol             | Min              | Тур | Max             | Unit | Temp Rated <sup>1</sup> |                |

|-----|---|-------------------------------------------|--------------------|------------------|-----|-----------------|------|-------------------------|----------------|

| Num |   |                                           |                    |                  |     |                 |      | Standard                | AEC Grade<br>0 |

| 1   | — | Supply voltage                            | $V_{DD}$           | 2.7              | _   | 5.5             | V    | х                       | х              |

| 2   | D | Supply current (active)                   | I <sub>DDAC</sub>  | —                | 20  | 35              | μA   | х                       | х              |

| 3   | D | Analog input voltage                      | V <sub>AIN</sub>   | $V_{\rm SS}-0.3$ |     | V <sub>DD</sub> | V    | х                       | х              |

| 4   | D | Analog input offset voltage               | V <sub>AIO</sub>   |                  | 20  | 40              | mV   | х                       | х              |

| 5   | D | Analog Comparator hysteresis              | V <sub>H</sub>     | 3.0              | 6.0 | 20.0            | mV   | х                       | x              |

| 6   | D | Analog input leakage current              | I <sub>ALKG</sub>  | —                |     | 1.0             | μA   | х                       | х              |

| 7   | D | Analog Comparator<br>initialization delay | t <sub>AINIT</sub> | —                | _   | 1.0             | μS   | х                       | x              |

Table A-10. Analog Comparator Electrical Specifications

<sup>1</sup> Electrical characteristics only apply to the temperature rated devices marked with x.

|                                                |                                              |          | Symb                    | Min | Typ <sup>1</sup> | Max  | Unit               | Temp Rated <sup>2</sup> |                   |                                           |  |

|------------------------------------------------|----------------------------------------------|----------|-------------------------|-----|------------------|------|--------------------|-------------------------|-------------------|-------------------------------------------|--|

| Characteristic                                 | Conditions                                   | С        |                         |     |                  |      |                    | Stand<br>ard            | AEC<br>Grade<br>0 | Comment                                   |  |

| Conversion                                     | Short sample<br>(ADLSMP=0)                   | D        |                         | _   | 20               | _    | ADCK               | х                       | х                 |                                           |  |

| time (including sample time)                   | Long sample<br>(ADLSMP=1)                    |          | t <sub>ADC</sub>        | _   | 40               | _    | cycles             | х                       | х                 | See ADC<br>Chapter<br>for                 |  |

| Sample time                                    | Short sample<br>(ADLSMP=0)                   | D        | +                       | _   | 3.5              | _    | ADCK               | х                       | х                 | conversion<br>time<br>variances           |  |

| Sample line                                    | Long sample<br>(ADLSMP=1)                    |          | t <sub>ADS</sub>        | _   | 23.5             | _    | cycles             | х                       | х                 | variances                                 |  |

| Total                                          | 10 bit mode                                  |          |                         | _   | ±1.5             | ±3.5 | LSB <sup>2</sup>   | х                       | х                 |                                           |  |

| unadjusted<br>error (Includes<br>quantization) | 8 bit mode                                   | Р        | E <sub>TUE</sub>        | _   | ±0.7             | ±1.5 | LSB <sup>3</sup>   | х                       | x                 |                                           |  |

|                                                | 10 bit mode                                  |          | DNL                     | _   | ±0.5             | ±1.0 | LSB <sup>3</sup>   | х                       | х                 |                                           |  |

| Differential<br>Non-Linearity                  | 8 bit mode                                   | - P      |                         | _   | ±0.3             | ±0.5 |                    | х                       | х                 |                                           |  |

|                                                | Monotonicity and No-Missing-Codes guaranteed |          |                         |     |                  |      |                    |                         |                   |                                           |  |

| Integral                                       | 10 bit mode                                  | -        | INL                     |     | ±0.5             | ±1.0 | LSB <sup>3</sup>   | х                       | х                 |                                           |  |

| non-linearity                                  | 8 bit mode                                   | — Т      |                         | _   | ±0.3             | ±0.5 |                    | х                       | х                 |                                           |  |

| Zero-scale                                     | 10 bit mode                                  | — Р      | E <sub>ZS</sub>         | _   | ±1.5             | ±2.5 | LSB <sup>3</sup>   | х                       | х                 |                                           |  |

| error                                          | 8 bit mode                                   |          |                         | _   | ±0.5             | ±0.7 |                    | х                       | х                 |                                           |  |

| Full-scale error                               | 10 bit mode                                  | _ т      | -                       | 0   | ±1.0             | ±1.5 | LSB <sup>3</sup>   | х                       | х                 |                                           |  |

| $(V_{ADIN} = V_{DD})$                          | 8 bit mode                                   |          | E <sub>FS</sub>         | 0   | ±0.5             | ±0.5 | LSB                | х                       | х                 |                                           |  |

| Quantization                                   | 10 bit mode                                  | D        | Е                       | —   | —                | ±0.5 | - LSB <sup>3</sup> | х                       | х                 |                                           |  |

| error                                          | 8 bit mode                                   |          | EQ                      | —   | —                | ±0.5 |                    | х                       | х                 |                                           |  |

| Input leakage                                  | 10 bit mode                                  |          |                         | 0   | ±0.2             | ±2.5 | LSB <sup>3</sup>   | х                       | х                 | Pad                                       |  |

| error                                          | 8 bit mode                                   | D        | E <sub>IL</sub>         | 0   | ±0.1             | ±1   |                    | х                       | х                 | leakage <sup>3</sup> *<br>R <sub>AS</sub> |  |

| Temp sensor                                    | –40°C to 25°C                                | <u> </u> |                         | _   | 3.266            | _    | m\//00             | х                       | х                 |                                           |  |

| slope                                          | 25°C to 125°C                                | — D      | m                       |     | 3.638            | —    | mV/°C —            | х                       | х                 |                                           |  |

| Temp sensor<br>voltage                         | 25°C                                         | D        | V <sub>TEMP</sub><br>25 | _   | 1.396            | _    | V                  | х                       | х                 |                                           |  |

### Table A-12. ADC Characteristics (continued)

<sup>1</sup> Typical values assume V<sub>DD</sub> = 5.0 V, Temp = 25°C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

<sup>2</sup> Electrical characteristics only apply to the temperature rated devices marked with x.

<sup>3</sup> Based on input pad leakage current. Refer to pad electricals.