Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFI

| Product Status          | Active                                                                |

|-------------------------|-----------------------------------------------------------------------|

| Туре                    | Floating Point                                                        |

| Interface               | DAI, DPI                                                              |

| Clock Rate              | 350MHz                                                                |

| Non-Volatile Memory     | ROM (768kB)                                                           |

| On-Chip RAM             | 256kB                                                                 |

| Voltage - I/O           | 3.30V                                                                 |

| Voltage - Core          | 1.20V                                                                 |

| Operating Temperature   | 0°C ~ 70°C (TA)                                                       |

| Mounting Type           | Surface Mount                                                         |

| Package / Case          | 208-LQFP Exposed Pad                                                  |

| Supplier Device Package | 208-LQFP-EP (28x28)                                                   |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-21369kswz-4a |

|                         |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The block diagram of the ADSP-21368 on Page 1 also shows the peripheral clock domain (also known as the I/O processor) and contains the following features:

- IOD0 (peripheral DMA) and IOD1 (external port DMA) buses for 32-bit data transfers

- Peripheral and external port buses for core connection

- External port with an AMI and SDRAM controller

- 4 units for PWM control

- 1 MTM unit for internal-to-internal memory transfers

- Digital applications interface that includes four precision clock generators (PCG), a input data port (IDP) for serial and parallel interconnect, an S/PDIF receiver/transmitter, four asynchronous sample rate converters, eight serial ports, a flexible signal routing unit (DAI SRU).

• Digital peripheral interface that includes three timers, a 2wire interface, two UARTs, two serial peripheral interfaces (SPI), 2 precision clock generators (PCG) and a flexible signal routing unit (DPI SRU).

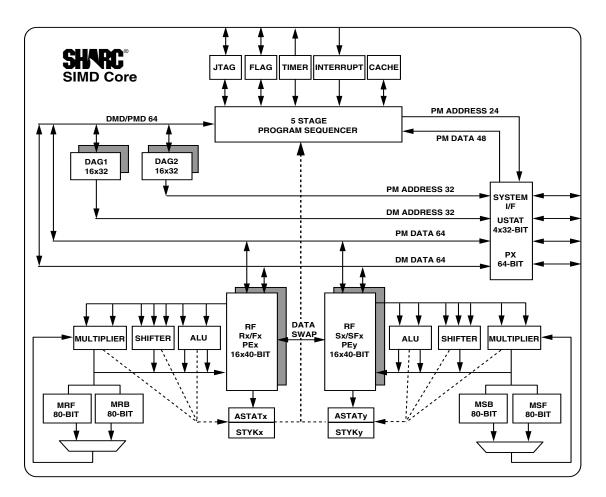

#### SHARC FAMILY CORE ARCHITECTURE

The ADSP-21367/ADSP-21368/ADSP-21369 are code compatible at the assembly level with the ADSP-2126x, ADSP-21160, and ADSP-21161, and with the first generation ADSP-2106x SHARC processors. The ADSP-21367/ADSP-21368/ ADSP-21369 processors share architectural features with the ADSP-2126x and ADSP-2116x SIMD SHARC processors, as shown in Figure 2 and detailed in the following sections.

Figure 2. SHARC Core Block Diagram

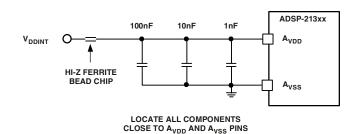

Figure 3. Analog Power (A<sub>VDD</sub>) Filter Circuit

#### Target Board JTAG Emulator Connector

Analog Devices DSP Tools product line of JTAG emulators uses the IEEE 1149.1 JTAG test access port of the ADSP-21367/ ADSP-21368/ADSP-21369 processors to monitor and control the target board processor during emulation. Analog Devices DSP Tools product line of JTAG emulators provides emulation at full processor speed, allowing inspection and modification of memory, registers, and processor stacks. The processor's JTAG interface ensures that the emulator will not affect target system loading or timing.

For complete information on Analog Devices' SHARC DSP Tools product line of JTAG emulator operation, see the appropriate "Emulator Hardware User's Guide."

#### **DEVELOPMENT TOOLS**

Analog Devices supports its processors with a complete line of software and hardware development tools, including integrated development environments (which include CrossCore<sup>®</sup> Embedded Studio and/or VisualDSP++<sup>®</sup>), evaluation products, emulators, and a wide variety of software add-ins.

#### Integrated Development Environments (IDEs)

For C/C++ software writing and editing, code generation, and debug support, Analog Devices offers two IDEs.

The newest IDE, CrossCore Embedded Studio, is based on the Eclipse<sup>™</sup> framework. Supporting most Analog Devices processor families, it is the IDE of choice for future processors, including multicore devices. CrossCore Embedded Studio seamlessly integrates available software add-ins to support real time operating systems, file systems, TCP/IP stacks, USB stacks, algorithmic software modules, and evaluation hardware board support packages. For more information visit www.analog.com/cces.

The other Analog Devices IDE, VisualDSP++, supports processor families introduced prior to the release of CrossCore Embedded Studio. This IDE includes the Analog Devices VDK real time operating system and an open source TCP/IP stack. For more information visit www.analog.com/visualdsp. Note that VisualDSP++ will not support future Analog Devices processors.

#### EZ-KIT Lite Evaluation Board

For processor evaluation, Analog Devices provides wide range of EZ-KIT Lite<sup>®</sup> evaluation boards. Including the processor and key peripherals, the evaluation board also supports on-chip emulation capabilities and other evaluation and development features. Also available are various EZ-Extenders<sup>®</sup>, which are daughter cards delivering additional specialized functionality, including audio and video processing. For more information visit www.analog.com and search on "ezkit" or "ezextender".

#### **EZ-KIT Lite Evaluation Kits**

For a cost-effective way to learn more about developing with Analog Devices processors, Analog Devices offer a range of EZ-KIT Lite evaluation kits. Each evaluation kit includes an EZ-KIT Lite evaluation board, directions for downloading an evaluation version of the available IDE(s), a USB cable, and a power supply. The USB controller on the EZ-KIT Lite board connects to the USB port of the user's PC, enabling the chosen IDE evaluation suite to emulate the on-board processor in-circuit. This permits the customer to download, execute, and debug programs for the EZ-KIT Lite system. It also supports in-circuit programming of the on-board Flash device to store user-specific boot code, enabling standalone operation. With the full version of Cross-Core Embedded Studio or VisualDSP++ installed (sold separately), engineers can develop software for supported EZ-KITs or any custom system utilizing supported Analog Devices processors.

#### Software Add-Ins for CrossCore Embedded Studio

Analog Devices offers software add-ins which seamlessly integrate with CrossCore Embedded Studio to extend its capabilities and reduce development time. Add-ins include board support packages for evaluation hardware, various middleware packages, and algorithmic modules. Documentation, help, configuration dialogs, and coding examples present in these add-ins are viewable through the CrossCore Embedded Studio IDE once the add-in is installed.

#### **Board Support Packages for Evaluation Hardware**

Software support for the EZ-KIT Lite evaluation boards and EZ-Extender daughter cards is provided by software add-ins called Board Support Packages (BSPs). The BSPs contain the required drivers, pertinent release notes, and select example code for the given evaluation hardware. A download link for a specific BSP is located on the web page for the associated EZ-KIT or EZ-Extender product. The link is found in the *Product Download* area of the product web page.

#### **Middleware Packages**

Analog Devices separately offers middleware add-ins such as real time operating systems, file systems, USB stacks, and TCP/IP stacks. For more information see the following web pages:

- www.analog.com/ucos3

- www.analog.com/ucfs

- www.analog.com/ucusbd

- www.analog.com/lwip

#### **Algorithmic Modules**

To speed development, Analog Devices offers add-ins that perform popular audio and video processing algorithms. These are available for use with both CrossCore Embedded Studio and VisualDSP++. For more information visit www.analog.com and search on "Blackfin software modules" or "SHARC software modules".

#### Designing an Emulator-Compatible DSP Board (Target)

For embedded system test and debug, Analog Devices provides a family of emulators. On each JTAG DSP, Analog Devices supplies an IEEE 1149.1 JTAG Test Access Port (TAP). In-circuit emulation is facilitated by use of this JTAG interface. The emulator accesses the processor's internal features via the processor's TAP, allowing the developer to load code, set breakpoints, and view variables, memory, and registers. The processor must be halted to send data and commands, but once an operation is completed by the emulator, the DSP system is set to run at full speed with no impact on system timing. The emulators require the target board to include a header that supports connection of the DSP's JTAG port to the emulator.

For details on target board design issues including mechanical layout, single processor connections, signal buffering, signal termination, and emulator pod logic, see the Engineer-to-Engineer Note "*Analog Devices JTAG Emulation Technical Reference*" (EE-68) on the Analog Devices website (www.analog.com)—use site search on "EE-68." This document is updated regularly to keep pace with improvements to emulator support.

#### **ADDITIONAL INFORMATION**

This data sheet provides a general overview of the ADSP-21367/ADSP-21368/ADSP-21369 architecture and functionality. For detailed information on the ADSP-2136x family core architecture and instruction set, refer to the *ADSP-21368 SHARC Processor Hardware Reference* and the *SHARC Processor Programming Reference*.

#### **RELATED SIGNAL CHAINS**

A *signal chain* is a series of signal conditioning electronic components that receive input (data acquired from sampling either real-time phenomena or from stored data) in tandem, with the output of one portion of the chain supplying input to the next. Signal chains are often used in signal processing applications to gather and process data or to apply system controls based on analysis of real-time phenomena. For more information about this term and related topics, see the "signal chain" entry in the Glossary of EE Terms on the Analog Devices website.

Analog Devices eases signal processing system development by providing signal processing components that are designed to work together well. A tool for viewing relationships between specific applications and related components is available on the www.analog.com website.

The Circuits from the Lab<sup>™</sup> site (www.analog.com/signal chains) provides:

- Graphical circuit block diagram presentation of signal chains for a variety of circuit types and applications

- Drill down links for components in each chain to selection guides and application information

- Reference designs applying best practice design techniques

### **PIN FUNCTION DESCRIPTIONS**

The following symbols appear in the Type column of Table 8: A = asynchronous, G = ground, I = input, O = output, O/T = output three-state, P = power supply, S = synchronous, (A/D) = active drive, (O/D) = open-drain, (pd) = pull-down resistor, (pu) = pull-up resistor. The ADSP-21367/ADSP-21368/ADSP-21369 SHARC processors use extensive pin multiplexing to achieve a lower pin count. For complete information on the multiplexing scheme, see the *ADSP-21368 SHARC Processor Hardware Reference*, "System Design" chapter.

#### Table 8. Pin Descriptions

| Name                                            | Туре                                           | State During/<br>After Reset<br>(ID = 00x) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------|------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR <sub>23-0</sub>                            | O/T (pu) <sup>1</sup>                          | Pulled high/<br>driven low                 | <b>External Address.</b> The processors output addresses for external memory and peripherals on these pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DATA <sub>31-0</sub>                            | I/O (pu) <sup>1</sup>                          | Pulled high/<br>pulled high                | <b>External Data.</b> Data pins can be multiplexed to support external memory interface data (I/O), the PDAP (I), FLAGS (I/O), and PWM (O). After reset, all DATA pins are in EMIF mode and FLAG(0-3) pins are in FLAGS mode (default). When configured using the IDP_P-DAP_CTL register, IDP Channel 0 scans the external port data pins for parallel input data.                                                                                                                                                                                                                                                            |

| АСК                                             | l (pu) <sup>1</sup>                            |                                            | <b>Memory Acknowledge.</b> External devices can deassert ACK (low) to add wait states to an external memory access. ACK is used by I/O devices, memory controllers, or other peripherals to hold off completion of an external memory access.                                                                                                                                                                                                                                                                                                                                                                                 |

| MS <sub>0−1</sub>                               | O/T (pu) <sup>1</sup>                          | Pulled high/<br>driven high                | <b>Memory Select Lines 0–1.</b> These lines are asserted (low) as chip selects for the corresponding banks of external memory. The $\overline{\text{MS}}_{3-0}$ lines are decoded memory address lines that change at the same time as the other address lines. When no external memory access is occurring, the $\overline{\text{MS}}_{3-0}$ lines are inactive; they are active, however, when a conditional memory access instruction is executed, whether or not the condition is true. The $\overline{\text{MS}}_1$ pin can be used in EPORT/FLASH boot mode. See the processor hardware reference for more information. |

| RD                                              | O/T (pu) <sup>1</sup>                          | Pulled high/<br>driven high                | <b>External Port Read Enable.</b> RD is asserted whenever the processors read a word from external memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| WR                                              | O/T (pu) <sup>1</sup>                          | Pulled high/<br>driven high                | <b>External Port Write Enable.</b> $\overline{\text{WR}}$ is asserted when the processors write a word to external memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| FLAG[0]/IRQ0                                    | I/O                                            | FLAG[0] INPUT                              | FLAG0/Interrupt Request 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| FLAG[1]/IRQ1                                    | I/O                                            | FLAG[1] INPUT                              | FLAG1/Interrupt Request 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| FLAG[2]/ <mark>IRQ2</mark> /<br>MS <sub>2</sub> | I/O with pro-<br>grammable pu<br>(for MS mode) | FLAG[2] INPUT                              | FLAG2/Interrupt Request 2/Memory Select 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| FLAG[3]/<br>TMREXP/MS <sub>3</sub>              | I/O with pro-<br>grammablepu<br>(for MS mode)  | FLAG[3] INPUT                              | FLAG3/Timer Expired/Memory Select 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### Table 8. Pin Descriptions (Continued)

| Name                   | Туре                                          | State During/<br>After Reset<br>(ID = 00x) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------|-----------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDRAS                  | O/T (pu) <sup>1</sup>                         | Pulled high/<br>driven high                | <b>SDRAM Row Address Strobe.</b> Connect to SDRAM's RAS pin. In conjunction with other SDRAM command pins, defines the operation for the SDRAM to perform.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SDCAS                  | O/T (pu) <sup>1</sup>                         | Pulled high/<br>driven high                | <b>SDRAM Column Address Select.</b> Connect to SDRAM's CAS pin. In conjunction with other SDRAM command pins, defines the operation for the SDRAM to perform.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SDWE                   | O/T (pu) <sup>1</sup>                         | Pulled high/<br>driven high                | SDRAM Write Enable. Connect to SDRAM's WE or W buffer pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SDCKE                  | O/T (pu) <sup>1</sup>                         | Pulled high/<br>driven high                | <b>SDRAM Clock Enable.</b> Connect to SDRAM's CKE pin. Enables and disables the CLK signal. For details, see the data sheet supplied with the SDRAM device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SDA10                  | O/T (pu) <sup>1</sup>                         | Pulled high/<br>driven low                 | <b>SDRAM A10 Pin.</b> Enables applications to refresh an SDRAM in parallel with non-SDRAM accesses. This pin replaces the DSP's A10 pin only during SDRAM accesses.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SDCLK0                 | 0/Т                                           | High-Z/driving                             | <b>SDRAM Clock Output 0.</b> Clock driver for this pin differs from all other clock drivers. See Figure 40 on Page 51.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SDCLK1                 | 0/Т                                           |                                            | <b>SDRAM Clock Output 1.</b> Additional clock for SDRAM devices. For systems with multiple SDRAM devices, handles the increased clock load requirements, eliminating need of off-<br>chip clock buffers. Either SDCLK1 or both SDCLKx pins can be three-stated. Clock driver for this pin differs from all other clock drivers. See Figure 40 on Page 51.<br>The SDCLK1 signal is only available on the SBGA package. SDCLK1 is not available on the LQFP_EP package.                                                                                                                                                                                                                                                                                                                                                  |

| DAI_P <sub>20-1</sub>  | I/O with pro-<br>grammable<br>pu <sup>2</sup> | Pulled high/<br>pulled high                | <b>Digital Applications Interface</b> . These pins provide the physical interface to the DAI SRU.<br>The DAI SRU configuration registers define the combination of on-chip audiocentric<br>peripheral inputs or outputs connected to the pin, and to the pin's output enable. The<br>configuration registers then determines the exact behavior of the pin. Any input or<br>output signal present in the DAI SRU may be routed to any of these pins. The DAI SRU<br>provides the connection from the serial ports (8), the SRC module, the S/PDIF module,<br>input data ports (2), and the precision clock generators (4), to the DAI_P20–1 pins. Pull-<br>ups can be disabled via the DAI_PIN_PULLUP register.                                                                                                        |

| DPI _P <sub>14-1</sub> | l/O with pro-<br>grammable<br>pu <sup>2</sup> | Pulled high/<br>pulled high                | <b>Digital Peripheral Interface.</b> These pins provide the physical interface to the DPI SRU.<br>The DPI SRU configuration registers define the combination of on-chip peripheral inputs<br>or outputs connected to the pin and to the pin's output enable. The configuration<br>registers of these peripherals then determines the exact behavior of the pin. Any input<br>or output signal present in the DPI SRU may be routed to any of these pins. The DPI SRU<br>provides the connection from the timers (3), SPIs (2), UARTs (2), flags (12) TWI (1), and<br>general-purpose I/O (9) to the DPI_P14–1 pins. The TWI output is an open-drain output—<br>so the pins used for I <sup>2</sup> C data and clock should be connected to logic level 0. Pull-ups can<br>be disabled via the DPI_PIN_PULLUP register. |

| TDI                    | l (pu)                                        |                                            | Test Data Input (JTAG). Provides serial data for the boundary scan logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TDO                    | O/T                                           |                                            | Test Data Output (JTAG). Serial scan output of the boundary scan path.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TMS                    | l (pu)                                        |                                            | Test Mode Select (JTAG). Used to control the test state machine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ТСК                    | 1                                             |                                            | <b>Test Clock (JTAG).</b> Provides a clock for JTAG boundary scan. TCK must be asserted (pulsed low) after power-up, or held low for proper operation of the processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TRST                   | l (pu)                                        |                                            | <b>Test Reset (JTAG).</b> Resets the test state machine. TRST must be asserted (pulsed low) after power-up or held low for proper operation of the processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

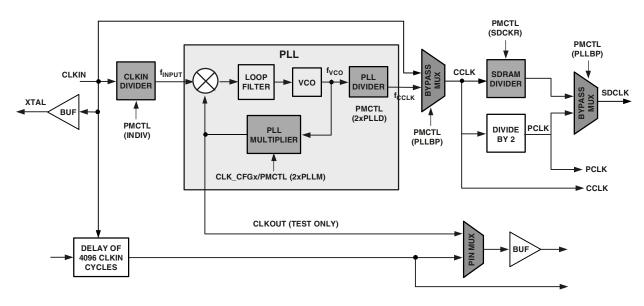

• The product of CLKIN and PLLM must never exceed  $f_{VCO}$  (max) in Table 13 if the input divider is enabled (INDIV = 1).

The VCO frequency is calculated as follows:

$f_{VCO} = 2 \times PLLM \times f_{INPUT}$  $f_{CCLK} = (2 \times PLLM \times f_{INPUT}) \div (2 \times PLLD)$ where:

$f_{VCO} = VCO$  output

*PLLM* = Multiplier value programmed in the PMCTL register. During reset, the PLLM value is derived from the ratio selected using the CLK\_CFG pins in hardware.

*PLLD* = Divider value 1, 2, 4, or 8 based on the PLLD value programmed on the PMCTL register. During reset this value is 1.

$f_{INPUT}$  = Input frequency to the PLL.

$f_{INPUT}$  = CLKIN when the input divider is disabled or

$f_{INPUT}$  = CLKIN ÷ 2 when the input divider is enabled

Note the definitions of the clock periods that are a function of CLKIN and the appropriate ratio control shown in and Table 11. All of the timing specifications for the ADSP-2136x peripherals are defined in relation to t<sub>PCLK</sub>. See the peripheral specific timing section for each peripheral's timing information.

Table 11. Clock Periods

| Timing<br>Requirements | Description                                   |

|------------------------|-----------------------------------------------|

| t <sub>ck</sub>        | CLKIN Clock Period                            |

| t <sub>cclk</sub>      | Processor Core Clock Period                   |

| t <sub>PCLK</sub>      | Peripheral Clock Period = $2 \times t_{CCLK}$ |

Figure 5 shows core to CLKIN relationships with external oscillator or crystal. The shaded divider/multiplier blocks denote where clock ratios can be set through hardware or software using the power management control register (PMCTL). For more information, see the processor hardware reference.

Figure 5. Core Clock and System Clock Relationship to CLKIN

#### **Clock Signals**

The processors can use an external clock or a crystal. See the CLKIN pin description in Table 8 on Page 13. Programs can configure the processor to use its internal clock generator by connecting the necessary components to CLKIN and XTAL. Figure 8 shows the component connections used for a crystal operating in fundamental mode.

Note that the clock rate is achieved using a 25 MHz crystal and a PLL multiplier ratio 16:1 (CCLK:CLKIN achieves a clock speed of 400 MHz). To achieve the full core clock rate, programs need to configure the multiplier bits in the PMCTL register.

R2 SHOULD BE CHOSEN TO LIMIT CRYSTAL DRIVE POWER. REFER TO CRYSTAL MANUFACTURER'S SPECIFICATIONS

Figure 8. 400 MHz Operation (Fundamental Mode Crystal)

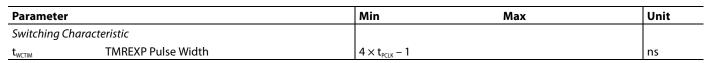

#### **Core Timer**

The following timing specification applies to FLAG3 when it is configured as the core timer (TMREXP).

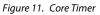

#### Table 16. Core Timer

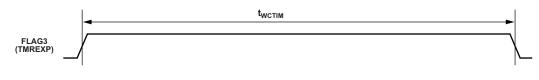

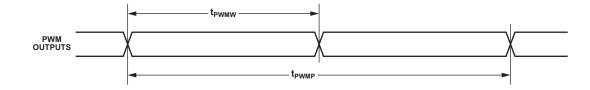

#### Timer PWM\_OUT Cycle Timing

The following timing specification applies to Timer0, Timer1, and Timer2 in PWM\_OUT (pulse-width modulation) mode. Timer signals are routed to the DPI\_P14-1 pins through the DPI SRU. Therefore, the timing specifications provided below are valid at the DPI\_P14-1 pins.

#### Table 17. Timer PWM\_OUT Timing

| Paramete                 | er                       | Min                       | Мах                                     | Unit |

|--------------------------|--------------------------|---------------------------|-----------------------------------------|------|

| Switching Characteristic |                          |                           |                                         |      |

| t <sub>PWMO</sub>        | Timer Pulse Width Output | $2 \times t_{PCLK} - 1.2$ | $2 \times (2^{31} - 1) \times t_{PCLK}$ | ns   |

Figure 12. Timer PWM\_OUT Timing

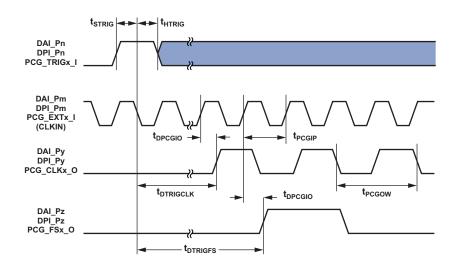

#### Precision Clock Generator (Direct Pin Routing)

This timing is only valid when the SRU is configured such that the precision clock generator (PCG) takes its inputs directly from the DAI pins (via pin buffers) and sends its outputs directly to the DAI pins. For the other cases, where the PCG's inputs and outputs are not directly routed to/from DAI pins (via pin buffers) there is no timing data available. All timing parameters and switching characteristics apply to external DAI pins (DAI\_P01-20).

#### Table 20. Precision Clock Generator (Direct Pin Routing)

| Parameter          |                                                                            | Min                                       | Мах                                      | Unit   |

|--------------------|----------------------------------------------------------------------------|-------------------------------------------|------------------------------------------|--------|

| Timing Re          | equirements                                                                |                                           |                                          |        |

| t <sub>PCGIP</sub> | Input Clock Period                                                         | $t_{\text{PCLK}} \times 4$                |                                          | ns     |

| STRIG              | PCG Trigger Setup Before Falling<br>Edge of PCG Input Clock                | 4.5                                       |                                          | ns     |

| HTRIG              | PCG Trigger Hold After Falling<br>Edge of PCG Input Clock                  | 3                                         |                                          | ns     |

| Switching          | Characteristics                                                            |                                           |                                          |        |

| DPCGIO             | PCG Output Clock and Frame Sync Active Edge<br>Delay After PCG Input Clock | 2.5                                       | 10                                       | ns     |

| DTRIGCLK           | PCG Output Clock Delay After PCG Trigger                                   | $2.5 + (2.5 \times t_{PCGIP})$            | $10 + (2.5 \times t_{PCGIP})$            | ns     |

| DTRIGFS            | PCG Frame Sync Delay After PCG Trigger                                     | $2.5 + ((2.5 + D - PH) \times t_{PCGIP})$ | $10 + ((2.5 + D - PH) \times t_{PCGIP})$ | ns     |

| 1<br>PCGOW         | Output Clock Period                                                        | $2 \times t_{PCGIP} - 1$                  |                                          | ns     |

| D = FSxD           | IV, and PH = FSxPHASE. For more information, see the                       | processor hardware reference, "           | Precision Clock Generators" cha          | apter. |

<sup>1</sup> In normal mode.

Figure 15. Precision Clock Generator (Direct Pin Routing)

#### **Memory Read**

Use these specifications for asynchronous interfacing to memories. These specifications apply when the processors are the bus master accessing external memory space in asynchronous access mode. Note that timing for ACK, DATA, RD, WR, and strobe timing parameters only apply to asynchronous access mode.

#### Table 24. Memory Read

| Paramete          | r                                                     | Min                      | Мах                          | Unit |

|-------------------|-------------------------------------------------------|--------------------------|------------------------------|------|

| Timing Req        | uirements                                             |                          |                              |      |

| t <sub>DAD</sub>  | Address, Selects Delay to Data Valid <sup>1, 2</sup>  |                          | $W + t_{SDCLK} - 5.12$       | ns   |

| t <sub>DRLD</sub> | $\overline{\text{RD}}$ Low to Data Valid <sup>2</sup> |                          | W – 3.2                      | ns   |

| t <sub>sDs</sub>  | Data Setup to RD High                                 | 2.5                      |                              | ns   |

| t <sub>HDRH</sub> | Data Hold from RD High <sup>3, 4</sup>                | 0                        |                              | ns   |

| t <sub>daak</sub> | ACK Delay from Address, Selects <sup>1, 5</sup>       |                          | $t_{\text{SDCLK}} - 9.5 + W$ | ns   |

| DSAK              | ACK Delay from RD Low <sup>5</sup>                    |                          | W – 7.0                      | ns   |

| witching (        | Characteristics                                       |                          |                              |      |

| DRHA              | Address Selects Hold After RD High                    | RH + 0.20                |                              | ns   |

| DARL              | Address Selects to RD Low <sup>1</sup>                | t <sub>sDCLK</sub> - 3.3 |                              | ns   |

| t <sub>rw</sub>   | RD Pulse Width                                        | W – 1.4                  |                              | ns   |

| RWR               | RD High to WR, RD Low                                 | $HI + t_{SDCLK} - 0.8$   |                              | ns   |

W = (number of wait states specified in AMICTLx register)  $\times$  t<sub>SDCLK</sub>.

HI =RHC + IC (RHC = number of read hold cycles specified in AMICTLx register)  $\times$  t<sub>SDCLK</sub>.

IC = (number of idle cycles specified in AMICTLx register)  $\times$  t<sub>SDCLK</sub>.

H = (number of hold cycles specified in AMICTLx register)  $\times$  t<sub>SDCLK</sub>.

<sup>1</sup> The falling edge of  $\overline{\text{MS}}x$  is referenced.

$^{2}$  The maximum limit of timing requirement values for t<sub>DAD</sub> and t<sub>DRLD</sub> parameters are applicable for the case where AMI\_ACK is always high and when the ACK feature is not used.  $^{3}$  Note that timing for ACK, DATA,  $\overline{RD}$ ,  $\overline{WR}$ , and strobe timing parameters only apply to asynchronous access mode.

<sup>4</sup>Data hold: User must meet t<sub>HDA</sub> or t<sub>HDRH</sub> in asynchronous access mode. See Test Conditions on Page 51 for the calculation of hold times given capacitive and dc loads.

<sup>5</sup> ACK delay/setup: User must meet t<sub>DAAK</sub>, or t<sub>DSAK</sub>, for deassertion of ACK (low). For asynchronous assertion of ACK (high), user must meet t<sub>DAAK</sub> or t<sub>DSAK</sub>.

#### **Serial Ports**

To determine whether communication is possible between two devices at clock speed n, the following specifications must be confirmed: 1) frame sync delay and frame sync setup and hold, 2) data delay and data setup and hold, and 3) SCLK width. Serial port signals SCLK, frame sync (FS), data channel A, data channel B are routed to the DAI\_P20-1 pins using the SRU. Therefore, the timing specifications provided below are valid at the DAI\_P20-1 pins.

#### Table 28. Serial Ports-External Clock

|                                |                                                                                         | 400 MH<br>366 MH<br>350 MH            | İz    | 333 MH                                | 17    | 266 MH                                | 7     |      |

|--------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------|-------|---------------------------------------|-------|---------------------------------------|-------|------|

| Parame                         | eter                                                                                    | Min                                   | Max   | Min                                   | Max   | Min                                   | Max   | Unit |

| Timing F                       | Requirements                                                                            |                                       |       |                                       |       |                                       |       |      |

| t <sub>sfse</sub> 1            | FS Setup Before SCLK<br>(Externally Generated FS in Either<br>Transmit or Receive Mode) | 2.5                                   |       | 2.5                                   |       | 2.5                                   |       | ns   |

| t <sub>HFSE</sub> <sup>1</sup> | FS Hold After SCLK<br>(Externally Generated FS in Either<br>Transmit or Receive Mode)   | 2.5                                   |       | 2.5                                   |       | 2.5                                   |       | ns   |

| t <sub>sDRE</sub> <sup>1</sup> | Receive Data Setup Before Receive<br>SCLK                                               | 1.9                                   |       | 2.0                                   |       | 2.5                                   |       | ns   |

| $t_{HDRE}^{1}$                 | Receive Data Hold After SCLK                                                            | 2.5                                   |       | 2.5                                   |       | 2.5                                   |       | ns   |

| t <sub>sclkw</sub>             | SCLK Width                                                                              | $(t_{_{PCLK}} \times 4) \div 2 - 0.5$ |       | $(t_{_{PCLK}} \times 4) \div 2 - 0.5$ | 5     | $(t_{_{PCLK}} \times 4) \div 2 - 0.5$ | 5     | ns   |

| t <sub>sclk</sub>              | SCLK Period                                                                             | $t_{\text{PCLK}} \times 4$            |       | $t_{\text{PCLK}} \times 4$            |       | $t_{\text{PCLK}} \times 4$            |       | ns   |

| Switchir                       | ng Characteristics                                                                      |                                       |       |                                       |       |                                       |       |      |

| $t_{\text{DFSE}}^{2}$          | FS Delay After SCLK<br>(Internally Generated FS in Either<br>Transmit or Receive Mode)  |                                       | 10.25 |                                       | 10.25 |                                       | 10.25 | ns   |

| ${\sf t}_{\sf HOFSE}^2$        | FS Hold After SCLK<br>(Internally Generated FS in Either<br>Transmit or Receive Mode)   | 2                                     |       | 2                                     |       | 2                                     |       | ns   |

| $t_{\text{DDTE}}^{2}$          | Transmit Data Delay After Transmit<br>SCLK                                              |                                       | 7.8   |                                       | 9.6   |                                       | 9.8   | ns   |

| $t_{\text{HDTE}}^{2}$          | Transmit Data Hold After Transmit<br>SCLK                                               | 2                                     |       | 2                                     |       | 2                                     |       | ns   |

<sup>1</sup>Referenced to sample edge.

<sup>2</sup> Referenced to drive edge.

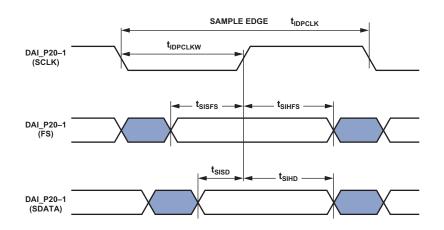

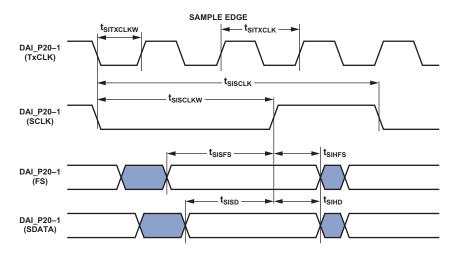

#### Input Data Port

The timing requirements for the IDP are given in Table 32. IDP signals SCLK, frame sync (FS), and SDATA are routed to the DAI\_P20-1 pins using the SRU. Therefore, the timing specifications provided below are valid at the DAI\_P20-1 pins.

#### Table 32. IDP

| Paramete             | r                                   | Min                                                     | Max Unit |

|----------------------|-------------------------------------|---------------------------------------------------------|----------|

| Timing Req           | uirements                           |                                                         |          |

| t <sub>sisfs</sub> 1 | FS Setup Before SCLK Rising Edge    | 4                                                       | ns       |

| t <sub>sihfs</sub> 1 | FS Hold After SCLK Rising Edge      | 2.5                                                     | ns       |

| t <sub>sisp</sub> 1  | SDATA Setup Before SCLK Rising Edge | 2.5                                                     | ns       |

| SIHD 1               | SDATA Hold After SCLK Rising Edge   | 2.5                                                     | ns       |

| t <sub>IDPCLKW</sub> | Clock Width                         | $(t_{PCLK} \times 4) \div 2 - 1$                        | ns       |

| t <sub>idpclk</sub>  | Clock Period                        | $(t_{PCLK} \times 4) \div 2 - 1$<br>$t_{PCLK} \times 4$ | ns       |

<sup>1</sup> DATA, SCLK, FS can come from any of the DAI pins. SCLK and FS can also come via PCG or SPORTs. PCG's input can be either CLKIN or any of the DAI pins.

Figure 26. IDP Master Timing

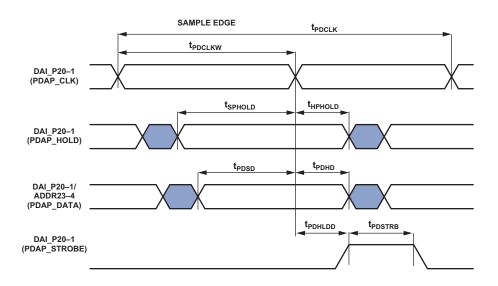

#### Parallel Data Acquisition Port (PDAP)

The timing requirements for the PDAP are provided in Table 33. PDAP is the parallel mode operation of Channel 0 of the IDP. For details on the operation of the IDP, see the IDP chapter of the *ADSP-21368 SHARC Processor Hardware Reference.* Note that the 20 bits of external PDAP data can be provided through the external port DATA31–12 pins or the DAI pins.

#### Table 33. Parallel Data Acquisition Port (PDAP)

| Parameter                        |                                                                  | Min                              | Max | Unit |

|----------------------------------|------------------------------------------------------------------|----------------------------------|-----|------|

| Timing Requ                      | irements                                                         |                                  |     |      |

| t <sub>sPHOLD</sub> <sup>1</sup> | PDAP_HOLD Setup Before PDAP_CLK Sample Edge                      | 2.5                              |     | ns   |

| t <sub>HPHOLD</sub> <sup>1</sup> | PDAP_HOLD Hold After PDAP_CLK Sample Edge                        | 2.5                              |     | ns   |

| t <sub>PDSD</sub> <sup>1</sup>   | PDAP_DAT Setup Before SCLK PDAP_CLK Sample Edge                  | 3.85                             |     | ns   |

| t <sub>PDHD</sub> <sup>1</sup>   | PDAP_DAT Hold After SCLK PDAP_CLK Sample Edge                    | 2.5                              |     | ns   |

| t <sub>PDCLKW</sub>              | Clock Width                                                      | $(t_{PCLK} \times 4) \div 2 - 3$ |     | ns   |

| t <sub>PDCLK</sub>               | Clock Period                                                     | $t_{PCLK} \times 4$              |     | ns   |

| Switching Ch                     | paracteristics                                                   |                                  |     |      |

| t <sub>PDHLDD</sub>              | Delay of PDAP Strobe After Last PDAP_CLK Capture Edge for a Word | $2 \times t_{\text{PCLK}} + 3$   |     | ns   |

| t <sub>PDSTRB</sub>              | PDAP Strobe Pulse Width                                          | $2 \times t_{\text{PCLK}} - 1$   |     | ns   |

<sup>1</sup>Data Source pins are DATA31-12, or DAI pins. Source pins for SCLK and FS are: 1) DATA11-10 pins, 2) DAI pins.

Figure 27. PDAP Timing

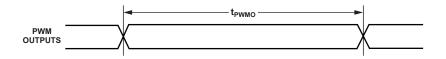

#### **Pulse-Width Modulation Generators**

#### Table 34. PWM Timing

| Parameter         |                        | Min                              | Мах                                 | Unit |

|-------------------|------------------------|----------------------------------|-------------------------------------|------|

| Switching (       | Characteristics        |                                  |                                     |      |

| t <sub>PWMW</sub> | PWM Output Pulse Width | t <sub>PCLK</sub> – 2            | $(2^{16} - 2) \times t_{PCLK}$      | ns   |

| t <sub>PWMP</sub> | PWM Output Period      | $2 \times t_{\text{PCLK}} - 1.5$ | $(2^{16}-1) \times t_{\text{PCLK}}$ | ns   |

Figure 28. PWM Timing

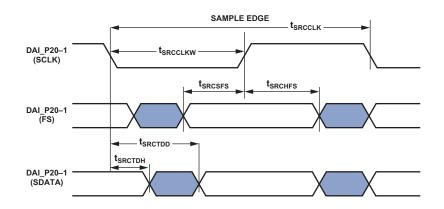

#### Sample Rate Converter—Serial Input Port

The SRC input signals SCLK, frame sync (FS), and SDATA are routed from the DAI\_P20-1 pins using the SRU. Therefore, the timing specifications provided in Table 35 are valid at the DAI\_P20-1 pins.

#### Table 35. SRC, Serial Input Port

| Parameter                        |                                     | Min                                                    | Мах | Unit |

|----------------------------------|-------------------------------------|--------------------------------------------------------|-----|------|

| Timing Req                       | uirements                           |                                                        |     |      |

| t <sub>sRCSFS</sub> <sup>1</sup> | FS Setup Before SCLK Rising Edge    | 4                                                      |     | ns   |

| t <sub>srchfs</sub> 1            | FS Hold After SCLK Rising Edge      | 5.5                                                    |     | ns   |

| t <sub>sRCSD</sub> <sup>1</sup>  | SDATA Setup Before SCLK Rising Edge | 4                                                      |     | ns   |

| t <sub>srchd</sub> 1             | SDATA Hold After SCLK Rising Edge   | 5.5                                                    |     | ns   |

| t <sub>srcclkw</sub>             | Clock Width                         | $(t_{PCLK} \times 4) \div 2 -$                         | 1   | ns   |

| t <sub>srcclk</sub>              | Clock Period                        | $(t_{_{PCLK}} \times 4) \div 2 - t_{_{PCLK}} \times 4$ |     | ns   |

<sup>1</sup> DATA, SCLK, FS can come from any of the DAI pins. SCLK and FS can also come via PCG or SPORTs. PCG's input can be either CLKIN or any of the DAI pins.

#### Sample Rate Converter—Serial Output Port

For the serial output port, the frame-sync is an input and it should meet setup and hold times with regard to SCLK on the output port. The serial data output, SDATA, has a hold time

#### Table 36. SRC, Serial Output Port

and delay specification with regard to SCLK. Note that SCLK rising edge is the sampling edge and the falling edge is the drive edge.

| Parameter                        | ,                                           | Min                                                    | Min Max |    |  |  |

|----------------------------------|---------------------------------------------|--------------------------------------------------------|---------|----|--|--|

| Timing Req                       | ning Requirements                           |                                                        |         |    |  |  |

| $t_{\text{SRCSFS}}^{1}$          | FS Setup Before SCLK Rising Edge            | 4                                                      |         | ns |  |  |

| t <sub>sRCHFS</sub> <sup>1</sup> | FS Hold After SCLK Rising Edge              | 5.5                                                    |         | ns |  |  |

| t <sub>srcclkw</sub>             | Clock Width                                 | $(t_{PCLK} \times 4) \div 2 -$                         | - 1     | ns |  |  |

| t <sub>srcclk</sub>              | Clock Period                                | $(t_{_{PCLK}} \times 4) \div 2 - t_{_{PCLK}} \times 4$ |         | ns |  |  |

| Switching C                      | haracteristics                              |                                                        |         |    |  |  |

| t <sub>srctdd</sub> <sup>1</sup> | Transmit Data Delay After SCLK Falling Edge |                                                        | 9.9     | ns |  |  |

| t <sub>srctdh</sub> <sup>1</sup> | Transmit Data Hold After SCLK Falling Edge  | 1                                                      |         | ns |  |  |

<sup>1</sup> DATA, SCLK, and FS can come from any of the DAI pins. SCLK and FS can also come via PCG or SPORTs. PCG's input can be either CLKIN or any of the DAI pins.

Figure 30. SRC Serial Output Port Timing

Figure 34. S/PDIF Transmitter Input Timing

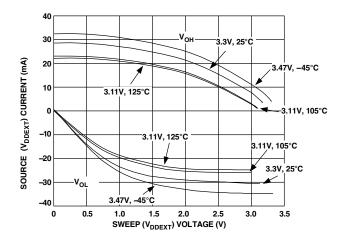

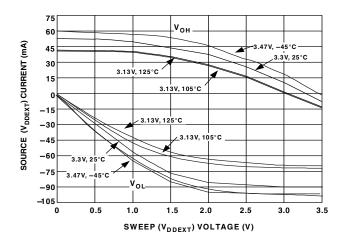

#### **OUTPUT DRIVE CURRENTS**

Figure 39 shows typical I-V characteristics for the output drivers and Figure 40 shows typical I-V characteristics for the SDCLK output drivers. The curves represent the current drive capability of the output drivers as a function of output voltage.

Figure 39. Typical Drive at Junction Temperature

Figure 40. SDCLK1–0 Drive at Junction Temperature

#### **TEST CONDITIONS**

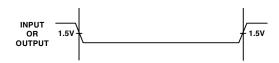

The ac signal specifications (timing parameters) appear in Table 14 on Page 23 through Table 42 on Page 50. These include output disable time, output enable time, and capacitive loading. The timing specifications for the SHARC apply for the voltage reference levels in Figure 41.

Timing is measured on signals when they cross the 1.5 V level as described in Figure 41. All delays (in nanoseconds) are measured between the point that the first signal reaches 1.5 V and the point that the second signal reaches 1.5 V.

Figure 41. Voltage Reference Levels for AC Measurements

#### **CAPACITIVE LOADING**

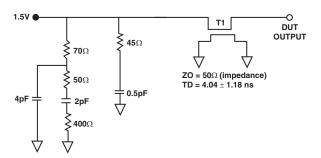

Output delays and holds are based on standard capacitive loads of an average of 6 pF on all pins (see Figure 42). Figure 47 and Figure 48 show graphically how output delays and holds vary with load capacitance. The graphs of Figure 43 through Figure 48 may not be linear outside the ranges shown for Typical Output Delay vs. Load Capacitance and Typical Output Rise Time (20% to 80%, V = Min) vs. Load Capacitance.

NOTES: THE WORST CASE TRANSMISSION LINE DELAY IS SHOWN AND CAN BE USED FOR THE OUTPUT TIMING ANALYSIS TO REFELECT THE TRANSMISSION LINE EFFECT AND MUST BE CONSIDERED. THE TRANSMISSION LINE (TD), IS FOR LOAD ONLY AND DOES NOT AFFECT THE DATA SHEET TIMING SPECIFICATIONS.

ANALOG DEVICES RECOMMENDS USING THE IBIS MODEL TIMING FOR A GIVEN SYSTEM REQUIREMENT. IF NECESSARY, A SYSTEM MAY INCORPORATE EXTERNAL DRIVERS TO COMPENSATE FOR ANY TIMING DIFFERENCES.

Figure 42. Equivalent Device Loading for AC Measurements (Includes All Fixtures)

### 256-BALL BGA\_ED PINOUT

The following table shows the ADSP-2136x's pin names and their default function after reset (in parentheses).

| Ball No. | Signal               | Ball No. | Signal               | Ball No. | Signal               | Ball No. | Signal             |

|----------|----------------------|----------|----------------------|----------|----------------------|----------|--------------------|

| A01      | NC                   | B01      | DAI_P05 (SD1A)       | C01      | DAI_P09 (SD2A)       | D01      | DAI_P10 (SD2B)     |

| A02      | TDI                  | B02      | SDCLK1 <sup>1</sup>  | C02      | DAI_P07 (SCLK1)      | D02      | DAI_P06 (SD1B)     |

| A03      | TMS                  | B03      | TRST                 | C03      | GND                  | D03      | GND                |

| A04      | CLK_CFG0             | B04      | ТСК                  | C04      | V <sub>DDEXT</sub>   | D04      | V <sub>DDEXT</sub> |

| A05      | CLK_CFG1             | B05      | BOOT_CFG0            | C05      | GND                  | D05      | GND                |

| A06      | EMU                  | B06      | BOOT_CFG1            | C06      | GND                  | D06      | V <sub>DDEXT</sub> |

| A07      | DAI_P04 (SFS0)       | B07      | TDO                  | C07      |                      | D07      |                    |

| A08      | DAI_P01 (SD0A)       | B08      | DAI_P03 (SCLK0)      | C08      | GND                  | D08      | GND                |

| A09      | DPI_P14 (TIMER1)     | B09      | DAI_P02 (SD0B)       | C09      | GND                  | D09      | V <sub>DDEXT</sub> |

| A10      | DPI_P12 (TWI_CLK)    | B10      | DPI_P13 (TIMER0)     | C10      |                      | D10      |                    |

| A11      | DPI_P10 (UARTORX)    | B11      | DPI_P11 (TWI_DATA)   | C11      | GND                  | D11      | GND                |

| A12      | DPI_P09 (UART0TX)    | B12      | DPI_P08 (SPIFLG3)    | C12      | GND                  | D12      | V <sub>DDEXT</sub> |

| A13      | DPI_P07 (SPIFLG2)    | B13      | DPI_P05 (SPIFLG0)    | C13      |                      | D13      |                    |

| A14      | DPI_P06 (SPIFLG1)    | B14      | DPI_P04 (SPIDS)      | C14      | GND                  | D14      | GND                |

| A15      | DPI_P03 (SPICLK)     | B15      | DPI_P01 (SPIMOSI)    | C15      | GND                  | D15      | V <sub>DDEXT</sub> |

| A16      | DPI_P02 (SPIMISO)    | B16      | RESET                | C16      |                      | D16      | GND                |

| A17      | RESETOUT             | B17      | DATA30               | C17      |                      | D17      | V <sub>DDEXT</sub> |

| A18      | DATA31               | B18      | DATA29               | C18      |                      | D18      | GND                |

| A19      | NC                   | B19      | DATA28               | C19      | DATA27               | D19      | DATA26             |

| A20      | NC                   | B20      | NC                   | C20      | NC/RPBA <sup>2</sup> | D20      | DATA24             |

| E01      | DAI_P11 (SD3A)       | F01      | DAI_P14 (SFS3)       | G01      | DAI_P15 (SD4A)       | H01      | DAI_P17 (SD5A)     |

| E02      | DAI_P08 (SFS1)       | F02      | DAI_P12 (SD3B)       | G02      | DAI_P13 (SCLK3)      | H02      | DAI_P16 (SD4B)     |

| E03      |                      | F03      | GND                  | G03      | GND                  | H03      |                    |

| E04      |                      | F04      | GND                  | G04      | V <sub>DDEXT</sub>   | H04      |                    |

| E17      | GND                  | F17      | V <sub>DDEXT</sub>   | G17      |                      | H17      | V <sub>DDEXT</sub> |

| E18      | GND                  | F18      | GND                  | G18      |                      | H18      | GND                |

| E19      | DATA25               | F19      | GND/ID2 <sup>2</sup> | G19      | DATA22               | H19      | DATA19             |

| E20      | DATA23               | F20      | DATA21               | G20      | DATA20               | H20      | DATA18             |

| J01      | DAI_P19 (SCLK5)      | K01      | FLAG0                | L01      | FLAG2                | M01      | ACK                |

| J02      | DAI_P18 (SD5B)       | K02      | DAI_P20 (SFS5)       | L02      | FLAG1                | M02      | FLAG3              |

| J03      | GND                  | K03      | GND                  | L03      |                      | M03      | GND                |

| J04      | GND                  | K04      | V <sub>DDEXT</sub>   | L04      |                      | M04      | GND                |

| J17      | GND                  | K17      | V <sub>DDINT</sub>   | L17      |                      | M17      | V <sub>DDEXT</sub> |

| J18      | GND                  | K18      |                      | L18      |                      | M18      | GND                |

| J19      | GND/ID1 <sup>2</sup> | K19      | GND/ID0 <sup>2</sup> | L19      | DATA15               | M19      | DATA12             |

| J20      | DATA17               | K20      | DATA16               | L20      | DATA14               | M20      | DATA13             |

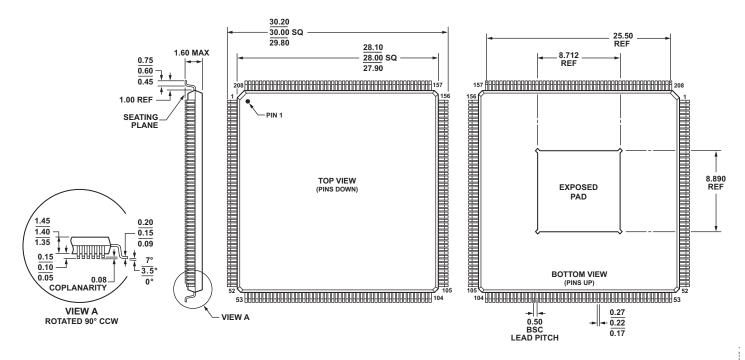

### **PACKAGE DIMENSIONS**

The ADSP-21367/ADSP-21368/ADSP-21369 processors are available in 256-ball RoHS compliant and leaded BGA\_ED, and 208-lead RoHS compliant LQFP\_EP packages.

COMPLIANT TO JEDEC STANDARDS MS-026-BJB-HD

NOTE:

THE EXPOSED PAD IS REQUIRED TO BE ELECTRICALLY AND THERMALLY CONNECTED TO VSS. THIS SHOULD BE IMPLEMENTED BY SOLDERING THE EXPOSED PAD TO A VSS PCB LAND THAT IS THE SAME SIZE AS THE EXPOSED PAD. THE VSS PCB LAND SHOULD BE ROBUSTLY CONNECTED TO THE VSS PLANE IN THE PCB WITH AN ARRAY OF THERMAL VIAS FOR BEST PERFORMANCE.

Figure 51. 208-Lead Low Profile Quad Flat Package, Exposed Pad [LQFP\_EP]

(SW-208-1)

Dimensions shown in millimeters