Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 7x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

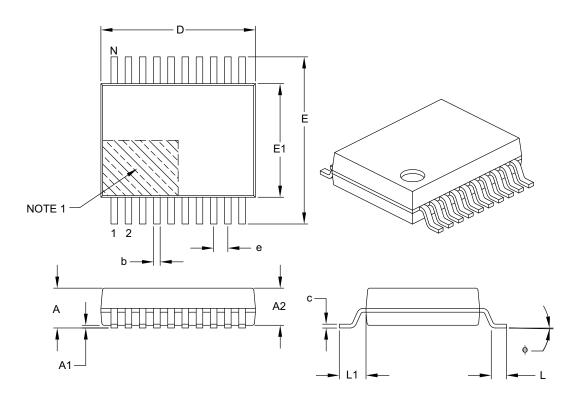

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1220-e-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

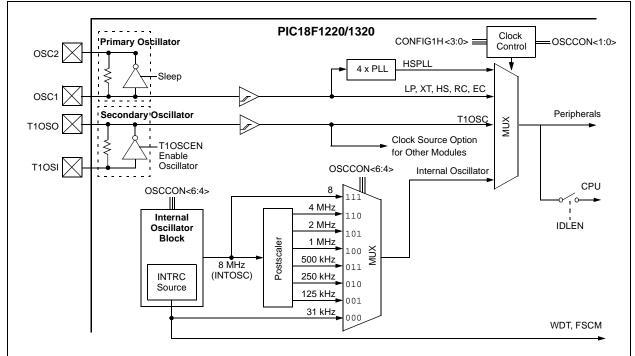

## 2.7.1 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 2-2) controls several aspects of the system clock's operation, both in full-power operation and in power managed modes.

The System Clock Select bits, SCS1:SCS0, select the clock source that is used when the device is operating in power managed modes. The available clock sources are the primary clock (defined in Configuration Register 1H), the secondary clock (Timer1 oscillator) and the internal oscillator block. The clock selection has no effect until a SLEEP instruction is executed and the device enters a power managed mode of operation. The SCS bits are cleared on all forms of Reset.

The Internal Oscillator Select bits, IRCF2:IRCF0, select the frequency output of the internal oscillator block that is used to drive the system clock. The choices are the INTRC source, the INTOSC source (8 MHz), or one of the six frequencies derived from the INTOSC postscaler (125 kHz to 4 MHz). If the internal oscillator block is supplying the system clock, changing the states of these bits will have an immediate change on the internal oscillator's output.

The OSTS, IOFS and T1RUN bits indicate which clock source is currently providing the system clock. The OSTS indicates that the Oscillator Start-up Timer has timed out and the primary clock is providing the system clock in Primary Clock modes. The IOFS bit indicates when the internal oscillator block has stabilized and is providing the system clock in RC Clock modes or during Two-Speed Start-ups. The T1RUN bit (T1CON<6>) indicates when the Timer1 oscillator is providing the system clock in Secondary Clock modes. In power managed modes, only one of these three bits will be set at any time. If none of these bits are set, the INTRC is providing the system clock, or the internal oscillator block has just started and is not yet stable.

The IDLEN bit controls the selective shutdown of the controller's CPU in power managed modes. The uses of these bits are discussed in more detail in **Section 3.0 "Power Managed Modes"**.

- Note 1: The Timer1 oscillator must be enabled to select the secondary clock source. The Timer1 oscillator is enabled by setting the T1OSCEN bit in the Timer1 Control register (T1CON<3>). If the Timer1 oscillator is not enabled, then any attempt to select a secondary clock source when executing a SLEEP instruction will be ignored.

- 2: It is recommended that the Timer1 oscillator be operating and stable before executing the SLEEP instruction or a very long delay may occur while the Timer1 oscillator starts.

#### FIGURE 2-8: PIC18F1220/1320 CLOCK DIAGRAM

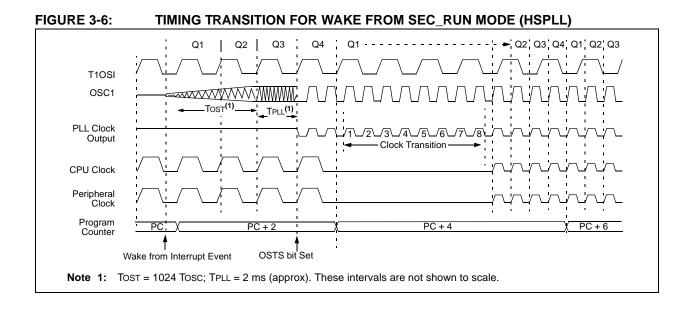

#### 3.3.2 SEC\_IDLE MODE

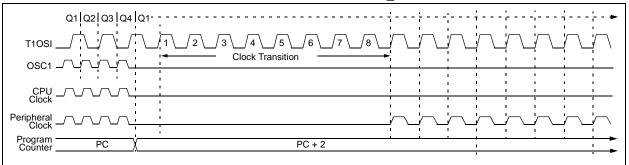

In SEC\_IDLE mode, the CPU is disabled, but the peripherals continue to be clocked from the Timer1 oscillator. This mode is entered by setting the Idle bit, modifying bits, SCS1:SCS0 = 01 and executing a SLEEP instruction. When the clock source is switched (see Figure 3-5) to the Timer1 oscillator, the primary oscillator is shut down, the OSTS bit is cleared and the T1RUN bit is set.

Note: The Timer1 oscillator should already be running prior to entering SEC\_IDLE mode. If the T1OSCEN bit is not set when the SLEEP instruction is executed, the SLEEP instruction will be ignored and entry to SEC\_IDLE mode will not occur. If the Timer1 oscillator is enabled, but not yet running, peripheral clocks will be delayed until the oscillator has started; in such situations, initial oscillator operation is far from stable and unpredictable operation may result. When a wake event occurs, the peripherals continue to be clocked from the Timer1 oscillator. After a 10  $\mu$ s delay following the wake event, the CPU begins executing code, being clocked by the Timer1 oscillator. The microcontroller operates in SEC\_RUN mode until the primary clock becomes ready. When the primary clock becomes ready, a clock switchback to the primary clock occurs (see Figure 3-6). When the clock switch is complete, the T1RUN bit is cleared, the OSTS bit is set and the primary clock is providing the system clock. The IDLEN and SCS bits are not affected by the wake-up. The Timer1 oscillator continues to run.

#### FIGURE 3-5: TIMING TRANSITION FOR ENTRY TO SEC IDLE MODE

#### 7.3 Reading the Data EEPROM Memory

To read a data memory location, the user must write the address to the EEADR register, clear the EEPGD control bit (EECON1<7>) and then set control bit, RD (EECON1<0>). The data is available for the very next instruction cycle; therefore, the EEDATA register can be read by the next instruction. EEDATA will hold this value until another read operation, or until it is written to by the user (during a write operation).

#### 7.4 Writing to the Data EEPROM Memory

To write an EEPROM data location, the address must first be written to the EEADR register and the data written to the EEDATA register. The sequence in Example 7-2 must be followed to initiate the write cycle.

The write will not begin if this sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. It is strongly recommended that interrupts be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable writes. This mechanism prevents accidental writes to data EEPROM due to unexpected code execution (i.e., runaway programs). The WREN bit should be kept clear at all times, except when updating the EEPROM. The WREN bit is not cleared by hardware.

## EXAMPLE 7-1: DATA EEPROM READ

After a write sequence has been initiated, EECON1, EEADR and EEDATA cannot be modified. The WR bit will be inhibited from being set unless the WREN bit is set. The WREN bit must be set on a previous instruction. Both WR and WREN cannot be set with the same instruction.

At the completion of the write cycle, the WR bit is cleared in hardware and the EEPROM Interrupt Flag bit (EEIF) is set. The user may either enable this interrupt or poll this bit. EEIF must be cleared by software.

## 7.5 Write Verify

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

## 7.6 Protection Against Spurious Write

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built-in. On power-up, the WREN bit is cleared. Also, the Power-up Timer (72 ms duration) prevents EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch or software malfunction.

| MOVLW | DATA_EE_ADDR;                       |  |

|-------|-------------------------------------|--|

| MOVWF | EEADR ; Data Memory Address to read |  |

| BCF   | EECON1, EEPGD; Point to DATA memory |  |

| BSF   | EECON1, RD ; EEPROM Read            |  |

| MOVF  | EEDATA, W ; W = EEDATA              |  |

#### EXAMPLE 7-2: DATA EEPROM WRITE

|          | MOVLW | DATA_EE_ADDR;                                 |

|----------|-------|-----------------------------------------------|

|          | MOVWF | EEADR ; Data Memory Address to write          |

|          | MOVLW | DATA_EE_DATA;                                 |

|          | MOVWF | EEDATA ; Data Memory Value to write           |

|          | BCF   | EECON1, EEPGD; Point to DATA memory           |

|          | BSF   | EECON1, WREN; Enable writes                   |

|          | BCF   | INTCON, GIE; Disable Interrupts               |

|          | MOVLW | 55h ;                                         |

| Required | MOVWF | EECON2 ; Write 55h                            |

| Sequence | MOVLW | AAh ;                                         |

|          | MOVWF | EECON2 ; Write AAh                            |

|          | BSF   | EECON1, WR ; Set WR bit to begin write        |

|          | BSF   | INTCON, GIE; Enable Interrupts                |

|          |       |                                               |

|          | SLEEP | ; Wait for interrupt to signal write complete |

|          | BCF   | EECON1, WREN; Disable writes                  |

|          |       |                                               |

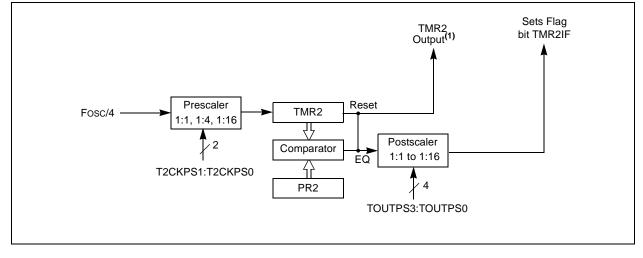

#### 13.2 Timer2 Interrupt

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon Reset.

FIGURE 13-1: TIMER2 BLOCK DIAGRAM

#### 13.3 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module, which optionally uses it to generate the shift clock.

#### TABLE 13-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Name                       | Bit 7      | Bit 6        | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|----------------------------|------------|--------------|---------|---------|---------|--------|---------|-----------|----------------------|---------------------------------|

| INTCON                     | GIE/GIEH   | PEIE/GIEL    | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF  | RBIF      | 0000 000x            | 0000 000u                       |

| PIR1                       | _          | ADIF         | RCIF    | TXIF    | _       | CCP1IF | TMR2IF  | TMR1IF    | -000 -000            | -000 -000                       |

| PIE1                       | _          | ADIE         | RCIE    | TXIE    | _       | CCP1IE | TMR2IE  | TMR1IE    | -000 -000            | -000 -000                       |

| IPR1                       | _          | ADIP         | RCIP    | TXIP    | _       | CCP1IP | TMR2IP  | TMR1IP    | -111 -111            | -111 -111                       |

| TMR2                       | Timer2 Mod | dule Registe | r       |         |         |        |         |           | 0000 0000            | 0000 0000                       |

| T2CON                      | —          | TOUTPS3      | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0   | -000 0000            | -000 0000                       |

| PR2 Timer2 Period Register |            |              |         |         |         |        |         | 1111 1111 | 1111 1111            |                                 |

| PR2 Timer2 Period Register |            |              |         |         |         |        |         |           |                      |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

## 14.0 TIMER3 MODULE

The Timer3 module timer/counter has the following features:

- 16-bit timer/counter (two 8-bit registers; TMR3H and TMR3L)

- Readable and writable (both registers)

- Internal or external clock select

- Interrupt-on-overflow from FFFFh to 0000h

- Reset from CCP module trigger

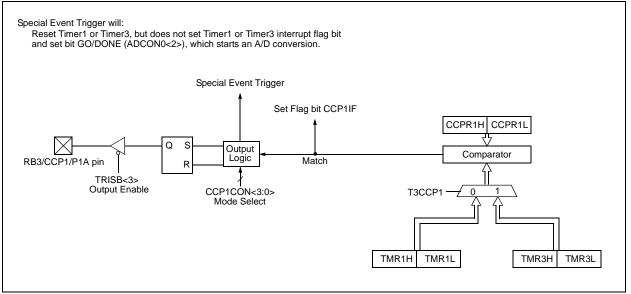

Figure 14-1 is a simplified block diagram of the Timer3 module.

Register 14-1 shows the Timer3 Control register. This register controls the operating mode of the Timer3 module and sets the CCP clock source.

Register 12-1 shows the Timer1 Control register. This register controls the operating mode of the Timer1 module, as well as contains the Timer1 Oscillator Enable bit (T1OSCEN), which can be a clock source for Timer3.

#### REGISTER 14-1: T3CON: TIMER3 CONTROL REGISTER

| R/W-0/0          | U-0                               | R/W-0/0                            | R/W-0/0         | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|-----------------------------------|------------------------------------|-----------------|----------------|------------------|------------------|-------------|

| RD16             | <u> </u>                          | T3CKPS1                            | T3CKPS0         | T3CCP1         | T3SYNC           | TMR3CS           | TMR3ON      |

| bit 7            |                                   |                                    |                 | 100011         | 1001110          |                  | bit C       |

| Legend:          |                                   |                                    |                 |                |                  |                  |             |

| R = Readable     | e bit                             | W = Writable                       | bit             | U = Unimplen   | nented bit, read | l as '0'         |             |

| u = Bit is unc   | hanged                            | x = Bit is unkr                    | nown            | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set | 1                                 | '0' = Bit is clea                  | ared            |                |                  |                  |             |

|                  |                                   |                                    |                 |                |                  |                  |             |

| bit 7            |                                   | Read/Write Mo                      |                 | 401.1          |                  |                  |             |

|                  |                                   | register read/w<br>register read/w |                 |                |                  |                  |             |

| bit 6            |                                   | nted: Read as '                    |                 |                |                  |                  |             |

| bit 5-4          | T3CKPS<1:0                        | <b>0&gt;:</b> Timer3 Inpu          | t Clock Presca  | le Select bits |                  |                  |             |

|                  | 11 = 1:8 Pre:                     | •                                  |                 |                |                  |                  |             |

|                  | 10 = 1:4 Pre                      |                                    |                 |                |                  |                  |             |

|                  | 01 = 1:2 Pres<br>00 = 1:1 Pres    |                                    |                 |                |                  |                  |             |

| bit 3            |                                   | ner3 and Timer                     | 1 to CCP1 Eng   | hla hits       |                  |                  |             |

| bit 5            |                                   | the clock source                   |                 |                | module           |                  |             |

|                  |                                   | s the clock source                 |                 |                |                  |                  |             |

| bit 2            |                                   | mer3 External C                    |                 |                |                  |                  |             |

|                  | •                                 | f the system clo                   | ck comes from   | n Timer1/Time  | r3.)             |                  |             |

|                  | <u>When TMR3</u><br>1 = Do not sy | <u>CS = 1</u> :<br>ynchronize exte | rnal clock innu | +              |                  |                  |             |

|                  | •                                 | nize external clo                  | •               | it.            |                  |                  |             |

|                  | When TMR3                         |                                    | ·               |                |                  |                  |             |

|                  | This bit is igr                   | ored. Timer3 u                     | ses the interna | l clock when T | MR3CS = 0.       |                  |             |

| bit 1            |                                   | mer3 Clock Sou                     |                 |                |                  |                  |             |

|                  |                                   | clock input from                   |                 |                | []               |                  |             |

|                  |                                   | ising edge after<br>clock (Fosc/4) | the mst talling | j edge)        |                  |                  |             |

| bit 0            | TMR3ON: Ti                        |                                    |                 |                |                  |                  |             |

|                  | 1 = Enables                       | Timer3                             |                 |                |                  |                  |             |

|                  | 0 = Stops Ti                      |                                    |                 |                |                  |                  |             |

### FIGURE 15-2: COMPARE MODE OPERATION BLOCK DIAGRAM

### TABLE 15-3: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, TIMER1 AND TIMER3

| Name    | Bit 7                                                                       | Bit 6           | Bit 5        | Bit 4        | Bit 3         | Bit 2    | Bit 1   | Bit 0  |      | e on<br>BOR | all o | ie on<br>other<br>sets |

|---------|-----------------------------------------------------------------------------|-----------------|--------------|--------------|---------------|----------|---------|--------|------|-------------|-------|------------------------|

| INTCON  | GIE/GIEH                                                                    | PEIE/GIEL       | TMR0IE       | INT0IE       | RBIE          | TMR0IF   | INT0IF  | RBIF   | 0000 | 000x        | 0000  | 000u                   |

| PIR1    | _                                                                           | ADIF            | RCIF         | TXIF         |               | CCP1IF   | TMR2IF  | TMR1IF | -000 | -000        | -000  | -000                   |

| PIE1    | —                                                                           | ADIE            | RCIE         | TXIE         | _             | CCP1IE   | TMR2IE  | TMR1IE | -000 | -000        | -000  | -000                   |

| IPR1    | —                                                                           | ADIP            | RCIP         | TXIP         | _             | CCP1IP   | TMR2IP  | TMR1IP | -111 | -111        | -111  | -111                   |

| TRISB   | PORTB Da                                                                    | ata Direction   | Register     |              |               |          |         |        | 1111 | 1111        | 1111  | 1111                   |

| TMR1L   | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                 |              |              |               |          |         |        |      | xxxx        | uuuu  | uuuu                   |

| TMR1H   | Holding Re                                                                  | egister for the | e Most Sign  | ificant Byte | of the 16-bit | TMR1 Reg | ister   |        | xxxx | xxxx        | uuuu  | uuuu                   |

| T1CON   | RD16                                                                        | T1RUN           | T1CKPS1      | T1CKPS0      | T1OSCEN       | T1SYNC   | TMR1CS  | TMR10N | 0000 | 0000        | uuuu  | uuuu                   |

| CCPR1L  | Capture/C                                                                   | ompare/PWI      | M Register 1 | (LSB)        |               |          | •       |        | xxxx | xxxx        | uuuu  | uuuu                   |

| CCPR1H  | Capture/C                                                                   | ompare/PWI      | M Register 1 | (MSB)        |               |          |         |        | xxxx | xxxx        | uuuu  | uuuu                   |

| CCP1CON | P1M1                                                                        | P1M0            | DC1B1        | DC1B0        | CCP1M3        | CCP1M2   | CCP1M1  | CCP1M0 | 0000 | 0000        | 0000  | 0000                   |

| TMR3L   | Holding Register for the Least Significant Byte of the 16-bit TMR3 Register |                 |              |              |               |          |         |        |      | xxxx        | uuuu  | uuuu                   |

| TMR3H   | Holding Register for the Most Significant Byte of the 16-bit TMR3 Register  |                 |              |              |               |          |         |        |      | xxxx        | uuuu  | uuuu                   |

| T3CON   | RD16                                                                        | _               | T3CKPS1      | T3CKPS0      | T3CCP1        | T3SYNC   | TMR3CS  | TMR3ON | 0-00 | 0000        | u-uu  | uuuu                   |

| ADCON0  | VCFG1                                                                       | VCFG0           | _            | CHS2         | CHS1          | CHS0     | GO/DONE | ADON   | 00-0 | 0000        | 00-0  | 0000                   |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by Capture and Timer1.

#### REGISTER 15-3: ECCPAS: ENHANCED CAPTURE/COMPARE/PWM/AUTO-SHUTDOWN CONTROL REGISTER

| R/W-0/0          | R/W-0/0                        | R/W-0/0                            | R/W-0/0       | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|--------------------------------|------------------------------------|---------------|----------------|------------------|------------------|-------------|

| ECCPASE          | ECCPAS2                        | ECCPAS1                            | ECCPAS0       | PSSAC1         | PSSAC0           | PSSBD1           | PSSBD0      |

| bit 7            |                                |                                    |               |                |                  |                  | bit 0       |

|                  |                                |                                    |               |                |                  |                  |             |

| Legend:          |                                |                                    |               |                |                  |                  |             |

| R = Readable     | bit                            | W = Writable                       | bit           | U = Unimplen   | nented bit, read | as '0'           |             |

| u = Bit is unch  | anged                          | x = Bit is unkr                    | nown          | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |                                | '0' = Bit is clea                  | ared          |                |                  |                  |             |

|                  |                                |                                    |               |                |                  |                  |             |

| bit 7            |                                | CCP Auto-Shu                       |               | Status bit     |                  |                  |             |

|                  |                                | tputs are opera                    | 0             |                |                  | _                |             |

|                  |                                |                                    |               | outputs are in | n shutdown stat  | e                |             |

| bit 6            |                                | CCP Auto-Shu                       | tdown bit 2   |                |                  |                  |             |

|                  | 0 = INT0 pin  <br>1 = INT0 pin | nas no effect<br>Iow causes shu    | Itdown        |                |                  |                  |             |

| bit 5            | •                              | CCP Auto-Shu                       |               |                |                  |                  |             |

| bit 5            | 0 = INT2 pin                   |                                    |               |                |                  |                  |             |

|                  | •                              | low causes shu                     | ıtdown        |                |                  |                  |             |

| bit 4            | ECCPAS0: E                     | CCP Auto-Shu                       | tdown bit 0   |                |                  |                  |             |

|                  | 0 = INT1 pin                   | has no effect                      |               |                |                  |                  |             |

|                  | 1 = INT1 pin                   | low causes shu                     | Itdown        |                |                  |                  |             |

| bit 3-2          | PSSACn: Pir                    | ns A and C Shu                     | tdown State C | ontrol bits    |                  |                  |             |

|                  |                                | ns A and C to '                    |               |                |                  |                  |             |

|                  |                                | ns A and C to '<br>and C tri-state | 1'            |                |                  |                  |             |

| <b>h</b> #4.0    |                                |                                    |               | a stral bita   |                  |                  |             |

| bit 1-0          |                                | ns B and D Shu                     |               | ontrol dits    |                  |                  |             |

|                  |                                | ns B and D to '<br>ns B and D to ' | -             |                |                  |                  |             |

|                  | 1x = Pins B a                  |                                    | ±             |                |                  |                  |             |

| U-0             | R-1                                        | U-0                                                                              | R/W-0/0        | R/W-0/0      | U-0              | R/W-0/0          | R/W-0/0        |

|-----------------|--------------------------------------------|----------------------------------------------------------------------------------|----------------|--------------|------------------|------------------|----------------|

| _               | RCIDL                                      | —                                                                                | SCKP           | BRG16        | _                | WUE              | ABDEN          |

| bit 7           |                                            |                                                                                  |                |              |                  |                  | bit 0          |

|                 |                                            |                                                                                  |                |              |                  |                  |                |

| Legend:         |                                            |                                                                                  |                |              |                  |                  |                |

| R = Readab      |                                            | W = Writable                                                                     |                | •            | mented bit, read |                  |                |

| u = Bit is und  | -                                          | x = Bit is unkt                                                                  |                | -n/n = value | at POR and BC    | R/Value at all o | ther Resets    |

| '1' = Bit is se | et                                         | '0' = Bit is cle                                                                 | ared           |              |                  |                  |                |

| bit 7           | Unimplemen                                 | ted: Read as '                                                                   | 0'             |              |                  |                  |                |

| bit 6           | -                                          | ive Operation                                                                    |                |              |                  |                  |                |

|                 | 1 = Receiver<br>0 = Receiver               |                                                                                  |                |              |                  |                  |                |

| bit 5           | Unimplemen                                 | ted: Read as '                                                                   | 0'             |              |                  |                  |                |

| bit 4           | SCKP: Synch                                | ronous Clock                                                                     | Polarity Selec | t bit        |                  |                  |                |

|                 | Asynchronous<br>Unused in this             |                                                                                  |                |              |                  |                  |                |

|                 |                                            | mode:<br>for clock (CK)<br>for clock (CK)                                        | •              | I            |                  |                  |                |

| bit 3           | <b>BRG16:</b> 16-b                         | it Baud Rate R                                                                   | egister Enabl  | e bit        |                  |                  |                |

|                 |                                            |                                                                                  |                | H and SPBRC  |                  | RGH value igno   | ored           |

| bit 2           | Unimplemen                                 | ted: Read as '                                                                   | 0'             |              |                  |                  |                |

| bit 1           | WUE: Wake-                                 | up Enable bit                                                                    |                |              |                  |                  |                |

|                 | hardware                                   | will continue t<br>on following r<br>ot monitored o<br><u>mode:</u>              | ising edge     |              | rupt generated   | on falling edge; | bit cleared in |

| bit 0           |                                            | -Baud Detect                                                                     | Enable bit     |              |                  |                  |                |

|                 | Asynchronous<br>1 = Enable b<br>cleared in | <u>s mode:</u><br>aud rate meas<br>n hardware up<br>e measuremen<br><u>mode:</u> | urement on th  |              | er – requires re | eception of a Sy | nc byte (55h); |

## REGISTER 16-3: BAUDCTL: BAUD RATE CONTROL REGISTER

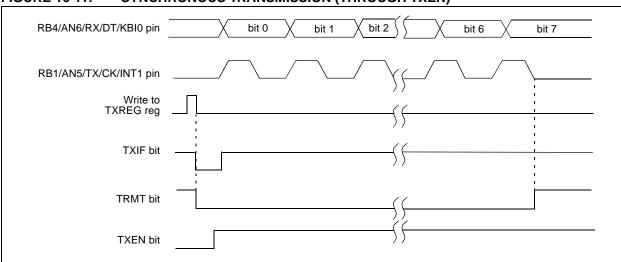

#### FIGURE 16-11: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

#### TABLE 16-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name    | Bit 7                                         | Bit 6        | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-----------------------------------------------|--------------|-------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| INTCON  | GIE/GIEH                                      | PEIE/GIEL    | TMR0IE      | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1    |                                               | ADIF         | RCIF        | TXIF   | _     | CCP1IF | TMR2IF | TMR1IF | -000 -000            | -000 -000                       |

| PIE1    | -                                             | ADIE         | RCIE        | TXIE   | _     | CCP1IE | TMR2IE | TMR1IE | -000 -000            | -000 -000                       |

| IPR1    | _                                             | ADIP         | RCIP        | TXIP   | —     | CCP1IP | TMR2IP | TMR1IP | -111 -111            | -111 -111                       |

| RCSTA   | SPEN                                          | RX9          | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 -00x            | 0000 -00x                       |

| TXREG   | EUSART T                                      | ransmit Regi | ster        |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA   | CSRC                                          | TX9          | TXEN        | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |

| BAUDCTL | _                                             | RCIDL        | —           | SCKP   | BRG16 | _      | WUE    | ABDEN  | -1-1 0-00            | -1-1 0-00                       |

| SPBRGH  | SPBRGH Baud Rate Generator Register High Byte |              |             |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| SPBRG   | Baud Rate                                     | Generator R  | egister Lov | v Byte |       |        |        |        | 0000 0000            | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

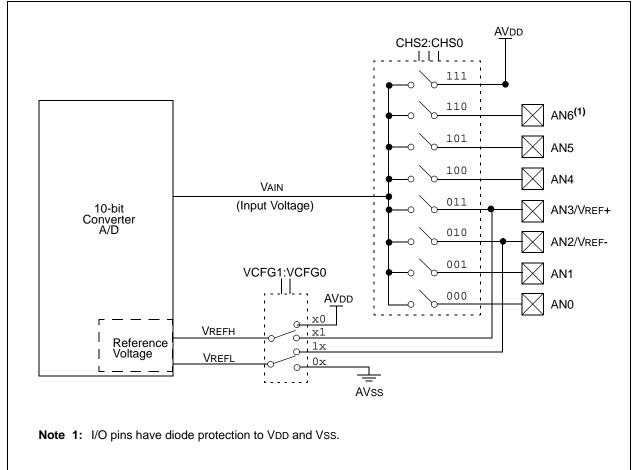

The analog reference voltage is software selectable to either the device's positive and negative supply voltage (AVDD and AVSS), or the voltage level on the RA3/AN3/ VREF+ and RA2/AN2/VREF- pins.

The A/D converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The output of the sample and hold is the input into the converter, which generates the result via successive approximation.

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off and any conversion in progress is aborted.

Each port pin associated with the A/D converter can be configured as an analog input, or as a digital I/O. The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is <u>loaded</u> into the ADRESH/ADRESL registers, the GO/DONE bit (ADCON0 register) is cleared and A/D Interrupt Flag bit, ADIF, is set. The block diagram of the A/D module is shown in Figure 17-1.

### 17.5 Operation in Low-Power Modes

The selection of the automatic acquisition time and the A/D conversion clock is determined, in part, by the low-power mode clock source and frequency while in a low-power mode.

If the A/D is expected to operate while the device is in a low-power mode, the ACQT2:ACQT0 and ADCS2:ADCS0 bits in ADCON2 should be updated in accordance with the low-power mode clock that will be used. After the low-power mode is entered (either of the Run modes), an A/D acquisition or conversion may be started. Once an acquisition or conversion is started, the device should continue to be clocked by the same low-power mode clock source until the conversion has been completed. If desired, the device may be placed into the corresponding low-power (ANY)\_IDLE mode during the conversion.

If the low-power mode clock frequency is less than 1 MHz, the A/D RC clock source should be selected.

Operation in the Low-Power Sleep mode requires the A/ D RC clock to be selected. If bits, ACQT2:ACQT0, are set to '000' and a conversion is started, the conversion will be delayed one instruction cycle to allow execution of the SLEEP instruction and entry to Low-Power Sleep mode. The IDLEN and SCS bits in the OSCCON register must have already been cleared prior to starting the conversion.

#### 17.6 Configuring Analog Port Pins

The ADCON1, TRISA and TRISB registers all configure the A/D port pins. The port pins needed as analog inputs must have their corresponding TRIS bits set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS2:CHS0 bits and the TRIS bits.

- Note 1: When reading the Port register, all pins configured as analog input channels will read as cleared (a low level). Pins configured as digital inputs will convert an analog input. Analog levels on a digitally configured input will be accurately converted.

- 2: Analog levels on any pin defined as a digital input may cause the digital input buffer to consume current out of the device's specification limits.

| BTFSC                                            |                | Bit Test File, Skip if Clear                                                                                                                                                                                                                                                                                                                                                                                                                           |                        |       |                |  |  |  |  |

|--------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------|----------------|--|--|--|--|

| Syntax:                                          |                | [ <i>label</i> ] B1                                                                                                                                                                                                                                                                                                                                                                                                                                    | FSC f,t                | o[,a] |                |  |  |  |  |

| Operand                                          | ds:            | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                  |                        |       |                |  |  |  |  |

| Operatio                                         | on:            | skip if (f <b< td=""><td><b>&gt;) =</b> 0</td><td></td><td></td></b<>                                                                                                                                                                                                                                                                                                                                                                                  | <b>&gt;) =</b> 0       |       |                |  |  |  |  |

| Status A                                         | ffected:       | None                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |       |                |  |  |  |  |

| Encodin                                          | a:             | 1011                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bbba                   | ffff  | ffff           |  |  |  |  |

| Words:<br>Cycles:                                | ion:           | If bit 'b' in register 'f' is '0', then the<br>next instruction is skipped.<br>If bit 'b' is '0', then the next<br>instruction fetched during the current<br>instruction execution is discarded<br>and a NOP is executed instead,<br>making this a 2-cycle instruction. If 'a'<br>is '0', the Access Bank will be<br>selected, overriding the BSR value. If<br>'a' = 1, then the bank will be selected<br>as per the BSR value (default).<br>1<br>1(2) |                        |       |                |  |  |  |  |

|                                                  | e Activity:    |                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ycles if s<br>a 2-word |       |                |  |  |  |  |

| Q Cycle                                          | Q1             | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Q3                     |       | Q4             |  |  |  |  |

|                                                  | Decode         | Read                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Proces                 | SS    | No             |  |  |  |  |

|                                                  |                | register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                           | Data                   | o     | peration       |  |  |  |  |

| If skip:                                         |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                        |       |                |  |  |  |  |

|                                                  | Q1             | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Q3                     |       | Q4             |  |  |  |  |

|                                                  | No<br>peration | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                        | No<br>operati          |       | No<br>peration |  |  |  |  |

|                                                  | •              | ed by 2-word                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        |       | Scration       |  |  |  |  |

| n onip c                                         | Q1             | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Q3                     | 011.  | Q4             |  |  |  |  |

|                                                  | No             | No                                                                                                                                                                                                                                                                                                                                                                                                                                                     | No                     |       | No             |  |  |  |  |

| 0                                                | peration       | operation                                                                                                                                                                                                                                                                                                                                                                                                                                              | operati                | on o  | peration       |  |  |  |  |

| 0                                                | No<br>peration | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                        | No<br>operati          | on o  | No<br>peration |  |  |  |  |

| Example: HERE BTFSC FLAG, 1<br>FALSE :<br>TRUE : |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                        |       |                |  |  |  |  |

| Before Instruction<br>PC = address (HERE)        |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                        |       |                |  |  |  |  |

|                                                  |                | = add                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ress (HEF              | RE)   |                |  |  |  |  |

| BTFSS Bit Test File, Skip if Set |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                       |                 |  |  |  |  |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------|--|--|--|--|--|

| Syntax:                          | Syntax: [ label ] BTFSS f,b[,a]                                                                                                                                                                                                                                                                                                                                                                                                           |                                       |                 |  |  |  |  |  |

| Operands:                        | $0 \le f \le 255$<br>$0 \le b < 7$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                       | 0 ≤ b < 7                             |                 |  |  |  |  |  |

| Operation:                       | skip if (f <b< td=""><td>&gt;) = 1</td><td></td></b<>                                                                                                                                                                                                                                                                                                                                                                                     | >) = 1                                |                 |  |  |  |  |  |

| Status Affected:                 | None                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |                 |  |  |  |  |  |

| Encoding:                        | 1010                                                                                                                                                                                                                                                                                                                                                                                                                                      | bbba ff                               | ff ffff         |  |  |  |  |  |

| Description:                     | If bit 'b' in register 'f' is '1', then the<br>next instruction is skipped.<br>If bit 'b' is '1', then the next<br>instruction fetched during the current<br>instruction execution is discarded<br>and a NOP is executed instead,<br>making this a 2-cycle instruction. If<br>'a' is '0', the Access Bank will be<br>selected, overriding the BSR value. If<br>'a' = 1, then the bank will be selected<br>as per the BSR value (default). |                                       |                 |  |  |  |  |  |

| Words:                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       | oldull).        |  |  |  |  |  |

| Cycles:<br>Q Cycle Activity:     |                                                                                                                                                                                                                                                                                                                                                                                                                                           | cycles if skip a<br>a 2-word ins      |                 |  |  |  |  |  |

| Q1                               | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q3                                    | Q4              |  |  |  |  |  |

| Decode                           | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                      | Process<br>Data                       | No<br>operation |  |  |  |  |  |

| If skip:                         | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                     | <u> </u>        |  |  |  |  |  |

| Q1                               | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q3                                    | Q4              |  |  |  |  |  |

| No                               | No                                                                                                                                                                                                                                                                                                                                                                                                                                        | No                                    | No              |  |  |  |  |  |

| operation<br>If skip and follow  | operation                                                                                                                                                                                                                                                                                                                                                                                                                                 | operation                             | operation       |  |  |  |  |  |

| Q1                               | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q3                                    | Q4              |  |  |  |  |  |

| No                               | No                                                                                                                                                                                                                                                                                                                                                                                                                                        | No                                    | No              |  |  |  |  |  |

| operation                        | operation                                                                                                                                                                                                                                                                                                                                                                                                                                 | operation                             | operation       |  |  |  |  |  |

| No                               | No                                                                                                                                                                                                                                                                                                                                                                                                                                        | No                                    | No              |  |  |  |  |  |

| operation                        | operation                                                                                                                                                                                                                                                                                                                                                                                                                                 | operation                             | operation       |  |  |  |  |  |

| Example:                         | HERE B<br>FALSE :<br>TRUE :                                                                                                                                                                                                                                                                                                                                                                                                               | FFSS FLAG                             | , 1             |  |  |  |  |  |

| Before Instru<br>PC              |                                                                                                                                                                                                                                                                                                                                                                                                                                           | ress (HERE)                           |                 |  |  |  |  |  |

| After Instruct                   |                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                       |                 |  |  |  |  |  |

| If FLAG<<br>PC<br>If FLAG<<br>PC | = add<br>1> = 1;                                                                                                                                                                                                                                                                                                                                                                                                                          | > = 0;<br>= address (FALSE)<br>> = 1; |                 |  |  |  |  |  |

| BTG                                             | Bit Toggle                                                                                                                                                                                                            | e f                          |      |                   |  |  |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|-------------------|--|--|

| Syntax:                                         | [ <i>label</i> ] B                                                                                                                                                                                                    | [ <i>label</i> ] BTG f,b[,a] |      |                   |  |  |

| Operands:                                       | 0 ≤ f ≤ 255<br>0 ≤ b < 7<br>a ∈ [0,1]                                                                                                                                                                                 | v = v · · ·                  |      |                   |  |  |

| Operation:                                      | $(\overline{f}\!<\!b\!\!>)\tof$                                                                                                                                                                                       | <b></b>                      |      |                   |  |  |

| Status Affected:                                | None                                                                                                                                                                                                                  |                              |      |                   |  |  |

| Encoding:                                       | 0111                                                                                                                                                                                                                  | bbba                         | ffff | ffff              |  |  |

| Description:                                    | Bit 'b' in data memory location 'f' is<br>inverted. If 'a' is '0', the Access Bank<br>will be selected, overriding the BSR<br>value. If 'a' = 1, then the bank will be<br>selected as per the BSR value<br>(default). |                              |      |                   |  |  |

| Words:                                          | 1                                                                                                                                                                                                                     |                              |      |                   |  |  |

| Cycles:                                         | 1                                                                                                                                                                                                                     |                              |      |                   |  |  |

| Q Cycle Activity                                | :                                                                                                                                                                                                                     |                              |      |                   |  |  |

| Q1                                              | Q2                                                                                                                                                                                                                    | Q3                           | (    | Q4                |  |  |

| Decode                                          | Read<br>register 'f'                                                                                                                                                                                                  | Process<br>Data              | -    | /rite<br>ster 'f' |  |  |

| Example: BTG PORTB, 4                           |                                                                                                                                                                                                                       |                              |      |                   |  |  |

| Before Instruction:<br>PORTB = 0111 0101 [0x75] |                                                                                                                                                                                                                       |                              |      |                   |  |  |

| After Instruction:<br>PORTB = 0110 0101 [0x65]  |                                                                                                                                                                                                                       |                              |      |                   |  |  |

| Synt                                                                                                                                                                                                                                                   | av.                   | [ <i>label</i> ] B  | [ <i>label</i> ] BOV n                                   |                                                                |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------|----------------------------------------------------------|----------------------------------------------------------------|--|--|--|

| -                                                                                                                                                                                                                                                      |                       | -128 < n <          |                                                          |                                                                |  |  |  |

| •                                                                                                                                                                                                                                                      | rands:                |                     |                                                          |                                                                |  |  |  |

| Opei                                                                                                                                                                                                                                                   | ration:               |                     | if Overflow bit is '1'<br>(PC) + 2 + 2n $\rightarrow$ PC |                                                                |  |  |  |

| Statu                                                                                                                                                                                                                                                  | is Affected:          | None                |                                                          |                                                                |  |  |  |

| Enco                                                                                                                                                                                                                                                   | oding:                | 1110                | 0100 nn                                                  | nn nnnn                                                        |  |  |  |

| Description: If the Overflow bit is '1', the<br>program will branch.<br>The 2's complement number<br>added to the PC. Since the<br>have incremented to fetche<br>instruction, the new addre<br>PC + 2 + 2n. This instruction<br>a 2-cycle instruction. |                       |                     |                                                          | umber '2n' i<br>e the PC wil<br>etch the nex<br>ldress will be |  |  |  |

| Word                                                                                                                                                                                                                                                   | ds:                   | 1                   |                                                          |                                                                |  |  |  |

| Cycl                                                                                                                                                                                                                                                   | es:                   | 1(2)                |                                                          |                                                                |  |  |  |

|                                                                                                                                                                                                                                                        | ycle Activity<br>Imp: | :                   |                                                          |                                                                |  |  |  |

|                                                                                                                                                                                                                                                        | Q1                    | Q2                  | Q3                                                       | Q4                                                             |  |  |  |

|                                                                                                                                                                                                                                                        | Decode                | Read literal<br>'n' | Process<br>Data                                          | Write to PC                                                    |  |  |  |