Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

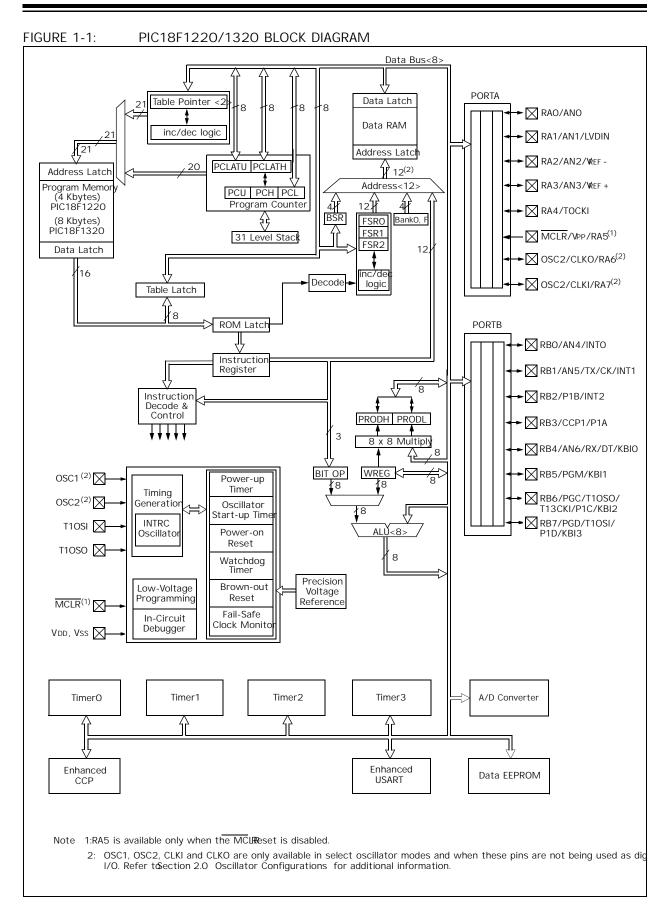

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 7x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1220-h-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

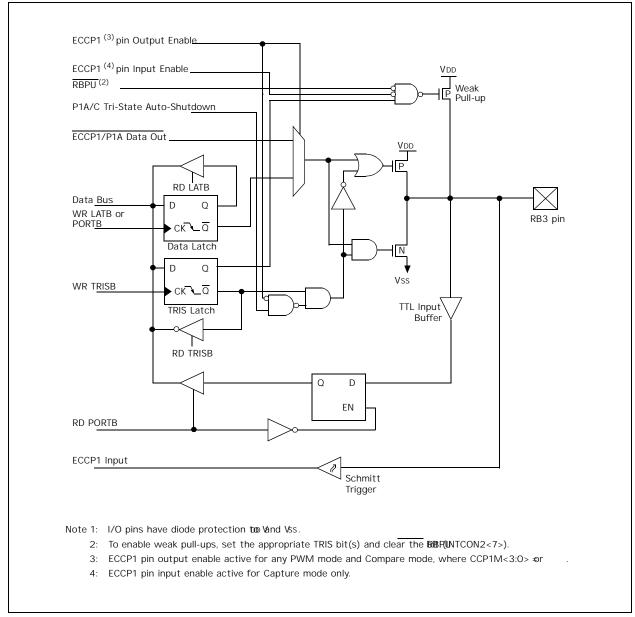

## 3.3.2 SEC\_IDLE MODE

In SEC\_IDLE mode, the CPU is disabled, but the peripherals continue to be clocked from the Timer1 oscillator. This mode is entered by setting the Idle bit, modifying bits, SCS1:SCSO = and executing a SLEEP instruction. When the clock source is switched (see Figure 3-5) to the Timer1 oscillator, the primary oscillator is shut down, the OSTS bit is cleared and the T1RUN bit is set.

Note: The Timer1 oscillator should already be running prior to entering SEC\_IDI E mode. If the T1OSCEN bit is not set when the SLEEP instruction is executed, he SLEEP instruction will be ignored nd entry to SEC\_IDLE mode will not occur. If the Timer1 oscillator is enabled, but hot yet running, peripheral clocks will be delayed until the oscillator has started; in such situations, initial oscillator operation is far from stable and unpredictable operation may result.

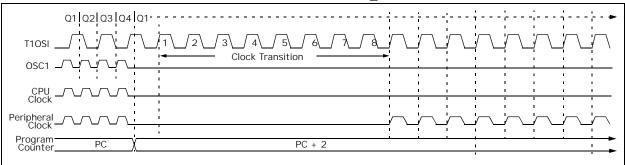

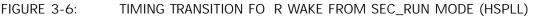

When a wake event occurs, the peripherals continue to be clocked from the Timer1 oscillator. After aR10 delay following the wake event, the CPU begins executing code, being clocked by the Timer1 oscillator. The microcontroller operates in SEC\_RUN mode until the primary clock becomes ready. When the primary clock becomes ready, a clock switchback to the primary clock occurs (seeFigure 3-6). When the clock switch is complete, the T1RUN bit is cleared, the OSTS bit is set and the primary clock is providing the system clock. The IDLEN and SCS bits are not affected by the wake-up. The Timer1 oscillator continues to run.

## 5.9.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given inTable 5-1 and Table 5-2 The SFRs can be classified into two sets: those associated with the core function and those related to the peripheral functions. Those registers related to the core are described in this section, while those related to the operation of the peripheral features are described in the section of that peripheral feature.

The SFRs are typically distributed among the peripherals whose functions they control.

The unused SFR locations will be unimplemented and read as 0 s.

| TABLE 5-1: | SPECIAL F               | UNCTION R | EGISTER N               | IAP FOR PIC | C18F1220/13 | 20 DEVICES | 5       |

|------------|-------------------------|-----------|-------------------------|-------------|-------------|------------|---------|

| Address    | Name                    | Address   | Name                    | Address     | Name        | Address    | Name    |

| FFFh       | TOSU                    | FDFh      | INDF2 <sup>(2)</sup>    | FBFh        | CCPR1H      | F9Fh       | IPR1    |

| FFEh       | TOSH                    | FDEh      | POSTINC2 <sup>(2)</sup> | FBEh        | CCPR1L      | F9Eh       | PIR1    |

| FFDh       | TOSL                    | FDDh      | POSTDEC2 <sup>(2)</sup> | FBDh        | CCP1CON     | F9Dh       | PIE1    |

| FFCh       | STKPTR                  | FDCh      | PREINC2 <sup>(2)</sup>  | FBCh        |             | F9Ch       |         |

| FFBh       | PCLATU                  | FDBh      | PLUSW2 <sup>(2)</sup>   | FBBh        |             | F9Bh       | OSCTUNE |

| FFAh       | PCLATH                  | FDAh      | FSR2H                   | FBAh        |             | F9Ah       |         |

| FF9h       | PCL                     | FD9h      | FSR2L                   | FB9h        |             | F99h       |         |

| FF8h       | TBLPTRU                 | FD8h      | STATUS                  | FB8h        |             | F98h       |         |

| FF7h       | TBLPTRH                 | FD7h      | TMROH                   | FB7h        | PWM1CON     | F97h       |         |

| FF6h       | TBLPTRL                 | FD6h      | TMROL                   | FB6h        | ECCPAS      | F96h       |         |

| FF5h       | TABLAT                  | FD5h      | TOCON                   | FB5h        |             | F95h       |         |

| FF4h       | PRODH                   | FD4h      |                         | FB4h        |             | F94h       |         |

| FF3h       | PRODL                   | FD3h      | OSCCON                  | FB3h        | TMR3H       | F93h       | TRISB   |

| FF2h       | INTCON                  | FD2h      | LVDCON                  | FB2h        | TMR3L       | F92h       | TRISA   |

| FF1h       | INTCON2                 | FD1h      | WDTCON                  | FB1h        | T3CON       | F91h       |         |

| FFOh       | INTCON3                 | FDOh      | RCON                    | FBOh        | SPBRGH      | F90h       |         |

| FEFh       | INDFO <sup>(2)</sup>    | FCFh      | TMR1H                   | FAFh        | SPBRG       | F8Fh       |         |

| FEEh       | POSTINCO <sup>(2)</sup> | FCEh      | TMR1L                   | FAEh        | RCREG       | F8Eh       |         |

| FEDh       | POSTDECO <sup>(2)</sup> | FCDh      | T1CON                   | FADh        | TXREG       | F8Dh       |         |

| FECh       | PREINCO <sup>(2)</sup>  | FCCh      | TMR2                    | FACh        | TXSTA       | F8Ch       |         |

| FEBh       | PLUSWO <sup>(2)</sup>   | FCBh      | PR2                     | FABh        | RCSTA       | F8Bh       |         |

| FEAh       | FSROH                   | FCAh      | T2CON                   | FAAh        | BAUDCTL     | F8Ah       | LATB    |

| FE9h       | FSROL                   | FC9h      |                         | FA9h        | EEADR       | F89h       | LATA    |

| FE8h       | WREG                    | FC8h      |                         | FA8h        | EEDATA      | F88h       |         |

| FE7h       | INDF1 <sup>(2)</sup>    | FC7h      |                         | FA7h        | EECON2      | F87h       |         |

| FE6h       | POSTINC1 (2)            | FC6h      |                         | FA6h        | EECON1      | F86h       |         |

| FE5h       | POSTDEC1 <sup>(2)</sup> | FC5h      |                         | FA5h        |             | F85h       |         |

| FE4h       | PREINC1 <sup>(2)</sup>  | FC4h      | ADRESH                  | FA4h        |             | F84h       |         |

| FE3h       | PLUSW1 <sup>(2)</sup>   | FC3h      | ADRESL                  | FA3h        |             | F83h       |         |

| FE2h       | FSR1H                   | FC2h      | ADCONO                  | FA2h        | IPR2        | F82h       |         |

| FE1h       | FSR1L                   | FC1h      | ADCON1                  | FA1h        | PIR2        | F81h       | PORTB   |

| FEOh       | BSR                     | FCOh      | ADCON2                  | FAOh        | PIE2        | F80h       | PORTA   |

Note 1: Unimplemented registers are read as.

2: This is not a physical register.

## 7.0 DATA EEPROM MEMORY

The data EEPROM is readable and writable during normal operation over the entime Vrange. The data memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers (SFR).

There are four SFRs used to read and write the program and data EEPROM memory. These registers are:

EECON1 EECON2 EEDATA EEADR

The EEPROM data memory allows byte read and write. When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write and EEADR holds the address of the EEPROM location being accessed. These devices have 256 bytes of data EEPROM with an address range from OOh to FFh.

The EEPROM data memory is rated for high erase/ write cycle endurance. A byte write automatically erases the location and writes the new data (erasebefore-write). The write time is controlled by an on-chip timer. The write time will vary with voltage and temperature, as well as from chip to chip. Please refer to parameter D122at/le 22-1 in Section 22.0 Electrical Characteristics ) for exact limits.

7.1 FFADR

The address register can address 256 bytes of data EEPROM.

## 7.2 EECON1 and EECON2 Registers

EECON1 is the control register for memory accesses.

EECON2 is not a physical register. Reading EECON2 will read all 0 s. The EECON2 register is used exclusively in the memory write and erase sequences.

Control bit, EEPGD, determines if the access will be to program or data EEPROM memory. When clear, operations will access the data EEPROM memory. When set, program memory is accessed. Control bit, CFGS, determines if the access will be to the Configuration registers or to program memory/data EEPROM memory. When set, subsequent operations access Configuration registers. When CFGS is clear, the EEPGD bit selects either program Flash or data EEPROM memory.

The WREN bit enables and disables erase and write operations. When set, erase and write operations are allowed. When clear, erase and write operations are disabled the WR bit cannot be set while the WREN bit is clear. This mechanism helps to prevent accidental writes to memory due to errant (unexpected) code execution.

Firmware should keep the WREN bit clear at all times, except when starting erase or write operations. Once firmware has set the WR bit, the WREN bit may be cleared. Clearing the WREN bit will not affect the operation in progress.

The WRERR bit is set when a write operation is interrupted by a Reset. In these situations, the user can check the WRERR bit and rewrite the location. It is necessary to reload the data and address registers (EEDATA and EEADR), as these registers have cleared as a result of the Reset.

Control bits, RD and WR, start read and erase/write operations, respectively. These bits are set by firmware and cleared by hardware at the completion of the operation.

The RD bit cannot be set when accessing program memory (EEPGD = 1). Program memory is read using table read instructions. Section 6.1 Table Reads and Table Writes regarding table reads.

Note: Interrupt flag bit, EEIF in the PIR2 register, is set when write is complete. It must be cleared in software.

| R/W-1/1                 | R/W-1/1                             | R/W-1/1         | R/W-1/1           | U-0        | R/W-1/1             | U-O R/W-1/                       |

|-------------------------|-------------------------------------|-----------------|-------------------|------------|---------------------|----------------------------------|

| RBPU                    | INTEDGO                             | INTEDG1         | INTEDG2           |            | TMROIP              | RBIP                             |

| oit 7                   |                                     |                 |                   |            |                     | bit C                            |

|                         |                                     |                 |                   |            |                     |                                  |

| Legend:<br>R = Readable | o hit                               | W = Writab      | la hit            | II – Unimr | plemented bit, read | 25.0                             |

| u = Bit is un           |                                     | x = Bit is u    |                   |            |                     | as 0<br>R/Value at all other Res |

| 1 = Bit is an           | •                                   | 0 = Bit is      |                   | 11711 – V  |                     |                                  |

|                         |                                     | 0 5.01          |                   |            |                     | ]                                |

| bit 7                   | RBPU : PORTE                        | 3 Pull-up Enal  | ble bit           |            |                     |                                  |

|                         | 1 = All PORT                        |                 |                   |            |                     |                                  |

|                         |                                     |                 | nabled by individ |            | tch values          |                                  |

| bit 6                   |                                     |                 | pt O Edge Selec   | t bit      |                     |                                  |

|                         | 1 = Interrupt<br>0 = Interrupt      |                 |                   |            |                     |                                  |

| bit 5                   | •                                   | •               | pt 1 Edge Selec   | t bit      |                     |                                  |

|                         | 1 = Interrupt                       |                 |                   |            |                     |                                  |

|                         | 0 = Interrupt                       | t on falling ed | lge               |            |                     |                                  |

| bit 4                   |                                     |                 | pt 2 Edge Selec   | t bit      |                     |                                  |

|                         | 1 = Interrupt<br>0 = Interrupt      |                 |                   |            |                     |                                  |

| bit 3                   | Unimplement                         | •               | •                 |            |                     |                                  |

| bit 2                   | •                                   |                 | nterrupt Priority | / bit      |                     |                                  |

|                         | 1 = High pric                       |                 |                   |            |                     |                                  |

|                         | 0 = Low prio                        | rity            |                   |            |                     |                                  |

| bit 1                   | Unimplemente                        |                 |                   |            |                     |                                  |

| bit O                   |                                     | •               | errupt Priority b | it         |                     |                                  |

|                         | 1 = High pric<br>0 = Low prio       |                 |                   |            |                     |                                  |

|                         |                                     | iity            |                   |            |                     |                                  |

| Note: Int               | terrupt flag bits                   | aro sot who     | n an interrunt    |            |                     |                                  |

|                         | ondition occurs,                    |                 |                   |            |                     |                                  |

| its                     | s corresponding                     | enable bit o    | r the Global      |            |                     |                                  |

|                         | terrupt Enable k<br>Isure the appro |                 |                   |            |                     |                                  |

|                         | e clear prior t                     |                 |                   |            |                     |                                  |

|                         | nis feature allow                   |                 |                   |            |                     |                                  |

REGISTER 9-2: INTCON2: INTERRUPT CONTROL REGISTER 2

# PIC18F1220/1320

| R/W-0/0        | U-0                                                                                                                                                               | U-0                                                        | R/W-0/0   | ) U-O        | R/W-0/         | /0 F     | R/W-0/0        | U-U     |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------|--------------|----------------|----------|----------------|---------|

| OSCFIF         |                                                                                                                                                                   |                                                            | EEIF      |              | LVDIF          | TMR3IF   |                |         |

| oit 7          |                                                                                                                                                                   |                                                            |           |              |                |          |                | bit C   |

|                |                                                                                                                                                                   |                                                            |           |              |                |          |                |         |

| Legend:        |                                                                                                                                                                   |                                                            |           |              |                |          |                |         |

| R = Readable   | bit                                                                                                                                                               | W = Writabl                                                | e bit     |              | plemented bit, |          |                |         |

| u = Bit is und | changed                                                                                                                                                           | x = Bit is u                                               | nknown    | -n/n = \     | /alue at POR a | nd BOR/V | /alue at all o | ther Re |

| 1 = Bit is set | et                                                                                                                                                                | 0 = Bit is                                                 | s cleared |              |                |          |                |         |

|                |                                                                                                                                                                   |                                                            |           |              |                |          |                |         |

| oit 7          |                                                                                                                                                                   | illator Fail Inte                                          |           |              |                |          |                |         |

|                |                                                                                                                                                                   |                                                            |           | t has change | ed to INTOSC ( | (must be | cleared in s   | oftware |

|                | •                                                                                                                                                                 | clock operatir                                             | •         |              |                |          |                |         |

| bit 6-5        | Unimplement                                                                                                                                                       | ted: Read as C                                             |           |              |                |          |                |         |

| bit 4          | EEIF: Data E                                                                                                                                                      | EEIF: Data EEPROM/Flash Write Operation Interrupt Flag bit |           |              |                |          |                |         |

|                | 1 = The write operation is complete (must be cleared in software)                                                                                                 |                                                            |           |              |                |          |                |         |

|                | 0 = The write operation is not complete or has not been started                                                                                                   |                                                            |           |              |                |          |                |         |

| bit 3          | Unimplement                                                                                                                                                       | ted: Read as C                                             |           |              |                |          |                |         |

| bit 2          | LVDIF: Low-Voltage Detect Interrupt Flag bit                                                                                                                      |                                                            |           |              |                |          |                |         |

|                | <ul> <li>1 = A low-voltage condition occurred (must be cleared in software)</li> <li>0 = The device voltage is above the Low-Voltage Detect trip point</li> </ul> |                                                            |           |              |                |          |                |         |

| bit 1          | TMR3IF: TMR3 Overflow Interrupt Flag bit                                                                                                                          |                                                            |           |              |                |          |                |         |

|                |                                                                                                                                                                   | egister overflo                                            |           |              | software)      |          |                |         |

|                |                                                                                                                                                                   | egister did not                                            |           |              | ·              |          |                |         |

| bit O          | Unimplement                                                                                                                                                       | ted: Read as 0                                             |           |              |                |          |                |         |

|                |                                                                                                                                                                   |                                                            |           |              |                |          |                |         |

## REGISTER 9-5: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

## 9.3 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Enable registers (PIE1, PIE2). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

REGISTER 9-6: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| U-O   | R/W-0/0 | R/W-0/0 | R/W-0 | /0 U-0 | R/W-0  | D/O R/W | /-0/0 R/ | ′W-0/0 |

|-------|---------|---------|-------|--------|--------|---------|----------|--------|

|       | ADIE    | RCIE    | TXIE  |        | CCP1IE | TMR2IE  | TMR1IE   |        |

| bit 7 |         |         |       |        |        |         | bit (    |        |

| Legend:              |                    |                                                       |

|----------------------|--------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit   | U = Unimplemented bit, read as O                      |

| u = Bit is unchanged | x = Bit is unknown | -n/n = Value at POR and BOR/Value at all other Resets |

| 1 = Bit is set       | 0 = Bit is cleared |                                                       |

| bit 7 | Unimplemented: Read as 0                                                                                                                  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ADIE: A/D Converter Interrupt Enable bit<br>= Enables the A/D interrupt<br>= Disables the A/D interrupt                                   |

| bit 5 | RCIE: EUSART Receive Interrupt Enable bit<br>= Enables the EUSART receive interrupt<br>= Disables the EUSART receive interrupt            |

| bit 4 | TXIE: EUSART Transmit Interrupt Enable bit<br>= Enables the EUSART transmit interrupt<br>= Disables the EUSART transmit interrupt         |

| bit 3 | Unimplemented: Read as 0                                                                                                                  |

| bit 2 | CCP1IE: CCP1 Interrupt Enable bit<br>= Enables the CCP1 interrupt<br>= Disables the CCP1 interrupt                                        |

| bit 1 | TMR2IE: TMR2 to PR2 Match Interrupt Enable bit<br>= Enables the TMR2 to PR2 match interrupt<br>= Disables the TMR2 to PR2 match interrupt |

| bit O | TMR1IE: TMR1 Overflow Interrupt Enable bit<br>= Enables the TMR1 overflow interrupt<br>= Disables the TMR1 overflow interrupt             |

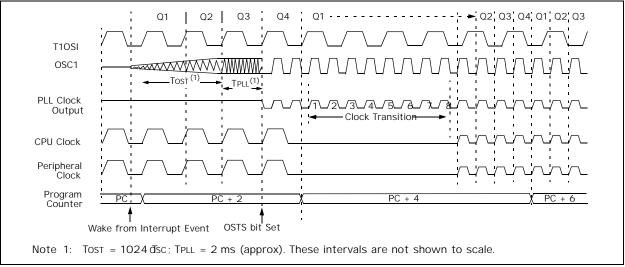

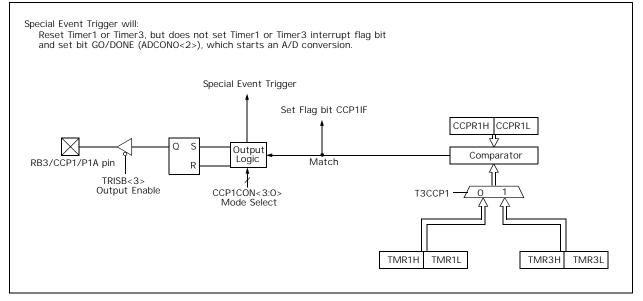

#### FIGURE 10-10: BLOCK DIAGRA M OF RB3/CCP1/P1A PIN

# PIC18F1220/1320

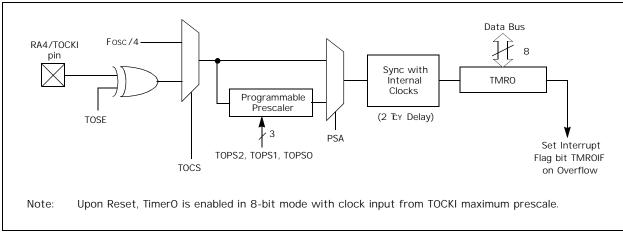

## FIGURE 11-1: TIMERO BLOCK DI AGRAM IN 8-BIT MODE

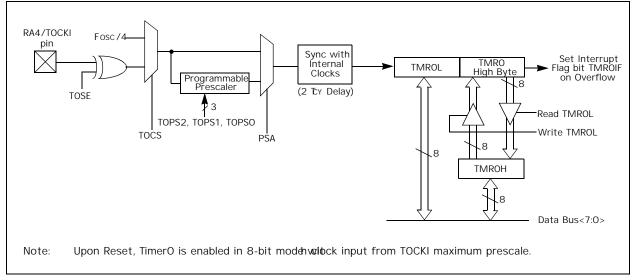

## FIGURE 11-2: TIMERO BLOCK DIAGRAM IN 16-BIT MODE

## 12.7 Using Timer1 as a Real-Time Clock

Adding an external LP oscillator to Timer1 (such as the one described inSection 12.2 Timer1 Oscillator, above), gives users the option to include RTC functionality to their applications. This is accomplished with an inexpensive watch crystal to provide an accurate time base and several lines of application code to calculate the time. When operating in Sleep mode and using a battery or supercapacitor as a power source, it can completely eliminate the need for a separate RTC device and battery backup.

The application code routinercisr, shown in Example 12-1, demonstrates a simple method to increment a counter at one-second intervals using an Interrupt Service Routine. Incrementing the TMR1 register pair to overflow, triggers the interrupt and calls the routine, which increments the seconds counter by one; additional counters for minutes and hours are incremented as the previous counter overflow.

Since the register pair is 16 bits wide, counting up to overflow the register directly from a 32.768 kHz clock would take two seconds. To force the overflow at the required one-second intervals, it is necessary to preload it; the simplest method is to set the MSb of TMR1H with æSF instruction. Note that the TMR1L register is never preloaded or altered; doing so may introduce cumulative error over many cycles.

For this method to be accurate, Timer1 must operate in Asynchronous mode and the Timer1 overflow interrupt must be enabled (PIE1<O>  $\pm$ ), as shown in the routine,RTCinit. The Timer1 oscillator must also be enabled and running at all times.

|               |                    | TIN AF OL O OL LIOUNIO A |                          |

|---------------|--------------------|--------------------------|--------------------------|

| EXAMPLE 12-1: | IMPLEMENTING A REA | l-TIME CLOCK USING A     | TIMER1 INTERRUPT SERVICE |

| RTCinit |        |              |   |                                             |

|---------|--------|--------------|---|---------------------------------------------|

|         | MOVLW  | 0x80         |   | Preload TMR1 register pair                  |

|         | MOVWF  | TMR1H        | ; | for 1 second overflow                       |

|         | CLRF   | TMR1L        |   |                                             |

|         | MOVLW  | b'00001111'  | ; | Configure for external clock,               |

|         | MOVWF  | T1OSC        | ; | Asynchronous operation, external oscillator |

|         | CLRF   | secs         | ; | Initialize timekeeping registers            |

|         | CLRF   | mins         | ; |                                             |

|         | MOVLW  | .12          |   |                                             |

|         | MOVWF  | hours        |   |                                             |

|         | BSF    | PIE1, TMR1IE | ; | Enable Timer1 interrupt                     |

|         | RETURN |              |   |                                             |

| RTCisr  |        |              |   |                                             |

|         | BSF    |              |   | Preload for 1 sec overflow                  |

|         | BCF    | PIR1, TMR1IF | ; | Clear interrupt flag                        |

|         | INCF   | secs, F      | ; | Increment seconds                           |

|         | MOVLW  | .59          | ; | 60 seconds elapsed?                         |

|         | CPFSGT | secs         |   |                                             |

|         | RETURN |              |   | No, done                                    |

|         | CLRF   | secs         | ; | Clear seconds                               |

|         | INCF   | mins, F      | ; | Increment minutes                           |

|         | MOVLW  | .59          | ; | 60 minutes elapsed?                         |

|         | CPFSGT | mins         |   |                                             |

|         | RETURN |              |   | No, done                                    |

|         | CLRF   | mins         | ; | clear minutes                               |

|         | INCF   | hours, F     |   | Increment hours                             |

|         | MOVLW  | .23          | ; | 24 hours elapsed?                           |

|         | CPFSGT | hours        |   |                                             |

|         | RETURN |              | ; | No, done                                    |

|         | MOVLW  | .01          | ; | Reset hours to 1                            |

|         | MOVWF  | hours        |   |                                             |

|         | RETURN |              | ; | Done                                        |

|         |        |              |   |                                             |

## 15.0 ENHANCED CAPTURE/ COMPARE/PWM (ECCP) MODULE

The Enhanced CCP module is implemented as a standard CCP module with Enhanced PWM capabilities. These capabilities allow for two or four output channels, user-selectable polarity, dead-band control and automatic shutdown and restart and are discussed in detail i $\mathfrak{B}$ ection 15.5 Enhanced PWM Mode .

The control register for CCP1 is show Reignister 15-1

In addition to the expanded functions of the CCP1CON register, the ECCP module has two additional registers associated with Enhanced PWM operation and auto-shutdown features:

PWM1CON ECCPAS

#### REGISTER 15-1: CCP1CON REGISTER FOR ENHANCED CCP OPERATION

| R/W-0/0 | U-0  | R/W-0/0 | R/W-0/ | '0 R/W-0 | D/O R/W- | 0/0 R/V | N-0/0 R | W-0/0 |

|---------|------|---------|--------|----------|----------|---------|---------|-------|

| P1M1    | P1M0 | DC1B1   | DC1BO  | CCP1M3   | CCP1M2   | CCP1M1  | CCP1M0  |       |

| bit 7   |      |         |        |          |          |         | bit C   |       |

| Legend:              |                    |                                                       |

|----------------------|--------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit   | U = Unimplemented bit, read as O                      |

| u = Bit is unchanged | x = Bit is unknown | -n/n = Value at POR and BOR/Value at all other Resets |

| 1 = Bit is set       | 0 = Bit is cleared |                                                       |

| bit 7-6 | P1M<1:0>:PWM Output Configuration bits                                                                                                                               |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | I <u>f CCP1M&lt;3:2&gt; =</u>                                                                                                                                        |

|         | xx = P1A assigned as Capture/Compare input; P1B, P1C, P1D assigned as port pins                                                                                      |

|         | $\frac{ \text{f CCP1M} < 3:2 > = :}{\text{Single output: D1A modulated D1B D1C D1D assigned as part pins}}$                                                          |

|         | <ul> <li>Single output; P1A modulated; P1B, P1C, P1D assigned as port pins</li> <li>Full-bridge output forward; P1Ddmlated; P1A active; P1B, P1C inactive</li> </ul> |

|         | = Half-bridge output; P1A, P1B modulated with dead-band control; P1C, P1D assigned as                                                                                |

|         | port pins                                                                                                                                                            |

|         | = Full-bridge output reverse; P1B modulated; P1C active; P1A, P1D inactive                                                                                           |

| bit 5-4 | DC1B<1:0>: PWM Duty Cycle Least Significant bits                                                                                                                     |

|         | Capture mode:                                                                                                                                                        |

|         | Unused.                                                                                                                                                              |

|         | Compare mode:                                                                                                                                                        |

|         | Unused.                                                                                                                                                              |

|         | <u>PWM mode</u> :<br>These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPR1L.                                                          |

|         |                                                                                                                                                                      |

| bit 3-0 | CCP1M<3:0>: ECCP1 Mode Select bits                                                                                                                                   |

|         | 0000 = Capture/Compare/PWM off (resets ECCP module)<br>0001 = Unused (reserved)                                                                                      |

|         | 0010 = Compare mode, toggle output on match (ECCP1IF bit is set)                                                                                                     |

|         | 0011 = Unused (reserved)                                                                                                                                             |

|         | 0100 = Capture mode, every falling edge                                                                                                                              |

|         | 0101 = Capture mode, every rising edge                                                                                                                               |

|         | 0110 = Capture mode, every 4th rising edge                                                                                                                           |

|         | 0111 = Capture mode, every 16th rising edge                                                                                                                          |

|         | 1000 = Compare mode, set output on match (ECCP1IF bit is set)<br>1001 = Compare mode, clear output on match (ECCP1IF bit is set)                                     |

|         | 1010 = Compare mode, generate software interrupt on match (ECCP1IF bit is set,                                                                                       |

|         | ECCP1 pin returns to port pin operation)                                                                                                                             |

|         | 1011 = Compare mode, trigger special event (ECCP1IF bit is set; ECCP resets TMR1 or                                                                                  |

|         | TMR3 and starts an A/D conversion if the A/D module is enabled)                                                                                                      |

|         | 1100 = PWM mode; P1A, P1C active-high; P1B, P1D active-high                                                                                                          |

|         | 1101 = PWM mode; P1A, P1C active-high; P1B, P1D active-low                                                                                                           |

|         | 1110 = PWM mode; P1A, P1C active-low; P1B, P1D active-high<br>1111 = PWM mode; P1A, P1C active-low; P1B, P1D active-low                                              |

|         | TITT - T WINTHOUG, TTA, FTC active-low, FTD, FTD active-low                                                                                                          |

## FIGURE 15-2: COMPARE MODE OPERAT ION BLOCK DIAGRAM

#### TABLE 15-3: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, TIMER1 AND TIMER3

| Name    | Bit 7                                                                       | Bit 6       | Bit 5    | Bit 4       | Bit 3       | Bit 2       | Bit 1       | Bit C  | Valu<br>POR, | e on<br>BOR | all c | e on<br>other<br>sets |

|---------|-----------------------------------------------------------------------------|-------------|----------|-------------|-------------|-------------|-------------|--------|--------------|-------------|-------|-----------------------|

| INTCON  | GIE/GIEH                                                                    | PEIE/GIEL   | TMROIE   | INTOIE      | RBIE        | TMROIF      | INTOIF      | RBIF   | 0000         | 000x        | 0000  | 000u                  |

| PIR1    |                                                                             | ADIF        | RCIF     | TXIF        |             | CCP1IF      | TMR2IF      | TMR1IF | -000         | -000        | -000  | -000                  |

| PIE1    |                                                                             | ADIE        | RCIE     | TXIE        |             | CCP1IE      | TMR2IE      | TMR1IE | -000         | -000        | -000  | -000                  |

| IPR1    |                                                                             | ADIP        | RCIP     | TXIP        |             | CCP1IP      | TMR2IP      | TMR1IP | -111         | -111        | -111  | -111                  |

| TRISB   | PORTB Data Direction Register                                               |             |          |             |             |             |             |        | 1111         | 1111        | 1111  | 1111                  |

| TMR1L   | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |             |          |             |             |             |             |        | xxxx         | xxxx        | uuuu  | uuuu                  |

| TMR1H   | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |             |          |             |             |             |             |        | xxxx         | xxxx        | uuuu  | uuuu                  |

| T1CON   | RD16 T1RUN T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON                     |             |          |             |             |             | 0000        | 0000   | uuuu         | uuuu        |       |                       |

| CCPR1L  | Capture/Compare/PWM Register 1 (LSB)                                        |             |          |             |             |             |             |        | xxxx         | xxxx        | uuuu  | uuuu                  |

| CCPR1H  | Capture/Compare/PWM Register 1 (MSB)                                        |             |          |             |             |             |             |        | xxxx         | xxxx        | uuuu  | uuuu                  |

| CCP1CON | P1M1                                                                        | P1M0        | DC1B1    | DC1BO       | CCP1M3      | CCP1M2      | CCP1M1      | CCP1M0 | 0000         | 0000        | 0000  | 0000                  |

| TMR3L   | Holding Register for the Least Significant Byte of the 16-bit TMR3 Register |             |          |             |             |             |             |        | xxxx         | xxxx        | uuuu  | uuuu                  |

| TMR3H   | Holding R                                                                   | egister for | the Most | Significant | Byte of the | e 16-bit TN | /IR3 Regist | er     | xxxx         | xxxx        | uuuu  | uuuu                  |

| T3CON   | RD16                                                                        | -           | 3CKPS1 1 | 3CKPS0      | T3CCP1 1    | 3SYNC       | TMR3CS      | TMR30N | 0-00         | 0000        | u-uu  | uuuu                  |

| ADCONO  | VCFG1                                                                       | VCFGO       |          | CHS2        | CHS1        | CHSO        | GO/DONE     | ADON   |              |             |       |                       |

Legend:  $\mathbf{x}$  = unknown<sub>u</sub> = unchanged, = unimplemented, read as. Shaded cells are not **ed** by Capture and Timer1.

## 15.5 Enhanced PWM Mode

The Enhanced PWM Mode provides additional PWM output options for a broader range of control applications. The module is an upwardly compatible version of the standard CCP module and offers up to four outputs, designated P1A through P1D. Users are also able to select the polarity of the signal (either active-high or active-low). The module s output mode and polarity are configured by setting the P1M1:P1MO and CCP1M3CCP1MO bits of the CCP1CON register (CCP1CON<7:6> and CCP1CON<3:0>, respectively).

Figure 15-3shows a simplified block diagram of PWM operation. All control regers are double-buffered and are loaded at the beginning of a new PWM cycle (the period boundary when Timer2 resets) in order to prevent glitches on any of the outputs. The exception is the PWM Delay register, ECCP1DEL, which is loaded at either the duty cycle boundary or the boundary period (whichever comes first). Because of the buffering, the module waits until the assigned timer resets instead of starting immediately. This means that Enhanced PWM waveforms do not exactly match the standard PWM waveforms, but are instead offset by one full instruction cycles() H

As before, the user must manually configure the appropriate TRIS bits for output.

#### 15.5.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the equation:

#### EQUATION 15-1: PWM PERIOD

$$PWM Period = [(PR2) + 1] \bullet 4 \bullet TOSC \bullet$$

(TMR2 Prescale Value)

PWM frequency is defined as 1/[PWM period]. When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

#### TMR2 is cleared

The CCP1 pin is set (if PWM duty cycle = 0%, the CCP1 pin will not be set)

The PWM duty cycle is copied from CCPR1L into CCPR1H

Note: The Timer2 postscaler (section 13.0 Timer2 Module ) is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

#### 15.5.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The PWM duty cycle is calculated by the equation:

PWM Duty Cycle = (CCPR1L:CCP1CON<5:4>) • Tosc • (TMR2 Prescale Value)

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not copied into CCPR1H until a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

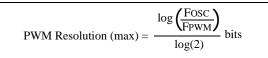

The CCPR1H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation. When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or two bits of the TMR2 prescaler, the CCP1 pin is cleared. The maximum PWM resolution (bits) for a given PWM frequency is given by the equation:

#### EQUATION 15-3: PWM RESOLUTION

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

#### 15.5.3 PWM OUTPUT CONFIGURATIONS

The P1M1:P1MO bits in the CCP1CON register allow one of four configurations:

Single Output Half-Bridge Output Full-Bridge Output, Forward mode

Full-Bridge Output, Reverse mode

The Single Output mode is the Standard PWM mode discussed inSection 15.5 Enhanced PWM Mode. The Half-Bridge and Full-Bridge Output modes are covered in detail in the sections that follow.

The general relationship of the outputs in all configurations is summarized Fingure 15-4

|  | TABLE 15-4: | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz |

|--|-------------|---------------------------------------------------|

|--|-------------|---------------------------------------------------|

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kH | z 312.50 k | Hz 416.67 k |

|----------------------------|----------|----------|-----------|-----------|------------|-------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1           |

| PR2 Value                  | FFh      | FFh      | FFh       | 3Fh       | 1Fh        | 17h         |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7          | 6.58        |

| R/W-0/0       | R/W-0/0                                                                         | R/W-0/0                              | R/W-0/       | ′0 R/V      | V-0/0           | R/W-0/0        | R-1/1    | R/V   |

|---------------|---------------------------------------------------------------------------------|--------------------------------------|--------------|-------------|-----------------|----------------|----------|-------|

| CSRC          | TX9                                                                             | TXEN <sup>(1)</sup>                  | SYNC         | SENDB       | BRGH            | TRMT           | TX9D     |       |

| it 7          |                                                                                 |                                      |              |             |                 | ·              | ł        | oit O |

|               |                                                                                 |                                      |              |             |                 |                |          |       |

| egend:        |                                                                                 |                                      |              |             |                 |                |          |       |

| = Readable    | bit                                                                             | W = Writable                         | bit          | U = Unin    | nplemente       | d bit, read as | 0        |       |

| = Bit is und  | Bit is unchanged $x = Bit$ is unknown $-n/n = Value$ at POR and BOR/Value at al |                                      |              |             | alue at all oth | her Re         |          |       |

| 1 = Bit is se | et                                                                              | 0 = Bit is c                         | leared       |             |                 |                |          |       |

|               |                                                                                 |                                      |              |             |                 |                |          |       |

| it 7          |                                                                                 | Source Select k                      | DIT          |             |                 |                |          |       |

|               | Asynchronous<br>Don t care.                                                     | <u>s mode</u> :                      |              |             |                 |                |          |       |

|               | Synchronous                                                                     | mode:                                |              |             |                 |                |          |       |

|               | 1 = Master r                                                                    | node (clock ger                      |              |             | BRG)            |                |          |       |

|               |                                                                                 | de (clock from                       |              | urce)       |                 |                |          |       |

| it 6          |                                                                                 | ansmit Enable b                      |              |             |                 |                |          |       |

|               |                                                                                 | 9-bit transmissi<br>3-bit transmissi |              |             |                 |                |          |       |

| it 5          |                                                                                 | nit Enable b <sup>it)</sup>          | OIT          |             |                 |                |          |       |

| 11 0          | 1 = Transmit                                                                    |                                      |              |             |                 |                |          |       |

|               | 0 = Transmit                                                                    |                                      |              |             |                 |                |          |       |

| it 4          | SYNC: EUSAR                                                                     | T Mode Select                        | bit          |             |                 |                |          |       |

|               | 1 = Synchror                                                                    |                                      |              |             |                 |                |          |       |

|               | 0 = Asynchro                                                                    |                                      |              |             |                 |                |          |       |

| it 3          |                                                                                 | l Break Charact                      | er bit       |             |                 |                |          |       |

|               | Asynchronous                                                                    | <u>s mode</u> :<br>nc Break on nex   | t transmiss  | ion (cleare | d by hard       | ware upon com  | nletion) |       |

|               |                                                                                 | ak transmission                      |              |             | a by nara       |                |          |       |

|               | <u>Synchronous</u>                                                              | mode:                                |              |             |                 |                |          |       |

|               | Don t care.                                                                     |                                      |              |             |                 |                |          |       |

| it 2          | -                                                                               | Baud Rate Selec                      | ct bit       |             |                 |                |          |       |

|               | Asynchronous<br>1 = High spe                                                    |                                      |              |             |                 |                |          |       |

|               | 0 = Low spece                                                                   |                                      |              |             |                 |                |          |       |

|               | Synchronous                                                                     |                                      |              |             |                 |                |          |       |

|               | Unused in thi                                                                   | s mode.                              |              |             |                 |                |          |       |

| it 1          |                                                                                 | nit Shift Regist                     | er Status bi | t           |                 |                |          |       |

|               | 1 = TSR Idle                                                                    | ,                                    |              |             |                 |                |          |       |

| it O          | 0 = TSR busy                                                                    | /<br>t of Transmit Da                | 1            |             |                 |                |          |       |

| n U           |                                                                                 | ess/data bit or a                    |              |             |                 |                |          |       |

|               |                                                                                 |                                      |              |             |                 |                |          |       |

| lote 1: SRE   | EN/CREN overri                                                                  | ides TXEN in Sy                      | nc mode.     |             |                 |                |          |       |

REGISTER 16-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

#### 16.3.2 EUSART ASYNCHRONOUS RECEIVER

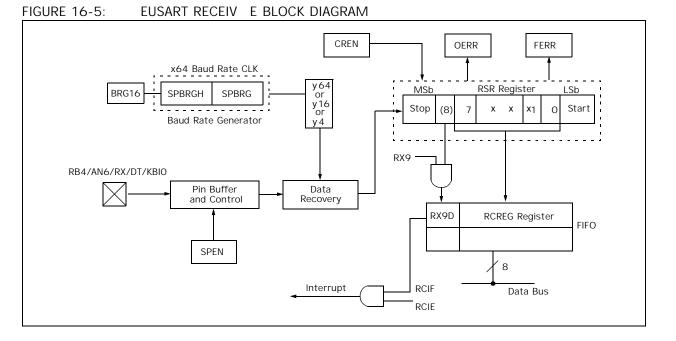

The receiver block diagram is shown Fingure 16-5 The data is received on the RB4/AN6/RX/DT/KBIO pin and drives the data recovery block. The data recovery block is actually a high-speed shifter, operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or soft. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, set enable bit RCIE.

- 4. If 9-bit reception is desired, set bit RX9.

- 5. Enable the reception by setting bit CREN.

- 6. Flag bit, RCIF, will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 7. Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

## 16.3.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are required, set the RCEN bit and select the desired priority level with the RCIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- 5. Set the ADDEN bit to enable address detect.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF bit will be set when reception is complete. The interrupt will be Acknowledged if the RCIE and GIE bits are set.

- 8. Read the RCSTA register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 9. Read RCREG to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

| R                | R          | R                  | R       | R                                              | R    | R    | R     |  |  |  |

|------------------|------------|--------------------|---------|------------------------------------------------|------|------|-------|--|--|--|

| DEV2             | DEV1       | DEVO               | REV4    | REV3                                           | REV2 | REV1 | REVO  |  |  |  |

| bit 7            |            | -                  |         |                                                |      |      | bit C |  |  |  |

|                  |            |                    |         |                                                |      |      |       |  |  |  |

| Legend:          |            |                    |         |                                                |      |      |       |  |  |  |

| R = Readable bit |            | W = Writak         | ole bit | U = Unimplemented bit, read as 0               |      |      |       |  |  |  |

| u = Bit is und   | changed    | x = Bit is         | unknown | -n/n = Value at POR and BOR/Value at all other |      |      |       |  |  |  |

| 1 = Bit is se    | et         | 0 = Bit is cleared |         |                                                |      |      |       |  |  |  |

|                  |            |                    |         |                                                |      |      |       |  |  |  |

| bit 7-5          | DEV<2:0>:[ | Device ID bits     |         |                                                |      |      |       |  |  |  |

|                  | = PIC18    | 3F1220             |         |                                                |      |      |       |  |  |  |

= PIC18F1320 bit 4-0 REV<4:0>: Revision ID bits These bits are used to indicate the device revision.

REGISTER 19-13: DEVID2: DEVICE ID REGISTER 2 FOR PIC18F1220/1320 DEVICES

|       | K    | ĸ    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV10 | DEV9 | DEV8 | DEV7 | DEV6 | DEV5 | DEV4 | DEV3  |

| bit 7 |      |      |      |      |      |      | bit C |

| Legend:              |                    |                                                       |

|----------------------|--------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit   | U = Unimplemented bit, read as O                      |

| u = Bit is unchanged | x = Bit is unknown | -n/n = Value at POR and BOR/Value at all other Resets |

| 1 = Bit is set       | 0 = Bit is cleared |                                                       |

bit 7-0 DEV<10:3>: Device ID bits

These bits are used with the DEV<2:0> bits in the Device ID Register 1 to identify the part number.

= PIC18F1220/1320 devices

Note 1: These values for DEV<10:3> may be shared with other devices. The specific device is always identified by using the entire DEV<10:0> bit sequence.

# PIC18F1220/1320

| MO                | /LW         | Move lite          | eral to N    | N   |       |           |

|-------------------|-------------|--------------------|--------------|-----|-------|-----------|

| Syn               | tax:        | [label]            | MOVL         | Nł  | <     |           |

| Ope               | rands:      | 0 dk d2            | 55           |     |       |           |

| Ope               | ration:     | ko W               |              |     |       |           |

| Stat              | us Affected | : None             |              |     |       |           |

| Enco              | oding:      |                    |              |     |       |           |

| Des               | cription:   | The 8-b<br>into W. | it litera    | l k | is Ic | aded      |

| Wor               | ds:         | 1                  |              |     |       |           |

| Сус               | les:        | 1                  |              |     |       |           |

| Q Cycle Activity: |             |                    |              |     |       |           |

|                   | Q1          | Q2                 | Q3           | 3   |       | Q4        |

|                   | Decode      | Read<br>literal k  | Proce<br>Dat |     | Wi    | rite to W |

|                   | 1 1         |                    |              |     |       |           |

| Example: MOVLW 0x5A |

|---------------------|

|---------------------|

After Instruction

W = Ox5A

| MOVWF            |                                                                                                                                                                                                                                                           | Move W                | to f        |    |       |                 |   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------|----|-------|-----------------|---|

| Syntax:          |                                                                                                                                                                                                                                                           | [label]               | MOVW        | /F | f [,; | a]              |   |

| Operands         | 5:                                                                                                                                                                                                                                                        | 0 df d25<br>a • [0,1] | 5           |    |       |                 |   |

| Operation        | า:                                                                                                                                                                                                                                                        | (W)of                 |             |    |       |                 |   |

| Status Af        | fected                                                                                                                                                                                                                                                    | : None                |             |    |       |                 |   |

| Encoding         | :                                                                                                                                                                                                                                                         |                       |             |    |       |                 |   |

| Descripti        | Description: Move data from W to register f<br>Location f can be anywhere in th<br>256-byte bank. If a ds, the<br>Access Bank will be selected, over<br>riding the BSR value. If a 1∓ then<br>the bank will be selected as per th<br>BSR value (default). |                       |             |    |       |                 |   |

| Words:           |                                                                                                                                                                                                                                                           | 1                     |             |    |       |                 |   |

| Cycles:          |                                                                                                                                                                                                                                                           | 1                     |             |    |       |                 |   |

| Q Cycle          | Q Cycle Activity:                                                                                                                                                                                                                                         |                       |             |    |       |                 |   |

| (                | 21                                                                                                                                                                                                                                                        | Q2                    | Q           | 3  |       | Q4              |   |

| De               | code                                                                                                                                                                                                                                                      | Read<br>register f    | Proc<br>Dat |    |       | Write<br>gister | f |

| <u>Example</u> : |                                                                                                                                                                                                                                                           | MOVWF                 | REG         |    |       |                 |   |

Before Instruction W = Ox4F REG = OxFF After Instruction W = Ox4F REG = Ox4F

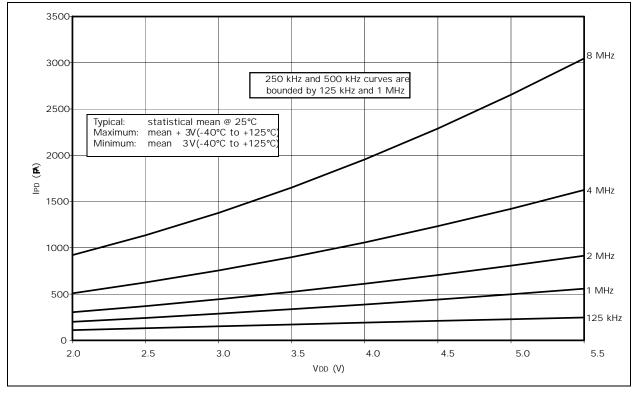

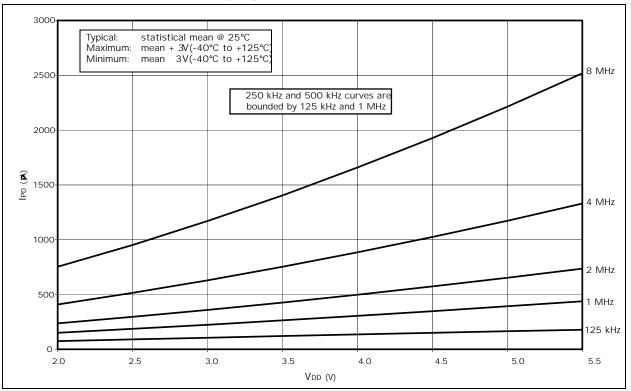

## 22.2 DC Characteristics: Power-Down and Supply Current PIC18F1220/1320 (Industrial) PIC18LF1220/1320 (Industrial) (Continued)

| PIC18LF1220/1320<br>(Industrial)          |                                      | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature -40° <b>C</b> TA d+85°C for industrial                          |       |              |            |              |                                  |  |

|-------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------|------------|--------------|----------------------------------|--|

| PIC18F1220/1320<br>(Industrial, Extended) |                                      | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature -40°CTA d+85°C for industrial<br>-40°C dTA d+125°C for extended |       |              |            |              |                                  |  |

| Param<br>No.                              | Device                               | Тур.                                                                                                                                             | Max.  | Units        | Conditions |              |                                  |  |

|                                           | Supply Current (bD) <sup>(2,3)</sup> |                                                                                                                                                  |       |              |            |              |                                  |  |

|                                           | PIC18LF1220/132                      | 0 415                                                                                                                                            | 60    | 0 <b>F</b> A | -40°C      | VDD = 2.0V   |                                  |  |

|                                           |                                      | 425                                                                                                                                              | 600   | FA           | +25°C      |              |                                  |  |

|                                           |                                      | 435                                                                                                                                              | 600   | FA           | +85°C      |              |                                  |  |

|                                           | PIC18LF1220/132                      | 0 0.8                                                                                                                                            | 7 1.C | mA           | -40°C      |              |                                  |  |

|                                           |                                      | 0.75                                                                                                                                             | 1.0   | mA           | +25°C      | 10/10 = 3.0V | Fosc = 4 MHz<br>(PRI RUN mode,   |  |

|                                           |                                      | 0.75                                                                                                                                             | 1.0   | mA           | +85°C      |              | EC oscillator)                   |  |

|                                           | All devices                          | 1.6                                                                                                                                              | 2.0   | mA           | -40°C      |              |                                  |  |

|                                           |                                      | 1.6                                                                                                                                              | 2.0   | mA           | +25°C      | VDD = 5.0V   |                                  |  |

|                                           |                                      | 1.5                                                                                                                                              | 2.0   | mA           | +85°C      | 100 - 3.01   |                                  |  |

|                                           | Extended devices                     | 5 1.5                                                                                                                                            | 2.0   | mA           | +125°C     |              |                                  |  |

|                                           | Extended devices                     | 6.3                                                                                                                                              | 9.0   | mA           | +125°C     | DW = 4.2V    | Fosc = 25 MHz                    |  |

|                                           |                                      | 9.7                                                                                                                                              | 10.0  | mA           | +125°C     | 10 = 5.0V    | (PRI_RUN mode,<br>EC oscillator) |  |