Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

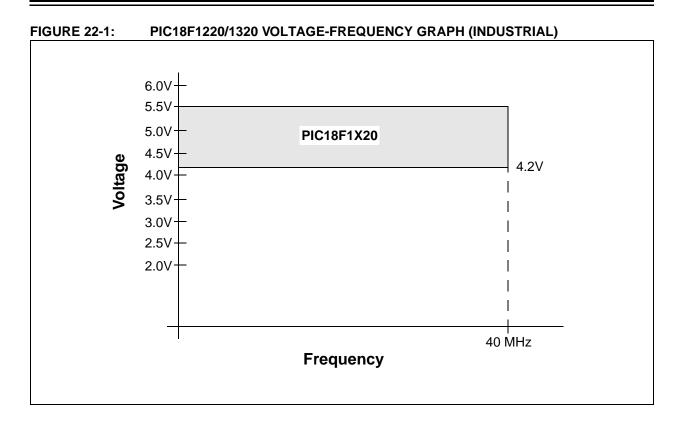

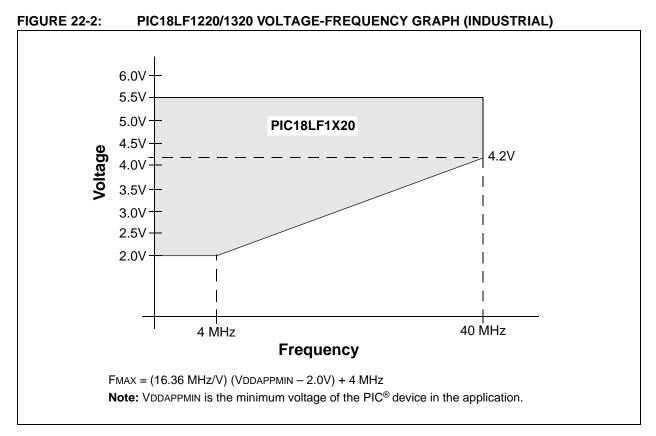

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 7x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1220-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.3 Details on Individual Family Members

Devices in the PIC18F1220/1320 family are available in 18-pin, 20-pin and 28-pin packages. A block diagram for this device family is shown in Figure 1-1.

The devices are differentiated from each other only in the amount of on-chip Flash program memory (4 Kbytes for the PIC18F1220 device, 8 Kbytes for the PIC18F1320 device). These and other features are summarized in Table 1-1. A block diagram of the PIC18F1220/1320 device architecture is provided in Figure 1-1. The pinouts for this device family are listed in Table 1-2.

# TABLE 1-1:DEVICE FEATURES

| Features                             | PIC18F1220                                                                                          | PIC18F1320                                                                                          |

|--------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Operating Frequency                  | DC – 40 MHz                                                                                         | DC – 40 MHz                                                                                         |

| Program Memory (Bytes)               | 4096                                                                                                | 8192                                                                                                |

| Program Memory (Instructions)        | 2048                                                                                                | 4096                                                                                                |

| Data Memory (Bytes)                  | 256                                                                                                 | 256                                                                                                 |

| Data EEPROM Memory (Bytes)           | 256                                                                                                 | 256                                                                                                 |

| Interrupt Sources                    | 15                                                                                                  | 15                                                                                                  |

| I/O Ports                            | Ports A, B                                                                                          | Ports A, B                                                                                          |

| Timers                               | 4                                                                                                   | 4                                                                                                   |

| Enhanced Capture/Compare/PWM Modules | 1                                                                                                   | 1                                                                                                   |

| Serial Communications                | Enhanced USART                                                                                      | Enhanced USART                                                                                      |

| 10-bit Analog-to-Digital Module      | 7 input channels                                                                                    | 7 input channels                                                                                    |

| Resets (and Delays)                  | POR, BOR,<br>RESET Instruction, Stack Full,<br>Stack Underflow (PWRT, OST),<br>MCLR (optional), WDT | POR, BOR,<br>RESET Instruction, Stack Full,<br>Stack Underflow (PWRT, OST),<br>MCLR (optional), WDT |

| Programmable Low-Voltage Detect      | Yes                                                                                                 | Yes                                                                                                 |

| Programmable Brown-out Reset         | Yes                                                                                                 | Yes                                                                                                 |

| Instruction Set                      | 75 Instructions                                                                                     | 75 Instructions                                                                                     |

| Packages                             | 18-pin SDIP<br>18-pin SOIC<br>20-pin SSOP<br>28-pin QFN                                             | 18-pin SDIP<br>18-pin SOIC<br>20-pin SSOP<br>28-pin QFN                                             |

# 3.0 POWER MANAGED MODES

The PIC18F1220/1320 devices offer a total of six operating modes for more efficient power management (see Table 3-1). These provide a variety of options for selective power conservation in applications where resources may be limited (i.e., battery powered devices).

There are three categories of power managed modes:

- Sleep mode

- Idle modes

- Run modes

These categories define which portions of the device are clocked and sometimes, what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or INTOSC multiplexer); the Sleep mode does not use a clock source.

The clock switching feature offered in other PIC18 devices (i.e., using the Timer1 oscillator in place of the primary oscillator) and the Sleep mode offered by all PIC<sup>®</sup> devices (where all system clocks are stopped) are both offered in the PIC18F1220/1320 devices (SEC\_RUN and Sleep modes, respectively). However, additional power managed modes are available that allow the user greater flexibility in determining what portions of the device are operating. The power managed modes are event driven; that is, some specific event must occur for the device to enter or (more particularly) exit these operating modes.

For PIC18F1220/1320 devices, the power managed modes are invoked by using the existing SLEEP instruction. All modes exit to PRI\_RUN mode when triggered by an interrupt, a Reset or a WDT time-out (PRI\_RUN mode is the normal full-power execution mode; the CPU and peripherals are clocked by the primary oscillator source). In addition, power managed Run modes may also exit to Sleep mode, or their corresponding Idle mode.

#### 3.1 Selecting Power Managed Modes

Selecting a power managed mode requires deciding if the CPU is to be clocked or not and selecting a clock source. The IDLEN bit controls CPU clocking, while the SCS1:SCS0 bits select a clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 3-1.

#### 3.1.1 CLOCK SOURCES

The clock source is selected by setting the SCS bits of the OSCCON register (Register 2-2). Three clock sources are available for use in power managed Idle modes: the primary clock (as configured in Configuration Register 1H), the secondary clock (Timer1 oscillator) and the internal oscillator block. The secondary and internal oscillator block sources are available for the power managed modes (PRI\_RUN mode is the normal full-power execution mode; the CPU and peripherals are clocked by the primary oscillator source).

|          | OSCCON Bits  |                    | Module          | Clocking |                                                                                                            |

|----------|--------------|--------------------|-----------------|----------|------------------------------------------------------------------------------------------------------------|

| Mode     | IDLEN<br><7> | SCS1:SCS0<br><1:0> | CPU Perinherals |          | Available Clock and Oscillator Source                                                                      |

| Sleep    | 0            | 00                 | Off             | Off      | None – All clocks are disabled                                                                             |

| PRI_RUN  | 0            | 00                 | Clocked         | Clocked  | Primary – LP, XT, HS, HSPLL, RC, EC, INTRC <sup>(1)</sup><br>This is the normal full-power execution mode. |

| SEC_RUN  | 0            | 01                 | Clocked         | Clocked  | Secondary – Timer1 Oscillator                                                                              |

| RC_RUN   | 0            | 1x                 | Clocked         | Clocked  | Internal Oscillator Block <sup>(1)</sup>                                                                   |

| PRI_IDLE | 1            | 00                 | Off             | Clocked  | Primary – LP, XT, HS, HSPLL, RC, EC                                                                        |

| SEC_IDLE | 1            | 01                 | Off             | Clocked  | Secondary – Timer1 Oscillator                                                                              |

| RC_IDLE  | 1            | 1x                 | Off             | Clocked  | Internal Oscillator Block <sup>(1)</sup>                                                                   |

#### TABLE 3-1: POWER MANAGED MODES

**Note 1:** Includes INTOSC and INTOSC postscaler, as well as the INTRC source.

# 3.4.4 EXIT TO IDLE MODE

An exit from a power managed Run mode to its corresponding Idle mode is executed by setting the IDLEN bit and executing a SLEEP instruction. The CPU is halted at the beginning of the instruction following the SLEEP instruction. There are no changes to any of the clock source status bits (OSTS, IOFS or T1RUN). While the CPU is halted, the peripherals continue to be clocked from the previously selected clock source.

# 3.4.5 EXIT TO SLEEP MODE

An exit from a power managed Run mode to Sleep mode is executed by clearing the IDLEN and SCS1:SCS0 bits and executing a SLEEP instruction. The code is no different than the method used to invoke Sleep mode from the normal operating (full-power) mode.

The primary clock and internal oscillator block are disabled. The INTRC will continue to operate if the WDT is enabled. The Timer1 oscillator will continue to run, if enabled in the T1CON register (Register 12-1). All clock source Status bits are cleared (OSTS, IOFS and T1RUN).

#### 3.5 Wake from Power Managed Modes

An exit from any of the power managed modes is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power managed modes. The clocking subsystem actions are discussed in each of the power managed modes (see Sections 3.2 through 3.4).

| Note: | If application code is timing sensitive, it |

|-------|---------------------------------------------|

|       | should wait for the OSTS bit to become      |

|       | set before continuing. Use the interval     |

|       | during the low-power exit sequence          |

|       | (before OSTS is set) to perform timing      |

|       | insensitive "housekeeping" tasks.           |

Device behavior during Low-Power mode exits is summarized in Table 3-3.

#### 3.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit a power managed mode and resume fullpower operation. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set. On all exits from Low-Power mode by interrupt, code execution branches to the interrupt vector if the GIE/GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see Section 9.0 "Interrupts").

| File Name | Bit 7         | Bit 6                                                                            | Bit 5          | Bit 4        | Bit 3         | Bit 2          | Bit 1           | Bit 0           | Value on<br>POR, BOR | Details on<br>Page: |

|-----------|---------------|----------------------------------------------------------------------------------|----------------|--------------|---------------|----------------|-----------------|-----------------|----------------------|---------------------|

| TOSU      | —             | —                                                                                | —              | Top-of-Stack | Upper Byte (  | FOS<20:16>)    |                 |                 | 0 0000               | 34, 40              |

| TOSH      | Top-of-Stack  | High Byte (TO                                                                    | DS<15:8>)      |              |               |                |                 |                 | 0000 0000            | 34, 40              |

| TOSL      | Top-of-Stack  | Low Byte (TC                                                                     | )S<7:0>)       |              |               |                |                 |                 | 0000 0000            | 34, 40              |

| STKPTR    | STKFUL        | STKUNF                                                                           | _              | Return Stack | Pointer       |                |                 |                 | 00-0 0000            | 34, 41              |

| PCLATU    | _             | bit 21 <sup>(3)</sup> Holding Register for PC<20:16>                             |                |              |               |                |                 |                 |                      | 34, 42              |

| PCLATH    | Holding Regi  | ster for PC<1                                                                    | 5:8>           |              |               |                |                 |                 | 0000 0000            | 34, 42              |

| PCL       | PC Low Byte   | e (PC<7:0>)                                                                      |                |              |               |                |                 |                 | 0000 0000            | 34, 42              |

| TBLPTRU   | _             | —         bit 21         Program Memory Table Pointer Upper Byte (TBLPTR<20:16>) |                |              |               |                |                 |                 |                      | 34, 58              |

| TBLPTRH   | Program Mer   | gram Memory Table Pointer High Byte (TBLPTR<15:8>)                               |                |              |               |                |                 |                 |                      | 34, 58              |

| TBLPTRL   | Program Mer   | mory Table Po                                                                    | ointer Low Byt | e (TBLPTR<7  | ':0>)         |                |                 |                 | 0000 0000            | 34, 58              |

| TABLAT    | Program Mer   | mory Table La                                                                    | tch            |              |               |                |                 |                 | 0000 0000            | 34, 58              |

| PRODH     | Product Regi  | ister High Byte                                                                  | Э              |              |               |                |                 |                 | xxxx xxxx            | 34, 68              |

| PRODL     | Product Regi  | ister Low Byte                                                                   | )              |              |               |                |                 |                 | xxxx xxxx            | 34, 68              |

| INTCON    | GIE/GIEH      | PEIE/GIEL                                                                        | TMR0IE         | INT0IE       | RBIE          | TMR0IF         | INT0IF          | RBIF            | 0000 000x            | 34, 72              |

| INTCON2   | RBPU          | INTEDG0                                                                          | INTEDG1        | INTEDG2      | _             | TMR0IP         | _               | RBIP            | 1111 -1-1            | 34, 73              |

| INTCON3   | INT2IP        | INT1IP                                                                           | -              | INT2IE       | INT1IE        |                | INT2IF          | INT1IF          | 11-0 0-00            | 34, 74              |

| INDF0     | Uses content  | ts of FSR0 to                                                                    | address data   | memory – val | ue of FSR0 n  | ot changed (n  | ot a physical r | register)       | N/A                  | 34, 51              |

| POSTINC0  | Uses content  | ts of FSR0 to                                                                    | address data   | memory – val | ue of FSR0 p  | ost-increment  | ed (not a phys  | sical register) | N/A                  | 34, 51              |

| POSTDEC0  | Uses content  | ts of FSR0 to                                                                    | address data   | memory- valu | ue of FSR0 pc | st-decrement   | ed (not a phys  | sical register) | N/A                  | 34, 51              |

| PREINC0   | Uses content  | ts of FSR0 to                                                                    | address data   | memory – val | ue of FSR0 p  | re-incremente  | d (not a physi  | cal register)   | N/A                  | 34, 51              |

| PLUSW0    | Uses content  | ts of FSR0 to                                                                    | address data   | memory – val | ue of FSR0 of | fset by W (no  | t a physical re | egister)        | N/A                  | 34, 51              |

| FSR0H     | _             | _                                                                                | _              | _            | Indirect Data | Memory Add     | ress Pointer 0  | High            | 0000                 | 34, 51              |

| FSR0L     | Indirect Data | Memory Add                                                                       | ress Pointer 0 | Low Byte     | •             |                |                 |                 | xxxx xxxx            | 34, 51              |

| WREG      | Working Reg   | ister                                                                            |                |              |               |                |                 |                 | xxxx xxxx            | 34                  |

| INDF1     | Uses content  | ts of FSR1 to                                                                    | address data   | memory – val | ue of FSR1 n  | ot changed (n  | ot a physical r | register)       | N/A                  | 34, 51              |

| POSTINC1  | Uses content  | ts of FSR1 to                                                                    | address data   | memory – val | ue of FSR1 p  | ost-increment  | ed (not a phys  | sical register) | N/A                  | 34, 51              |

| POSTDEC1  | Uses content  | ts of FSR1 to a                                                                  | address data   | memory – val | ue of FSR1 po | st-decrement   | ed (not a phy   | sical register) | N/A                  | 34, 51              |

| PREINC1   | Uses content  | ts of FSR1 to                                                                    | address data   | memory – val | ue of FSR1 p  | re-incremente  | d (not a physi  | cal register)   | N/A                  | 34, 51              |

| PLUSW1    | Uses content  | ts of FSR1 to                                                                    | address data   | memory – val | ue of FSR1 of | fset by W (no  | t a physical re | egister)        | N/A                  | 34, 51              |

| FSR1H     | _             | _                                                                                | _              | _            | Indirect Data | Memory Add     | ress Pointer 1  | High            | 0000                 | 34, 51              |

| FSR1L     | Indirect Data | Memory Add                                                                       | ress Pointer 1 | Low Byte     |               |                |                 |                 | xxxx xxxx            | 34, 51              |

| BSR       | _             | _                                                                                | _              | _            | Bank Select   | Register       |                 |                 | 0000                 | 35, 50              |

| INDF2     | Uses content  | ts of FSR2 to                                                                    | address data   | memory – val | ue of FSR2 n  | ot changed (n  | ot a physical r | register)       | N/A                  | 35, 51              |

| POSTINC2  | Uses content  | ts of FSR2 to                                                                    | address data   | memory – val | ue of FSR2 p  | ost-increment  | ed (not a phys  | sical register) | N/A                  | 35, 51              |

| POSTDEC2  | Uses content  | ts of FSR2 to a                                                                  | address data   | memory – val | ue of FSR2 po | st-decrement   | ed (not a phy   | sical register) | N/A                  | 35, 51              |

| PREINC2   | Uses content  | ts of FSR2 to                                                                    | address data   | memory – val | ue of FSR2 p  | re-incremente  | d (not a physi  | cal register)   | N/A                  | 35, 51              |

| PLUSW2    | Uses content  | ts of FSR2 to                                                                    | address data   | memory – val | ue of FSR2 of | ifset by W (no | t a physical re | egister)        | N/A                  | 35, 51              |

| FSR2H     | —             | _                                                                                | —              | —            | Indirect Data | Memory Add     | ress Pointer 2  | High            | 0000                 | 35, 51              |

| FSR2L     | Indirect Data | Memory Add                                                                       | ress Pointer 2 | Low Byte     |               |                |                 |                 | xxxx xxxx            | 35, 51              |

| STATUS    | _             | _                                                                                | _              | N            | OV            | Z              | DC              | С               | x xxxx               | 35, 53              |

| TMR0H     | Timer0 Regis  | ster High Byte                                                                   |                |              |               |                |                 |                 | 0000 0000            | 35, 97              |

| TMR0L     | Timer0 Regis  | ster Low Byte                                                                    |                |              |               |                |                 |                 | xxxx xxxx            | 35, 97              |

| T0CON     | TMR0ON        | T08BIT                                                                           | TOCS           | TOSE         | PSA           | T0PS2          | T0PS1           | T0PS0           | 1111 1111            | 35, 95              |

| OSCCON    | IDLEN         | IRCF2                                                                            | IRCF1          | IRCF0        | OSTS          | IOFS           | SCS1            | SCS0            | 0000 q000            | 35, 16              |

| LVDCON    | _             | —                                                                                | IVRST          | LVDEN        | LVDL3         | LVDL2          | LVDL1           | LVDL0           | 00 0101              | 35, 162             |

|           | 1             |                                                                                  |                |              |               |                |                 |                 | 0                    | 25 174              |

| WDTCON    | —             | _                                                                                |                | _            |               |                | _               | SWDTEN          | 0                    | 35, 174             |

#### TABLE 5-2 **REGISTER FILE SUMMARY (PIC18E1220/1320)**

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition**Note**1:RA6 and associated bits are configured as port pins in RCIO, ECIO and INTIO2 (with port function on RA6) Oscillator mode only and read '0' in11: RAb and associated bits are configured as port pins in RCIO, ECO and in RCIO,

# 9.1 INTCON Registers

The INTCON registers are readable and writable registers, which contain various enable, priority and flag bits.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### REGISTER 9-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0/0  | R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R-0/0               |

|----------|-----------|---------|---------|---------|---------|---------|---------------------|

| GIE/GIEH | PEIE/GIEL | TMR0IE  | INTOIE  | RBIE    | TMR0IF  | INTOIF  | RBIF <sup>(1)</sup> |

| bit 7    |           |         |         |         |         |         | bit 0               |

|          |           |         |         |         |         |         |                     |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | GIE/GIEH: Global Interrupt Enable bit<br><u>When IPEN = 0:</u><br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts<br><u>When IPEN = 1:</u><br>1 = Enables all high priority interrupts<br>0 = Disables all interrupts                                                              |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | PEIE/GIEL: Peripheral Interrupt Enable bit<br><u>When IPEN = 0:</u><br>1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts<br><u>When IPEN = 1:</u><br>1 = Enables all low priority peripheral interrupts<br>0 = Disables all low priority peripheral interrupts |

| bit 5   | <b>TMR0IE:</b> TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 overflow interrupt<br>0 = Disables the TMR0 overflow interrupt                                                                                                                                                              |

| bit 4   | INTOIE: INTO External Interrupt Enable bit<br>1 = Enables the INTO external interrupt<br>0 = Disables the INTO external interrupt                                                                                                                                                                     |

| bit 3   | <b>RBIE:</b> RB Port Change Interrupt Enable bit<br>1 = Enables the RB port change interrupt<br>0 = Disables the RB port change interrupt                                                                                                                                                             |

| bit 2   | <b>TMR0IF:</b> Timer0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed<br>0 = TMR0 register did not overflow                                                                                                                                                                           |

| bit 1   | <b>INTOIF:</b> INT0 External Interrupt Flag bit<br>1 = The INT0 external interrupt occurred (must be cleared in software)<br>0 = The INT0 external interrupt did not occur                                                                                                                            |

| bit 0   | <b>RBIF:</b> RB Port Change Interrupt Flag bit <sup>(1)</sup><br>1 = At least one of the RB<7:4> pins changed state (must be cleared in software)<br>0 = None of the RB<7:4> pins have changed state                                                                                                  |

| Note 1: | A mismatch condition will continue to set this bit. Reading PORTB will end the mismatch condition and allow the bit to be cleared.                                                                                                                                                                    |

# 11.0 TIMER0 MODULE

The Timer0 module has the following features:

- Software selectable as an 8-bit or 16-bit timer/ counter

- Readable and writable

- Dedicated 8-bit software programmable prescaler

- · Clock source selectable to be external or internal

- Interrupt-on-overflow from FFh to 00h in 8-bit mode and FFFFh to 0000h in 16-bit mode

- Edge select for external clock

#### REGISTER 11-1: TOCON: TIMERO CONTROL REGISTER

Figure 11-1 shows a simplified block diagram of the Timer0 module in 8-bit mode and Figure 11-2 shows a simplified block diagram of the Timer0 module in 16-bit mode.

The T0CON register (Register 11-1) is a readable and writable register that controls all the aspects of Timer0, including the prescale selection.

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TMR0ON  | T08BIT  | TOCS    | TOSE    | PSA     | T0PS2   | T0PS1   | T0PS0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:          |                                                                                        |                                                                                                                                                                                                                                                                                                                 |                                                       |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| R = Readable bit |                                                                                        | W = Writable bit                                                                                                                                                                                                                                                                                                | U = Unimplemented bit, read as '0'                    |  |  |  |  |

| u = Bit is ur    | nchanged                                                                               | x = Bit is unknown                                                                                                                                                                                                                                                                                              | -n/n = Value at POR and BOR/Value at all other Resets |  |  |  |  |

| '1' = Bit is s   | set                                                                                    | '0' = Bit is cleared                                                                                                                                                                                                                                                                                            |                                                       |  |  |  |  |

| bit 7            | TMR0ON:                                                                                | Timer0 On/Off Control bit                                                                                                                                                                                                                                                                                       |                                                       |  |  |  |  |

|                  | 1 = Enabl<br>0 = Stops                                                                 |                                                                                                                                                                                                                                                                                                                 |                                                       |  |  |  |  |

| bit 6            | 1 = Timer                                                                              | mer0 8-bit/16-bit Control bit<br>0 is configured as an 8-bit tir<br>0 is configured as a 16-bit tir                                                                                                                                                                                                             |                                                       |  |  |  |  |

| bit 5            | 1 = Trans                                                                              | er0 Clock Source Select bit<br>ition on T0CKI pin<br>al instruction cycle clock (CL                                                                                                                                                                                                                             | KO)                                                   |  |  |  |  |

| bit 4            | 1 = Increr                                                                             | <b>T0SE:</b> Timer0 Source Edge Select bit<br>1 = Increment on high-to-low transition on T0CKI pin<br>0 = Increment on low-to-high transition on T0CKI pin                                                                                                                                                      |                                                       |  |  |  |  |

| bit 3            | 1 = TImer                                                                              | <ul> <li>PSA: Timer0 Prescaler Assignment bit</li> <li>1 = TImer0 prescaler is NOT assigned. Timer0 clock input bypasses prescaler.</li> <li>0 = Timer0 prescaler is assigned. Timer0 clock input comes from prescaler output.</li> </ul>                                                                       |                                                       |  |  |  |  |

| bit 2-0          | 111 = 1:25 $110 = 1:12$ $101 = 1:64$ $100 = 1:32$ $011 = 1:16$ $010 = 1:8$ $001 = 1:4$ | <ul> <li>&gt;: Timer0 Prescaler Select b</li> <li>56 Prescale value</li> <li>28 Prescale value</li> <li>4 Prescale value</li> <li>2 Prescale value</li> <li>5 Prescale value</li> <li>Prescale value</li> <li>Prescale value</li> <li>Prescale value</li> <li>Prescale value</li> <li>Prescale value</li> </ul> | its                                                   |  |  |  |  |

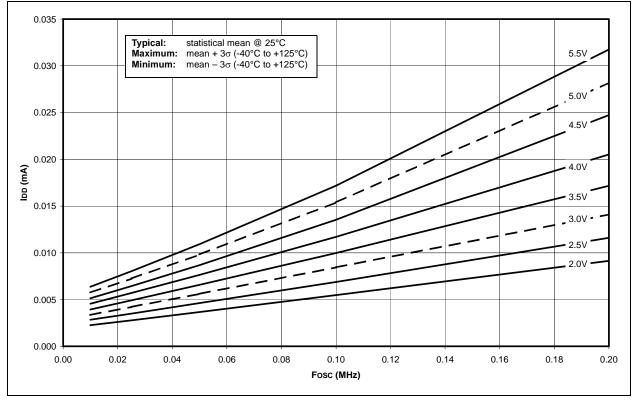

# 13.2 Timer2 Interrupt

The Timer2 module has an 8-bit period register, PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon Reset.

FIGURE 13-1: TIMER2 BLOCK DIAGRAM

# 13.3 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module, which optionally uses it to generate the shift clock.

#### TABLE 13-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Name   | Bit 7      | Bit 6        | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|------------|--------------|---------|---------|---------|--------|---------|---------|----------------------|---------------------------------|

| INTCON | GIE/GIEH   | PEIE/GIEL    | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF  | RBIF    | 0000 000x            | 0000 000u                       |

| PIR1   | _          | ADIF         | RCIF    | TXIF    | _       | CCP1IF | TMR2IF  | TMR1IF  | -000 -000            | -000 -000                       |

| PIE1   | _          | ADIE         | RCIE    | TXIE    | _       | CCP1IE | TMR2IE  | TMR1IE  | -000 -000            | -000 -000                       |

| IPR1   | _          | ADIP         | RCIP    | TXIP    | _       | CCP1IP | TMR2IP  | TMR1IP  | -111 -111            | -111 -111                       |

| TMR2   | Timer2 Mod | dule Registe | r       |         |         |        |         |         | 0000 0000            | 0000 0000                       |

| T2CON  | —          | TOUTPS3      | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

| PR2    | Timer2 Per | iod Register |         |         |         |        |         |         | 1111 1111            | 1111 1111                       |

| PR2    |            | lod Register |         |         |         |        |         |         | 1111 1111<br>4 - T   |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

# 15.1 ECCP Outputs

The Enhanced CCP module may have up to four outputs, depending on the selected operating mode. These outputs, designated P1A through P1D, are multiplexed with I/O pins on PORTB. The pin assignments are summarized in Table 15-1.

To configure I/O pins as PWM outputs, the proper PWM mode must be selected by setting the P1Mn and CCP1Mn bits (CCP1CON<7:6> and <3:0>, respectively). The appropriate TRISB direction bits for the port pins must also be set as outputs.

| ECCP Mode      | CCP1CON<br>Configuration | RB3  | RB2      | RB6                       | RB7                |

|----------------|--------------------------|------|----------|---------------------------|--------------------|

| Compatible CCP | 00xx 11xx                | CCP1 | RB2/INT2 | RB6/PGC/T1OSO/T13CKI/KBI2 | RB7/PGD/T1OSI/KBI3 |

| Dual PWM       | 10xx 11xx                | P1A  | P1B      | RB6/PGC/T1OSO/T13CKI/KBI2 | RB7/PGD/T1OSI/KBI3 |

| Quad PWM       | x1xx 11xx                | P1A  | P1B      | P1C                       | P1D                |

**Legend:** x = Don't care. Shaded cells indicate pin assignments not used by ECCP in a given mode.

**Note 1:** TRIS register values must be configured appropriately.

#### 15.2 CCP Module

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

# TABLE 15-2:CCP MODE – TIMER<br/>RESOURCE

| CCP Mode           | Timer Resource                       |

|--------------------|--------------------------------------|

| Capture<br>Compare | Timer1 or Timer3<br>Timer1 or Timer3 |

| PWM                | Timer2                               |

# 15.3 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on pin RB3/CCP1/P1A. An event is defined as one of the following:

- every falling edge

- every rising edge

- every 4th rising edge

- · every 16th rising edge

The event is selected by control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR1<2>), is set; it must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

# 15.3.1 CCP PIN CONFIGURATION

In Capture mode, the RB3/CCP1/P1A pin should be configured as an input by setting the TRISB<3> bit.

| Note: | If the RB3/CCP1/P1A is configured as an |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|

|       | output, a write to the port can cause a |  |  |  |  |

|       | capture condition.                      |  |  |  |  |

#### 15.3.2 TIMER1/TIMER3 MODE SELECTION

The timers that are to be used with the capture feature (either Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work. The timer to be used with the CCP module is selected in the T3CON register.

#### 15.3.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit, CCP1IE (PIE1<2>), clear while changing capture modes to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in operating mode.

# 16.2.3 AUTO-BAUD RATE DETECT

The Enhanced USART module supports the automatic detection and calibration of baud rate. This feature is active only in Asynchronous mode and while the WUE bit is clear.

The automatic baud rate measurement sequence (Figure 16-1) begins whenever a Start bit is received and the ABDEN bit is set. The calculation is self-averaging.

In the Auto-Baud Rate Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. In ABD mode, the internal Baud Rate Generator is used as a counter to time the bit period of the incoming serial byte stream.

Once the ABDEN bit is set, the state machine will clear the BRG and look for a Start bit. The Auto-Baud Detect must receive a byte with the value 55h (ASCII "U", which is also the LIN bus Sync character), in order to calculate the proper bit rate. The measurement is taken over both a low and a high bit time in order to minimize any effects caused by asymmetry of the incoming signal. After a Start bit, the SPBRG begins counting up using the preselected clock source on the first rising edge of RX. After eight bits on the RX pin, or the fifth rising edge, an accumulated value totaling the proper BRG period is left in the SPBRGH:SPBRG registers. Once the fifth edge is seen (should correspond to the Stop bit), the ABDEN bit is automatically cleared.

While calibrating the baud rate period, the BRG registers are clocked at 1/8th the preconfigured clock rate. Note that the BRG clock will be configured by the BRG16 and BRGH bits. Independent of the BRG16 bit setting, both the SPBRG and SPBRGH will be used as a 16-bit counter. This allows the user to verify that no carry occurred for 8-bit modes, by checking for 00h in the SPBRGH register. Refer to Table 16-4 for counter clock rates to the BRG.

While the ABD sequence takes place, the EUSART state machine is held in Idle. The RCIF interrupt is set once the fifth rising edge on RX is detected. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded.

Note 1: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible due to bit error rates. Overall system timing and communication baud rates must be taken into consideration when using the Auto-Baud Rate Detection feature.

# 16.2.4 RECEIVING A SYNC (AUTO-BAUD RATE DETECT)

To receive a Sync (Auto-Baud Rate Detect):

- 1. Configure the EUSART for asynchronous receive. TXEN should remain clear. SPBRGH:SPBRG may be left as is. The controller should operate in either PRI\_RUN or PRI\_IDLE.

- 2. Enable RXIF interrupts. Set RCIE, PEIE, GIE.

- 3. Enable Auto-Baud Rate Detect. Set ABDEN.

- 4. When the next RCIF interrupt occurs, the received baud rate has been measured. Read RCREG to clear RCIF and discard. Check SPBRGH:SPBRG for a valid value. The EUSART is ready for normal communications. Return from the interrupt. Allow the primary clock to run (PRI\_RUN or PRI\_IDLE).

- Process subsequent RCIF interrupts normally as in asynchronous reception. Remain in PRI\_RUN or PRI\_IDLE until communications are complete.

| TABLE 16-4: | BRG COUNTER CLOCK |

|-------------|-------------------|

|             | RATES             |

| BRG16 | BRGH | BRG Counter Clock |

|-------|------|-------------------|

| 0     | 0    | Fosc/512          |

| 0     | 1    | Fosc/128          |

| 1     | 0    | Fosc/128          |

| 1     | 1    | Fosc/32           |

**Note:** During the ABD sequence, SPBRG and SPBRGH are both used as a 16-bit counter, independent of BRG16 setting.

# 16.5 EUSART Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTA<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the RB1/AN5/TX/CK/INT1 pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any low-power mode.

#### 16.5.1 EUSART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical, except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in the TXREG register.

- c) Flag bit, TXIF, will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit, TXIF, will now be set.

- e) If enable bit, TXIE, is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name    | Bit 7                                  | Bit 6                                            | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|----------------------------------------|--------------------------------------------------|--------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| INTCON  | GIE/GIEH                               | PEIE/GIEL                                        | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1    | _                                      | ADIF                                             | RCIF   | TXIF   | —     | CCP1IF | TMR2IF | TMR1IF | -000 -000            | -000 -000                       |

| PIE1    | _                                      | ADIE                                             | RCIE   | TXIE   | —     | CCP1IE | TMR2IE | TMR1IE | -000 -000            | -000 -000                       |

| IPR1    |                                        | ADIP                                             | RCIP   | TXIP   | _     | CCP1IP | TMR2IP | TMR1IP | -111 -111            | -111 -111                       |

| RCSTA   | SPEN                                   | RX9                                              | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D   | x000 000x            | 0000 000x                       |

| TXREG   | EUSART Tra                             | ansmit Registe                                   | er     |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA   | CSRC                                   | TX9                                              | TXEN   | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |

| BAUDCTL | —                                      | RCIDL                                            | —      | SCKP   | BRG16 | _      | WUE    | ABDEN  | -1-1 0-00            | -1-1 0-00                       |

| SPBRGH  | Baud Rate Generator Register High Byte |                                                  |        |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| SPBRG   | Baud Rate G                            | aud Rate Generator Register Low Byte 0000 0000 0 |        |        |       |        |        |        |                      | 0000 0000                       |

# TABLE 16-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

| U-0              | R/W-0/0                                                                                                                                          | R/W-0/0                             | R/W-0/0       | R/W-0/0                              | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------|--------------------------------------|------------------|------------------|-------------|

| _                | PCFG6                                                                                                                                            | PCFG5                               | PCFG4         | PCFG3                                | PCFG2            | PCFG1            | PCFG0       |

| bit 7            |                                                                                                                                                  |                                     |               |                                      |                  |                  | bit         |

|                  |                                                                                                                                                  |                                     |               |                                      |                  |                  |             |

| Legend:          |                                                                                                                                                  |                                     |               |                                      |                  |                  |             |

| R = Readable     | e bit                                                                                                                                            | W = Writable                        | bit           | •                                    | mented bit, read |                  |             |

| u = Bit is unc   | hanged                                                                                                                                           | x = Bit is unk                      | nown          | -n/n = Value a                       | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set | t                                                                                                                                                | '0' = Bit is cle                    | ared          |                                      |                  |                  |             |

|                  |                                                                                                                                                  |                                     | o.!           |                                      |                  |                  |             |

| bit 7            | •                                                                                                                                                | nted: Read as '                     |               |                                      |                  |                  |             |

| bit 6            |                                                                                                                                                  | Port Configura<br>igured as a digi  |               |                                      |                  |                  |             |

|                  |                                                                                                                                                  |                                     |               | – digital input o                    | disabled and rea | ads '0'          |             |

| bit 5            |                                                                                                                                                  | Port Configura                      | •             | ang tan inip at t                    |                  |                  |             |

| 2.1.0            |                                                                                                                                                  | igured as a digi                    |               |                                      |                  |                  |             |

|                  | 0 = Pin confi                                                                                                                                    | igured as an ar                     | nalog channel | <ul> <li>digital input of</li> </ul> | disabled and rea | ads '0'          |             |

| bit 4            |                                                                                                                                                  | Port Configura                      |               |                                      |                  |                  |             |

|                  |                                                                                                                                                  | igured as a digi                    |               |                                      |                  |                  |             |

|                  |                                                                                                                                                  | •                                   | •             | •                                    | disabled and rea | ads '0'          |             |

| bit 3            |                                                                                                                                                  | Port Configura                      |               |                                      |                  |                  |             |

|                  |                                                                                                                                                  | igured as a digi<br>igured as an ar |               | – digital input o                    | disabled and rea | ads '0'          |             |

| bit 2            |                                                                                                                                                  | Port Configura                      | •             | •                                    |                  |                  |             |

| SR 2             |                                                                                                                                                  | igured as a digi                    |               |                                      |                  |                  |             |

|                  | 0 = Pin configured as an analog channel – digital input disabled and reads '0'                                                                   |                                     |               |                                      |                  |                  |             |

| bit 1            |                                                                                                                                                  | Port Configura                      |               |                                      |                  |                  |             |

|                  | <ul> <li>1 = Pin configured as a digital port</li> <li>0 = Pin configured as an analog channel – digital input disabled and reads '0'</li> </ul> |                                     |               |                                      |                  |                  |             |

|                  |                                                                                                                                                  | •                                   | •             | •                                    | disabled and rea | ads '0'          |             |

| bit 0            |                                                                                                                                                  | Port Configura                      |               |                                      |                  |                  |             |

|                  |                                                                                                                                                  | igured as a digi                    |               | digital input                        | disabled and re- | ade (0'          |             |

|                  |                                                                                                                                                  | igureu as an af                     | alog channel  | – uigitai iriput (                   | disabled and rea | aus U            |             |

# REGISTER 17-2: ADCON1: A/D CONTROL REGISTER 1

| R/W-0/0          | U-0                                                                                                                               | R/W-0/0                                     | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------|----------------|------------------|------------------|-------------|

| ADFM             | _                                                                                                                                 | ACQT2                                       | ACQT1          | ACQT0          | ADCS2            | ADCS1            | ADCS0       |

| bit 7            |                                                                                                                                   |                                             |                |                |                  |                  | bit         |

| Legend:          |                                                                                                                                   |                                             |                |                |                  |                  |             |

| -                | .:.                                                                                                                               |                                             | <b>L</b> :4    |                |                  |                  |             |

| R = Readable b   |                                                                                                                                   | W = Writable                                |                |                | nented bit, read |                  |             |

| u = Bit is uncha | inged                                                                                                                             | x = Bit is unki                             |                | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| 1' = Bit is set  |                                                                                                                                   | '0' = Bit is cle                            | ared           |                |                  |                  |             |

| bit 7            | ADFM: A/D                                                                                                                         | Result Format S                             | Select bit     |                |                  |                  |             |

|                  | 1 = Right jus<br>0 = Left justi                                                                                                   |                                             |                |                |                  |                  |             |

| bit 6            | Unimpleme                                                                                                                         | nted: Read as '                             | 0'             |                |                  |                  |             |

| bit 5-3          | ACQT<2:0><br>000 = 0 TAD<br>001 = 2 TAD<br>010 = 4 TAD<br>011 = 6 TAD<br>100 = 8 TAD<br>101 = 12 TA<br>110 = 16 TA<br>111 = 20 TA | D                                           | n Time Select  | bits           |                  |                  |             |

| bit 2-0          |                                                                                                                                   | : A/D Conversion                            | on Clock Selec | t bits         |                  |                  |             |

|                  | 000 = FOSC/<br>001 = FOSC/<br>010 = FOSC/<br>011 = FRC (<br>100 = FOSC/<br>101 = FOSC/<br>110 = FOSC/<br>111 = FRC (              | /8<br>/32<br>clock derived fro<br>/4<br>/16 |                |                |                  |                  |             |

# REGISTER 17-3: ADCON2: A/D CONTROL REGISTER 2

clock starts. This allows the  ${\tt SLEEP}$  instruction to be executed before starting a conversion.

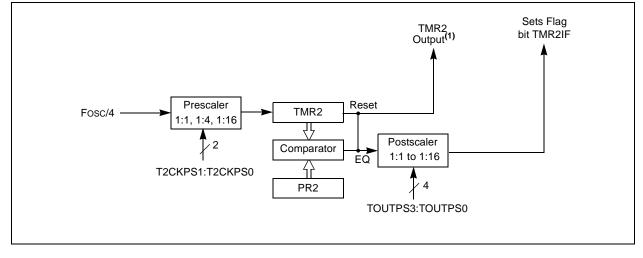

# 17.7 A/D Conversions

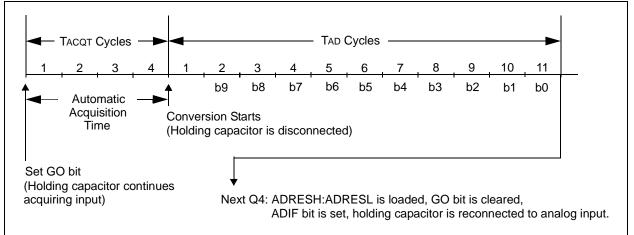

Figure 17-3 shows the operation of the A/D converter after the GO bit has been set and the ACQT2:ACQT0 bits are cleared. A conversion is started after the following instruction to allow entry into Low-Power Sleep mode before the conversion begins.

Figure 17-4 shows the operation of the A/D converter after the GO bit has been set and the ACQT2:ACQT0 bits are set to '010' and selecting a 4 TAD acquisition time before the conversion starts.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/ D conversion sample. This means the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers).

After the A/D conversion is completed or aborted, a 2 TAD wait is required before the next acquisition can be started. After this wait, acquisition on the selected channel is automatically started.

Note: The GO/DONE bit should NOT be set in the same instruction that turns on the A/D.

#### FIGURE 17-3: A/D CONVERSION TAD CYCLES (Acqt<2:0> = 000, Tacq = 0)

#### FIGURE 17-4: A/D CONVERSION TAD CYCLES (Acqt<2:0> = 010, Tacq = 4 Tad)

# 19.4 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the microcontroller to continue operation, in the event of an external oscillator failure, by automatically switching the system clock to the internal oscillator block. The FSCM function is enabled by setting the Fail-Safe Clock Monitor Enable bit, FSCM (CONFIG1H<6>).

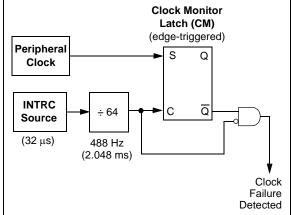

When FSCM is enabled, the INTRC oscillator runs at all times to monitor clocks to peripherals and provide an instant backup clock in the event of a clock failure. Clock monitoring (shown in Figure 19-3) is accomplished by creating a sample clock signal, which is the INTRC output divided by 64. This allows ample time between FSCM sample clocks for a peripheral clock edge to occur. The peripheral system clock and the sample clock are presented as inputs to the Clock Monitor latch (CM). The CM is set on the falling edge of the system clock source, but cleared on the rising edge of the sample clock.

Clock failure is tested for on the falling edge of the sample clock. If a sample clock falling edge occurs while CM is still set, a clock failure has been detected (Figure 19-4). This causes the following:

- the FSCM generates an oscillator fail interrupt by setting bit, OSCFIF (PIR2<7>);

- the system clock source is switched to the internal oscillator block (OSCCON is not updated to show the current clock source – this is the Fail-Safe condition); and

- the WDT is reset.

Since the postscaler frequency from the internal oscillator block may not be sufficiently stable, it may be desirable to select another clock configuration and enter an alternate power managed mode (see Section 19.3.1 "Special Considerations for Using Two-Speed Start-up" and Section 3.1.3 "Multiple Sleep Commands" for more details). This can be done to attempt a partial recovery, or execute a controlled shutdown.

To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IFRC2:IFRC0, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting IFRC2:IFRC0 prior to entering Sleep mode.

Adjustments to the internal oscillator block, using the OSCTUNE register, also affect the period of the FSCM by the same factor. This can usually be neglected, as the clock frequency being monitored is generally much higher than the sample clock frequency.

The FSCM will detect failures of the primary or secondary clock sources only. If the internal oscillator block fails, no failure would be detected, nor would any action be possible.

#### 19.4.1 FSCM AND THE WATCHDOG TIMER

Both the FSCM and the WDT are clocked by the INTRC oscillator. Since the WDT operates with a separate divider and counter, disabling the WDT has no effect on the operation of the INTRC oscillator when the FSCM is enabled.

As already noted, the clock source is switched to the INTOSC clock when a clock failure is detected. Depending on the frequency selected by the IRCF2:IRCF0 bits, this may mean a substantial change in the speed of code execution. If the WDT is enabled with a small prescale value, a decrease in clock speed allows a WDT time-out to occur and a subsequent device Reset. For this reason, Fail-Safe Clock events also reset the WDT and postscaler, allowing it to start timing from when execution speed was changed and decreasing the likelihood of an erroneous time-out.

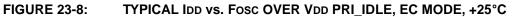

# 22.2 DC Characteristics: Power-Down and Supply Current PIC18F1220/1320 (Industrial) PIC18LF1220/1320 (Industrial) (Continued)

|              | PIC18LF1220/1320<br>(Industrial)<br>PIC18F1220/1320<br>(Industrial, Extended) |      | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial                                                      |       |        |            |                                                                      |  |  |  |  |

|--------------|-------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|------------|----------------------------------------------------------------------|--|--|--|--|

|              |                                                                               |      | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |       |        |            |                                                                      |  |  |  |  |

| Param<br>No. | Device                                                                        | Тур. | Max.                                                                                                                                                                                    | Units |        | Condit     | ions                                                                 |  |  |  |  |

|              | Supply Current (IDD) <sup>(2,3)</sup>                                         |      |                                                                                                                                                                                         |       |        |            |                                                                      |  |  |  |  |

|              | PIC18LF1220/1320                                                              | 140  | 220                                                                                                                                                                                     | μA    | -40°C  |            |                                                                      |  |  |  |  |

|              |                                                                               | 145  | 220                                                                                                                                                                                     | μA    | +25°C  | VDD = 2.0V |                                                                      |  |  |  |  |

|              |                                                                               | 155  | 220                                                                                                                                                                                     | μΑ    | +85°C  | ]          |                                                                      |  |  |  |  |

|              | PIC18LF1220/1320                                                              | 215  | 330                                                                                                                                                                                     | μΑ    | -40°C  |            | Fosc = 1 MHz<br>( <b>RC_RUN</b> mode,<br>Internal oscillator source) |  |  |  |  |

|              |                                                                               | 225  | 330                                                                                                                                                                                     | μA    | +25°C  | VDD = 3.0V |                                                                      |  |  |  |  |

|              |                                                                               | 235  | 330                                                                                                                                                                                     | μA    | +85°C  | VDD = 5.0V |                                                                      |  |  |  |  |

|              | All devices                                                                   | 385  | 550                                                                                                                                                                                     | μΑ    | -40°C  |            |                                                                      |  |  |  |  |

|              |                                                                               | 390  | 550                                                                                                                                                                                     | μA    | +25°C  |            |                                                                      |  |  |  |  |

|              |                                                                               | 405  | 550                                                                                                                                                                                     | μA    | +85°C  | 100 - 0.01 |                                                                      |  |  |  |  |