Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 4KB (2K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 7x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1220-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-2:PIC18F1220/1320 PINOUT I/O DESCRIPTIONS

|                       | Pi                              | n Numb   | er        |             |                |                                                                                                                                                                     |

|-----------------------|---------------------------------|----------|-----------|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name              | PDIP/<br>SOIC                   | SSOP     | QFN       | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                         |

| MCLR/Vpp/RA5<br>MCLR  | 4                               | 4        | 1         | I           | ST             | Master Clear (input) or programming voltage (input).<br>Master Clear (Reset) input. This pin is an active-lov<br>Reset to the device.                               |

| VPP                   |                                 |          |           | Р           | —              | Programming voltage input.                                                                                                                                          |

| RA5                   |                                 |          |           | I           | ST             | Digital input.                                                                                                                                                      |

| OSC1/CLKI/RA7<br>OSC1 | 16                              | 18       | 21        | I           | ST             | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source<br>input. ST buffer when configured in RC mode,<br>CMOS otherwise. |

| CLKI                  |                                 |          |           | I           | CMOS           | External clock source input. Always associated with<br>pin function OSC1. (See related OSC1/CLKI,<br>OSC2/CLKO pins.)                                               |

| RA7                   |                                 |          |           | I/O         | ST             | General purpose I/O pin.                                                                                                                                            |

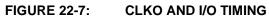

| OSC2/CLKO/RA6<br>OSC2 | 15                              | 17       | 20        | 0           | _              | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal or<br>resonator in Crystal Oscillator mode.                                   |

| CLKO                  |                                 |          |           | 0           |                | In RC, EC and INTRC modes, OSC2 pin outputs<br>CLKO, which has 1/4 the frequency of OSC1 and<br>denotes instruction cycle rate.                                     |

| RA6                   |                                 |          |           | I/O         | ST             | General purpose I/O pin.                                                                                                                                            |

|                       |                                 |          |           |             |                | PORTA is a bidirectional I/O port.                                                                                                                                  |

| RA0/AN0               | 1                               | 1        | 26        |             |                |                                                                                                                                                                     |

| RA0<br>AN0            |                                 |          |           | I/O<br>I    | ST<br>Analog   | Digital I/O.<br>Analog input 0.                                                                                                                                     |

| RA1/AN1/LVDIN         | 2                               | 2        | 27        | •           | / malog        | , halog input o.                                                                                                                                                    |

| RA1                   |                                 | _        |           | I/O         | ST             | Digital I/O.                                                                                                                                                        |

| AN1                   |                                 |          |           | <br>        | Analog         | Analog input 1.                                                                                                                                                     |

|                       | 0                               | 7        | 7         | I           | Analog         | Low-Voltage Detect input.                                                                                                                                           |

| RA2/AN2/VREF-<br>RA2  | 6                               | 7        | 7         | I/O         | ST             | Digital I/O.                                                                                                                                                        |

| AN2                   | 1                               |          |           | 1           | Analog         | Analog input 2.                                                                                                                                                     |

| VREF-                 | 1                               |          |           | Т           | Analog         | A/D reference voltage (low) input.                                                                                                                                  |

| RA3/AN3/VREF+         | 7                               | 8        | 8         |             | o <del></del>  |                                                                                                                                                                     |

| RA3<br>AN3            | 1                               |          |           | 1/O<br>1    | ST<br>Analog   | Digital I/O.<br>Analog input 3.                                                                                                                                     |

| VREF+                 |                                 |          |           |             | Analog         | A/D reference voltage (high) input.                                                                                                                                 |

| RA4/T0CKI             | 3                               | 3        | 28        |             |                |                                                                                                                                                                     |

| RA4<br>T0CKI          |                                 |          |           | I/O<br>I    | ST/OD<br>ST    | Digital I/O. Open-drain when configured as output.<br>Timer0 external clock input.                                                                                  |

| RA5                   |                                 |          |           |             |                | See the MCLR/VPP/RA5 pin.                                                                                                                                           |

| RA6                   |                                 |          |           |             |                | See the OSC2/CLKO/RA6 pin.                                                                                                                                          |

| RA7                   | 1                               |          |           |             |                | See the OSC1/CLKI/RA7 pin.                                                                                                                                          |

| ST = S<br>O = O       | TL compa<br>chmitt Tri<br>utput | gger inp | ut with ( |             | evels          | CMOS = CMOS compatible input or output<br>I = Input<br>P = Power                                                                                                    |

| R/W-0/0         | R/W-0/0        | R/W-1/1                                                                                                  | R/W-1/1                   | R <sup>(1)</sup> | R-0/0              | R/W-0/0         | R/W-0/0      |  |  |  |  |

|-----------------|----------------|----------------------------------------------------------------------------------------------------------|---------------------------|------------------|--------------------|-----------------|--------------|--|--|--|--|

| IDLEN           |                | IRCF<2:0>                                                                                                |                           | OSTS             | IOFS               | SCS             | <1:0>        |  |  |  |  |

| bit 7           |                |                                                                                                          |                           |                  |                    |                 | bit (        |  |  |  |  |

|                 |                |                                                                                                          |                           |                  |                    |                 |              |  |  |  |  |

| Legend:         |                |                                                                                                          |                           |                  |                    |                 |              |  |  |  |  |

| R = Readabl     | e bit          | W = Writable                                                                                             | bit                       | U = Unimpler     | mented bit, rea    | d as '0'        |              |  |  |  |  |

| u = Bit is und  | changed        | x = Bit is unkr                                                                                          | iown                      | -n/n = Value a   | at POR and BC      | DR/Value at all | other Resets |  |  |  |  |

| '1' = Bit is se | t              | '0' = Bit is clea                                                                                        | ared                      |                  |                    |                 |              |  |  |  |  |

|                 |                |                                                                                                          |                           |                  |                    |                 |              |  |  |  |  |

| bit 7           |                | Enable bits                                                                                              |                           |                  |                    |                 |              |  |  |  |  |

|                 |                | ode enabled; CPl<br>ode enabled; CP                                                                      |                           |                  | 0                  |                 |              |  |  |  |  |

| bit 6-4         |                |                                                                                                          |                           |                  |                    | ep mode         |              |  |  |  |  |

| DIL 0-4         |                | IRCF<2:0>: Internal Oscillator Frequency Select bits<br>111 = 8 MHz (8 MHz source drives clock directly) |                           |                  |                    |                 |              |  |  |  |  |

|                 |                | 111 = 4  MHz                                                                                             |                           |                  |                    |                 |              |  |  |  |  |

|                 |                | 101 = 2  MHz                                                                                             |                           |                  |                    |                 |              |  |  |  |  |

|                 | 100 = 1 MH     | łz                                                                                                       |                           |                  |                    |                 |              |  |  |  |  |

|                 | 011 = 500      |                                                                                                          |                           |                  |                    |                 |              |  |  |  |  |

|                 | 010 = 250      |                                                                                                          |                           |                  |                    |                 |              |  |  |  |  |

|                 | 001 = 125 k    | кнz<br>-lz (INTRC sourc                                                                                  | e drives clock            | directly)        |                    |                 |              |  |  |  |  |

| bit 3           |                | illator Start-up Ti                                                                                      |                           | • •              |                    |                 |              |  |  |  |  |

|                 |                | or Start-up Timer                                                                                        |                           |                  | rv oscillator is r | runnina         |              |  |  |  |  |

|                 |                | or Start-up Timer                                                                                        |                           |                  | •                  | •               |              |  |  |  |  |

| bit 2           | IOFS: INTC     | SC Frequency S                                                                                           | table bit                 |                  |                    |                 |              |  |  |  |  |

|                 | 1 = INTOS      | C frequency is st                                                                                        | able                      |                  |                    |                 |              |  |  |  |  |

|                 | 0 = INTOS      | C frequency is no                                                                                        | ot stable                 |                  |                    |                 |              |  |  |  |  |

| bit 1-0         | SCS<1:0>:      | System Clock Se                                                                                          | elect bits <sup>(1)</sup> |                  |                    |                 |              |  |  |  |  |

|                 |                | al oscillator block                                                                                      | • • •                     |                  |                    |                 |              |  |  |  |  |

|                 |                | oscillator (Secon                                                                                        |                           |                  |                    |                 |              |  |  |  |  |

|                 | 00 = Primai    | ry oscillator (Slee                                                                                      | p and PRI_ID              | ILE modes)       |                    |                 |              |  |  |  |  |

| Note 1: D       | epends on stat | e of the IESO bit                                                                                        | in Configurat             | ion Register 1H  | ł.                 |                 |              |  |  |  |  |

|                 |                |                                                                                                          |                           |                  |                    |                 |              |  |  |  |  |

## REGISTER 2-2: OSCCON: OSCILLATOR CONTROL REGISTER

#### 3.1.2 ENTERING POWER MANAGED MODES

In general, entry, exit and switching between power managed clock sources requires clock source switching. In each case, the sequence of events is the same.

Any change in the power managed mode begins with loading the OSCCON register and executing a SLEEP instruction. The SCS1:SCS0 bits select one of three power managed clock sources; the primary clock (as defined in Configuration Register 1H), the secondary clock (the Timer1 oscillator) and the internal oscillator block (used in RC modes). Modifying the SCS bits will have no effect until a SLEEP instruction is executed. Entry to the power managed mode is triggered by the execution of a SLEEP instruction.

Figure 3-5 shows how the system is clocked while switching from the primary clock to the Timer1 oscillator. When the SLEEP instruction is executed, clocks to the device are stopped at the beginning of the next instruction cycle. Eight clock cycles from the new clock source are counted to synchronize with the new clock source are counted, clocks from the new clock source are counted, clocks from the new clock source are counted, clocks from the new clock source resume clocking the system. The actual length of the pause is between eight and nine clock periods from the new clock source. This ensures that the new clock source is stable and that its pulse width will not be less than the shortest pulse width of the two clock sources.

Three bits indicate the current clock source: OSTS and IOFS in the OSCCON register and T1RUN in the T1CON register. Only one of these bits will be set while in a power managed mode. When the OSTS bit is set, the primary clock is providing the system clock. When the IOFS bit is set, the INTOSC output is providing a stable 8 MHz clock source and is providing the system clock. When the T1RUN bit is set, the Timer1 oscillator is providing the system clock. If none of these bits are set, then either the INTRC clock source is clocking the system, or the INTOSC source is not yet stable.

If the internal oscillator block is configured as the primary clock source in Configuration Register 1H, then both the OSTS and IOFS bits may be set when in PRI\_RUN or PRI\_IDLE modes. This indicates that the primary clock (INTOSC output) is generating a stable 8 MHz output. Entering an RC power managed mode (same frequency) would clear the OSTS bit.

| Note 1: | Caution should be used when modifying         |

|---------|-----------------------------------------------|

|         | a single IRCF bit. If VDD is less than 3V, it |

|         | is possible to select a higher clock speed    |

|         | than is supported by the low VDD.             |

|         | Improper device operation may result if       |

|         | the VDD/FOSC specifications are violated.     |

|         |                                               |

2: Executing a SLEEP instruction does not necessarily place the device into Sleep mode; executing a SLEEP instruction is simply a trigger to place the controller into a power managed mode selected by the OSCCON register, one of which is Sleep mode.

#### 3.1.3 MULTIPLE SLEEP COMMANDS

The power managed mode that is invoked with the SLEEP instruction is determined by the settings of the IDLEN and SCS bits at the time the instruction is executed. If another SLEEP instruction is executed, the device will enter the power managed mode specified by these same bits at that time. If the bits have changed, the device will enter the new power managed mode specified by the new bit settings.

#### 3.1.4 COMPARISONS BETWEEN RUN AND IDLE MODES

Clock source selection for the Run modes is identical to the corresponding Idle modes. When a SLEEP instruction is executed, the SCS bits in the OSCCON register are used to switch to a different clock source. As a result, if there is a change of clock source at the time a SLEEP instruction is executed, a clock switch will occur.

In Idle modes, the CPU is not clocked and is not running. In Run modes, the CPU is clocked and executing code. This difference modifies the operation of the WDT when it times out. In Idle modes, a WDT time-out results in a wake from power managed modes. In Run modes, a WDT time-out results in a WDT Reset (see Table 3-2).

During a wake-up from an Idle mode, the CPU starts executing code by entering the corresponding Run mode until the primary clock becomes ready. When the primary clock becomes ready, the clock source is automatically switched to the primary clock. The IDLEN and SCS bits are unchanged during and after the wake-up.

Figure 3-2 shows how the system is clocked during the clock source switch. The example assumes the device was in SEC\_IDLE or SEC\_RUN mode when a wake is triggered (the primary clock was configured in HSPLL mode).

| Power<br>Managed<br>Mode | CPU is Clocked by                                       | WDT Time-out causes a | Peripherals are<br>Clocked by                           | Clock during Wake-up<br>(while primary becomes<br>ready)                                         |

|--------------------------|---------------------------------------------------------|-----------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Sleep                    | Not clocked (not running)                               | Wake-up               | Not clocked                                             | None or INTOSC multiplexer<br>if Two-Speed Start-up or<br>Fail-Safe Clock Monitor are<br>enabled |

| Any Idle mode            | Not clocked (not running)                               | Wake-up               | Primary, Secondary or<br>INTOSC multiplexer             | Unchanged from Idle mode<br>(CPU operates as in<br>corresponding Run mode)                       |

| Any Run mode             | Primary or secondary<br>clocks or INTOSC<br>multiplexer | Reset                 | Primary or secondary<br>clocks or INTOSC<br>multiplexer | Unchanged from Run mode                                                                          |

#### TABLE 3-2: COMPARISON BETWEEN POWER MANAGED MODES

#### 3.2 Sleep Mode

The power managed Sleep mode in the PIC18F1220/ 1320 devices is identical to that offered in all other PIC microcontrollers. It is entered by clearing the IDLEN and SCS1:SCS0 bits (this is the Reset state) and executing the SLEEP instruction. This shuts down the primary oscillator and the OSTS bit is cleared (see Figure 3-1).

When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the system will not be clocked until the primary clock source becomes ready (see Figure 3-2), or it will be clocked from the internal oscillator block if either the Two-Speed Start-up or the Fail-Safe Clock Monitor are enabled (see **Section 19.0 "Special Features of the CPU"**). In either case, the OSTS bit is set when the primary clock is providing the system clocks. The IDLEN and SCS bits are not affected by the wake-up.

## 3.3 Idle Modes

The IDLEN bit allows the microcontroller's CPU to be selectively shut down while the peripherals continue to operate. Clearing IDLEN allows the CPU to be clocked. Setting IDLEN disables clocks to the CPU, effectively stopping program execution (see Register 2-2). The peripherals continue to be clocked regardless of the setting of the IDLEN bit.

There is one exception to how the IDLEN bit functions. When all the low-power OSCCON bits are cleared (IDLEN:SCS1:SCS0 = 000), the device enters Sleep mode upon the execution of the SLEEP instruction. This is both the Reset state of the OSCCON register and the setting that selects Sleep mode. This maintains compatibility with other PIC devices that do not offer power managed modes. If the Idle Enable bit, IDLEN (OSCCON<7>), is set to a '1' when a SLEEP instruction is executed, the peripherals will be clocked from the clock source selected using the SCS1:SCS0 bits; however, the CPU will not be clocked. Since the CPU is not executing instructions, the only exits from any of the Idle modes are by interrupt, WDT time-out or a Reset.

When a wake event occurs, CPU execution is delayed approximately 10  $\mu$ s while it becomes ready to execute code. When the CPU begins executing code, it is clocked by the same clock source as was selected in the power managed mode (i.e., when waking from RC\_IDLE mode, the internal oscillator block will clock the CPU and peripherals until the primary clock source becomes ready – this is essentially RC\_RUN mode). This continues until the primary clock source becomes ready. When the primary clock becomes ready, the OSTS bit is set and the system clock source is switched to the primary clock (see Figure 3-4). The IDLEN and SCS bits are not affected by the wake-up.

While in any Idle mode or the Sleep mode, a WDT time-out will result in a WDT wake-up to full-power operation.

## TABLE 3-3: ACTIVITY AND EXIT DELAY ON WAKE FROM SLEEP MODE OR ANY IDLE MODE (BY CLOCK SOURCES)

| Clock in Power          | Primary System               | Power<br>Managed              | Clock Ready<br>Status Bit |                                                | Wake-up from<br>aged Mode                           |

|-------------------------|------------------------------|-------------------------------|---------------------------|------------------------------------------------|-----------------------------------------------------|

| Managed Mode            | Clock                        | Mode Exit<br>Delay            | (OSCCON)                  | Exit by Interrupt                              | Exit by Reset                                       |

|                         | LP, XT, HS                   |                               | OSTS                      | CPU and peripherals                            | Not clocked or                                      |

| Primary System<br>Clock | HSPLL                        | 5-10 μs <b>(5)</b>            | 0313                      | clocked by primary clock and executing         | Two-Speed Start-up<br>(if enabled) <sup>(3)</sup> . |

| (PRI_IDLE mode)         | EC, RC, INTRC <sup>(1)</sup> | 5-10 μ3·                      |                           | instructions.                                  | (il ellabled).                                      |

| (                       | INTOSC <sup>(2)</sup>        |                               | IOFS                      |                                                |                                                     |

|                         | LP, XT, HS                   | OST                           | OSTS                      | CPU and peripherals                            |                                                     |

| T1OSC or                | HSPLL                        | OST + 2 ms                    | 0313                      | clocked by selected                            |                                                     |

| INTRC <sup>(1)</sup>    | EC, RC, INTRC <sup>(1)</sup> | 5-10 μs <b><sup>(5)</sup></b> | —                         | power managed mode clock and executing         |                                                     |

|                         | INTOSC <sup>(2)</sup>        | 1 ms <sup>(4)</sup>           | IOFS                      | instructions until                             |                                                     |

|                         | LP, XT, HS                   | OST                           | OSTS                      | primary clock source                           |                                                     |

| INTOSC <sup>(2)</sup>   | HSPLL                        | OST + 2 ms                    | 0313                      | becomes ready.                                 |                                                     |

|                         | EC, RC, INTRC <sup>(1)</sup> | 5-10 μs <b><sup>(5)</sup></b> | —                         |                                                |                                                     |

|                         | INTOSC <sup>(2)</sup>        | None                          | IOFS                      |                                                |                                                     |

|                         | LP, XT, HS                   | OST                           | OSTS                      | Not clocked or                                 |                                                     |

| Clean made              | HSPLL                        | OST + 2 ms                    | 0313                      | Two-Speed Start-up (if                         |                                                     |

| Sleep mode              | EC, RC, INTRC <sup>(1)</sup> | 5-10 μs <b><sup>(5)</sup></b> |                           | enabled) until primary<br>clock source becomes |                                                     |

|                         | INTOSC <sup>(2)</sup>        | 1 ms <sup>(4)</sup>           | IOFS                      | ready <sup>(3)</sup> .                         |                                                     |

Note 1: In this instance, refers specifically to the INTRC clock source.

2: Includes both the INTOSC 8 MHz source and postscaler derived frequencies.

3: Two-Speed Start-up is covered in greater detail in Section 19.3 "Two-Speed Start-up".

**4:** Execution continues during the INTOSC stabilization period.

5: Required delay when waking from Sleep and all Idle modes. This delay runs concurrently with any other required delays (see Section 3.3 "Idle Modes").

#### 5.9.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. A list of these registers is given in Table 5-1 and Table 5-2. The SFRs can be classified into two sets: those associated with the "core" function and those related to the peripheral functions. Those registers related to the "core" are described in this section, while those related to the operation of the peripheral features are described in the section of that peripheral feature.

The SFRs are typically distributed among the peripherals whose functions they control.

The unused SFR locations will be unimplemented and read as '0's.

#### TABLE 5-1: SPECIAL FUNCTION REGISTER MAP FOR PIC18F1220/1320 DEVICES

| ADLE 5-1. | SFECIAL                 | FUNCTION | REGISTER IVI           |         | JIOF 1220/1320 | DEVICES |         |

|-----------|-------------------------|----------|------------------------|---------|----------------|---------|---------|

| Address   | Name                    | Address  | Name                   | Address | Name           | Address | Name    |

| FFFh      | TOSU                    | FDFh     | INDF2 <sup>(2)</sup>   | FBFh    | CCPR1H         | F9Fh    | IPR1    |

| FFEh      | TOSH                    | FDEh     | POSTINC2(2)            | FBEh    | CCPR1L         | F9Eh    | PIR1    |

| FFDh      | TOSL                    | FDDh     | POSTDEC2(2)            | FBDh    | CCP1CON        | F9Dh    | PIE1    |

| FFCh      | STKPTR                  | FDCh     | PREINC2 <sup>(2)</sup> | FBCh    | _              | F9Ch    | _       |

| FFBh      | PCLATU                  | FDBh     | PLUSW2 <sup>(2)</sup>  | FBBh    | _              | F9Bh    | OSCTUNE |

| FFAh      | PCLATH                  | FDAh     | FSR2H                  | FBAh    | _              | F9Ah    | _       |

| FF9h      | PCL                     | FD9h     | FSR2L                  | FB9h    | —              | F99h    |         |

| FF8h      | TBLPTRU                 | FD8h     | STATUS                 | FB8h    | _              | F98h    | _       |

| FF7h      | TBLPTRH                 | FD7h     | TMR0H                  | FB7h    | PWM1CON        | F97h    | _       |

| FF6h      | TBLPTRL                 | FD6h     | TMR0L                  | FB6h    | ECCPAS         | F96h    |         |

| FF5h      | TABLAT                  | FD5h     | TOCON                  | FB5h    | —              | F95h    | _       |

| FF4h      | PRODH                   | FD4h     | —                      | FB4h    | —              | F94h    | _       |

| FF3h      | PRODL                   | FD3h     | OSCCON                 | FB3h    | TMR3H          | F93h    | TRISB   |

| FF2h      | INTCON                  | FD2h     | LVDCON                 | FB2h    | TMR3L          | F92h    | TRISA   |

| FF1h      | INTCON2                 | FD1h     | WDTCON                 | FB1h    | T3CON          | F91h    | _       |

| FF0h      | INTCON3                 | FD0h     | RCON                   | FB0h    | SPBRGH         | F90h    | _       |

| FEFh      | INDF0 <sup>(2)</sup>    | FCFh     | TMR1H                  | FAFh    | SPBRG          | F8Fh    | _       |

| FEEh      | POSTINC0(2)             | FCEh     | TMR1L                  | FAEh    | RCREG          | F8Eh    | _       |

| FEDh      | POSTDEC0(2)             | FCDh     | T1CON                  | FADh    | TXREG          | F8Dh    |         |

| FECh      | PREINC0 <sup>(2)</sup>  | FCCh     | TMR2                   | FACh    | TXSTA          | F8Ch    | _       |

| FEBh      | PLUSW0 <sup>(2)</sup>   | FCBh     | PR2                    | FABh    | RCSTA          | F8Bh    | —       |

| FEAh      | FSR0H                   | FCAh     | T2CON                  | FAAh    | BAUDCTL        | F8Ah    | LATB    |

| FE9h      | FSR0L                   | FC9h     | —                      | FA9h    | EEADR          | F89h    | LATA    |

| FE8h      | WREG                    | FC8h     | —                      | FA8h    | EEDATA         | F88h    | —       |

| FE7h      | INDF1 <sup>(2)</sup>    | FC7h     | —                      | FA7h    | EECON2         | F87h    | —       |

| FE6h      | POSTINC1 <sup>(2)</sup> | FC6h     | —                      | FA6h    | EECON1         | F86h    | —       |

| FE5h      | POSTDEC1 <sup>(2)</sup> | FC5h     | —                      | FA5h    |                | F85h    | —       |

| FE4h      | PREINC1 <sup>(2)</sup>  | FC4h     | ADRESH                 | FA4h    | —              | F84h    |         |

| FE3h      | PLUSW1 <sup>(2)</sup>   | FC3h     | ADRESL                 | FA3h    |                | F83h    |         |

| FE2h      | FSR1H                   | FC2h     | ADCON0                 | FA2h    | IPR2           | F82h    | —       |

| FE1h      | FSR1L                   | FC1h     | ADCON1                 | FA1h    | PIR2           | F81h    | PORTB   |

| FE0h      | BSR                     | FC0h     | ADCON2                 | FA0h    | PIE2           | F80h    | PORTA   |

|           |                         |          |                        |         |                | -       |         |

Note 1: Unimplemented registers are read as '0'.

2: This is not a physical register.

#### 6.2.2 TABLAT – TABLE LATCH REGISTER

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The table latch is used to hold 8-bit data during data transfers between program memory and data RAM.

#### 6.2.3 **TBLPTR – TABLE POINTER** REGISTER

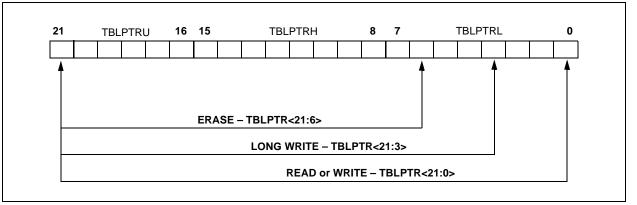

The Table Pointer (TBLPTR) addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. Setting the 22nd bit allows access to the device ID, the user ID and the configuration bits.

The Table Pointer (TBLPTR) register is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations are shown in Table 6-1. These operations on the TBLPTR only affect the low-order 21 bits.

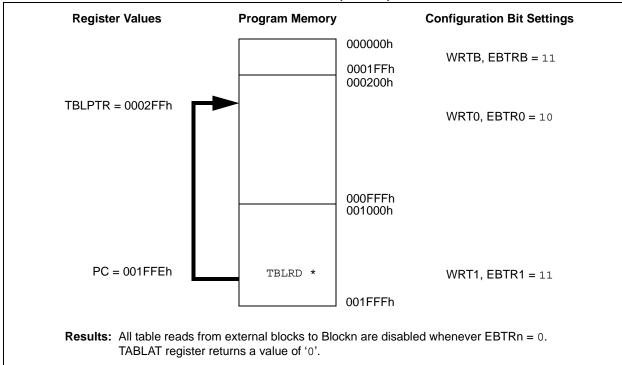

#### TABLE POINTER BOUNDARIES 6.2.4

TBLPTR is used in reads, writes and erases of the Flash program memory.

When a TBLRD is executed, all 22 bits of the Table Pointer determine which byte is read from program or configuration memory into TABLAT.

When a TBLWT is executed, the three LSbs of the Table Pointer (TBLPTR<2:0>) determine which of the eight program memory holding registers is written to. When the timed write to program memory (long write) begins, the 19 MSbs of the Table Pointer (TBLPTR<21:3>) will determine which program memory block of 8 bytes is written to (TBLPTR<2:0> are ignored). For more detail, see Section 6.5 "Writing to Flash Program Memory".

When an erase of program memory is executed, the 16 MSbs of the Table Pointer (TBLPTR<21:6>) point to the 64-byte block that will be erased. The Least Significant bits (TBLPTR<5:0>) are ignored.

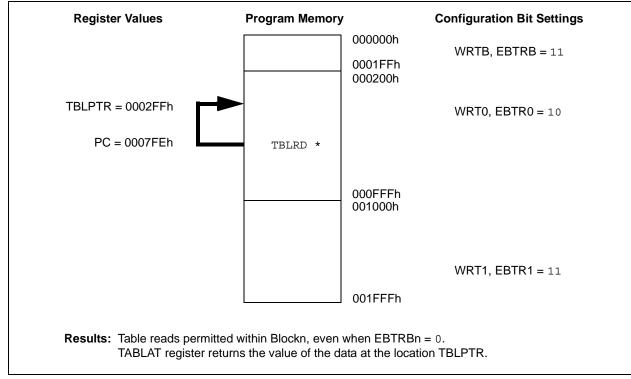

Figure 6-3 describes the relevant boundaries of TBLPTR based on Flash program memory operations.

| TABLE 6-1:         | TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS |

|--------------------|------------------------------------------------------------|

| Example            | Operation on Table Pointer                                 |

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                                     |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write                 |

TBLPTR is decremented after the read/write

TBLPTR is incremented before the read/write

#### FRATIONS WITH TRUDE AND TRUMT INSTRUCTIONS

#### FIGURE 6-3: TABLE POINTER BOUNDARIES BASED ON OPERATION

TBLRD\*-

TBLWT\*-TBLRD+\*

TBLWT+\*

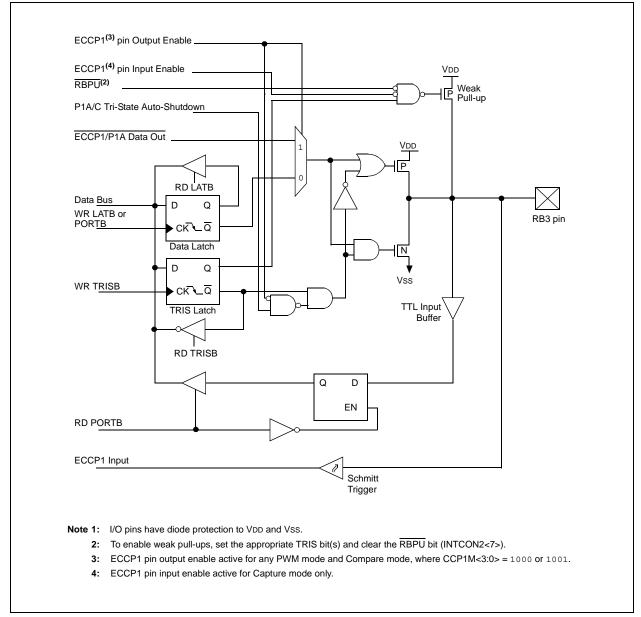

#### FIGURE 10-10: BLOCK DIAGRAM OF RB3/CCP1/P1A PIN

#### 16.3.4 AUTO-WAKE-UP ON SYNC BREAK CHARACTER

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper byte reception cannot be performed. The auto-wake-up feature allows the controller to wake-up due to activity on the RX/DT line while the EUSART is operating in Asynchronous mode.

The auto-wake-up feature is enabled by setting the WUE bit (BAUDCTL<1>). Once set, the typical receive sequence on RX/DT is disabled and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a Sync Break or a Wake-up Signal character for the LIN protocol.)

Following a wake-up event, the module generates an RCIF interrupt. The interrupt is generated synchronously to the Q clocks in normal operating modes (Figure 16-7) and asynchronously if the device is in Sleep mode (Figure 16-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared once a low-to-high transition is observed on the RX line, following the wakeup event. At this point, the EUSART module is in Idle mode and returns to normal operation. This signals to the user that the Sync Break event is over.

## 16.3.4.1 Special Considerations Using Auto-Wake-up

Since auto-wake-up functions by sensing rising edge transitions on RX/DT, information with any state changes before the Stop bit may signal a false end-of-character

and cause data or framing errors. To work properly, therefore, the initial character in the transmission must be all '0's. This can be 00h (8 bytes) for standard RS-232 devices, or 000h (12 bits) for LIN bus.

Oscillator start-up time must also be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS/PLL mode). The Sync Break (or Wake-up Signal) character must be of sufficient length and be followed by a sufficient period, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

## 16.3.4.2 Special Considerations Using the WUE Bit

The timing of WUE and RCIF events may cause some confusion when it comes to determining the validity of received data. As noted, setting the WUE bit places the EUSART in an Idle mode. The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared after this when a rising edge is seen on RX/ DT. The interrupt condition is then cleared by reading the RCREG register. Ordinarily, the data in RCREG will be dummy data and should be discarded.

The fact that the WUE bit has been cleared (or is still set) and the RCIF flag is set should not be used as an indicator of the integrity of the data in RCREG. Users should consider implementing a parallel method in firmware to verify received data integrity.

To assure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

#### FIGURE 16-7: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING NORMAL OPERATION

| 0801           | YAAAA       | pununun                               | INNUNIA.                               | 13.1 | NAMA.                                   | 17 h.    | A.A.A.   | punu   | NANANA                  | 191                                   | NA U      | 1.2 N.E            | NAMAN       | ununun                                 | 320   |

|----------------|-------------|---------------------------------------|----------------------------------------|------|-----------------------------------------|----------|----------|--------|-------------------------|---------------------------------------|-----------|--------------------|-------------|----------------------------------------|-------|

|                | 1 88.389 by | ¥286°                                 |                                        |      |                                         | 2        | 2        | e<br>e |                         |                                       |           |                    |             | alip by bas                            | i den |

| - 890,483 (ost | 4           |                                       | .2                                     |      | • • • • • • • • • • • • • • • • • • • • |          | >        | {      |                         | · · · · · · · · · · · · · · · · · · · |           |                    |             |                                        |       |

|                |             | 1<br>1                                | 2<br>2                                 |      |                                         | 5<br>- 2 | 5<br>5   | :<br>: |                         |                                       |           | 1                  | <u> </u>    |                                        |       |

| XBY Law        | *           | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · ·  | 3    | UMAAAA                                  | ÛUQ.     | ziiiiina |        |                         | Alth                                  | aaaaaaa   | We -               |             | ************************************** |       |

| ci ci ce       |             |                                       |                                        | 5 5  |                                         | 2        | 1. N     | 5      | •<br>•••••••••••••••••• |                                       |           | ۰ د<br>میں بی در د |             |                                        |       |

| RCE            |             | ·                                     | ······································ | ÷    |                                         |          |          | 9<br>• | Acres 6                 |                                       | Same.     | an it              | 80886       | Ç                                      |       |

|                | ·           |                                       |                                        |      |                                         | 1        |          | ·      | nansearena soa          |                                       | water ees | toor set           | Constraints |                                        |       |

#### FIGURE 16-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

| R/P-1            | U-0                                                                                           | U-0               | U-0  | U-0          | U-0              | U-0    | U-0   |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------|-------------------|------|--------------|------------------|--------|-------|--|--|--|--|

| MCLRE            | —                                                                                             | —                 | —    | —            | —                | —      | —     |  |  |  |  |

| bit 7            |                                                                                               |                   |      |              |                  |        | bit 0 |  |  |  |  |

|                  |                                                                                               |                   |      |              |                  |        |       |  |  |  |  |

| Legend:          |                                                                                               |                   |      |              |                  |        |       |  |  |  |  |

| R = Readable     | bit                                                                                           | W = Writable I    | bit  | U = Unimpler | mented bit, read | as '0' |       |  |  |  |  |

| u = Bit is uncha | u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |                   |      |              |                  |        |       |  |  |  |  |

| '1' = Bit is set |                                                                                               | '0' = Bit is clea | ared | P = Program  | mable bit        |        |       |  |  |  |  |

### REGISTER 19-4: CONFIG3H: CONFIGURATION REGISTER 3 HIGH (BYTE ADDRESS 300005h)

| bit 7   | MCLRE: MCLR Pin Enable bit                                |

|---------|-----------------------------------------------------------|

|         | $1 = \overline{MCLR}$ pin enabled, RA5 input pin disabled |

|         | 0 = RA5 input pin enabled, MCLR disabled                  |

| bit 6-0 | Unimplemented: Read as '0'                                |

#### REGISTER 19-5: CONFIG4L: CONFIGURATION REGISTER 4 LOW (BYTE ADDRESS 300006h)

| R/P-1 | U-0 | U-0 | U-0 | U-0 | R/P-1 | U-0 | R/P-1 |

|-------|-----|-----|-----|-----|-------|-----|-------|

| DEBUG | —   | —   | _   |     | LVP   |     | STVR  |

| bit 7 |     |     |     |     |       |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | P = Programmable bit                                  |

| bit 7   | DEBUG: Background Debugger Enable bit (see note)                                                                                                                                                 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Background debugger disabled, RB6 and RB7 configured as general purpose I/O pins</li> <li>0 = Background debugger enabled, RB6 and RB7 are dedicated to In-Circuit Debug</li> </ul> |

| bit 6-3 | Unimplemented: Read as '0'                                                                                                                                                                       |

| bit 2   | LVP: Low-Voltage ICSP Enable bit                                                                                                                                                                 |

|         | 1 = Low-Voltage ICSP enabled<br>0 = Low-Voltage ICSP disabled                                                                                                                                    |

| bit 1   | Unimplemented: Read as '0'                                                                                                                                                                       |

| bit 0   | STVR: Stack Full/Underflow Reset Enable bit                                                                                                                                                      |

|         | <ul><li>1 = Stack full/underflow will cause Reset</li><li>0 = Stack full/underflow will not cause Reset</li></ul>                                                                                |

**Note:** The Timer1 oscillator shares the T1OSI and T1OSO pins with the PGD and PGC pins used for programming and debugging.

When using the Timer1 oscillator, In-Circuit Serial Programming (ICSP) may not function correctly (high voltage or low voltage), or the In-Circuit Debugger (ICD) may not communicate with the controller. As a result of using either ICSP or ICD, the Timer1 crystal may be damaged.

If ICSP or ICD operations are required, the crystal should be disconnected from the circuit (disconnect either lead) or installed after programming. The oscillator loading capacitors may remain in-circuit during ICSP or ICD operation.

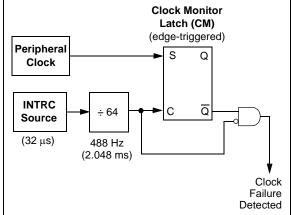

### 19.4 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the microcontroller to continue operation, in the event of an external oscillator failure, by automatically switching the system clock to the internal oscillator block. The FSCM function is enabled by setting the Fail-Safe Clock Monitor Enable bit, FSCM (CONFIG1H<6>).

When FSCM is enabled, the INTRC oscillator runs at all times to monitor clocks to peripherals and provide an instant backup clock in the event of a clock failure. Clock monitoring (shown in Figure 19-3) is accomplished by creating a sample clock signal, which is the INTRC output divided by 64. This allows ample time between FSCM sample clocks for a peripheral clock edge to occur. The peripheral system clock and the sample clock are presented as inputs to the Clock Monitor latch (CM). The CM is set on the falling edge of the system clock source, but cleared on the rising edge of the sample clock.

Clock failure is tested for on the falling edge of the sample clock. If a sample clock falling edge occurs while CM is still set, a clock failure has been detected (Figure 19-4). This causes the following:

- the FSCM generates an oscillator fail interrupt by setting bit, OSCFIF (PIR2<7>);

- the system clock source is switched to the internal oscillator block (OSCCON is not updated to show the current clock source – this is the Fail-Safe condition); and

- the WDT is reset.

Since the postscaler frequency from the internal oscillator block may not be sufficiently stable, it may be desirable to select another clock configuration and enter an alternate power managed mode (see Section 19.3.1 "Special Considerations for Using Two-Speed Start-up" and Section 3.1.3 "Multiple Sleep Commands" for more details). This can be done to attempt a partial recovery, or execute a controlled shutdown.

To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IFRC2:IFRC0, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting IFRC2:IFRC0 prior to entering Sleep mode.

Adjustments to the internal oscillator block, using the OSCTUNE register, also affect the period of the FSCM by the same factor. This can usually be neglected, as the clock frequency being monitored is generally much higher than the sample clock frequency.

The FSCM will detect failures of the primary or secondary clock sources only. If the internal oscillator block fails, no failure would be detected, nor would any action be possible.

#### 19.4.1 FSCM AND THE WATCHDOG TIMER

Both the FSCM and the WDT are clocked by the INTRC oscillator. Since the WDT operates with a separate divider and counter, disabling the WDT has no effect on the operation of the INTRC oscillator when the FSCM is enabled.

As already noted, the clock source is switched to the INTOSC clock when a clock failure is detected. Depending on the frequency selected by the IRCF2:IRCF0 bits, this may mean a substantial change in the speed of code execution. If the WDT is enabled with a small prescale value, a decrease in clock speed allows a WDT time-out to occur and a subsequent device Reset. For this reason, Fail-Safe Clock events also reset the WDT and postscaler, allowing it to start timing from when execution speed was changed and decreasing the likelihood of an erroneous time-out.

#### FIGURE 19-7: EXTERNAL BLOCK TABLE READ (EBTRn) DISALLOWED: PIC18F1320

#### FIGURE 19-8: EXTERNAL BLOCK TABLE READ (EBTRn) ALLOWED: PIC18F1320

### 19.9 Low-Voltage ICSP Programming

The LVP bit in Configuration register, CONFIG4L, enables Low-Voltage Programming (LVP). When LVP is enabled, the microcontroller can be programmed without requiring high voltage being applied to the MCLR/VPP/RA5 pin, but the RB5/PGM/KB11 pin is then dedicated to controlling Program mode entry and is not available as a general purpose I/O pin.

LVP is enabled in erased devices.

<u>While</u> programming using LVP, VDD is applied to the MCLR/VPP/RA5 pin as in normal execution mode. To enter Programming mode, VDD is applied to the PGM pin.

- Note 1: High-voltage programming is always available, regardless of the state of the LVP bit or the PGM pin, by applying VIHH to the MCLR pin.

- 2: When Low-Voltage Programming is enabled, the RB5 pin can no longer be used as a general purpose I/O pin.

- 3: When LVP is enabled, externally pull the PGM pin to Vss to allow normal program execution.

If Low-Voltage Programming mode will not be used, the LVP bit can be cleared and RB5/PGM/KBI1 becomes available as the digital I/O pin RB5. The LVP bit may be set or cleared only when using standard high-voltage programming (VIHH applied to the MCLR/VPP/RA5 pin). Once LVP has been disabled, only the standard high-voltage programming is available and must be used to program the device.

Memory that is not code-protected can be erased, using either a Block Erase, or erased row by row, then written at any specified VDD. If code-protected memory is to be erased, a Block Erase is required. If a Block Erase is to be performed when using Low-Voltage Programming, the device must be supplied with VDD of 4.5V to 5.5V.

# PIC18F1220/1320

| ANDWF AND W with f                                                                                                                                                                                                                                                                                     |                        |                                |      |                       |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------------|------|-----------------------|--|--|--|

| Syntax:                                                                                                                                                                                                                                                                                                | f [,d [,a              | a]]                            |      |                       |  |  |  |

| Operands:                                                                                                                                                                                                                                                                                              |                        | $0 \le f \le 255$              |      |                       |  |  |  |

|                                                                                                                                                                                                                                                                                                        | a ∈ [0,1]<br>a ∈ [0,1] | $d \in [0,1]$<br>$a \in [0,1]$ |      |                       |  |  |  |

| Operation:                                                                                                                                                                                                                                                                                             | (W) .AND.              | (f) $\rightarrow$ des          | t    |                       |  |  |  |

| Status Affected:                                                                                                                                                                                                                                                                                       | N, Z                   |                                |      |                       |  |  |  |

| Encoding:                                                                                                                                                                                                                                                                                              | 0001                   | 01da i                         | Efff | ffff                  |  |  |  |

| Description: The contents of W are AND'ed with<br>register 'f'. If 'd' is '0', the result is<br>stored in W. If 'd' is '1', the result is<br>stored back in register 'f' (default).<br>If 'a' is '0', the Access Bank will be<br>selected. If 'a' is '1', the BSR will<br>not be overridden (default). |                        |                                |      |                       |  |  |  |

| Words:                                                                                                                                                                                                                                                                                                 | 1                      | 1                              |      |                       |  |  |  |

| Cycles:                                                                                                                                                                                                                                                                                                | 1                      | 1                              |      |                       |  |  |  |

| Q Cycle Activity:                                                                                                                                                                                                                                                                                      |                        |                                |      |                       |  |  |  |

| Q1                                                                                                                                                                                                                                                                                                     | Q2                     | Q3                             |      | Q4                    |  |  |  |

| Decode                                                                                                                                                                                                                                                                                                 | Read<br>register 'f'   | Process<br>Data                | -    | Vrite to<br>stination |  |  |  |

| Example:                                                                                                                                                                                                                                                                                               | ANDWF                  | REG, W                         |      |                       |  |  |  |

| Before Instru                                                                                                                                                                                                                                                                                          | ction                  |                                |      |                       |  |  |  |

| W<br>REG                                                                                                                                                                                                                                                                                               | = 0x17<br>= 0xC2       | •••••                          |      |                       |  |  |  |

| After Instruct                                                                                                                                                                                                                                                                                         | ion                    |                                |      |                       |  |  |  |

| W<br>REG                                                                                                                                                                                                                                                                                               | = 0x02<br>= 0xC2       |                                |      |                       |  |  |  |

|                                                                                                                                                                                                                                                                                                        |                        |                                |      |                       |  |  |  |

| Suptor                                                |                                                        | [label] D                                                                        | [ <i>label</i> ] BC n                                                                                                                                                                                                                                                                 |                                            |  |  |  |

|-------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|--|--|

| Syntax:                                               |                                                        |                                                                                  |                                                                                                                                                                                                                                                                                       |                                            |  |  |  |

| Operand                                               | ds:                                                    | -128 ≤ n ≤                                                                       | 127                                                                                                                                                                                                                                                                                   |                                            |  |  |  |

| Operatio                                              | on:                                                    |                                                                                  | if Carry bit is '1'<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                 |                                            |  |  |  |

| Status A                                              | ffected:                                               | None                                                                             |                                                                                                                                                                                                                                                                                       |                                            |  |  |  |

| Encoding                                              | g:                                                     | 1110                                                                             | 0010 nni                                                                                                                                                                                                                                                                              | nn nnnn                                    |  |  |  |

| Descripti                                             |                                                        | program w<br>The 2's co<br>added to t<br>have incre<br>instruction<br>PC + 2 + 2 | If the Carry bit is '1', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then<br>a 2-cycle instruction. |                                            |  |  |  |

| 14/                                                   |                                                        | 1                                                                                |                                                                                                                                                                                                                                                                                       |                                            |  |  |  |

| Words:                                                |                                                        | 1                                                                                |                                                                                                                                                                                                                                                                                       |                                            |  |  |  |

| Words:<br>Cycles:                                     |                                                        | 1(2)                                                                             |                                                                                                                                                                                                                                                                                       |                                            |  |  |  |

| Cycles:                                               | e Activity:                                            | 1(2)                                                                             |                                                                                                                                                                                                                                                                                       |                                            |  |  |  |

| Cycles:<br>Q Cycle                                    | •                                                      | 1(2)                                                                             | Q3                                                                                                                                                                                                                                                                                    | Q4                                         |  |  |  |

| Cycles:<br>Q Cycle<br>If Jump:                        | :                                                      | 1(2)                                                                             | Q3<br>Process<br>Data                                                                                                                                                                                                                                                                 |                                            |  |  |  |

| Cycles:<br>Q Cycle<br>If Jump:                        | :<br>Q1                                                | 1(2)<br>Q2<br>Read literal                                                       | Process                                                                                                                                                                                                                                                                               | Q4<br>Write to P0<br>No                    |  |  |  |

| Cycles:<br>Q Cycle<br>If Jump:                        | :<br>Q1<br>Decode                                      | 1(2)<br>Q2<br>Read literal<br>'n'                                                | Process<br>Data                                                                                                                                                                                                                                                                       | Write to PO                                |  |  |  |

| Cycles:<br>Q Cycle<br>If Jump:                        | Q1<br>Decode<br>No<br>Deration                         | 1(2)<br>Q2<br>Read literal<br>'n'<br>No                                          | Process<br>Data<br>No                                                                                                                                                                                                                                                                 | Write to PO                                |  |  |  |

| Cycles:<br>Q Cycle<br>If Jump:<br>D                   | Q1<br>Decode<br>No<br>Deration                         | 1(2)<br>Q2<br>Read literal<br>'n'<br>No                                          | Process<br>Data<br>No                                                                                                                                                                                                                                                                 | Write to PO                                |  |  |  |

| Cycles:<br>Q Cycle<br>If Jump:<br>D<br>op<br>If No Ju | Calleration                                            | 1(2)<br>Q2<br>Read literal<br>'n'<br>No<br>operation                             | Process<br>Data<br>No<br>operation                                                                                                                                                                                                                                                    | Write to PO<br>No<br>operation<br>Q4<br>No |  |  |  |

| Cycles:<br>Q Cycle<br>If Jump:<br>D<br>op<br>If No Ju | Q1<br>Decode<br>No<br>peration<br>Imp:<br>Q1           | 1(2)<br>Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2<br>Read literal       | Process<br>Data<br>No<br>operation<br>Q3<br>Process                                                                                                                                                                                                                                   | Write to PO<br>No<br>operation<br>Q4       |  |  |  |