Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 4KB (2K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 × 8                                                                    |

| RAM Size                   | 256 × 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 7x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1220t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 3.0 POWER MANAGED MODES

The PIC18F1220/1320 devices offer a total of six operating modes for more efficient power management (see Table 3-1). These provide a variety of options for selective power conservation in applications where resources may be limited (i.e., battery powered devices).

There are three categories of power managed modes:

- Sleep mode

- Idle modes

- Run modes

These categories define which portions of the device are clocked and sometimes, what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or INTOSC multiplexer); the Sleep mode does not use a clock source.

The clock switching feature offered in other PIC18 devices (i.e., using the Timer1 oscillator in place of the primary oscillator) and the Sleep mode offered by all PIC<sup>®</sup> devices (where all system clocks are stopped) are both offered in the PIC18F1220/1320 devices (SEC\_RUN and Sleep modes, respectively). However, additional power managed modes are available that allow the user greater flexibility in determining what portions of the device are operating. The power managed modes are event driven; that is, some specific event must occur for the device to enter or (more particularly) exit these operating modes.

For PIC18F1220/1320 devices, the power managed modes are invoked by using the existing SLEEP instruction. All modes exit to PRI\_RUN mode when triggered by an interrupt, a Reset or a WDT time-out (PRI\_RUN mode is the normal full-power execution mode; the CPU and peripherals are clocked by the primary oscillator source). In addition, power managed Run modes may also exit to Sleep mode, or their corresponding Idle mode.

### 3.1 Selecting Power Managed Modes

Selecting a power managed mode requires deciding if the CPU is to be clocked or not and selecting a clock source. The IDLEN bit controls CPU clocking, while the SCS1:SCS0 bits select a clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 3-1.

#### 3.1.1 CLOCK SOURCES

The clock source is selected by setting the SCS bits of the OSCCON register (Register 2-2). Three clock sources are available for use in power managed Idle modes: the primary clock (as configured in Configuration Register 1H), the secondary clock (Timer1 oscillator) and the internal oscillator block. The secondary and internal oscillator block sources are available for the power managed modes (PRI\_RUN mode is the normal full-power execution mode; the CPU and peripherals are clocked by the primary oscillator source).

|          | osco         | CON Bits           | Module Clocking |             |                                                                                                            |

|----------|--------------|--------------------|-----------------|-------------|------------------------------------------------------------------------------------------------------------|

| Mode     | IDLEN<br><7> | SCS1:SCS0<br><1:0> | CPU             | Peripherals | Available Clock and Oscillator Source                                                                      |

| Sleep    | 0            | 00                 | Off             | Off         | None – All clocks are disabled                                                                             |

| PRI_RUN  | 0            | 00                 | Clocked         | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC, INTRC <sup>(1)</sup><br>This is the normal full-power execution mode. |

| SEC_RUN  | 0            | 01                 | Clocked         | Clocked     | Secondary – Timer1 Oscillator                                                                              |

| RC_RUN   | 0            | 1x                 | Clocked         | Clocked     | Internal Oscillator Block <sup>(1)</sup>                                                                   |

| PRI_IDLE | 1            | 00                 | Off             | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC                                                                        |

| SEC_IDLE | 1            | 01                 | Off             | Clocked     | Secondary – Timer1 Oscillator                                                                              |

| RC_IDLE  | 1            | 1x                 | Off             | Clocked     | Internal Oscillator Block <sup>(1)</sup>                                                                   |

#### TABLE 3-1: POWER MANAGED MODES

**Note 1:** Includes INTOSC and INTOSC postscaler, as well as the INTRC source.

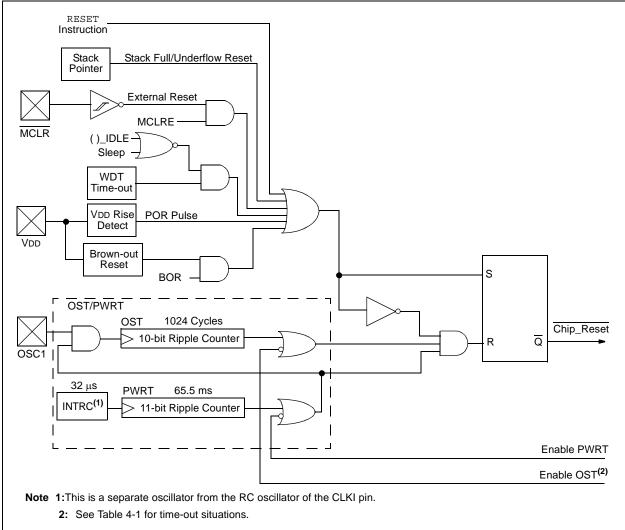

## 4.0 RESET

The PIC18F1220/1320 devices differentiate between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during Sleep

- d) Watchdog Timer (WDT) Reset (during execution)

- e) Programmable Brown-out Reset (BOR)

- f) RESET Instruction

- g) Stack Full Reset

- h) Stack Underflow Reset

Most registers are unaffected by a Reset. Their status is unknown on POR and unchanged by all other Resets. The other registers are forced to a "Reset state", depending on the type of Reset that occurred. Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register (Register 5-2), RI, TO, PD, POR and BOR, are set or cleared differently in different Reset situations, as indicated in Table 4-2. These bits are used in software to determine the nature of the Reset. See Table 4-3 for a full description of the Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 4-1.

The Enhanced MCU devices have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

The  $\overline{\text{MCLR}}$  pin is not driven low by any internal Resets, including the WDT.

The  $\overline{\text{MCLR}}$  input provided by the  $\overline{\text{MCLR}}$  pin can be disabled with the MCLRE bit in Configuration Register 3H (CONFIG3H<7>).

### 5.8 Look-up Tables

Look-up tables are implemented two ways:

- Computed GOTO

- Table Reads

## 5.8.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (see Example 5-4).

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW 0xnn instructions. WREG is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW 0xnn instructions, that returns the value 0xnn to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSB = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 5-4: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVFW  | OFFSET |

|-------|--------|--------|

|       | CALL   | TABLE  |

| ORG   | 0xnn00 |        |

| TABLE | ADDWF  | PCL    |

|       | RETLW  | 0xnn   |

|       | RETLW  | 0xnn   |

|       | RETLW  | 0xnn   |

|       |        |        |

|       |        |        |

|       |        |        |

|       |        |        |

### 5.8.2 TABLE READS/TABLE WRITES

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word by using table reads and writes. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from or written to program memory. Data is transferred to/from program memory, one byte at a time.

The table read/table write operation is discussed further in Section 6.1 "Table Reads and Table Writes".

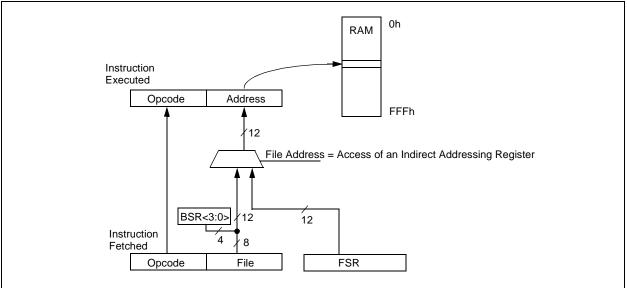

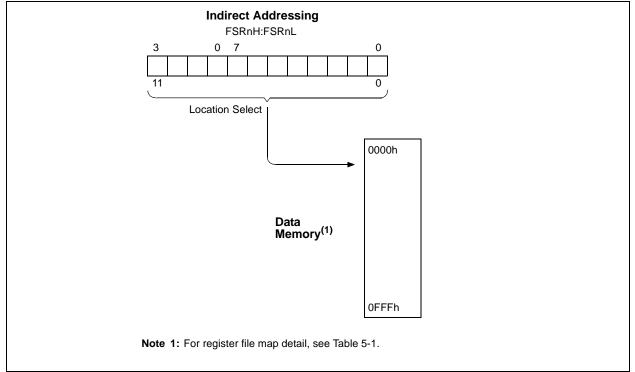

## 5.9 Data Memory Organization

The data memory is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. Figure 5-6 shows the data memory organization for the PIC18F1220/1320 devices.

The data memory map is divided into as many as 16 banks that contain 256 bytes each. The lower four bits of the Bank Select Register (BSR<3:0>) select which bank will be accessed. The upper four bits for the BSR are not implemented.

The data memory contains Special Function Registers (SFR) and General Purpose Registers (GPR). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratch pad operations in the user's application. The SFRs start at the last location of Bank 15 (FFFh) and extend towards F80h. Any remaining space beyond the SFRs in the Bank may be implemented as GPRs. GPRs start at the first location of Bank 0 and grow upwards. Any read of an unimplemented location will read as '0's.

The entire data memory may be accessed directly or indirectly. Direct addressing may require the use of the BSR register. Indirect addressing requires the use of a File Select Register (FSRn) and a corresponding Indirect File Operand (INDFn). Each FSR holds a 12-bit address value that can be used to access any location in the Data Memory map without banking. See Section 5.12 "Indirect Addressing, INDF and FSR Registers" for indirect addressing details.

The instruction set and architecture allow operations across all banks. This may be accomplished by indirect addressing or by the use of the MOVFF instruction. The MOVFF instruction is a two-word/two-cycle instruction that moves a value from one register to another.

To ensure that commonly used registers (SFRs and select GPRs) can be accessed in a single cycle, regardless of the current BSR values, an Access Bank is implemented. A segment of Bank 0 and a segment of Bank 15 comprise the Access RAM. **Section 5.10 "Access Bank"** provides a detailed description of the Access RAM.

#### 5.9.1 GENERAL PURPOSE REGISTER FILE

Enhanced MCU devices may have banked memory in the GPR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

Data RAM is available for use as GPR registers by all instructions. The second half of Bank 15 (F80h to FFFh) contains SFRs. All other banks of data memory contain GPRs, starting with Bank 0.

## FIGURE 5-9: INDIRECT ADDRESSING

### EXAMPLE 6-3: WRITING TO FLASH PROGRAM MEMORY

|            | MOVLW<br>MOVWF | D'64<br>COUNTER  | ; | number of bytes in erase block           |

|------------|----------------|------------------|---|------------------------------------------|

|            | MOVWF          |                  | ; | point to buffer                          |

|            | MOVWF          | FSR0H            |   |                                          |

|            | MOVLW          | BUFFER_ADDR_LOW  |   |                                          |

|            | MOVWF          | FSROL            |   |                                          |

|            | MOVLW          | CODE_ADDR_UPPER  | ; | Load TBLPTR with the base                |

|            | MOVWF          | TBLPTRU          | ; | address of the memory block              |

|            | MOVLW          | CODE_ADDR_HIGH   |   | -                                        |

|            | MOVWF          | TBLPTRH          |   |                                          |

|            | MOVLW          |                  | ; | 6 LSB = 0                                |

|            | MOVWF          | TBLPTRL          |   |                                          |

| READ_BLOCK | _              |                  |   |                                          |

|            | TBLRD*+        | F                | ; | read into TABLAT, and inc                |

|            | MOVF           | TABLAT, W        | ; | get data                                 |

|            | MOVWF          | POSTINC0         | ; | store data and increment FSR0            |

|            | DECFSZ         | COUNTER          | ; | done?                                    |

|            | GOTO           | READ_BLOCK       | ; | repeat                                   |

| MODIFY_WOR | D              |                  |   |                                          |

|            | MOVLW          | DATA_ADDR_HIGH   | ; | point to buffer                          |

|            | MOVWF          | FSROH            |   |                                          |

|            | MOVLW          | DATA_ADDR_LOW    |   |                                          |

|            | MOVWF          | FSROL            |   |                                          |

|            | MOVLW          | NEW_DATA_LOW     | ; | update buffer word and increment FSR0    |

|            | MOVWF          | POSTINC0         |   |                                          |

|            | MOVLW          | NEW_DATA_HIGH    | ; | update buffer word                       |

|            | MOVWF          | INDF0            |   |                                          |

| ERASE_BLOC | !K             |                  |   |                                          |

|            | MOVLW          | CODE_ADDR_UPPER  | ; | load TBLPTR with the base                |

|            | MOVWF          | TBLPTRU          | ; | address of the memory block              |

|            | MOVLW          | CODE_ADDR_HIGH   |   |                                          |

|            | MOVWF          | TBLPTRH          |   |                                          |

|            | MOVLW          | CODE_ADDR_LOW    | ; | 6 LSB = 0                                |

|            | MOVWF          | TBLPTRL          |   |                                          |

|            | BCF            | EECON1, CFGS     | ; | point to PROG/EEPROM memory              |

|            | BSF            | EECON1, EEPGD    | ; | point to FLASH program memory            |

|            | BSF            | EECON1, WREN     | ; | enable write to memory                   |

|            | BSF            | EECON1, FREE     | ; | enable Row Erase operation               |

|            | BCF            | INTCON, GIE      | ; | disable interrupts                       |

|            | MOVLW          | 55h              | ; | Required sequence                        |

|            | MOVWF          | EECON2           | ; | write 55H                                |

|            | MOVLW          | AAh              |   |                                          |

|            | MOVWF          | EECON2           | ; | write AAH                                |

|            | BSF            | EECON1, WR       | ; | start erase (CPU stall)                  |

|            | NOP            |                  |   |                                          |

|            | BSF            | INTCON, GIE      | ; | re-enable interrupts                     |

| WRITE_BUFF | 'ER_BACK       |                  |   |                                          |

|            | MOVLW          | 8                | ; | number of write buffer groups of 8 bytes |

|            | MOVWF          | COUNTER_HI       |   |                                          |

|            | MOVLW          | BUFFER_ADDR_HIGH | ; | point to buffer                          |

|            | MOVWF          | FSROH            |   |                                          |

|            | MOVLW          | BUFFER_ADDR_LOW  |   |                                          |

|            | MOVWF          | FSROL            |   |                                          |

| PROGRAM_LC | OP             |                  |   |                                          |

|            | MOVLW          | 8                | ; | number of bytes in holding register      |

|            | MOVWF          | COUNTER          |   |                                          |

|            |                |                  |   |                                          |

### 7.7 Operation During Code-Protect

Data EEPROM memory has its own code-protect bits in Configuration Words. External read and write operations are disabled if either of these mechanisms are enabled.

The microcontroller itself can both read and write to the internal data EEPROM, regardless of the state of the code-protect Configuration bit. Refer to Section 19.0 "Special Features of the CPU" for additional information.

#### 7.8 Using the Data EEPROM

The data EEPROM is a high endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). Frequently changing values will typically be updated more often than specification D124. If this is not the case, an array refresh must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

A simple data EEPROM refresh routine is shown in Example 7-3.

**Note:** If data EEPROM is only used to store constants and/or data that changes rarely, an array refresh is likely not required. See specification D124.

|      | LL I=0. |               |                              |

|------|---------|---------------|------------------------------|

|      | CLRF    | EEADR         | ; Start at address 0         |

|      | BCF     | EECON1, CFGS  | ; Set for memory             |

|      | BCF     | EECON1, EEPGD | ; Set for Data EEPROM        |

|      | BCF     | INTCON, GIE   | ; Disable interrupts         |

|      | BSF     | EECON1, WREN  | ; Enable writes              |

| Loop |         |               | ; Loop to refresh array      |

|      | BSF     | EECON1, RD    | ; Read current address       |

|      | MOVLW   | 55h           | ;                            |

|      | MOVWF   | EECON2        | ; Write 55h                  |

|      | MOVLW   | AAh           | ;                            |

|      | MOVWF   | EECON2        | ; Write AAh                  |

|      | BSF     | EECON1, WR    | ; Set WR bit to begin write  |

|      | BTFSC   | EECON1, WR    | ; Wait for write to complete |

|      | BRA     | \$-2          |                              |

|      | INCFSZ  | EEADR, F      | ; Increment address          |

|      | BRA     | Loop          | ; Not zero, do it again      |

|      | BCF     | EECON1, WREN  | ; Disable writes             |

|      | BSF     | INTCON, GIE   |                              |

|      |         |               |                              |

#### EXAMPLE 7-3: DATA EEPROM REFRESH ROUTINE

| Name   | Bit 7    | Bit 6          | Bit 5         | Bit 4        | Bit 3   | Bit 2  | Bit 1  | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|----------------|---------------|--------------|---------|--------|--------|-------|-----------------------|---------------------------------|

| INTCON | GIE/GIEH | PEIE/GIEL      | TMR0IE        | INTE         | RBIE    | TMR0IF | INTF   | RBIF  | 0000 000x             | 0000 000u                       |

| EEADR  | EEPROM A | ddress Regis   | ter           |              |         |        |        |       | 0000 0000             | 0000 0000                       |

| EEDATA | EEPROM D | ata Register   |               |              |         |        |        |       | 0000 0000             | 0000 0000                       |

| EECON2 | EEPROM C | ontrol Registe | er 2 (not a p | ohysical reg | gister) |        |        |       | _                     | _                               |

| EECON1 | EEPGD    | CFGS           | _             | FREE         | WRERR   | WREN   | WR     | RD    | xx-0 x000             | uu-0 u000                       |

| IPR2   | OSCFIP   | _              | _             | EEIP         | —       | LVDIP  | TMR3IP | —     | 11 -11-               | 11 -11-                         |

| PIR2   | OSCFIF   | _              | —             | EEIF         | _       | LVDIF  | TMR3IF | _     | 00 -00-               | 00 -00-                         |

| PIE2   | OSCFIE   | _              | —             | EEIE         | _       | LVDIE  | TMR3IE | _     | 00 -00-               | 00 -00-                         |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

© 2002-2015 Microchip Technology Inc.

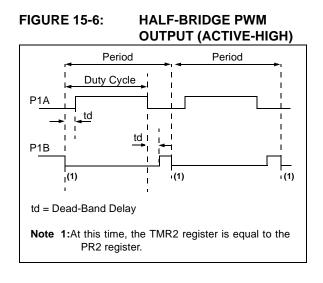

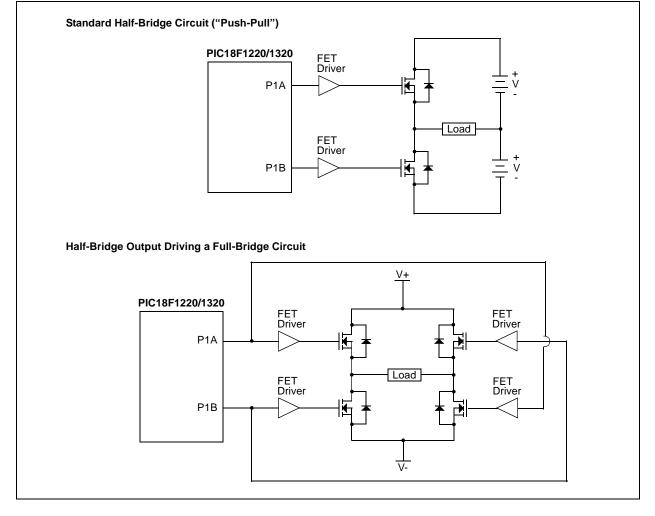

### 15.5.4 HALF-BRIDGE MODE

In the Half-Bridge Output mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the RB3/CCP1/P1A pin, while the complementary PWM output signal is output on the RB2/P1B/INT2 pin (Figure 15-6). This mode can be used for half-bridge applications, as shown in Figure 15-7, or for full-bridge applications, where four power switches are being modulated with two PWM signals.

In Half-Bridge Output mode, the programmable deadband delay can be used to prevent shoot-through current in half-bridge power devices. The value of bits, PDC6:PDC0 (PWM1CON<6:0>), sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **Section 15.5.6 "Programmable Dead-Band Delay"** for more details of the dead-band delay operations. The TRISB<3> and TRISB<2> bits must be cleared to configure P1A and P1B as outputs.

## FIGURE 15-7: EXAMPLES OF HALF-BRIDGE OUTPUT MODE APPLICATIONS

## 16.0 ENHANCED ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Addressable Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The Enhanced Addressable USART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These features make it ideally suited for use in Local Interconnect Network (LIN) bus systems.

The EUSART can be configured in the following modes:

- Asynchronous (full duplex) with:

- Auto-wake-up on character reception

- Auto-baud calibration

- 12-bit Break character transmission

- Synchronous Master (half duplex) with selectable clock polarity

- Synchronous Slave (half duplex) with selectable clock polarity

The RB1/AN5/TX/CK/INT1 and RB4/AN6/RX/DT/KBI0 pins must be configured as follows for use with the Universal Synchronous Asynchronous Receiver Transmitter:

- SPEN (RCSTA<7>) bit must be set ( = 1),

- PCFG6:PCFG5 (ADCON1<5:6>) must be set ( = 1),

- TRISB<4> bit must be set ( = 1) and

- TRISB<1> bit must be set ( = 1).

The operation of the Enhanced USART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCTL)

These are detailed in on the following pages in Register 16-1, Register 16-2 and Register 16-3, respectively.

## 16.1 Asynchronous Operation in Power Managed Modes

The EUSART may operate in Asynchronous mode while the peripheral clocks are being provided by the internal oscillator block. This makes it possible to remove the crystal or resonator that is commonly connected as the primary clock on the OSC1 and OSC2 pins.

The factory calibrates the internal oscillator block output (INTOSC) for 8 MHz (see Table 22-6). However, this frequency may drift as VDD or temperature changes and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output back to 8 MHz. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source (see **Section 3.6 "INTOSC Frequency Drift**" for more information).

The other method adjusts the value in the Baud Rate Generator (BRG). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

| U-0                                      | R-1                                        | U-0                                                                              | R/W-0/0        | R/W-0/0      | U-0              | R/W-0/0          | R/W-0/0        |

|------------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------|----------------|--------------|------------------|------------------|----------------|

| _                                        | RCIDL                                      | —                                                                                | SCKP           | BRG16        | _                | WUE              | ABDEN          |

| bit 7                                    |                                            |                                                                                  |                |              |                  |                  | bit 0          |

|                                          |                                            |                                                                                  |                |              |                  |                  |                |

| Legend:                                  |                                            |                                                                                  |                |              |                  |                  |                |

| R = Readab                               |                                            | W = Writable                                                                     |                | •            | mented bit, read |                  |                |

| u = Bit is unchanged<br>'1' = Bit is set |                                            | x = Bit is unkt                                                                  |                | -n/n = Value | at POR and BC    | R/Value at all o | ther Resets    |

|                                          |                                            | '0' = Bit is cle                                                                 | ared           |              |                  |                  |                |

| bit 7                                    | Unimplemen                                 | ted: Read as '                                                                   | 0'             |              |                  |                  |                |

| bit 6                                    | -                                          | ive Operation                                                                    |                |              |                  |                  |                |

|                                          | 1 = Receiver<br>0 = Receiver               |                                                                                  |                |              |                  |                  |                |

| bit 5                                    | Unimplemen                                 | ted: Read as '                                                                   | 0'             |              |                  |                  |                |

| bit 4                                    | SCKP: Synch                                | ronous Clock                                                                     | Polarity Selec | t bit        |                  |                  |                |

|                                          | Asynchronous<br>Unused in this             |                                                                                  |                |              |                  |                  |                |

|                                          |                                            | mode:<br>for clock (CK)<br>for clock (CK)                                        | •              | I            |                  |                  |                |

| bit 3                                    | <b>BRG16:</b> 16-b                         | it Baud Rate R                                                                   | egister Enabl  | e bit        |                  |                  |                |

|                                          |                                            |                                                                                  |                | H and SPBRC  |                  | RGH value igno   | ored           |

| bit 2                                    | Unimplemen                                 | ted: Read as '                                                                   | 0'             |              |                  |                  |                |

| bit 1                                    | WUE: Wake-                                 | up Enable bit                                                                    |                |              |                  |                  |                |

|                                          | hardware                                   | will continue t<br>on following r<br>ot monitored o<br><u>mode:</u>              | ising edge     |              | rupt generated   | on falling edge; | bit cleared in |

| bit 0                                    |                                            | -Baud Detect                                                                     | Enable bit     |              |                  |                  |                |

|                                          | Asynchronous<br>1 = Enable b<br>cleared in | <u>s mode:</u><br>aud rate meas<br>n hardware up<br>e measuremen<br><u>mode:</u> | urement on th  |              | er – requires re | eception of a Sy | nc byte (55h); |

## REGISTER 16-3: BAUDCTL: BAUD RATE CONTROL REGISTER

#### 19.4.2 EXITING FAIL-SAFE OPERATION

The Fail-Safe condition is terminated by either a device Reset, or by entering a power managed mode. On Reset, the controller starts the primary clock source specified in Configuration Register 1H (with any required start-up delays that are required for the oscillator mode, such as OST or PLL timer). The INTOSC multiplexer provides the system clock until the primary clock source becomes ready (similar to a Two-Speed Start-up). The clock system source is then switched to the primary clock (indicated by the OSTS bit in the OSCCON register becoming set). The Fail-Safe Clock Monitor then resumes monitoring the peripheral clock.

The primary clock source may never become ready during start-up. In this case, operation is clocked by the INTOSC multiplexer. The OSCCON register will remain in its Reset state until a power managed mode is entered.

Entering a power managed mode by loading the OSCCON register and executing a SLEEP instruction will clear the Fail-Safe condition. When the Fail-Safe condition is cleared, the clock monitor will resume monitoring the peripheral clock.

#### 19.4.3 FSCM INTERRUPTS IN POWER MANAGED MODES

As previously mentioned, entering a power managed mode clears the Fail-Safe condition. By entering a power managed mode, the clock multiplexer selects the clock source selected by the OSCCON register. Fail-Safe monitoring of the power managed clock source resumes in the power managed mode.

If an oscillator failure occurs during power managed operation, the subsequent events depend on whether or not the oscillator failure interrupt is enabled. If enabled (OSCFIF = 1), code execution will be clocked by the INTOSC multiplexer. An automatic transition back to the failed clock source will not occur.

If the interrupt is disabled, the device will not exit the power managed mode on oscillator failure. Instead, the device will continue to operate as before, but clocked by the INTOSC multiplexer. While in Idle mode, subsequent interrupts will cause the CPU to begin executing instructions while being clocked by the INTOSC multiplexer. The device will not transition to a different clock source until the Fail-Safe condition is cleared.

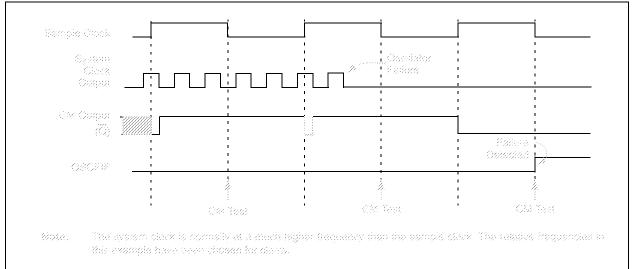

#### FIGURE 19-4: FSCM TIMING DIAGRAM

# 19.5 Program Verification and Code Protection

The overall structure of the code protection on the PIC18 Flash devices differs significantly from other PIC devices.

The user program memory is divided into three blocks. One of these is a boot block of 512 bytes. The remainder of the memory is divided into two blocks on binary boundaries. Each of the three blocks has three protection bits associated with them. They are:

- Code-Protect bit (CPn)

- Write-Protect bit (WRTn)

- External Block Table Read bit (EBTRn)

Figure 19-5 shows the program memory organization for 4 and 8-Kbyte devices and the specific code protection bit associated with each block. The actual locations of the bits are summarized in Table 19-3.

#### FIGURE 19-5: CODE-PROTECTED PROGRAM MEMORY FOR PIC18F1220/1320

| Block Code                      |                    | MEMORY S                   | IZE/DEVICE                 |                    | Block Code                      |

|---------------------------------|--------------------|----------------------------|----------------------------|--------------------|---------------------------------|

| Protection<br>Controlled By:    | Address<br>Range   | 4 Kbytes<br>(PIC18F1220)   | 8 Kbytes<br>(PIC18F1320)   | Address<br>Range   | Protection<br>Controlled By:    |

| CPB, WRTB, EBTRB                | 000000h<br>0001FFh | Boot Block                 | Boot Block                 | 000000h<br>0001FFh | CPB, WRTB, EBTRB                |

| CP0, WRT0, EBTR0                | 000200h<br>0007FFh | Block 0                    | Block 0                    | 000200h            | CP0, WRT0, EBTR0                |

| CP1, WRT1, EBTR1                | 000800h<br>000FFFh | Block 1                    |                            | 000FFFh            |                                 |

|                                 | 001000h            |                            | Block 1                    | 001000h            | CP1, WRT1, EBTR1                |

| (Unimplemented<br>Memory Space) |                    | Unimplemented<br>Read '0's |                            | 001FFFh<br>002000h |                                 |

|                                 |                    |                            | Unimplemented<br>Read '0's |                    | (Unimplemented<br>Memory Space) |

|                                 | 1FFFFFh            |                            |                            | 1FFFFFh            |                                 |

#### TABLE 19-3: SUMMARY OF CODE PROTECTION REGISTERS

| File    | Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| 300008h | CONFIG5L |       | —     |       | —     | —     |       | CP1   | CP0   |

| 300009h | CONFIG5H | CPD   | CPB   | _     | —     | —     | _     | —     | _     |

| 30000Ah | CONFIG6L | —     | —     | _     | —     | —     | _     | WRT1  | WRT0  |

| 30000Bh | CONFIG6H | WRTD  | WRTB  | WRTC  | —     | —     | _     | —     | _     |

| 30000Ch | CONFIG7L | —     | —     | _     | —     | —     | _     | EBTR1 | EBTR0 |

| 30000Dh | CONFIG7H | _     | EBTRB |       |       | _     |       |       | —     |

**Legend:** Shaded cells are unimplemented.

<sup>© 2002-2015</sup> Microchip Technology Inc.

| POP         |                                    | Рор Тор                                                                                   | Pop Top of Return Stack                                                                                                                                                                                                                                                                          |                      |                 |  |  |

|-------------|------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------|--|--|

| Synta       | ax:                                | [ label ]                                                                                 | POP                                                                                                                                                                                                                                                                                              |                      |                 |  |  |

| Oper        | ands:                              | None                                                                                      |                                                                                                                                                                                                                                                                                                  |                      |                 |  |  |

| Oper        | ation:                             | $(TOS) \rightarrow$                                                                       | bit buck                                                                                                                                                                                                                                                                                         | et                   |                 |  |  |

| Statu       | is Affected:                       | None                                                                                      |                                                                                                                                                                                                                                                                                                  |                      |                 |  |  |

| Enco        | oding:                             | 0000                                                                                      | 0000                                                                                                                                                                                                                                                                                             | 0000                 | 0110            |  |  |

| Desc        | ription:                           | return sta<br>TOS valu<br>previous<br>onto the r<br>This instr<br>enable th<br>the return | The TOS value is pulled off the<br>return stack and is discarded. The<br>TOS value then becomes the<br>previous value that was pushed<br>onto the return stack.<br>This instruction is provided to<br>enable the user to properly manage<br>the return stack to incorporate a<br>software stack. |                      |                 |  |  |

| Word        | ds:                                | 1                                                                                         |                                                                                                                                                                                                                                                                                                  |                      |                 |  |  |

| Cycle       | es:                                | 1                                                                                         |                                                                                                                                                                                                                                                                                                  |                      |                 |  |  |

| QC          | ycle Activity:                     |                                                                                           |                                                                                                                                                                                                                                                                                                  |                      |                 |  |  |

| -           | Q1                                 | Q2                                                                                        | Q                                                                                                                                                                                                                                                                                                | 3                    | Q4              |  |  |

|             | Decode                             | No<br>operation                                                                           | Pop T<br>valu                                                                                                                                                                                                                                                                                    |                      | No<br>operation |  |  |

| <u>Exan</u> | nple:                              | POP<br>GOTO                                                                               | NEW                                                                                                                                                                                                                                                                                              |                      |                 |  |  |

| I           | Before Instru<br>TOS<br>Stack (1 I | iction<br>evel down)                                                                      |                                                                                                                                                                                                                                                                                                  | )x0031A2<br>)x014332 | -               |  |  |

| ,           | After Instruct<br>TOS<br>PC        | ion                                                                                       |                                                                                                                                                                                                                                                                                                  | )x014332<br>NEW      | 2               |  |  |

| PUSH                     | Push Top                                                                                                 | Push Top of Return Stack                                 |                                           |                                                 |  |  |  |

|--------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------|-------------------------------------------------|--|--|--|

| Syntax:                  | [label]                                                                                                  | [label] PUSH                                             |                                           |                                                 |  |  |  |

| Operands:                | None                                                                                                     |                                                          |                                           |                                                 |  |  |  |

| Operation:               | (PC + 2) –                                                                                               | → TOS                                                    |                                           |                                                 |  |  |  |

| Status Affected:         | None                                                                                                     |                                                          |                                           |                                                 |  |  |  |

| Encoding:                | 0000                                                                                                     | 0000                                                     | 0000                                      | 0101                                            |  |  |  |

| Description:             | The PC +<br>of the retu<br>TOS value<br>stack.<br>This instru<br>ing a softv<br>TOS and t<br>return stac | rn stack<br>is push<br>iction al<br>vare sta<br>then pus | k. The p<br>ned dov<br>lows in<br>ck by r | previous<br>wn on the<br>nplement-<br>nodifying |  |  |  |

| Words:                   | 1                                                                                                        |                                                          |                                           |                                                 |  |  |  |

| Cycles:                  | 1                                                                                                        |                                                          |                                           |                                                 |  |  |  |

| Q Cycle Activit          | y:                                                                                                       |                                                          |                                           |                                                 |  |  |  |

| Q1                       | Q2                                                                                                       | Q3                                                       | 3                                         | Q4                                              |  |  |  |

| Decode                   | Push<br>PC + 2 onto<br>return stack                                                                      | No<br>opera                                              |                                           | No<br>operation                                 |  |  |  |

| Example:                 | PUSH                                                                                                     |                                                          |                                           |                                                 |  |  |  |

| -                        | ruction                                                                                                  |                                                          |                                           |                                                 |  |  |  |

| Before Inst<br>TOS<br>PC |                                                                                                          |                                                          | x00345<br>x00012                          |                                                 |  |  |  |

| RET      | FIE                                                    | Return fro                                                                                                                | Return from Interrupt                                                                                                                                                                                                                                                                                                                                                                                       |                                             |  |  |  |  |  |

|----------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--|--|--|--|--|

| Synt     | ax:                                                    | [label]                                                                                                                   | [label] RETFIE [s]                                                                                                                                                                                                                                                                                                                                                                                          |                                             |  |  |  |  |  |

| Ope      | rands:                                                 | s ∈ [0,1]                                                                                                                 | s ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                   |                                             |  |  |  |  |  |

| Ope      | ration:                                                | $1 \rightarrow GIE/C$<br>if s = 1<br>(WS) $\rightarrow$ W<br>(STATUSS<br>(BSRS) $\rightarrow$                             | $\begin{array}{l} (\text{TOS}) \rightarrow \text{PC}, \\ 1 \rightarrow \text{GIE/GIEH or PEIE/GIEL}, \\ \text{if s = 1} \\ (\text{WS}) \rightarrow \text{W}, \\ (\text{STATUSS}) \rightarrow \text{Status}, \\ (\text{BSRS}) \rightarrow \text{BSR}, \\ \text{PCLATU, PCLATH are unchanged}. \end{array}$                                                                                                   |                                             |  |  |  |  |  |

| Statu    | us Affected:                                           | GIE/GIEH                                                                                                                  | , PEIE/GIEL.                                                                                                                                                                                                                                                                                                                                                                                                | 1                                           |  |  |  |  |  |

| Enco     | oding:                                                 | 0000                                                                                                                      | 0000 000                                                                                                                                                                                                                                                                                                                                                                                                    | 000s                                        |  |  |  |  |  |

| Desc     | cription:                                              | popped ar<br>loaded into<br>enabled by<br>or low prio<br>Enable bit<br>the shador<br>STATUSS<br>into their o<br>W, Status | Return from interrupt. Stack is<br>popped and Top-of-Stack (TOS) is<br>loaded into the PC. Interrupts are<br>enabled by setting either the high<br>or low priority Global Interrupt<br>Enable bit. If 's' = 1, the contents of<br>the shadow registers, WS,<br>STATUSS and BSRS, are loaded<br>into their corresponding registers,<br>W, Status and BSR. If 's' = 0, no<br>update of these registers occurs |                                             |  |  |  |  |  |

| Wor      | ds:                                                    | 1                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                           |                                             |  |  |  |  |  |

| Cycl     | es:                                                    | 2                                                                                                                         | 2                                                                                                                                                                                                                                                                                                                                                                                                           |                                             |  |  |  |  |  |

| QC       | cycle Activity:                                        |                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                             |                                             |  |  |  |  |  |

|          | Q1                                                     | Q2                                                                                                                        | Q3                                                                                                                                                                                                                                                                                                                                                                                                          | Q4                                          |  |  |  |  |  |

|          | Decode                                                 | No<br>operation                                                                                                           | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                             | Pop PC<br>from stack<br>Set GIEH or<br>GIEL |  |  |  |  |  |

|          | No                                                     | No                                                                                                                        | No                                                                                                                                                                                                                                                                                                                                                                                                          | No                                          |  |  |  |  |  |

|          | operation                                              | operation                                                                                                                 | operation                                                                                                                                                                                                                                                                                                                                                                                                   | operation                                   |  |  |  |  |  |

| Example: |                                                        | RETFIE 1                                                                                                                  | L                                                                                                                                                                                                                                                                                                                                                                                                           |                                             |  |  |  |  |  |

|          | After Interrup<br>PC<br>W<br>BSR<br>Status<br>GIE/GIEH | ot<br>H, PEIE/GIEL                                                                                                        | = TOS<br>= WS<br>= BSRS<br>= STATL<br>= 1                                                                                                                                                                                                                                                                                                                                                                   | ISS                                         |  |  |  |  |  |

| Syntax:            | [label]                                      | RETLW F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (       |                 |  |  |  |  |

|--------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------|--|--|--|--|

| Operands:          |                                              | $0 \le k \le 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |                 |  |  |  |  |

| •                  |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                 |  |  |  |  |

| Operation:         | $k \rightarrow W$ ,<br>(TOS) $\rightarrow F$ | or of the second s |         |                 |  |  |  |  |

|                    | PCLATU,                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | are und | hanged          |  |  |  |  |

| Status Affected:   | None                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                 |  |  |  |  |

| Encoding:          | 0000                                         | 1100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | kkk     | kkkk            |  |  |  |  |

|                    |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                 |  |  |  |  |

| Description:       | W is loade<br>The progra                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                 |  |  |  |  |

|                    | from the to                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                 |  |  |  |  |

|                    | address).                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                 |  |  |  |  |

|                    | (PCLATH)                                     | remains u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | unchar  | iged.           |  |  |  |  |

| Words:             | 1                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                 |  |  |  |  |

| Cycles:            | 2                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                 |  |  |  |  |

| Q Cycle Activity:  | :                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                 |  |  |  |  |

| Q1                 | Q2                                           | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         | Q4              |  |  |  |  |