Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 4KB (2K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 7x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1220t-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                                   | Pi                 | n Numb                 | er        | Din Duffer                |                                  |                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------|--------------------|------------------------|-----------|---------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                          | PDIP/<br>SOIC      | SSOP                   | QFN       | Pin<br>Type               | Buffer<br>Type                   | Description                                                                                                                                                                                       |

|                                                                                   | _                  |                        | _         |                           |                                  | PORTB is a bidirectional I/O port. PORTB can be softwa<br>programmed for internal weak pull-ups on all inputs.                                                                                    |

| RB0/AN4/INT0<br>RB0<br>AN4<br>INT0                                                | 8                  | 9                      | 9         | I/O<br>I<br>I             | TTL<br>Analog<br>ST              | Digital I/O.<br>Analog input 4.<br>External interrupt 0.                                                                                                                                          |

| RB1/AN5/TX/CK/INT1<br>RB1<br>AN5<br>TX<br>CK<br>INT1                              | 9                  | 10                     | 10        | I/O<br>I<br>0<br>I/O<br>I | TTL<br>Analog<br>—<br>ST<br>ST   | Digital I/O.<br>Analog input 5.<br>EUSART asynchronous transmit.<br>EUSART synchronous clock (see related RX/DT).<br>External interrupt 1.                                                        |

| RB2/P1B/INT2<br>RB2<br>P1B<br>INT2                                                | 17                 | 19                     | 23        | I/O<br>O<br>I             | TTL<br>—<br>ST                   | Digital I/O.<br>Enhanced CCP1/PWM output.<br>External interrupt 2.                                                                                                                                |

| RB3/CCP1/P1A<br>RB3<br>CCP1<br>P1A                                                | 18                 | 20                     | 24        | I/O<br>I/O<br>O           | TTL<br>ST                        | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM 1 output.<br>Enhanced CCP1/PWM output.                                                                                                       |

| RB4/AN6/RX/DT/KBI0<br>RB4<br>AN6<br>RX<br>DT<br>KBI0                              | 10                 | 11                     | 12        | I/O<br>I<br>I<br>I/O<br>I | TTL<br>Analog<br>ST<br>ST<br>TTL | Digital I/O.<br>Analog input 6.<br>EUSART asynchronous receive.<br>EUSART synchronous data (see related TX/CK).<br>Interrupt-on-change pin.                                                       |

| RB5/PGM/KBI1<br>RB5<br>PGM<br>KBI1                                                | 11                 | 12                     | 13        | I/O<br>I/O<br>I           | TTL<br>ST<br>TTL                 | Digital I/O.<br>Low-Voltage ICSP™ Programming enable pin.<br>Interrupt-on-change pin.                                                                                                             |

| RB6/PGC/T10S0/<br>T13CKI/P1C/KBI2<br>RB6<br>PGC<br>T10S0<br>T13CKI<br>P1C<br>KBI2 | 12                 | 13                     | 15        | I/O<br>I/O<br>I<br>O<br>I | TTL<br>ST<br>—<br>ST<br>—<br>TTL | Digital I/O.<br>In-Circuit Debugger and ICSP programming clock pin.<br>Timer1 oscillator output.<br>Timer1/Timer3 external clock output.<br>Enhanced CCP1/PWM output.<br>Interrupt-on-change pin. |

| RB7/PGD/T1OSI/<br>P1D/KBI3<br>RB7<br>PGD<br>T1OSI<br>P1D<br>KBI3                  | 13                 | 14                     | 16        | I/O<br>I/O<br>I<br>O<br>I | TTL<br>ST<br>CMOS<br>—<br>TTL    | Digital I/O.<br>In-Circuit Debugger and ICSP programming data pin.<br>Timer1 oscillator input.<br>Enhanced CCP1/PWM output.<br>Interrupt-on-change pin.                                           |

| Vss                                                                               | 5                  | 5, 6                   | 3, 5      | Р                         | —                                | Ground reference for logic and I/O pins.                                                                                                                                                          |

| Vdd                                                                               | 14                 | 15, 16                 | 17, 19    | Р                         |                                  | Positive supply for logic and I/O pins.                                                                                                                                                           |

| NC                                                                                | —                  | —                      | 18        | —                         | —                                | No connect.                                                                                                                                                                                       |

| ST = Sc                                                                           | hmitt Tri<br>Itput | atible inp<br>gger inp | ut with ( |                           | evels                            | CMOS = CMOS compatible input or output<br>I = Input<br>P = Power                                                                                                                                  |

O = Output OD = Open-drain (no P diode to VDD)

# 4.1 Power-on Reset (POR)

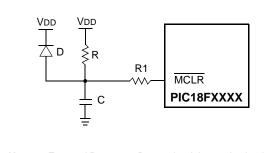

A Power-on Reset pulse is generated on-chip when VDD rise is detected. To take advantage of the POR circuitry, just tie the MCLR pin through a resistor (1k to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004). For a slow rise time, see Figure 4-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

FIGURE 4-2: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1:External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that the voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 \ge 1 \ k\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C, in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

# 4.2 Power-up Timer (PWRT)

The Power-up Timer (PWRT) of the PIC18F1220/1320 is an 11-bit counter, which uses the INTRC source as the clock input. This yields a count of  $2048 \times 32 \ \mu s = 65.6 \ ms$ . While the PWRT is counting, the device is held in Reset.

The power-up time delay will vary from chip-to-chip due to VDD, temperature and process variation. See DC parameter 33 for details.

The PWRT is enabled by clearing Configuration bit, PWRTEN.

# 4.3 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter 33). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP, HS and HSPLL modes and only on Power-on Reset, or on exit from most low-power modes.

## 4.4 PLL Lock Time-out

With the PLL enabled in its PLL mode, the time-out sequence following a Power-on Reset is slightly different from other oscillator modes. A portion of the Power-up Timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the Oscillator Start-up Time-out.

## 4.5 Brown-out Reset (BOR)

A Configuration bit, BOR, can disable (if clear/ programmed), or enable (if set) the Brown-out Reset circuitry. If VDD falls below VBOR (parameter D005) for greater than TBOR (parameter 35), the brown-out situation will reset the chip. A Reset may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR. If the Power-up Timer is enabled, it will be invoked after VDD rises above VBOR; it then will keep the chip in Reset for an additional time delay, TPWRT (parameter 33). If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay. Enabling BOR Reset does not automatically enable the PWRT.

# 4.6 Time-out Sequence

On power-up, the time-out sequence is as follows: First, after the POR pulse has cleared, PWRT time-out is invoked (if enabled). Then, the OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 4-3, Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, all time-outs will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 4-5). This is useful for testing purposes or to synchronize more than one PIC18FXXXX device operating in parallel.

Table 4-2 shows the Reset conditions for some Special Function Registers, while Table 4-3 shows the Reset conditions for all the registers.

## 5.14 RCON Register

The Reset Control (RCON) register contains flag bits that allow differentiation between the sources of a device Reset. These flags include the TO, PD, POR, BOR and RI bits. This register is readable and writable.

- Note 1: If the BOR Configuration bit is set (Brown-out Reset enabled), the BOR bit is '1' on a Power-on Reset. After a Brown-out Reset has occurred, the BOR bit will be cleared and must be set by firmware to indicate the occurrence of the next Brown-out Reset.

- 2: It is recommended that the POR bit be set after a Power-on Reset has been detected, so that subsequent Power-on Resets may be detected.

### REGISTER 5-3: RCON: RESET CONTROL REGISTER

| R/W-0                                                                                                                                             | U-0                                                                                                        | U-0               | R/W-1          | R-1               | R-1              | R/W-0            | R/W-0       |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------|----------------|-------------------|------------------|------------------|-------------|--|--|--|

| IPEN                                                                                                                                              | _                                                                                                          | _                 | RI             | TO                | PD               | POR              | BOR         |  |  |  |

| bit 7                                                                                                                                             |                                                                                                            |                   |                |                   |                  |                  | bit 0       |  |  |  |

|                                                                                                                                                   |                                                                                                            |                   |                |                   |                  |                  |             |  |  |  |

| Legend:                                                                                                                                           |                                                                                                            |                   |                |                   |                  |                  |             |  |  |  |

| R = Readable                                                                                                                                      | bit                                                                                                        | W = Writable      | bit            | U = Unimpler      | mented bit, read | l as '0'         |             |  |  |  |

| u = Bit is unch                                                                                                                                   | anged                                                                                                      | x = Bit is unki   | nown           | -n/n = Value      | at POR and BO    | R/Value at all o | ther Resets |  |  |  |

| '1' = Bit is set                                                                                                                                  |                                                                                                            | '0' = Bit is cle  | ared           | q = Value de      | pends on condit  | ion              |             |  |  |  |

|                                                                                                                                                   |                                                                                                            |                   |                |                   |                  |                  |             |  |  |  |

| bit 7                                                                                                                                             |                                                                                                            | pt Priority Enat  |                |                   |                  |                  |             |  |  |  |

|                                                                                                                                                   | 1 = Enable priority levels on interrupts                                                                   |                   |                |                   |                  |                  |             |  |  |  |

| <ul> <li>0 = Disable priority levels on interrupts (PIC16CXXX Compatibility mode)</li> <li>bit 6-5</li> <li>Unimplemented: Read as '0'</li> </ul> |                                                                                                            |                   |                |                   |                  |                  |             |  |  |  |

| bit 4                                                                                                                                             | Unimplemented: Read as '0'                                                                                 |                   |                |                   |                  |                  |             |  |  |  |

| DIL 4                                                                                                                                             | <b>RI:</b> RESET Instruction Flag bit<br>1 = The RESET instruction was not executed (set by firmware only) |                   |                |                   |                  |                  |             |  |  |  |

|                                                                                                                                                   |                                                                                                            |                   |                | causing a devi    |                  |                  |             |  |  |  |

|                                                                                                                                                   | (must be                                                                                                   | set in software   | e after a Brow | n-out Reset oc    | curs)            |                  |             |  |  |  |

| bit 3                                                                                                                                             | TO: Watchdo                                                                                                | g Time-out Fla    | g bit          |                   |                  |                  |             |  |  |  |

|                                                                                                                                                   |                                                                                                            | ower-up, CLRW     |                | or SLEEP instr    | uction           |                  |             |  |  |  |

| bit 2                                                                                                                                             |                                                                                                            | own Detection     |                |                   |                  |                  |             |  |  |  |

| DIL Z                                                                                                                                             |                                                                                                            | ower-up or by t   | U              | struction         |                  |                  |             |  |  |  |

|                                                                                                                                                   |                                                                                                            | by execution of   |                |                   |                  |                  |             |  |  |  |

| bit 1                                                                                                                                             | POR: Power-                                                                                                | on Reset Statu    | s bit          |                   |                  |                  |             |  |  |  |

|                                                                                                                                                   |                                                                                                            |                   |                | (set by firmwar   |                  |                  |             |  |  |  |

|                                                                                                                                                   | 0 = A Power                                                                                                | -on Reset occu    | rred (must be  | e set in software | e after a Power- | on Reset occur   | s)          |  |  |  |

| bit 0                                                                                                                                             |                                                                                                            | out Reset Stat    |                |                   |                  |                  |             |  |  |  |

|                                                                                                                                                   |                                                                                                            |                   |                | (set by firmwar   |                  | aut Daaat        |             |  |  |  |

|                                                                                                                                                   | 0 = A Brown                                                                                                | -out Reset occ    | urred (must b  | e set in softwar  | e after a Brown  | -out Reset occi  | urs)        |  |  |  |

| Note 1: For                                                                                                                                       | Borrow, the po                                                                                             | larity is reverse | ed. A subtract | tion is executed  | I by adding the  | two's compleme   | ent of the  |  |  |  |

**Note 1:** For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register.

| R/W-x           | R/W-x                                                                                                                          | U-0                               | R/W-0                  | R/W-x                            | R/W-0            | R/S-0             | R/S-0          |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------|----------------------------------|------------------|-------------------|----------------|--|--|--|

| EEPGD           | CFGS                                                                                                                           |                                   | FREE                   | WRERR <sup>(1)</sup>             | WREN             | WR                | RD             |  |  |  |

| bit 7           | •                                                                                                                              |                                   |                        |                                  |                  |                   | bit C          |  |  |  |

|                 |                                                                                                                                |                                   |                        |                                  |                  |                   |                |  |  |  |

| Legend:         |                                                                                                                                |                                   |                        |                                  |                  |                   |                |  |  |  |

| R = Readabl     | e bit                                                                                                                          | W = Writable                      | bit                    | U = Unimplem                     | ented bit, read  | as '0'            |                |  |  |  |

| S = Bit can o   | nly be set                                                                                                                     | x = Bit is unk                    | nown                   | -n/n = Value a                   | t POR and BO     | R/Value at all o  | ther Resets    |  |  |  |

| '1' = Bit is se | t                                                                                                                              | '0' = Bit is cle                  | eared                  | HC = Bit is cle                  | ared by hardw    | are               |                |  |  |  |

| bit 7           | EEPGD: Fla                                                                                                                     | ish Program or                    | Data EEPRO             | M Memory Selec                   | ct bit           |                   |                |  |  |  |

|                 |                                                                                                                                | program Flash                     |                        | ,                                |                  |                   |                |  |  |  |

|                 |                                                                                                                                | data EEPROM                       |                        |                                  |                  |                   |                |  |  |  |

| bit 6           | CFGS: Flas                                                                                                                     | h Program/Data                    | a EEPROM or            | Configuration S                  | elect bit        |                   |                |  |  |  |

|                 |                                                                                                                                |                                   |                        | Device ID Reg                    | sters            |                   |                |  |  |  |

|                 | 0 = Accesses Flash Program or data EEPROM Memory                                                                               |                                   |                        |                                  |                  |                   |                |  |  |  |

| bit 5           | Unimplemented: Read as '0'                                                                                                     |                                   |                        |                                  |                  |                   |                |  |  |  |

| bit 4           | FREE: Flash Row Erase Enable bit <ol> <li>= Erase the program memory row addressed by TBLPTR on the next WR command</li> </ol> |                                   |                        |                                  |                  |                   |                |  |  |  |

|                 |                                                                                                                                |                                   |                        | ressed by TBLP<br>ation – TBLPTR |                  |                   |                |  |  |  |

|                 | 0 = Perform                                                                                                                    | • •                               |                        |                                  |                  | iou)              |                |  |  |  |

| bit 3           | WRERR: EE                                                                                                                      | EPROM Error F                     | lag bit <sup>(1)</sup> |                                  |                  |                   |                |  |  |  |

|                 |                                                                                                                                |                                   |                        | rminated (any R                  | eset during sel  | f-timed program   | nming)         |  |  |  |

|                 |                                                                                                                                | te operation cor                  | -                      | ally                             |                  |                   |                |  |  |  |

| bit 2           |                                                                                                                                | gram/Erase Ena                    |                        |                                  |                  |                   |                |  |  |  |

|                 |                                                                                                                                | program/erase                     | ,                      |                                  |                  |                   |                |  |  |  |

| <b>L</b> :L 4   |                                                                                                                                |                                   | rasing or prog         | ram Flash and o                  |                  |                   |                |  |  |  |

| bit 1           | WR: Write C                                                                                                                    |                                   | Maraaa/writa           | cycle or a progra                | mmomory          | aa ayala ar yyrit |                |  |  |  |

|                 |                                                                                                                                |                                   |                        | bit is cleared by                |                  |                   |                |  |  |  |

|                 |                                                                                                                                | only be set (not                  |                        |                                  |                  | oo .o oop         |                |  |  |  |

|                 | 0 = Write cy                                                                                                                   | cle completed                     |                        |                                  |                  |                   |                |  |  |  |

| bit 0           | RD: Read C                                                                                                                     | ontrol bit                        |                        |                                  |                  |                   |                |  |  |  |

|                 |                                                                                                                                | a memory read                     |                        |                                  |                  |                   |                |  |  |  |

|                 |                                                                                                                                | акеѕ one cycle<br>e. RD bit canno |                        | d in hardware.                   | The RD bit car   | n only be set (r  | not cleared) i |  |  |  |

|                 | 0 = Read co                                                                                                                    |                                   |                        | OD                               |                  |                   |                |  |  |  |

| Note 1: W       | hen a WRERR                                                                                                                    | occurs, the FF                    | PGD and CF             | GS bits are not c                | leared. This all | ows               |                |  |  |  |

|                 |                                                                                                                                |                                   |                        |                                  |                  |                   |                |  |  |  |

# REGISTER 7-1: EECON1: EEPROM CONTROL 1 REGISTER

| R/W-0/0          | R/W-0/0                                                                                    | R/W-0/0             | R/W-0/0         | R/W-0/0          | R/W-0/0          | R-1/1            | R/W-0/0      |  |  |

|------------------|--------------------------------------------------------------------------------------------|---------------------|-----------------|------------------|------------------|------------------|--------------|--|--|

| CSRC             | TX9                                                                                        | TXEN <sup>(1)</sup> | SYNC            | SENDB            | BRGH             | TRMT             | TX9D         |  |  |

| bit 7            |                                                                                            |                     |                 |                  |                  |                  | bit (        |  |  |

|                  |                                                                                            |                     |                 |                  |                  |                  |              |  |  |

| Legend:          |                                                                                            |                     |                 |                  |                  |                  |              |  |  |

| R = Readable     | bit                                                                                        | W = Writable        | bit             | U = Unimplen     | nented bit, read | as '0'           |              |  |  |

| u = Bit is unch  | anged                                                                                      | x = Bit is unkr     | nown            | -n/n = Value a   | at POR and BOI   | R/Value at all o | other Resets |  |  |

| '1' = Bit is set |                                                                                            | '0' = Bit is cle    | ared            |                  |                  |                  |              |  |  |

|                  |                                                                                            |                     |                 |                  |                  |                  |              |  |  |

| bit 7            |                                                                                            | k Source Select     | bit             |                  |                  |                  |              |  |  |

|                  | Asynchronou<br>Don't care.                                                                 | <u>us mode:</u>     |                 |                  |                  |                  |              |  |  |

|                  | Synchronous                                                                                | <u>s mode:</u>      |                 |                  |                  |                  |              |  |  |

|                  |                                                                                            | mode (clock ger     |                 |                  |                  |                  |              |  |  |

| 1.10             |                                                                                            | ode (clock from     |                 | ce)              |                  |                  |              |  |  |

| bit 6            |                                                                                            | ansmit Enable I     |                 |                  |                  |                  |              |  |  |

|                  | <ul> <li>1 = Selects 9-bit transmission</li> <li>0 = Selects 8-bit transmission</li> </ul> |                     |                 |                  |                  |                  |              |  |  |

| bit 5            | TXEN: Transmit Enable bit <sup>(1)</sup>                                                   |                     |                 |                  |                  |                  |              |  |  |

|                  | 1 = Transmi                                                                                | t enabled           |                 |                  |                  |                  |              |  |  |

|                  | 0 = Transmi                                                                                | it disabled         |                 |                  |                  |                  |              |  |  |

| bit 4            | SYNC: EUS                                                                                  | ART Mode Sele       | ect bit         |                  |                  |                  |              |  |  |

|                  | 1 = Synchro                                                                                |                     |                 |                  |                  |                  |              |  |  |

|                  | •                                                                                          | onous mode          |                 |                  |                  |                  |              |  |  |

| bit 3            |                                                                                            | nd Break Chara      | cter bit        |                  |                  |                  |              |  |  |

|                  | Asynchronou<br>1 = Send Sv                                                                 | /nc Break on ne     | ext transmissio | on (cleared by h | nardware upon o  | completion)      |              |  |  |

|                  |                                                                                            | eak transmissio     |                 | (1 1 1 1 1 1 )   |                  | , ,              |              |  |  |

|                  | Synchronous                                                                                | <u>s mode:</u>      |                 |                  |                  |                  |              |  |  |

|                  | Don't care.                                                                                |                     |                 |                  |                  |                  |              |  |  |

| bit 2            |                                                                                            | Baud Rate Sel       | ect bit         |                  |                  |                  |              |  |  |

|                  | Asynchronou<br>1 = High spe                                                                |                     |                 |                  |                  |                  |              |  |  |

|                  | 0 = Low spectrum                                                                           |                     |                 |                  |                  |                  |              |  |  |

|                  | Synchronous                                                                                | <u>s mode:</u>      |                 |                  |                  |                  |              |  |  |

|                  | Unused in th                                                                               |                     |                 |                  |                  |                  |              |  |  |

| bit 1            |                                                                                            | smit Shift Regist   | ter Status bit  |                  |                  |                  |              |  |  |

|                  | 1 = TSR Idle                                                                               |                     |                 |                  |                  |                  |              |  |  |

|                  | 0 = TSR bus                                                                                | -                   |                 |                  |                  |                  |              |  |  |

| bit ()           | <b>TX9D:</b> 9th bit of Transmit Data                                                      |                     |                 |                  |                  |                  |              |  |  |

| bit 0            |                                                                                            | ess/data bit or a   |                 |                  |                  |                  |              |  |  |

# REGISTER 16-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

| U-0             | R-1                                                                                                                       | U-0                                                                              | R/W-0/0       | R/W-0/0      | U-0              | R/W-0/0          | R/W-0/0        |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------|--------------|------------------|------------------|----------------|--|--|

| _               | RCIDL                                                                                                                     | —                                                                                | SCKP          | BRG16        | _                | WUE              | ABDEN          |  |  |

| bit 7           |                                                                                                                           |                                                                                  |               |              |                  |                  | bit 0          |  |  |

|                 |                                                                                                                           |                                                                                  |               |              |                  |                  |                |  |  |

| Legend:         |                                                                                                                           |                                                                                  |               |              |                  |                  |                |  |  |

| R = Readab      |                                                                                                                           | W = Writable                                                                     |               | •            | mented bit, read |                  |                |  |  |

| u = Bit is und  | -                                                                                                                         | x = Bit is unkt                                                                  |               | -n/n = value | at POR and BC    | R/Value at all o | ther Resets    |  |  |

| '1' = Bit is se | et                                                                                                                        | '0' = Bit is cle                                                                 | ared          |              |                  |                  |                |  |  |

| bit 7           | Unimplemen                                                                                                                | ted: Read as '                                                                   | 0'            |              |                  |                  |                |  |  |

| bit 6           | -                                                                                                                         | ive Operation                                                                    |               |              |                  |                  |                |  |  |

|                 | 1 = Receiver<br>0 = Receiver                                                                                              |                                                                                  |               |              |                  |                  |                |  |  |

| bit 5           | Unimplemen                                                                                                                | ted: Read as '                                                                   | 0'            |              |                  |                  |                |  |  |

| bit 4           | SCKP: Synchronous Clock Polarity Select bit                                                                               |                                                                                  |               |              |                  |                  |                |  |  |

|                 | Asynchronous mode:<br>Unused in this mode.                                                                                |                                                                                  |               |              |                  |                  |                |  |  |

|                 | <u>Synchronous mode:</u><br>1 = Idle state for clock (CK) is a high level<br>0 = Idle state for clock (CK) is a low level |                                                                                  |               |              |                  |                  |                |  |  |

| bit 3           | <b>BRG16:</b> 16-b                                                                                                        | it Baud Rate R                                                                   | egister Enabl | e bit        |                  |                  |                |  |  |

|                 |                                                                                                                           |                                                                                  |               | H and SPBRC  |                  | RGH value igno   | ored           |  |  |

| bit 2           | Unimplemen                                                                                                                | ted: Read as '                                                                   | 0'            |              |                  |                  |                |  |  |

| bit 1           | WUE: Wake-                                                                                                                | up Enable bit                                                                    |               |              |                  |                  |                |  |  |

|                 | hardware                                                                                                                  | will continue t<br>on following r<br>ot monitored o<br><u>mode:</u>              | ising edge    |              | rupt generated   | on falling edge; | bit cleared in |  |  |

| bit 0           |                                                                                                                           | -Baud Detect                                                                     | Enable bit    |              |                  |                  |                |  |  |

|                 | Asynchronous<br>1 = Enable b<br>cleared ii                                                                                | <u>s mode:</u><br>aud rate meas<br>n hardware up<br>e measuremen<br><u>mode:</u> | urement on th |              | er – requires re | eception of a Sy | nc byte (55h); |  |  |

# REGISTER 16-3: BAUDCTL: BAUD RATE CONTROL REGISTER

To set up an Asynchronous Transmission:

- Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH (see Section 16.2 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, set enable bit TXIE.

- If 9-bit transmission is desired, set transmit bit TX9. Can be used as address/data bit.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

### TABLE 16-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Name    | Bit 7       | Bit 6          | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------|----------------|-------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| INTCON  | GIE/GIEH    | PEIE/GIEL      | TMR0IE      | INT0IE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1    | _           | ADIF           | RCIF        | TXIF   | —     | CCP1IF | TMR2IF | TMR1IF | -000 -000            | -000 -000                       |

| PIE1    | —           | ADIE           | RCIE        | TXIE   | —     | CCP1IE | TMR2IE | TMR1IE | -000 -000            | -000 -000                       |

| IPR1    | —           | ADIP           | RCIP        | TXIP   | —     | CCP1IP | TMR2IP | TMR1IP | -111 -111            | -111 -111                       |

| RCSTA   | SPEN        | RX9            | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| RCREG   | EUSART Re   | eceive Registe | er          |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA   | CSRC        | TX9            | TXEN        | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |

| BAUDCTL | —           | RCIDL          | —           | SCKP   | BRG16 | —      | WUE    | ABDEN  | -1-1 0-00            | -1-1 0-00                       |

| SPBRGH  | Baud Rate C | Generator Reg  | ister High  | Byte   |       |        |        |        | 0000 0000            | 0000 0000                       |

| SPBRG   | Baud Rate C | Generator Reg  | ister Low E | Byte   |       |        |        |        | 0000 0000            | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

# 16.3.5 BREAK CHARACTER SEQUENCE

The Enhanced USART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The Frame Break character is sent whenever the SENDB and TXEN bits (TXSTA<3> and TXSTA<5>) are set while the Transmit Shift register is loaded with data. Note that the value of data written to TXREG will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

Note that the data value written to the TXREG for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 16-9 for the timing of the Break character sequence.

### 16.3.5.1 Transmitting A Break Signal

The Enhanced USART module has the capability of sending the Break signal that is required by the LIN bus standard. The Break signal consists of a Start bit, followed by twelve '0' bits and a Stop bit. The Break signal is sent whenever the SENDB (TXSTA<3>) and TXEN (TXSTA<5>) bits are set and TXREG is loaded with data. The data written to TXREG will be ignored and all '0's will be transmitted.

SENDB is automatically cleared by hardware when the Break signal has been sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission.

To send a Break Signal:

- Configure the EUSART for asynchronous transmissions (steps 1-5). Initialize the SPBRG register for the appropriate baud rate. If a high-speed baud rate is desired, set bit BRGH (see Section 16.2 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set transmit bit TX9. Can be used as address/data bit.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. Set the SENDB bit.

- 7. Load a byte into TXREG. This triggers sending a Break signal. The Break signal is complete when TRMT is set. SENDB will also be cleared.

See Figure 16-9 for the timing of the Break signal sequence.

### 16.3.6 RECEIVING A BREAK CHARACTER

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 the typical speed. This allows for the Stop bit transition to be at the correct sampling location (12 bits for Break versus Start bit and eight data bits for typical data).

The second method uses the auto-wake-up feature described in **Section 16.3.4 "Auto-Wake-up on Sync Break Character"**. By enabling this feature, the EUSART will sample the next two transitions on RX/DT, cause an RCIF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABD bit before placing the EUSART in its Sleep mode.

### 16.3.6.1 Transmitting a Break Sync

The following sequence will send a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to set up the Break character.

- 3. Load the TXREG with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG to load the Sync character into the transmit FIFO buffer.

- After the Break has been sent, the SENDB bit is reset by hardware. The Sync character now transmits in the preconfigured mode. When the TXREG becomes empty, as indicated by the TXIF, the next data byte can be written to TXREG.

### 16.4.2 EUSART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either the Single Receive Enable bit, SREN (RCSTA<5>), or the Continuous Receive Enable bit, CREN (RCSTA<4>). Data is sampled on the RB4/AN6/RX/DT/KBI0 pin on the falling edge of the clock.

If enable bit, SREN, is set, only a single word is received. If enable bit, CREN, is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, set enable bit RCIE.

- 5. If 9-bit reception is desired, set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- 7. Interrupt flag bit, RCIF, will be set when reception is complete and an interrupt will be generated if the enable bit, RCIE, was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| RB4/AN6/RX/<br>DT/KBI0 pin               |            | <u>.</u>           | bit (       | $\overline{}$ | bit 1     | $\sim$ | bit 2                   | $\sim$  | bit 3            | $\sim$ | bit 4            | $\sim$ | bit 5            | $\sim$ | bit 6       | $\sim$ | bit 7       |                  |    |

|------------------------------------------|------------|--------------------|-------------|---------------|-----------|--------|-------------------------|---------|------------------|--------|------------------|--------|------------------|--------|-------------|--------|-------------|------------------|----|

| RB1/AN5/TX/<br>CK/INT1 pin<br>(SCKP = 0) |            | · /                | ц.          |               |           |        |                         | _/\<br> |                  |        |                  |        |                  |        | <u> </u>    |        | ;<br>;<br>; | 1<br>1<br>1<br>1 |    |

| RB1/AN5/TX/<br>CK/INT1 pin<br>(SCKP = 1) |            | 1<br><u>1</u><br>1 | ı<br>Ļ.r    |               |           |        |                         |         |                  |        |                  |        |                  |        | ;<br>       |        |             | 1<br>1<br>1      |    |

| Write to<br>bit SREN                     |            | ļ                  | 1<br>1<br>1 |               | 1<br>     |        | 1<br><u>1</u><br>1<br>1 |         | 1<br>1<br>1      |        | 1<br>1<br>1<br>1 |        | 1<br>1<br>1      |        | ·<br>·<br>· |        |             |                  |    |

| SREN bit                                 |            |                    | <br>        |               |           |        |                         |         | L                |        | ,<br>,<br>,      |        |                  |        |             |        | <u>:</u>    | i                |    |

| CREN bit                                 | '0'        |                    | 1<br>1      |               |           |        | ,<br>,                  |         | I                |        |                  |        |                  |        |             |        |             |                  | "( |

| RCIF bit<br>(Interrupt)                  | . <u> </u> | 1<br>1<br>1        | 1<br>1<br>1 |               | <br> <br> |        | 1<br>1<br>1<br>1        |         | 1<br>1<br>1<br>1 |        | 1<br>1<br>1<br>1 |        | 1<br>1<br>1<br>1 |        | •<br>•<br>• |        | •<br>•<br>• | ;                |    |

| Read<br>RXREG                            |            | 1<br>1             | י<br>י      |               |           |        | •<br>•                  |         | •                |        |                  |        |                  |        | :           |        |             | :                |    |

### FIGURE 16-12: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

### 19.5.2 DATA EEPROM CODE PROTECTION

The entire data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of data EEPROM. WRTD inhibits external writes to data EEPROM. The CPU can continue to read and write data EEPROM, regardless of the protection bit settings.

### 19.5.3 CONFIGURATION REGISTER PROTECTION

The Configuration registers can be write-protected. The WRTC bit controls protection of the Configuration registers. In normal execution mode, the WRTC bit is readable only. WRTC can only be written via ICSP or an external programmer.

# 19.6 ID Locations

Eight memory locations (20000h-200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are both readable and writable during normal execution through the TBLRD and TBLWT instructions, or during program/verify. The ID locations can be read when the device is code-protected.

# 19.7 In-Circuit Serial Programming

PIC18F1220/1320 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed (see Table 19-4).

| Note: | The Timer1 oscillator shares the T1OSI<br>and T1OSO pins with the PGD and PGC<br>pins used for programming and<br>debugging.                                                                                                                                                                             |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | When using the Timer1 oscillator, In-Circuit<br>Serial Programming (ICSP) may not<br>function correctly (high voltage or low<br>voltage), or the In-Circuit Debugger (ICD)<br>may not communicate with the controller.<br>As a result of using either ICSP or ICD, the<br>Timer1 crystal may be damaged. |

|       | If ICSP or ICD operations are required,<br>the crystal should be disconnected from<br>the circuit (disconnect either lead), or<br>installed after programming. The oscillator<br>loading capacitors may remain in-circuit<br>during ICSP or ICD operation.                                               |

### TABLE 19-4: ICSP/ICD CONNECTIONS

| Signal | Pin                               | Notes                                     |

|--------|-----------------------------------|-------------------------------------------|

| PGD    | RB7/PGD/T1OSI/<br>P1D/KBI3        | Shared with T1OSC – protect crystal       |

| PGC    | RB6/PGC/T1OSO/<br>T13CKI/P1C/KBI2 | Shared with T1OSC – protect<br>crystal    |

| MCLR   | MCLR/Vpp/RA5                      |                                           |

| Vdd    | Vdd                               |                                           |

| Vss    | Vss                               |                                           |

| PGM    | RB5/PGM/KBI1                      | Optional – pull RB5 low is<br>LVP enabled |

# 19.8 In-Circuit Debugger

When the DEBUG bit in Configuration register, CONFIG4L, is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some resources are not available for general use. Table 19-5 shows which resources are required by the background debugger.

### TABLE 19-5: DEBUGGER RESOURCES

| I/O pins:       | RB6, RB7  |

|-----------------|-----------|

| Stack:          | 2 levels  |

| Program Memory: | 512 bytes |

| Data Memory:    | 10 bytes  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, Vss, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip, or one of the third party development tool companies (see the note following **Section 19.7 "In-Circuit Serial Programming"** for more information).

# PIC18F1220/1320

#### 20.2 **Instruction Set**

W = 0x25

| ADD                | DLW             | ADD liter           | al to W                                                                             |     |    |          |  |  |

|--------------------|-----------------|---------------------|-------------------------------------------------------------------------------------|-----|----|----------|--|--|

| Synt               | tax:            | [label] A           | DDLW                                                                                | k   |    |          |  |  |

| Ope                | rands:          | $0 \le k \le 25$    | 5                                                                                   |     |    |          |  |  |

| Ope                | ration:         | (W) + k →           | • W                                                                                 |     |    |          |  |  |

| State              | us Affected:    | N, OV, C,           | DC, Z                                                                               |     |    |          |  |  |

| Enc                | oding:          | 0000                | 1111                                                                                | kkk | k  | kkkk     |  |  |

| Des                | cription:       | 8-bit litera        | The contents of W are added to the 8-bit literal 'k' and the result is placed in W. |     |    |          |  |  |

| Wor                | ds:             | 1                   | 1                                                                                   |     |    |          |  |  |

| Cycl               | es:             | 1                   | 1                                                                                   |     |    |          |  |  |

| QC                 | Cycle Activity: |                     |                                                                                     |     |    |          |  |  |

|                    | Q1              | Q2                  | Q3                                                                                  |     |    | Q4       |  |  |

|                    | Decode          | Read<br>literal 'k' | Proce<br>Dat                                                                        |     | Wi | ite to W |  |  |

| <u>Exa</u>         | mple:           | ADDLW (             | 0x15                                                                                |     |    |          |  |  |

| Before Instruction |                 |                     |                                                                                     |     |    |          |  |  |

|                    | W =             | 0x10                |                                                                                     |     |    |          |  |  |

| After Instruction  |                 |                     |                                                                                     |     |    |          |  |  |

| Cycles:         | 1  |

|-----------------|----|

| Q Cycle Activit | y: |

| Q1              |    |

| Decode          |    |

|                 | re |

|                 |    |

| Example:        | A  |

| Defere last     |    |

| ADDWF             | ADD W to                                                                            | o f                                                |                                          |                                 |  |

|-------------------|-------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------|---------------------------------|--|

| Syntax:           | [ label ] Al                                                                        | DDWF                                               | f [,d [,a                                | l]]                             |  |

| Operands:         | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                               |                                                    |                                          |                                 |  |

| Operation:        | (W) + (f) -                                                                         | → dest                                             |                                          |                                 |  |

| Status Affected:  | N, OV, C,                                                                           | DC, Z                                              |                                          |                                 |  |

| Encoding:         | 0010                                                                                | 01da                                               | ffff                                     | ffff                            |  |

| Description:      | Add W to<br>result is st<br>result is st<br>(default).<br>Bank will I<br>the BSR is | tored in N<br>tored ba<br>If 'a' is '0<br>be selec | W. If 'd' is<br>ck in regi<br>)', the Ac | s '1', the<br>ister 'f'<br>cess |  |

| Words:            | 1                                                                                   |                                                    |                                          |                                 |  |

| Cycles:           | 1                                                                                   |                                                    |                                          |                                 |  |

| Q Cycle Activity: |                                                                                     |                                                    |                                          |                                 |  |

| Q1                | Q2                                                                                  | Q3                                                 |                                          | Q4                              |  |

| Decode            | Read<br>register 'f'                                                                | Proce<br>Data                                      |                                          | Vrite to<br>stination           |  |

| Example:          | ADDWF                                                                               | REG, N                                             | N                                        |                                 |  |

| Before Instru     | ction                                                                               |                                                    |                                          |                                 |  |

| W                 | = 0x17                                                                              |                                                    |                                          |                                 |  |

| W            | =     | 0x17 |

|--------------|-------|------|

| REG          | =     | 0xC2 |

| After Instru | ction |      |

| W   | = | 0xD9 |

|-----|---|------|

| REG | = | 0xC2 |

# PIC18F1220/1320

| CPFSGT Compare f with W, skip if t                                              |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |                 |  |  |  |  |

|---------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|--|--|--|--|