Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 7x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1320-e-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                                   | Pin Number         |                        |           |                           | D                                |                                                                                                                                                                                                   |  |  |

|-----------------------------------------------------------------------------------|--------------------|------------------------|-----------|---------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                                                          | PDIP/<br>SOIC      | SSOP QFN               |           | Pin<br>Type               | Buffer<br>Type                   | Description                                                                                                                                                                                       |  |  |

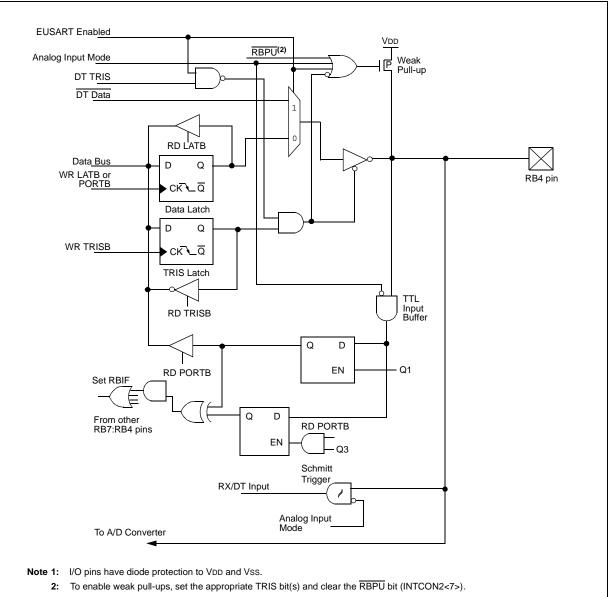

|                                                                                   | _                  |                        | _         |                           |                                  | PORTB is a bidirectional I/O port. PORTB can be softwa<br>programmed for internal weak pull-ups on all inputs.                                                                                    |  |  |

| RB0/AN4/INT0<br>RB0<br>AN4<br>INT0                                                | 8                  | 9                      | 9         | I/O<br>I<br>I             | TTL<br>Analog<br>ST              | Digital I/O.<br>Analog input 4.<br>External interrupt 0.                                                                                                                                          |  |  |

| RB1/AN5/TX/CK/INT1<br>RB1<br>AN5<br>TX<br>CK<br>INT1                              | 9                  | 10                     | 10        | I/O<br>I<br>0<br>I/O<br>I | TTL<br>Analog<br>—<br>ST<br>ST   | Digital I/O.<br>Analog input 5.<br>EUSART asynchronous transmit.<br>EUSART synchronous clock (see related RX/DT).<br>External interrupt 1.                                                        |  |  |

| RB2/P1B/INT2<br>RB2<br>P1B<br>INT2                                                | 17                 | 19                     | 23        | I/O<br>O<br>I             | TTL<br>—<br>ST                   | Digital I/O.<br>Enhanced CCP1/PWM output.<br>External interrupt 2.                                                                                                                                |  |  |

| RB3/CCP1/P1A<br>RB3<br>CCP1<br>P1A                                                | 18                 | 20                     | 24        | I/O<br>I/O<br>O           | TTL<br>ST                        | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM 1 output.<br>Enhanced CCP1/PWM output.                                                                                                       |  |  |

| RB4/AN6/RX/DT/KBI0<br>RB4<br>AN6<br>RX<br>DT<br>KBI0                              | 10                 | 11                     | 12        | I/O<br>I<br>I<br>I/O<br>I | TTL<br>Analog<br>ST<br>ST<br>TTL | Digital I/O.<br>Analog input 6.<br>EUSART asynchronous receive.<br>EUSART synchronous data (see related TX/CK).<br>Interrupt-on-change pin.                                                       |  |  |

| RB5/PGM/KBI1<br>RB5<br>PGM<br>KBI1                                                | 11                 | 12                     | 13        | I/O<br>I/O<br>I           | TTL<br>ST<br>TTL                 | Digital I/O.<br>Low-Voltage ICSP™ Programming enable pin.<br>Interrupt-on-change pin.                                                                                                             |  |  |

| RB6/PGC/T10S0/<br>T13CKI/P1C/KBI2<br>RB6<br>PGC<br>T10S0<br>T13CKI<br>P1C<br>KBI2 | 12                 | 13                     | 15        | I/O<br>I/O<br>I<br>O<br>I | TTL<br>ST<br>—<br>ST<br>—<br>TTL | Digital I/O.<br>In-Circuit Debugger and ICSP programming clock pin.<br>Timer1 oscillator output.<br>Timer1/Timer3 external clock output.<br>Enhanced CCP1/PWM output.<br>Interrupt-on-change pin. |  |  |

| RB7/PGD/T1OSI/<br>P1D/KBI3<br>RB7<br>PGD<br>T1OSI<br>P1D<br>KBI3                  | 13                 | 14                     | 16        | I/O<br>I/O<br>I<br>O<br>I | TTL<br>ST<br>CMOS<br>—<br>TTL    | Digital I/O.<br>In-Circuit Debugger and ICSP programming data pin.<br>Timer1 oscillator input.<br>Enhanced CCP1/PWM output.<br>Interrupt-on-change pin.                                           |  |  |

| Vss                                                                               | 5                  | 5, 6                   | 3, 5      | Ρ                         | —                                | Ground reference for logic and I/O pins.                                                                                                                                                          |  |  |

| Vdd                                                                               | 14                 | 15, 16                 | 17, 19    | Р                         |                                  | Positive supply for logic and I/O pins.                                                                                                                                                           |  |  |

| NC                                                                                | —                  | —                      | 18        | —                         | —                                | No connect.                                                                                                                                                                                       |  |  |

| ST = Sc                                                                           | hmitt Tri<br>Itput | atible inp<br>gger inp | ut with ( |                           | evels                            | CMOS = CMOS compatible input or output<br>I = Input<br>P = Power                                                                                                                                  |  |  |

O = Output OD = Open-drain (no P diode to VDD)

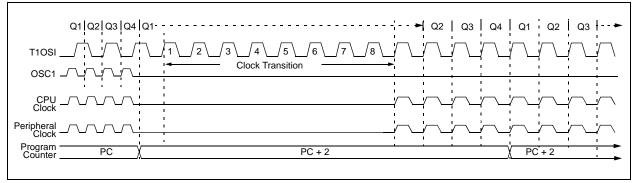

### 2.7.2 OSCILLATOR TRANSITIONS

The PIC18F1220/1320 devices contain circuitry to prevent clocking "glitches" when switching between clock sources. A short pause in the system clock occurs during the clock switch. The length of this pause is between eight and nine clock periods of the new clock source. This ensures that the new clock source is stable and that its pulse width will not be less than the shortest pulse width of the two clock sources.

Clock transitions are discussed in greater detail in **Section 3.1.2 "Entering Power Managed Modes"**.

## 2.8 Effects of Power Managed Modes on the Various Clock Sources

When the device executes a SLEEP instruction, the system is switched to one of the power managed modes, depending on the state of the IDLEN and SCS1:SCS0 bits of the OSCCON register. See **Section 3.0 "Power Managed Modes"** for details.

When PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power managed modes, the oscillator using the OSC1 pin is disabled. The OSC1 pin (and OSC2 pin, if used by the oscillator) will stop oscillating.

In Secondary Clock modes (SEC\_RUN and SEC\_I-DLE), the Timer1 oscillator is operating and providing the system clock. The Timer1 oscillator may also run in all power managed modes if required to clock Timer1 or Timer3.

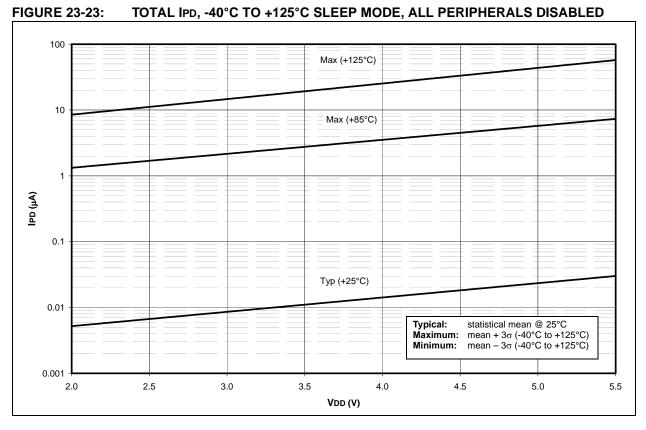

In Internal Oscillator modes (RC\_RUN and RC\_IDLE), the internal oscillator block provides the system clock source. The INTRC output can be used directly to provide the system clock and may be enabled to support various special features, regardless of the power managed mode (see Section 19.2 "Watchdog Timer (WDT)" through Section 19.4 "Fail-Safe Clock Monitor"). The INTOSC output at 8 MHz may be used directly to clock the system, or may be divided down first. The INTOSC output is disabled if the system clock is provided directly from the INTRC output. If the Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The INTRC is required to support WDT operation. The Timer1 oscillator may be operating to support a realtime clock. Other features may be operating that do not require a system clock source (i.e., INTn pins, A/D conversions and others).

## 2.9 Power-up Delays

Power-up delays are controlled by two timers, so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see Sections 4.1 through 4.5.

The first timer is the Power-up Timer (PWRT), which provides a fixed delay on power-up (parameter 33, Table 22-8) if enabled in Configuration Register 2L. The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (LP, XT and HS modes). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

When the HSPLL Oscillator mode is selected, the device is kept in Reset for an additional 2 ms following the HS mode OST delay, so the PLL can lock to the incoming clock frequency.

There is a delay of 5 to 10  $\mu s$  following POR while the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the EC, RC or INTIO modes are used as the primary clock source.

| Oscillator Mode | OSC1 Pin                                              | OSC2 Pin                                              |

|-----------------|-------------------------------------------------------|-------------------------------------------------------|

| RC, INTIO1      | Floating, external resistor should pull high          | At logic low (clock/4 output)                         |

| RCIO, INTIO2    | Floating, external resistor should pull high          | Configured as PORTA, bit 6                            |

| ECIO            | Floating, pulled by external clock                    | Configured as PORTA, bit 6                            |

| EC              | Floating, pulled by external clock                    | At logic low (clock/4 output)                         |

| LP, XT and HS   | Feedback inverter disabled at quiescent voltage level | Feedback inverter disabled at quiescent voltage level |

TABLE 2-3:

OSC1 AND OSC2 PIN STATES IN SLEEP MODE

**Note:** See Table 4-1 in **Section 4.0** "**Reset**" for time-outs due to Sleep and MCLR Reset.

#### 3.3.1 PRI\_IDLE MODE

This mode is unique among the three Low-Power Idle modes, in that it does not disable the primary system clock. For timing sensitive applications, this allows for the fastest resumption of device operation with its more accurate primary clock source, since the clock source does not have to "warm up" or transition from another oscillator.

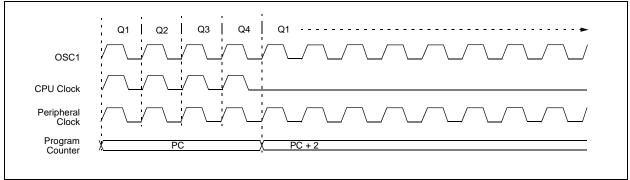

PRI\_IDLE mode is entered by setting the IDLEN bit, clearing the SCS bits and executing a SLEEP instruction. Although the CPU is disabled, the peripherals continue to be clocked from the primary clock source specified in Configuration Register 1H. The OSTS bit remains set in PRI\_IDLE mode (see Figure 3-3).

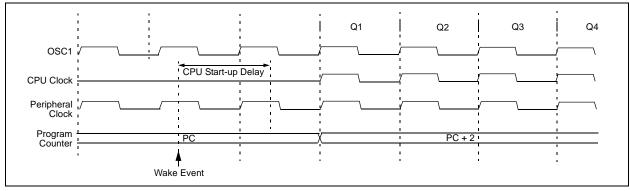

When a wake event occurs, the CPU is clocked from the primary clock source. A delay of approximately 10  $\mu$ s is required between the wake event and code execution starts. This is required to allow the CPU to become ready to execute instructions. After the wakeup, the OSTS bit remains set. The IDLEN and SCS bits are not affected by the wake-up (see Figure 3-4).

#### FIGURE 3-4: TRANSITION TIMING FOR WAKE FROM PRI\_IDLE MODE

## 3.4 Run Modes

If the IDLEN bit is clear when a SLEEP instruction is executed, the CPU and peripherals are both clocked from the source selected using the SCS1:SCS0 bits. While these operating modes may not afford the power conservation of Idle or Sleep modes, they do allow the device to continue executing instructions by using a lower frequency clock source. RC\_RUN mode also offers the possibility of executing code at a frequency greater than the primary clock.

Wake-up from a power managed Run mode can be triggered by an interrupt, or any Reset, to return to fullpower operation. As the CPU is executing code in Run modes, several additional exits from Run modes are possible. They include exit to Sleep mode, exit to a corresponding Idle mode and exit by executing a RESET instruction. While the device is in any of the power managed Run modes, a WDT time-out will result in a WDT Reset.

#### 3.4.1 PRI\_RUN MODE

The PRI\_RUN mode is the normal full-power execution mode. If the SLEEP instruction is never executed, the microcontroller operates in this mode (a SLEEP instruction is executed to enter all other power managed modes). All other power managed modes exit to PRI\_RUN mode when an interrupt or WDT time-out occur.

There is no entry to PRI\_RUN mode. The OSTS bit is set. The IOFS bit may be set if the internal oscillator block is the primary clock source (see **Section 2.7.1** "Oscillator Control Register").

#### 3.4.2 SEC\_RUN MODE

The SEC\_RUN mode is the compatible mode to the "clock switching" feature offered in other PIC18 devices. In this mode, the CPU and peripherals are clocked from the Timer1 oscillator. This gives users the option of lower power consumption while still using a high accuracy clock source.

SEC\_RUN mode is entered by clearing the IDLEN bit, setting SCS1:SCS0 = 01 and executing a SLEEP instruction. The system clock source is switched to the Timer1 oscillator (see Figure 3-9), the primary oscillator is shut down, the T1RUN bit (T1CON<6>) is set and the OSTS bit is cleared.

Note: The Timer1 oscillator should already be running prior to entering SEC\_RUN mode. If the T1OSCEN bit is not set when the SLEEP instruction is executed, the SLEEP instruction will be ignored and entry to SEC\_RUN mode will not occur. If the Timer1 oscillator is enabled, but not yet running, system clocks will be delayed until the oscillator has started; in such situations, initial oscillator operation is far from stable and unpredictable operation may result.

When a wake event occurs, the peripherals and CPU continue to be clocked from the Timer1 oscillator while the primary clock is started. When the primary clock becomes ready, a clock switchback to the primary clock occurs (see Figure 3-6). When the clock switch is complete, the T1RUN bit is cleared, the OSTS bit is set and the primary clock is providing the system clock. The IDLEN and SCS bits are not affected by the wake-up. The Timer1 oscillator continues to run.

Firmware can force an exit from SEC\_RUN mode. By clearing the T1OSCEN bit (T1CON<3>), an exit from SEC\_RUN back to normal full-power operation is triggered. The Timer1 oscillator will continue to run and provide the system clock, even though the T1OSCEN bit is cleared. The primary clock is started. When the primary clock becomes ready, a clock switchback to the primary clock occurs (see Figure 3-6). When the clock switch is cleared, the Timer1 oscillator is disabled, the T1RUN bit is cleared, the OSTS bit is set and the primary clock is providing the system clock. The IDLEN and SCS bits are not affected by the wake-up.

#### FIGURE 3-9: TIMING TRANSITION FOR ENTRY TO SEC\_RUN MODE

### 3.4.4 EXIT TO IDLE MODE

An exit from a power managed Run mode to its corresponding Idle mode is executed by setting the IDLEN bit and executing a SLEEP instruction. The CPU is halted at the beginning of the instruction following the SLEEP instruction. There are no changes to any of the clock source status bits (OSTS, IOFS or T1RUN). While the CPU is halted, the peripherals continue to be clocked from the previously selected clock source.

### 3.4.5 EXIT TO SLEEP MODE

An exit from a power managed Run mode to Sleep mode is executed by clearing the IDLEN and SCS1:SCS0 bits and executing a SLEEP instruction. The code is no different than the method used to invoke Sleep mode from the normal operating (full-power) mode.

The primary clock and internal oscillator block are disabled. The INTRC will continue to operate if the WDT is enabled. The Timer1 oscillator will continue to run, if enabled in the T1CON register (Register 12-1). All clock source Status bits are cleared (OSTS, IOFS and T1RUN).

#### 3.5 Wake from Power Managed Modes

An exit from any of the power managed modes is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power managed modes. The clocking subsystem actions are discussed in each of the power managed modes (see Sections 3.2 through 3.4).

| Note: | If application code is timing sensitive, it |

|-------|---------------------------------------------|

|       | should wait for the OSTS bit to become      |

|       | set before continuing. Use the interval     |

|       | during the low-power exit sequence          |

|       | (before OSTS is set) to perform timing      |

|       | insensitive "housekeeping" tasks.           |

Device behavior during Low-Power mode exits is summarized in Table 3-3.

#### 3.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit a power managed mode and resume fullpower operation. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set. On all exits from Low-Power mode by interrupt, code execution branches to the interrupt vector if the GIE/GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see Section 9.0 "Interrupts").

#### 3.6.1 EXAMPLE – EUSART

An adjustment may be indicated when the EUSART begins to generate framing errors, or receives data with errors while in Asynchronous mode. Framing errors indicate that the system clock frequency is too high – try decrementing the value in the OSCTUNE register to reduce the system clock frequency. Errors in data may suggest that the system clock speed is too low – increment OSCTUNE.

#### 3.6.2 EXAMPLE – TIMERS

This technique compares system clock speed to some reference clock. Two timers may be used; one timer is clocked by the peripheral clock, while the other is clocked by a fixed reference source, such as the Timer1 oscillator.

Both timers are cleared, but the timer clocked by the reference generates interrupts. When an interrupt occurs, the internally clocked timer is read and both timers are cleared. If the internally clocked timer value is greater than expected, then the internal oscillator block is running too fast – decrement OSCTUNE.

## 3.6.3 EXAMPLE – CCP IN CAPTURE MODE

A CCP module can use free running Timer1 (or Timer3), clocked by the internal oscillator block and an external event with a known period (i.e., AC power frequency). The time of the first event is captured in the CCPRxH:CCPRxL registers and is recorded for use later. When the second event causes a capture, the time of the first event is subtracted from the time of the second event. Since the period of the external event is known, the time difference between events can be calculated.

If the measured time is much greater than the calculated time, the internal oscillator block is running too fast – decrement OSCTUNE. If the measured time is much less than the calculated time, the internal oscillator block is running too slow-increment OSCTUNE.

| R/W-x            | R/W-x                                                                                                                                                                          | U-0                                                                                                                                                                                                                   | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-x                | R/W-0            | R/S-0            | R/S-0          |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------|------------------|----------------|--|--|--|

| EEPGD            | CFGS                                                                                                                                                                           | _                                                                                                                                                                                                                     | FREE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | WRERR <sup>(1)</sup> | WREN             | WR               | RD             |  |  |  |

| bit 7            |                                                                                                                                                                                |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | · ·                  |                  |                  | bit C          |  |  |  |

|                  |                                                                                                                                                                                |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |                  |                  |                |  |  |  |

| Legend:          |                                                                                                                                                                                |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |                  |                  |                |  |  |  |

| R = Readable     | e bit                                                                                                                                                                          | W = Writable                                                                                                                                                                                                          | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U = Unimplem         | nented bit, read | l as '0'         |                |  |  |  |

| S = Bit can or   | nly be set                                                                                                                                                                     | x = Bit is unk                                                                                                                                                                                                        | x = Bit is unknown -n/n = Value at POR and BOR/Value at all other structures of the second |                      |                  |                  |                |  |  |  |

| '1' = Bit is set |                                                                                                                                                                                | '0' = Bit is cle                                                                                                                                                                                                      | eared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | HC = Bit is cle      | ared by hardw    | are              |                |  |  |  |

| bit 7            | EEPGD: Fla                                                                                                                                                                     | sh Program or                                                                                                                                                                                                         | Data EEPRO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | M Memory Selec       | ct bit           |                  |                |  |  |  |

|                  |                                                                                                                                                                                | program Flash                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ,                    |                  |                  |                |  |  |  |

|                  |                                                                                                                                                                                | data EEPROM                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |                  |                  |                |  |  |  |

| bit 6            | CFGS: Flas                                                                                                                                                                     | h Program/Data                                                                                                                                                                                                        | a EEPROM or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Configuration S      | elect bit        |                  |                |  |  |  |

|                  |                                                                                                                                                                                | 1 = Accesses Configuration, User ID and Device ID Registers                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |                  |                  |                |  |  |  |

|                  |                                                                                                                                                                                | -                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PROM Memory          |                  |                  |                |  |  |  |

| bit 5            | •                                                                                                                                                                              | nted: Read as                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |                  |                  |                |  |  |  |

| bit 4            |                                                                                                                                                                                | Row Erase Enable bit                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |                  |                  |                |  |  |  |

|                  | <ul> <li>1 = Erase the program memory row addressed by TBLPTR on the next WR command<br/>(cleared by completion of erase operation – TBLPTR&lt;5:0&gt; are ignored)</li> </ul> |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |                  |                  |                |  |  |  |

|                  | 0 = Perform write only                                                                                                                                                         |                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |                  |                  |                |  |  |  |

| bit 3            | WRERR: EE                                                                                                                                                                      | EPROM Error F                                                                                                                                                                                                         | lag bit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |                  |                  |                |  |  |  |

|                  |                                                                                                                                                                                | 1 = A write operation was prematurely terminated (any Reset during self-timed programming)                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |                  |                  |                |  |  |  |

|                  | 0 = The writ                                                                                                                                                                   | e operation completed normally                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |                  |                  |                |  |  |  |