Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 7x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 18-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1320-h-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                                                       |     |

|-------|---------------------------------------------------------------------------------------|-----|

| 2.0   | Oscillator Configurations                                                             | 10  |

| 3.0   | Power Managed Modes                                                                   |     |

| 4.0   | Reset                                                                                 |     |

| 5.0   | Memory Organization                                                                   | 39  |

| 6.0   | Flash Program Memory                                                                  | 55  |

| 7.0   | Data EEPROM Memory                                                                    | 64  |

| 8.0   | 8 x 8 Hardware Multiplier                                                             | 68  |

| 9.0   | Interrupts                                                                            |     |

| 10.0  | I/O Ports                                                                             | 83  |

| 11.0  | Timer0 Module                                                                         | 95  |

| 12.0  | Timer1 Module                                                                         |     |

| 13.0  | Timer2 Module                                                                         | 104 |

| 14.0  |                                                                                       |     |

| 15.0  |                                                                                       |     |

| 16.0  | Enhanced Addressable Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | 126 |

| 17.0  | 10-Bit Analog-to-Digital Converter (A/D) Module                                       | 149 |

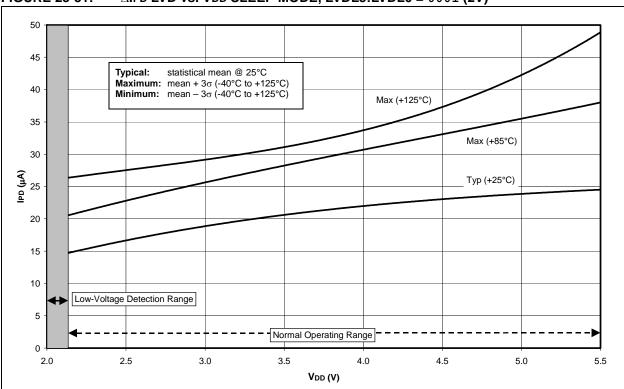

| 18.0  | Low-Voltage Detect                                                                    | 160 |

| 19.0  | Special Features of the CPU                                                           | 165 |

| 20.0  | Instruction Set Summary                                                               | 184 |

| 21.0  | Development Support                                                                   | 226 |

| 22.0  |                                                                                       |     |

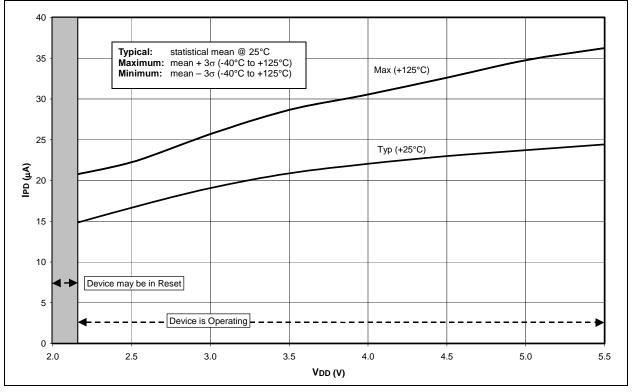

| 23.0  | DC and AC Characteristics Graphs and Tables                                           | 262 |

| 24.0  | Packaging Information                                                                 | 280 |

| Appe  | andix A: Revision History                                                             | 290 |

| Appe  | andix B: Device Differences                                                           | 290 |

| Appe  | andix C: Conversion Considerations                                                    | 291 |

| Appe  | andix D: Migration from Baseline to Enhanced Devices                                  | 291 |

|       | andix E: Migration from Mid-Range to Enhanced Devices                                 |     |

| Appe  | andix F: Migration from High-End to Enhanced Devices                                  | 292 |

|       | Microchip Web Site                                                                    |     |

| Custo | omer Change Notification Service                                                      | 293 |

| Custo | omer Support                                                                          | 293 |

| PIC1  | 8F1220/1320 Product Identification System                                             |     |

# 3.4.4 EXIT TO IDLE MODE

An exit from a power managed Run mode to its corresponding Idle mode is executed by setting the IDLEN bit and executing a SLEEP instruction. The CPU is halted at the beginning of the instruction following the SLEEP instruction. There are no changes to any of the clock source status bits (OSTS, IOFS or T1RUN). While the CPU is halted, the peripherals continue to be clocked from the previously selected clock source.

# 3.4.5 EXIT TO SLEEP MODE

An exit from a power managed Run mode to Sleep mode is executed by clearing the IDLEN and SCS1:SCS0 bits and executing a SLEEP instruction. The code is no different than the method used to invoke Sleep mode from the normal operating (full-power) mode.

The primary clock and internal oscillator block are disabled. The INTRC will continue to operate if the WDT is enabled. The Timer1 oscillator will continue to run, if enabled in the T1CON register (Register 12-1). All clock source Status bits are cleared (OSTS, IOFS and T1RUN).

# 3.5 Wake from Power Managed Modes

An exit from any of the power managed modes is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power managed modes. The clocking subsystem actions are discussed in each of the power managed modes (see Sections 3.2 through 3.4).

| Note: | If application code is timing sensitive, it |

|-------|---------------------------------------------|

|       | should wait for the OSTS bit to become      |

|       | set before continuing. Use the interval     |

|       | during the low-power exit sequence          |

|       | (before OSTS is set) to perform timing      |

|       | insensitive "housekeeping" tasks.           |

Device behavior during Low-Power mode exits is summarized in Table 3-3.

# 3.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit a power managed mode and resume fullpower operation. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set. On all exits from Low-Power mode by interrupt, code execution branches to the interrupt vector if the GIE/GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see Section 9.0 "Interrupts").

# 5.3 Fast Register Stack

A "fast return" option is available for interrupts. A fast register stack is provided for the Status, WREG and BSR registers and is only one in depth. The stack is not readable or writable and is loaded with the current value of the corresponding register when the processor vectors for an interrupt. The values in the registers are then loaded back into the working registers, if the RETFIE, FAST instruction is used to return from the interrupt.

All interrupt sources will push values into the stack registers. If both low and high priority interrupts are enabled, the stack registers cannot be used reliably to return from low priority interrupts. If a high priority interrupt occurs while servicing a low priority interrupt, the stack register values stored by the low priority interrupt will be overwritten. Users must save the key registers in software during a low priority interrupt.

If interrupt priority is not used, all interrupts may use the fast register stack for returns from interrupt.

If no interrupts are used, the fast register stack can be used to restore the Status, WREG and BSR registers at the end of a subroutine call. To use the fast register stack for a subroutine call, a CALL LABEL, FAST instruction must be executed to save the Status, WREG and BSR registers to the fast register stack. A RETURN, FAST instruction is then executed to restore these registers from the fast register stack.

Example 5-1 shows a source code example that uses the fast register stack during a subroutine call and return.

#### EXAMPLE 5-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST | ;STATUS, WREG, BSR      |

|-----------------|-------------------------|

|                 | ;SAVED IN FAST REGISTER |

|                 | ; STACK                 |

| •               |                         |

| •               |                         |

|                 |                         |

| SUB1 •          |                         |

| •               |                         |

| RETURN, FAST    | ;RESTORE VALUES SAVED   |

|                 | ;IN FAST REGISTER STACK |

|                 |                         |

# 5.4 PCL, PCLATH and PCLATU

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide. The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits and is not directly readable or writable. Updates to the PCH register may be performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits and is not directly readable or writable. Updates to the PCLATH register. Updates to the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits and is not directly readable or writable. Updates to the PCU register may be performed through the PCLATU register.

The contents of PCLATH and PCLATU will be transferred to the program counter by any operation that writes PCL. Similarly, the upper two bytes of the program counter will be transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 5.8.1** "**Computed GOTO**").

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the LSB of PCL is fixed to a value of '0'. The PC increments by two to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

| R/W-x                                                                                                        | R/W-x                            | U-0                                                                                                                                                                                                                   | R/W-0                  | R/W-x                | R/W-0            | R/S-0            | R/S-0          |  |  |  |

|--------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------|------------------|------------------|----------------|--|--|--|

| EEPGD                                                                                                        | CFGS                             | _                                                                                                                                                                                                                     | FREE                   | WRERR <sup>(1)</sup> | WREN             | WR               | RD             |  |  |  |

| bit 7                                                                                                        |                                  |                                                                                                                                                                                                                       |                        | · ·                  |                  |                  | bit C          |  |  |  |

|                                                                                                              |                                  |                                                                                                                                                                                                                       |                        |                      |                  |                  |                |  |  |  |

| Legend:                                                                                                      |                                  |                                                                                                                                                                                                                       |                        |                      |                  |                  |                |  |  |  |

| R = Readable                                                                                                 | e bit                            | W = Writable                                                                                                                                                                                                          | bit                    | U = Unimplem         | nented bit, read | l as '0'         |                |  |  |  |

| S = Bit can or                                                                                               | nly be set                       | x = Bit is unk                                                                                                                                                                                                        | nown                   | -n/n = Value a       | t POR and BO     | R/Value at all o | ther Resets    |  |  |  |

| '1' = Bit is set                                                                                             |                                  | '0' = Bit is cle                                                                                                                                                                                                      | eared                  | HC = Bit is cle      | ared by hardw    | are              |                |  |  |  |

| bit 7                                                                                                        | EEPGD: Fla                       | sh Program or                                                                                                                                                                                                         | Data EEPRO             | M Memory Selec       | ct bit           |                  |                |  |  |  |

|                                                                                                              |                                  | program Flash                                                                                                                                                                                                         |                        | ,                    |                  |                  |                |  |  |  |

|                                                                                                              |                                  | data EEPROM                                                                                                                                                                                                           |                        |                      |                  |                  |                |  |  |  |

| bit 6                                                                                                        | CFGS: Flas                       | h Program/Data                                                                                                                                                                                                        | a EEPROM or            | Configuration S      | elect bit        |                  |                |  |  |  |

|                                                                                                              |                                  |                                                                                                                                                                                                                       |                        | Device ID Reg        | isters           |                  |                |  |  |  |

|                                                                                                              |                                  | -                                                                                                                                                                                                                     |                        | PROM Memory          |                  |                  |                |  |  |  |

| bit 5                                                                                                        | •                                | nted: Read as                                                                                                                                                                                                         |                        |                      |                  |                  |                |  |  |  |

| bit 4                                                                                                        | FREE: Flash Row Erase Enable bit |                                                                                                                                                                                                                       |                        |                      |                  |                  |                |  |  |  |

|                                                                                                              |                                  | se the program memory row addressed by TBLPTR on the next WR command                                                                                                                                                  |                        |                      |                  |                  |                |  |  |  |

| <pre>(cleared by completion of erase operation - TBLPTR&lt;5:0&gt; are ignored) 0 = Perform write only</pre> |                                  |                                                                                                                                                                                                                       |                        |                      |                  |                  |                |  |  |  |

| bit 3                                                                                                        | WRERR: EE                        | EPROM Error F                                                                                                                                                                                                         | lag bit <sup>(1)</sup> |                      |                  |                  |                |  |  |  |

|                                                                                                              |                                  |                                                                                                                                                                                                                       |                        | rminated (any R      | eset during sel  | lf-timed prograr | nming)         |  |  |  |

|                                                                                                              | 0 = The writ                     | te operation cor                                                                                                                                                                                                      | mpleted norma          | ally                 |                  |                  |                |  |  |  |

| bit 2                                                                                                        | WREN: Prog                       | gram/Erase Ena                                                                                                                                                                                                        | able bit               |                      |                  |                  |                |  |  |  |

|                                                                                                              |                                  | orogram/erase                                                                                                                                                                                                         | ,                      |                      |                  |                  |                |  |  |  |

| 1.1.4                                                                                                        |                                  |                                                                                                                                                                                                                       | rasing of prog         | ram Flash and o      | ata EEPROM       |                  |                |  |  |  |

| bit 1                                                                                                        | WR: Write C                      |                                                                                                                                                                                                                       | Maraakurita            |                      |                  |                  |                |  |  |  |

|                                                                                                              |                                  | <ul> <li>Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle.</li> <li>(The operation is self-timed and the bit is cleared by hardware once write is complete. The WR</li> </ul> |                        |                      |                  |                  |                |  |  |  |

|                                                                                                              |                                  | bit can only be set (not cleared) in software.)                                                                                                                                                                       |                        |                      |                  |                  |                |  |  |  |

|                                                                                                              |                                  | cle completed                                                                                                                                                                                                         |                        |                      |                  |                  |                |  |  |  |

| bit 0                                                                                                        | RD: Read C                       | ontrol bit                                                                                                                                                                                                            |                        |                      |                  |                  |                |  |  |  |

|                                                                                                              |                                  | a memory read                                                                                                                                                                                                         |                        |                      |                  |                  |                |  |  |  |

|                                                                                                              |                                  | akes one cycle<br>e. RD bit canno                                                                                                                                                                                     |                        | ed in hardware.      | The RD bit car   | n only be set (r | not cleared) i |  |  |  |

|                                                                                                              | 0 = Read co                      |                                                                                                                                                                                                                       |                        | LL: GD – 1.)         |                  |                  |                |  |  |  |

| Note 1: W                                                                                                    | hen a WRERR                      | occurs the EE                                                                                                                                                                                                         | PGD and CE(            | 25 hits are not c    | laarad This all  | 0.005            |                |  |  |  |

|                                                                                                              |                                  |                                                                                                                                                                                                                       |                        |                      |                  |                  |                |  |  |  |

# REGISTER 6-1: EECON1: EEPROM CONTROL 1 REGISTER

# EXAMPLE 6-3: WRITING TO FLASH PROGRAM MEMORY

|            | MOVLW<br>MOVWF | D'64<br>COUNTER  | ; | number of bytes in erase block           |

|------------|----------------|------------------|---|------------------------------------------|

|            | MOVWF          |                  | ; | point to buffer                          |

|            | MOVWF          | FSR0H            |   |                                          |

|            | MOVLW          | BUFFER_ADDR_LOW  |   |                                          |

|            | MOVWF          | FSROL            |   |                                          |

|            | MOVLW          | CODE_ADDR_UPPER  | ; | Load TBLPTR with the base                |

|            | MOVWF          | TBLPTRU          | ; | address of the memory block              |

|            | MOVLW          | CODE_ADDR_HIGH   |   | -                                        |

|            | MOVWF          | TBLPTRH          |   |                                          |

|            | MOVLW          |                  | ; | 6 LSB = 0                                |

|            | MOVWF          | TBLPTRL          |   |                                          |

| READ_BLOCK | _              |                  |   |                                          |

|            | TBLRD*+        | F                | ; | read into TABLAT, and inc                |

|            | MOVF           | TABLAT, W        | ; | get data                                 |

|            | MOVWF          | POSTINC0         | ; | store data and increment FSR0            |

|            | DECFSZ         | COUNTER          | ; | done?                                    |

|            | GOTO           | READ_BLOCK       | ; | repeat                                   |

| MODIFY_WOR | D              |                  |   |                                          |

|            | MOVLW          | DATA_ADDR_HIGH   | ; | point to buffer                          |

|            | MOVWF          | FSROH            |   |                                          |

|            | MOVLW          | DATA_ADDR_LOW    |   |                                          |

|            | MOVWF          | FSROL            |   |                                          |

|            | MOVLW          | NEW_DATA_LOW     | ; | update buffer word and increment FSR0    |

|            | MOVWF          | POSTINC0         |   |                                          |

|            | MOVLW          | NEW_DATA_HIGH    | ; | update buffer word                       |

|            | MOVWF          | INDF0            |   |                                          |

| ERASE_BLOC | !K             |                  |   |                                          |

|            | MOVLW          | CODE_ADDR_UPPER  | ; | load TBLPTR with the base                |

|            | MOVWF          | TBLPTRU          | ; | address of the memory block              |

|            | MOVLW          | CODE_ADDR_HIGH   |   |                                          |

|            | MOVWF          | TBLPTRH          |   |                                          |

|            | MOVLW          | CODE_ADDR_LOW    | ; | 6 LSB = 0                                |

|            | MOVWF          | TBLPTRL          |   |                                          |

|            | BCF            | EECON1, CFGS     | ; | point to PROG/EEPROM memory              |

|            | BSF            | EECON1, EEPGD    | ; | point to FLASH program memory            |

|            | BSF            | EECON1, WREN     | ; | enable write to memory                   |

|            | BSF            | EECON1, FREE     | ; | enable Row Erase operation               |

|            | BCF            | INTCON, GIE      | ; | disable interrupts                       |

|            | MOVLW          | 55h              | ; | Required sequence                        |

|            | MOVWF          | EECON2           | ; | write 55H                                |

|            | MOVLW          | AAh              |   |                                          |

|            | MOVWF          | EECON2           | ; | write AAH                                |

|            | BSF            | EECON1, WR       | ; | start erase (CPU stall)                  |

|            | NOP            |                  |   |                                          |

|            | BSF            | INTCON, GIE      | ; | re-enable interrupts                     |

| WRITE_BUFF | 'ER_BACK       |                  |   |                                          |

|            | MOVLW          | 8                | ; | number of write buffer groups of 8 bytes |

|            | MOVWF          | COUNTER_HI       |   |                                          |

|            | MOVLW          | BUFFER_ADDR_HIGH | ; | point to buffer                          |

|            | MOVWF          | FSROH            |   |                                          |

|            | MOVLW          | BUFFER_ADDR_LOW  |   |                                          |

|            | MOVWF          | FSROL            |   |                                          |

| PROGRAM_LC | OP             |                  |   |                                          |

|            | MOVLW          | 8                | ; | number of bytes in holding register      |

|            | MOVWF          | COUNTER          |   |                                          |

|            |                |                  |   |                                          |

| R/W-x           | R/W-x                                                                                          | U-0                                                                                                                                                                                                                       | R/W-0                  | R/W-x                | R/W-0            | R/S-0             | R/S-0          |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------|------------------|-------------------|----------------|--|--|--|

| EEPGD           | CFGS                                                                                           |                                                                                                                                                                                                                           | FREE                   | WRERR <sup>(1)</sup> | WREN             | WR                | RD             |  |  |  |

| bit 7           | •                                                                                              |                                                                                                                                                                                                                           |                        |                      |                  |                   | bit C          |  |  |  |

|                 |                                                                                                |                                                                                                                                                                                                                           |                        |                      |                  |                   |                |  |  |  |

| Legend:         |                                                                                                |                                                                                                                                                                                                                           |                        |                      |                  |                   |                |  |  |  |

| R = Readabl     | e bit                                                                                          | W = Writable                                                                                                                                                                                                              | bit                    | U = Unimplem         | ented bit, read  | as '0'            |                |  |  |  |

| S = Bit can o   | nly be set                                                                                     | x = Bit is unk                                                                                                                                                                                                            | nown                   | -n/n = Value a       | t POR and BO     | R/Value at all o  | ther Resets    |  |  |  |

| '1' = Bit is se | t                                                                                              | '0' = Bit is cle                                                                                                                                                                                                          | eared                  | HC = Bit is cle      | ared by hardw    | are               |                |  |  |  |

| bit 7           | EEPGD: Fla                                                                                     | ish Program or                                                                                                                                                                                                            | Data EEPRO             | M Memory Selec       | ct bit           |                   |                |  |  |  |

|                 |                                                                                                | program Flash                                                                                                                                                                                                             |                        | ,                    |                  |                   |                |  |  |  |

|                 |                                                                                                | data EEPROM                                                                                                                                                                                                               |                        |                      |                  |                   |                |  |  |  |

| bit 6           | CFGS: Flas                                                                                     | h Program/Data                                                                                                                                                                                                            | a EEPROM or            | Configuration S      | elect bit        |                   |                |  |  |  |

|                 |                                                                                                |                                                                                                                                                                                                                           |                        | Device ID Reg        | sters            |                   |                |  |  |  |

|                 |                                                                                                | -                                                                                                                                                                                                                         |                        | PROM Memory          |                  |                   |                |  |  |  |

| bit 5           | •                                                                                              | nted: Read as                                                                                                                                                                                                             |                        |                      |                  |                   |                |  |  |  |

| bit 4           | FREE: Flash Row Erase Enable bit                                                               |                                                                                                                                                                                                                           |                        |                      |                  |                   |                |  |  |  |

|                 |                                                                                                | L = Erase the program memory row addressed by TBLPTR on the next WR command<br>(cleared by completion of erase operation – TBLPTR<5:0> are ignored)                                                                       |                        |                      |                  |                   |                |  |  |  |

|                 | (cleared by completion of erase operation – TBLPTR<5:0> are ignored)<br>0 = Perform write only |                                                                                                                                                                                                                           |                        |                      |                  |                   |                |  |  |  |

| bit 3           | WRERR: EE                                                                                      | EPROM Error F                                                                                                                                                                                                             | lag bit <sup>(1)</sup> |                      |                  |                   |                |  |  |  |

|                 |                                                                                                |                                                                                                                                                                                                                           |                        | rminated (any R      | eset during sel  | f-timed program   | nming)         |  |  |  |

|                 |                                                                                                | te operation cor                                                                                                                                                                                                          | -                      | ally                 |                  |                   |                |  |  |  |

| bit 2           |                                                                                                | gram/Erase Ena                                                                                                                                                                                                            |                        |                      |                  |                   |                |  |  |  |

|                 |                                                                                                | program/erase                                                                                                                                                                                                             | ,                      |                      |                  |                   |                |  |  |  |

| <b>L</b> :L 4   |                                                                                                |                                                                                                                                                                                                                           | rasing or prog         | ram Flash and o      |                  |                   |                |  |  |  |

| bit 1           | WR: Write C                                                                                    |                                                                                                                                                                                                                           | Maraaa/writa           |                      | mmomory          | aa ayala ar yyrit |                |  |  |  |

|                 |                                                                                                | <ul> <li>1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle.</li> <li>(The operation is self-timed and the bit is cleared by hardware once write is complete. The WR</li> </ul> |                        |                      |                  |                   |                |  |  |  |

|                 |                                                                                                | bit can only be set (not cleared) in software.)                                                                                                                                                                           |                        |                      |                  |                   |                |  |  |  |

|                 | 0 = Write cy                                                                                   | cle completed                                                                                                                                                                                                             |                        |                      |                  |                   |                |  |  |  |

| bit 0           | RD: Read C                                                                                     | ontrol bit                                                                                                                                                                                                                |                        |                      |                  |                   |                |  |  |  |

|                 |                                                                                                | a memory read                                                                                                                                                                                                             |                        |                      |                  |                   |                |  |  |  |

|                 |                                                                                                | akes one cycle<br>e. RD bit canno                                                                                                                                                                                         |                        | d in hardware.       | The RD bit car   | n only be set (r  | not cleared) i |  |  |  |

|                 | 0 = Read co                                                                                    |                                                                                                                                                                                                                           |                        | OD                   |                  |                   |                |  |  |  |

| Note 1: W       | hen a WRERR                                                                                    | occurs, the FF                                                                                                                                                                                                            | PGD and CF             | GS bits are not c    | leared. This all | ows               |                |  |  |  |

|                 |                                                                                                |                                                                                                                                                                                                                           |                        |                      |                  |                   |                |  |  |  |

# REGISTER 7-1: EECON1: EEPROM CONTROL 1 REGISTER

# 9.4 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Priority registers (IPR1, IPR2). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

#### REGISTER 9-8: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

| U-0   | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|---------|---------|---------|-----|---------|---------|---------|

| —     | ADIP    | RCIP    | TXIP    | —   | CCP1IP  | TMR2IP  | TMR1IP  |

| bit 7 |         |         |         |     |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                        |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ADIP: A/D Converter Interrupt Priority bit                                                                                                                                                                                                                                        |

|       | 1 = High priority                                                                                                                                                                                                                                                                 |

|       | 0 = Low priority                                                                                                                                                                                                                                                                  |

| bit 5 | RCIP: EUSART Receive Interrupt Priority bit                                                                                                                                                                                                                                       |

|       | 1 = High priority                                                                                                                                                                                                                                                                 |

|       | 0 = Low priority                                                                                                                                                                                                                                                                  |

| bit 4 | <b>TXIP:</b> EUSART Transmit Interrupt Priority bit                                                                                                                                                                                                                               |

|       | 1 = High priority                                                                                                                                                                                                                                                                 |

|       | 0 = Low priority                                                                                                                                                                                                                                                                  |

| bit 3 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                        |

| bit 5 | Onimplemented. Read as 0                                                                                                                                                                                                                                                          |

| bit 2 | <b>CCP1IP:</b> CCP1 Interrupt Priority bit                                                                                                                                                                                                                                        |

|       | -                                                                                                                                                                                                                                                                                 |

|       | CCP1IP: CCP1 Interrupt Priority bit                                                                                                                                                                                                                                               |

|       | <b>CCP1IP:</b> CCP1 Interrupt Priority bit<br>1 = High priority                                                                                                                                                                                                                   |

| bit 2 | <ul> <li>CCP1IP: CCP1 Interrupt Priority bit</li> <li>1 = High priority</li> <li>0 = Low priority</li> <li>TMR2IP: TMR2 to PR2 Match Interrupt Priority bit</li> <li>1 = High priority</li> </ul>                                                                                 |

| bit 2 | <ul> <li>CCP1IP: CCP1 Interrupt Priority bit</li> <li>1 = High priority</li> <li>0 = Low priority</li> <li>TMR2IP: TMR2 to PR2 Match Interrupt Priority bit</li> </ul>                                                                                                            |

| bit 2 | <ul> <li>CCP1IP: CCP1 Interrupt Priority bit</li> <li>1 = High priority</li> <li>0 = Low priority</li> <li>TMR2IP: TMR2 to PR2 Match Interrupt Priority bit</li> <li>1 = High priority</li> </ul>                                                                                 |

| bit 2 | <pre>CCP1IP: CCP1 Interrupt Priority bit 1 = High priority 0 = Low priority TMR2IP: TMR2 to PR2 Match Interrupt Priority bit 1 = High priority 0 = Low priority</pre>                                                                                                             |

| bit 2 | <ul> <li>CCP1IP: CCP1 Interrupt Priority bit</li> <li>1 = High priority</li> <li>0 = Low priority</li> <li>TMR2IP: TMR2 to PR2 Match Interrupt Priority bit</li> <li>1 = High priority</li> <li>0 = Low priority</li> <li>TMR1IP: TMR1 Overflow Interrupt Priority bit</li> </ul> |

# 9.5 RCON Register

The RCON register contains bits used to determine the cause of the last Reset or wake-up from a low-power mode. RCON also contains the bit that enables interrupt priorities (IPEN).

#### REGISTER 9-10: RCON: RESET CONTROL REGISTER

| R/W-0 | U-0 | U-0 | R/W-1 | R-1 | R-1 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-----|-----|-------|-------|

| IPEN  | —   | _   | RI    | TO  | PD  | POR   | BOR   |

| bit 7 |     |     |       |     |     |       | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | <b>IPEN:</b> Interrupt Priority Enable bit<br>1 = Enable priority levels on interrupts<br>0 = Disable priority levels on interrupts (PIC16CXXX Compatibility mode) |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-5 | Unimplemented: Read as '0'                                                                                                                                         |

| bit 4   | RI: RESET Instruction Flag bit                                                                                                                                     |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

| bit 3   | TO: Watchdog Time-out Flag bit                                                                                                                                     |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

| bit 2   | PD: Power-down Detection Flag bit                                                                                                                                  |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

| bit 1   | POR: Power-on Reset Status bit                                                                                                                                     |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

| bit 0   | BOR: Brown-out Reset Status bit                                                                                                                                    |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

|         |                                                                                                                                                                    |

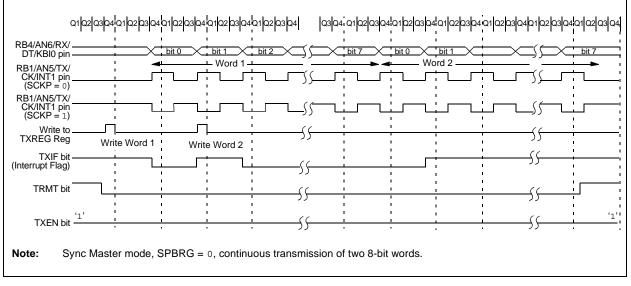

# 16.4 EUSART Synchronous Master Mode

The Synchronous Master mode is entered by setting the CSRC bit (TXSTA<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTA<4>). In addition, enable bit, SPEN (RCSTA<7>), is set in order to configure the RB1/AN5/ TX/CK/INT1 and RB4/AN6/RX/DT/KBI0 I/O pins to CK (clock) and DT (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CK line. Clock polarity is selected with the SCKP bit (BAUDCTL<5>); setting SCKP sets the Idle state on CK as high, while clearing the bit sets the Idle state as low. This option is provided to support Microwire devices with this module.

#### 16.4.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 16-2. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The shift register obtains its data from the Read/Write Transmit Buffer register, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG is empty and interrupt bit, TXIF (PIR1<4>), is set. The interrupt can be enabled/disabled by setting/clearing enable bit, TXIE (PIE1<4>). Flag bit, TXIF, will be set, regardless of the state of enable bit, TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register.

While flag bit, TXIF, indicates the status of the TXREG register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit, which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory, so it is not available to the user.

To set up a Synchronous Master Transmission:

- Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

# FIGURE 16-10: SYNCHRONOUS TRANSMISSION

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|----------|-------|-------|-------|--------|--------|--------|--------|--------|

| CONFIG2H | —     | _     | —     | WDTPS3 | WDTPS2 | WDTPS2 | WDTPS0 | WDTEN  |

| RCON     | IPEN  | _     | —     | RI     | TO     | PD     | POR    | BOR    |

| WDTCON   | —     |       | —     | _      | _      |        |        | SWDTEN |

TABLE 19-2:

SUMMARY OF WATCHDOG TIMER REGISTERS

**Legend:** Shaded cells are not used by the Watchdog Timer.

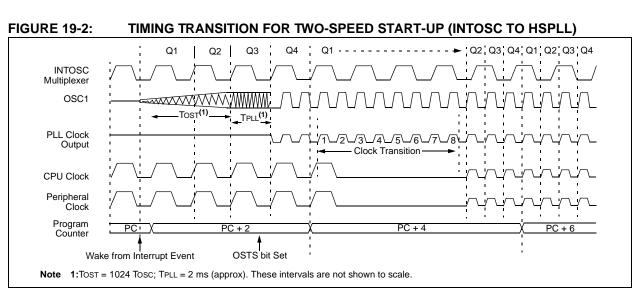

# 19.3 Two-Speed Start-up

The Two-Speed Start-up feature helps to minimize the latency period from oscillator start-up to code execution by allowing the microcontroller to use the INTRC oscillator as a clock source until the primary clock source is available. It is enabled by setting the IESO bit in Configuration Register 1H (CONFIG1H<7>).

Two-Speed Start-up is available only if the primary oscillator mode is LP, XT, HS or HSPLL (crystal-based modes). Other sources do not require an OST start-up delay; for these, Two-Speed Start-up is disabled.

When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer after a Power-on Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI\_RUN mode.

Because the OSCCON register is cleared on Reset events, the INTOSC (or postscaler) clock source is not initially available after a Reset event; the INTRC clock is used directly at its base frequency. To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IFRC2:IFRC0, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting IFRC2:IFRC0 prior to entering Sleep mode. In all other power managed modes, Two-Speed Start-up is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

# 19.3.1 SPECIAL CONSIDERATIONS FOR USING TWO-SPEED START-UP

While using the INTRC oscillator in Two-Speed Startup, the device still obeys the normal command sequences for entering power managed modes, including serial SLEEP instructions (refer to **Section 3.1.3 "Multiple Sleep Commands"**). In practice, this means that user code can change the SCS1:SCS0 bit settings and issue SLEEP commands before the OST times out. This would allow an application to briefly wake-up, perform routine "housekeeping" tasks and return to Sleep before the device starts to operate from the primary oscillator.

User code can also check if the primary clock source is currently providing the system clocking by checking the status of the OSTS bit (OSCCON<3>). If the bit is set, the primary oscillator is providing the system clock. Otherwise, the internal oscillator block is providing the clock during wake-up from Reset or Sleep mode.

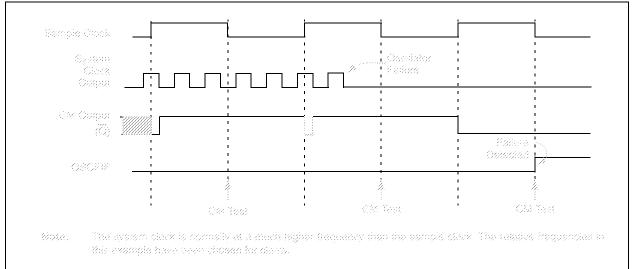

#### 19.4.2 EXITING FAIL-SAFE OPERATION

The Fail-Safe condition is terminated by either a device Reset, or by entering a power managed mode. On Reset, the controller starts the primary clock source specified in Configuration Register 1H (with any required start-up delays that are required for the oscillator mode, such as OST or PLL timer). The INTOSC multiplexer provides the system clock until the primary clock source becomes ready (similar to a Two-Speed Start-up). The clock system source is then switched to the primary clock (indicated by the OSTS bit in the OSCCON register becoming set). The Fail-Safe Clock Monitor then resumes monitoring the peripheral clock.

The primary clock source may never become ready during start-up. In this case, operation is clocked by the INTOSC multiplexer. The OSCCON register will remain in its Reset state until a power managed mode is entered.

Entering a power managed mode by loading the OSCCON register and executing a SLEEP instruction will clear the Fail-Safe condition. When the Fail-Safe condition is cleared, the clock monitor will resume monitoring the peripheral clock.

#### 19.4.3 FSCM INTERRUPTS IN POWER MANAGED MODES

As previously mentioned, entering a power managed mode clears the Fail-Safe condition. By entering a power managed mode, the clock multiplexer selects the clock source selected by the OSCCON register. Fail-Safe monitoring of the power managed clock source resumes in the power managed mode.

If an oscillator failure occurs during power managed operation, the subsequent events depend on whether or not the oscillator failure interrupt is enabled. If enabled (OSCFIF = 1), code execution will be clocked by the INTOSC multiplexer. An automatic transition back to the failed clock source will not occur.

If the interrupt is disabled, the device will not exit the power managed mode on oscillator failure. Instead, the device will continue to operate as before, but clocked by the INTOSC multiplexer. While in Idle mode, subsequent interrupts will cause the CPU to begin executing instructions while being clocked by the INTOSC multiplexer. The device will not transition to a different clock source until the Fail-Safe condition is cleared.

#### FIGURE 19-4: FSCM TIMING DIAGRAM

# PIC18F1220/1320

| NEGF                                         | Negate f                                                                                                                                                                                                                                                            |              |        |                     |  |  |  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------|---------------------|--|--|--|

| Syntax:                                      | [ label ]                                                                                                                                                                                                                                                           | NEGF         | f [,a] |                     |  |  |  |

| Operands:                                    | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                            |              |        |                     |  |  |  |

| Operation:                                   | $(\overline{f}) + 1 \rightarrow f$                                                                                                                                                                                                                                  |              |        |                     |  |  |  |

| Status Affected:                             | N, OV, C,                                                                                                                                                                                                                                                           | DC, Z        |        |                     |  |  |  |

| Encoding:                                    | 0110                                                                                                                                                                                                                                                                | 110a         | ffff   | ffff                |  |  |  |

| Description:                                 | Location 'f' is negated using two's<br>complement. The result is placed in<br>the data memory location 'f'. If 'a' is<br>'0', the Access Bank will be<br>selected, overriding the BSR value.<br>If 'a' = 1, then the bank will be<br>selected as per the BSR value. |              |        |                     |  |  |  |

| Words:                                       | 1                                                                                                                                                                                                                                                                   |              |        |                     |  |  |  |

| Cycles:                                      | 1                                                                                                                                                                                                                                                                   |              |        |                     |  |  |  |

| Q Cycle Activity:                            |                                                                                                                                                                                                                                                                     |              |        |                     |  |  |  |

| Q1                                           | Q2                                                                                                                                                                                                                                                                  | Q            | 3      | Q4                  |  |  |  |

| Decode                                       | Read<br>register 'f'                                                                                                                                                                                                                                                | Proce<br>Dat |        | Write<br>gister 'f' |  |  |  |

| Example: NEGF REG, 1                         |                                                                                                                                                                                                                                                                     |              |        |                     |  |  |  |

| Before Instruction<br>REG = 0011 1010 [0x3A] |                                                                                                                                                                                                                                                                     |              |        |                     |  |  |  |

| NOF   | )              | No Operation  |       |      |    |          |  |

|-------|----------------|---------------|-------|------|----|----------|--|

| Synt  | ax:            | [ label ]     | NOP   |      |    |          |  |

| Ope   | rands:         | None          |       |      |    |          |  |

| Ope   | ration:        | No opera      | tion  |      |    |          |  |

| Statu | us Affected:   | None          |       |      |    |          |  |

| Enco  | oding:         | 0000          | 0000  | 000  | 0  | 0000     |  |

|       |                | 1111          | xxxx  | XXX  | x  | XXXX     |  |

| Des   | cription:      | No operation. |       |      |    |          |  |

| Wor   | ds:            | 1             |       |      |    |          |  |

| Cycl  | es:            | 1             |       |      |    |          |  |

| QC    | ycle Activity: |               |       |      |    |          |  |

|       | Q1             | Q2            | Q3    |      |    | Q4       |  |

|       | Decode         | No No M       |       | No   |    |          |  |

|       |                | operation     | opera | tion | op | peration |  |

#### Example:

None.

After Instruction

REG = 1100 0110 [0xC6]

| TBLWT            | Table Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |      |                                            |  |  |  |