Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 7x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1320-h-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.1 Power-on Reset (POR)

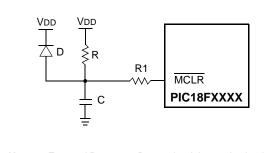

A Power-on Reset pulse is generated on-chip when VDD rise is detected. To take advantage of the POR circuitry, just tie the MCLR pin through a resistor (1k to 10 k $\Omega$ ) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset delay. A minimum rise rate for VDD is specified (parameter D004). For a slow rise time, see Figure 4-2.

When the device starts normal operation (i.e., exits the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

FIGURE 4-2: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1:External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2:  $R < 40 \text{ k}\Omega$  is recommended to make sure that the voltage drop across R does not violate the device's electrical specification.

- 3:  $R1 \ge 1 \ k\Omega$  will limit any current flowing into  $\overline{MCLR}$  from external capacitor C, in the event of  $\overline{MCLR}/VPP$  pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

# 4.2 Power-up Timer (PWRT)

The Power-up Timer (PWRT) of the PIC18F1220/1320 is an 11-bit counter, which uses the INTRC source as the clock input. This yields a count of  $2048 \times 32 \ \mu s = 65.6 \ ms$ . While the PWRT is counting, the device is held in Reset.

The power-up time delay will vary from chip-to-chip due to VDD, temperature and process variation. See DC parameter 33 for details.

The PWRT is enabled by clearing Configuration bit, PWRTEN.

# 4.3 Oscillator Start-up Timer (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter 33). This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP, HS and HSPLL modes and only on Power-on Reset, or on exit from most low-power modes.

### 4.4 PLL Lock Time-out

With the PLL enabled in its PLL mode, the time-out sequence following a Power-on Reset is slightly different from other oscillator modes. A portion of the Power-up Timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the Oscillator Start-up Time-out.

### 4.5 Brown-out Reset (BOR)

A Configuration bit, BOR, can disable (if clear/ programmed), or enable (if set) the Brown-out Reset circuitry. If VDD falls below VBOR (parameter D005) for greater than TBOR (parameter 35), the brown-out situation will reset the chip. A Reset may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR. If the Power-up Timer is enabled, it will be invoked after VDD rises above VBOR; it then will keep the chip in Reset for an additional time delay, TPWRT (parameter 33). If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay. Enabling BOR Reset does not automatically enable the PWRT.

# 4.6 Time-out Sequence

On power-up, the time-out sequence is as follows: First, after the POR pulse has cleared, PWRT time-out is invoked (if enabled). Then, the OST is activated. The total time-out will vary based on oscillator configuration and the status of the PWRT. For example, in RC mode with the PWRT disabled, there will be no time-out at all. Figure 4-3, Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7 depict time-out sequences on power-up.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, all time-outs will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 4-5). This is useful for testing purposes or to synchronize more than one PIC18FXXXX device operating in parallel.

Table 4-2 shows the Reset conditions for some Special Function Registers, while Table 4-3 shows the Reset conditions for all the registers.

#### EXAMPLE 6-3: WRITING TO FLASH PROGRAM MEMORY (CONTINUED)

| WRITE_WORD  | _TO_HREG | S         |              |   |                                                      |

|-------------|----------|-----------|--------------|---|------------------------------------------------------|

|             | MOVF     | POSTINC   | 0, W         | ; | get low byte of buffer data and increment FSR0       |

|             | MOVWF    | TABLAT    |              | ; | present data to table latch                          |

|             | TBLWT+*  | :         |              | ; | short write                                          |

|             |          |           |              | ; | to internal TBLWT holding register, increment TBLPTR |

|             | DECFSZ   | COUNTER   |              | ; | loop until buffers are full                          |

|             | GOTO     | WRITE_W   | ORD_TO_HREGS |   |                                                      |

| PROGRAM_MEI | MORY     |           |              |   |                                                      |

|             | BCF      | INTCON,   | GIE          | ; | disable interrupts                                   |

|             | MOVLW    | 55h       |              | ; | required sequence                                    |

|             | MOVWF    | EECON2    |              | ; | write 55H                                            |

|             | MOVLW    | AAh       |              |   |                                                      |

|             | MOVWF    | EECON2    |              | ; | write AAH                                            |

|             | BSF      | EECON1,   | WR           | ; | start program (CPU stall)                            |

|             | NOP      |           |              |   |                                                      |

|             | BSF      | INTCON,   | GIE          | ; | re-enable interrupts                                 |

|             | DECFSZ   | COUNTER   | _HI          | ; | loop until done                                      |

|             | GOTO PF  | ROGRAM_LC | OOP          |   |                                                      |

|             | BCF      | EECON1,   | WREN         | ; | disable write to memory                              |

|             |          |           |              |   |                                                      |

#### 6.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

# 6.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed if needed. The WRERR bit is set when a write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset during normal operation. In these situations, users can check the WRERR bit and rewrite the location.

### 6.6 Flash Program Operation During Code Protection

See **Section 19.0 "Special Features of the CPU"** for details on code protection of Flash program memory.

| IADLE 0 |           |              |                                                                      |              |              |             |              |             |                       |                                 |

|---------|-----------|--------------|----------------------------------------------------------------------|--------------|--------------|-------------|--------------|-------------|-----------------------|---------------------------------|

| Name    | Bit 7     | Bit 6        | Bit 5                                                                | Bit 4        | Bit 3        | Bit 2       | Bit 1        | Bit 0       | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

| TBLPTRU | _         |              | bit 21                                                               | Program M    | lemory Table | Pointer Upp | er Byte (TBL | PTR<20:16>) | 00 0000               | 00 0000                         |

| TBPLTRH | Program N | lemory Table | Pointer High Byte (TBLPTR<15:8>)         0000 0000         0000 0000 |              |              |             |              |             |                       |                                 |

| TBLPTRL | Program N | lemory Table | e Pointer H                                                          | ligh Byte (  | TBLPTR<7:0   | )>)         |              |             | 0000 0000             | 0000 0000                       |

| TABLAT  | Program N | lemory Table | e Latch                                                              |              |              |             |              |             | 0000 0000             | 0000 0000                       |

| INTCON  | GIE/GIEH  | PEIE/GIEL    | TMR0IE                                                               | INTE         | RBIE         | TMR0IF      | INTF         | RBIF        | 0000 000x             | 0000 000u                       |

| EECON2  | EEPROM    | Control Regi | ster 2 (no                                                           | t a physical | l register)  |             |              |             |                       | —                               |

| EECON1  | EEPGD     | CFGS         | _                                                                    | FREE         | WRERR        | WREN        | WR           | RD          | xx-0 x000             | uu-0 u000                       |

| IPR2    | OSCFIP    | _            | _                                                                    | EEIP         | _            | LVDIP       | TMR3IP       | _           | 11 -11-               | 11 -11-                         |

| PIR2    | OSCFIF    |              | _                                                                    | EEIF         | _            | LVDIF       | TMR3IF       |             | 00 -00-               | 00 -00-                         |

| PIE2    | OSCFIE    |              | _                                                                    | EEIE         | _            | LVDIE       | TMR3IE       |             | 00 -00-               | 00 -00-                         |

#### TABLE 6-2: REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

# 9.3 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Enable registers (PIE1, PIE2). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

### REGISTER 9-6: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| U-0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-----|---------|---------|---------|

| —     | ADIE    | RCIE    | TXIE    | —   | CCP1IE  | TMR2IE  | TMR1IE  |

| bit 7 |         |         |         |     |         |         | bit 0   |

#### Legend:

| Legenu.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7          | Unimplemented: Read as '0'                                                                                                                                                                                                                          |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6          | ADIE: A/D Converter Interrupt Enable bit                                                                                                                                                                                                            |

|                | <ul><li>1 = Enables the A/D interrupt</li><li>0 = Disables the A/D interrupt</li></ul>                                                                                                                                                              |

| bit 5          | RCIE: EUSART Receive Interrupt Enable bit                                                                                                                                                                                                           |

|                | <ul><li>1 = Enables the EUSART receive interrupt</li><li>0 = Disables the EUSART receive interrupt</li></ul>                                                                                                                                        |

| bit 4          | TXIE: EUSART Transmit Interrupt Enable bit                                                                                                                                                                                                          |

|                | <ul> <li>1 = Enables the EUSART transmit interrupt</li> <li>0 = Disables the EUSART transmit interrupt</li> </ul>                                                                                                                                   |

|                | •                                                                                                                                                                                                                                                   |

| bit 3          | Unimplemented: Read as '0'                                                                                                                                                                                                                          |

| bit 3<br>bit 2 | Unimplemented: Read as '0'<br>CCP1IE: CCP1 Interrupt Enable bit                                                                                                                                                                                     |

|                | •                                                                                                                                                                                                                                                   |

|                | CCP1IE: CCP1 Interrupt Enable bit                                                                                                                                                                                                                   |

|                | <b>CCP1IE:</b> CCP1 Interrupt Enable bit<br>1 = Enables the CCP1 interrupt                                                                                                                                                                          |

| bit 2          | <b>CCP1IE:</b> CCP1 Interrupt Enable bit<br>1 = Enables the CCP1 interrupt<br>0 = Disables the CCP1 interrupt                                                                                                                                       |

| bit 2          | <ul> <li>CCP1IE: CCP1 Interrupt Enable bit</li> <li>1 = Enables the CCP1 interrupt</li> <li>0 = Disables the CCP1 interrupt</li> <li>TMR2IE: TMR2 to PR2 Match Interrupt Enable bit</li> <li>1 = Enables the TMR2 to PR2 match interrupt</li> </ul> |

# 9.5 RCON Register

The RCON register contains bits used to determine the cause of the last Reset or wake-up from a low-power mode. RCON also contains the bit that enables interrupt priorities (IPEN).

#### REGISTER 9-10: RCON: RESET CONTROL REGISTER

| R/W-0 | U-0 | U-0 | R/W-1 | R-1 | R-1 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-----|-----|-------|-------|

| IPEN  | —   | _   | RI    | TO  | PD  | POR   | BOR   |

| bit 7 |     |     |       |     |     |       | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | <b>IPEN:</b> Interrupt Priority Enable bit<br>1 = Enable priority levels on interrupts<br>0 = Disable priority levels on interrupts (PIC16CXXX Compatibility mode) |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-5 | Unimplemented: Read as '0'                                                                                                                                         |

| bit 4   | RI: RESET Instruction Flag bit                                                                                                                                     |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

| bit 3   | TO: Watchdog Time-out Flag bit                                                                                                                                     |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

| bit 2   | PD: Power-down Detection Flag bit                                                                                                                                  |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

| bit 1   | POR: Power-on Reset Status bit                                                                                                                                     |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

| bit 0   | BOR: Brown-out Reset Status bit                                                                                                                                    |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

|         |                                                                                                                                                                    |

# 11.0 TIMER0 MODULE

The Timer0 module has the following features:

- Software selectable as an 8-bit or 16-bit timer/ counter

- Readable and writable

- Dedicated 8-bit software programmable prescaler

- · Clock source selectable to be external or internal

- Interrupt-on-overflow from FFh to 00h in 8-bit mode and FFFFh to 0000h in 16-bit mode

- Edge select for external clock

#### REGISTER 11-1: TOCON: TIMERO CONTROL REGISTER

Figure 11-1 shows a simplified block diagram of the Timer0 module in 8-bit mode and Figure 11-2 shows a simplified block diagram of the Timer0 module in 16-bit mode.

The T0CON register (Register 11-1) is a readable and writable register that controls all the aspects of Timer0, including the prescale selection.

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TMR0ON  | T08BIT  | TOCS    | TOSE    | PSA     | T0PS2   | T0PS1   | T0PS0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:                                                                                                                                                                                                                                                                                             |                        |                                                                                                     |                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| R = Readable bit                                                                                                                                                                                                                                                                                    |                        | W = Writable bit                                                                                    | U = Unimplemented bit, read as '0'                                                        |

| u = Bit is unchanged x = Bit is unknown                                                                                                                                                                                                                                                             |                        | x = Bit is unknown                                                                                  | -n/n = Value at POR and BOR/Value at all other Resets                                     |

| '1' = Bit is set '0' = Bit is cleared                                                                                                                                                                                                                                                               |                        |                                                                                                     |                                                                                           |

| bit 7                                                                                                                                                                                                                                                                                               | TMR0ON:                | Timer0 On/Off Control bit                                                                           |                                                                                           |

|                                                                                                                                                                                                                                                                                                     | 1 = Enabl<br>0 = Stops |                                                                                                     |                                                                                           |

| bit 6                                                                                                                                                                                                                                                                                               | 1 = Timer              | mer0 8-bit/16-bit Control bit<br>0 is configured as an 8-bit tir<br>0 is configured as a 16-bit tir |                                                                                           |

| bit 5 <b>TOCS:</b> Timer0 Clock Source Select bit<br>1 = Transition on TOCKI pin<br>0 = Internal instruction cycle clock (CLI                                                                                                                                                                       |                        |                                                                                                     | KO)                                                                                       |

| bit 4 <b>TOSE:</b> Timer0 Source Edge Select bit<br>1 = Increment on high-to-low transition<br>0 = Increment on low-to-high transition                                                                                                                                                              |                        |                                                                                                     | •                                                                                         |

| bit 3 <b>PSA:</b> Timer0 Prescaler Assignment bit<br>1 = TImer0 prescaler is NOT assigned.                                                                                                                                                                                                          |                        |                                                                                                     | I. Timer0 clock input bypasses prescaler.<br>er0 clock input comes from prescaler output. |

| bit 2-0 <b>TOPS&lt;2:0&gt;:</b> Timer0 Prescaler Select bits<br>111 = 1:256 Prescale value<br>110 = 1:128 Prescale value<br>101 = 1:64 Prescale value<br>100 = 1:32 Prescale value<br>011 = 1:16 Prescale value<br>010 = 1:8 Prescale value<br>001 = 1:4 Prescale value<br>000 = 1:2 Prescale value |                        |                                                                                                     | its                                                                                       |

## 11.1 Timer0 Operation

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing the T0CS bit. In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit. In Counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit (T0SE). Clearing the T0SE bit selects the rising edge.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 11.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not readable or writable.

The PSA and T0PS2:T0PS0 bits determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, x, ..., etc.) will clear the prescaler count.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

### 11.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution).

# 11.3 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF bit. The interrupt can be masked by clearing the TMR0IE bit. The TMR0IF bit must be cleared in software by the Timer0 module Interrupt Service Routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from Low-Power Sleep mode, since the timer requires clock cycles even when T0CS is set.

# 11.4 16-Bit Mode Timer Reads and Writes

TMR0H is not the high byte of the timer/counter in 16-bit mode, but is actually a buffered version of the high byte of Timer0 (refer to Figure 11-2). The high byte of the Timer0 counter/timer is not directly readable nor writable. TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0, without having to verify that the read of the high and low byte were valid due to a rollover between successive reads of the high and low byte.

A write to the high byte of Timer0 must also take place through the TMR0H Buffer register. Timer0 high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

| Name   | Bit 7              | Bit 6              | Bit 5    | Bit 4   | Bit 3       | Bit 2      | Bit 1         | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|--------------------|--------------------|----------|---------|-------------|------------|---------------|-------|----------------------|---------------------------------|

| TMR0L  | Timer0 Modu        | ule Low Byte F     | Register |         |             |            |               |       | xxxx xxxx            | uuuu uuuu                       |

| TMR0H  | Timer0 Modu        | ule High Byte I    | Register |         |             |            |               |       | 0000 0000            | 0000 0000                       |

| INTCON | GIE/GIEH           | PEIE/GIEL          | TMR0IE   | INT0IE  | RBIE        | TMR0IF     | <b>INT0IF</b> | RBIF  | 0000 000x            | 0000 000u                       |

| T0CON  | TMR0ON             | T08BIT             | TOCS     | TOSE    | PSA         | T0PS2      | T0PS1         | T0PS0 | 1111 1111            | 1111 1111                       |

| TRISA  | RA7 <sup>(1)</sup> | RA6 <sup>(1)</sup> | —        | PORTA D | ata Directi | on Registe | r             |       | 11-1 1111            | 11-1 1111                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

Note 1: RA6 and RA7 are enabled as I/O pins, depending on the oscillator mode selected in Configuration Word 1H.

| U-0             | R-1                                        | U-0                                                                              | R/W-0/0        | R/W-0/0      | U-0              | R/W-0/0          | R/W-0/0        |

|-----------------|--------------------------------------------|----------------------------------------------------------------------------------|----------------|--------------|------------------|------------------|----------------|

| _               | RCIDL                                      | —                                                                                | SCKP           | BRG16        | _                | WUE              | ABDEN          |

| bit 7           |                                            |                                                                                  |                |              |                  |                  | bit 0          |

|                 |                                            |                                                                                  |                |              |                  |                  |                |

| Legend:         |                                            |                                                                                  |                |              |                  |                  |                |

| R = Readab      |                                            | W = Writable                                                                     |                | •            | mented bit, read |                  |                |

| u = Bit is und  | -                                          | x = Bit is unkt                                                                  |                | -n/n = value | at POR and BC    | R/Value at all o | ther Resets    |

| '1' = Bit is se | et                                         | '0' = Bit is cle                                                                 | ared           |              |                  |                  |                |

| bit 7           | Unimplemen                                 | ted: Read as '                                                                   | 0'             |              |                  |                  |                |

| bit 6           | -                                          | ive Operation                                                                    |                |              |                  |                  |                |

|                 | 1 = Receiver<br>0 = Receiver               |                                                                                  |                |              |                  |                  |                |

| bit 5           | Unimplemen                                 | ted: Read as '                                                                   | 0'             |              |                  |                  |                |

| bit 4           | SCKP: Synch                                | ronous Clock                                                                     | Polarity Selec | t bit        |                  |                  |                |

|                 | Asynchronous<br>Unused in this             |                                                                                  |                |              |                  |                  |                |

|                 |                                            | mode:<br>for clock (CK)<br>for clock (CK)                                        | •              | I            |                  |                  |                |

| bit 3           | <b>BRG16:</b> 16-b                         | it Baud Rate R                                                                   | egister Enabl  | e bit        |                  |                  |                |

|                 |                                            |                                                                                  |                | H and SPBRC  |                  | RGH value igno   | ored           |

| bit 2           | Unimplemen                                 | ted: Read as '                                                                   | 0'             |              |                  |                  |                |

| bit 1           | WUE: Wake-                                 | up Enable bit                                                                    |                |              |                  |                  |                |

|                 | hardware                                   | will continue t<br>on following r<br>ot monitored o<br><u>mode:</u>              | ising edge     |              | rupt generated   | on falling edge; | bit cleared in |

| bit 0           |                                            | -Baud Detect                                                                     | Enable bit     |              |                  |                  |                |

|                 | Asynchronous<br>1 = Enable b<br>cleared ii | <u>s mode:</u><br>aud rate meas<br>n hardware up<br>e measuremen<br><u>mode:</u> | urement on th  |              | er – requires re | eception of a Sy | nc byte (55h); |

## REGISTER 16-3: BAUDCTL: BAUD RATE CONTROL REGISTER

### 16.3.2 EUSART ASYNCHRONOUS RECEIVER

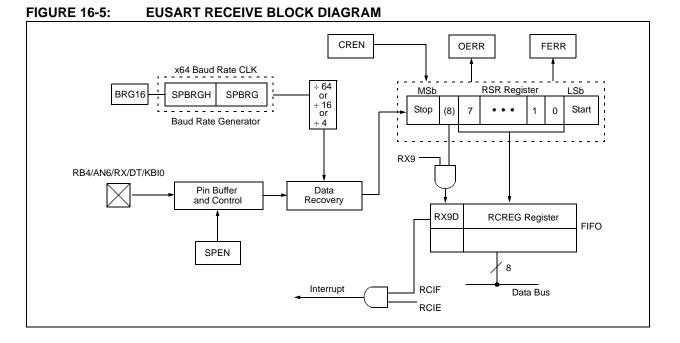

The receiver block diagram is shown in Figure 16-5. The data is received on the RB4/AN6/RX/DT/KBI0 pin and drives the data recovery block. The data recovery block is actually a high-speed shifter, operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, set enable bit RCIE.

- 4. If 9-bit reception is desired, set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit, RCIF, will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

# 16.3.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are required, set the RCEN bit and select the desired priority level with the RCIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- 5. Set the ADDEN bit to enable address detect.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF bit will be set when reception is complete. The interrupt will be Acknowledged if the RCIE and GIE bits are set.

- 8. Read the RCSTA register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 9. Read RCREG to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

| Name    | Bit 7     | Bit 6        | Bit 5        | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-----------|--------------|--------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| INTCON  | GIE/GIEH  | PEIE/GIEL    | TMR0IE       | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | x000 000x            | 0000 000u                       |

| PIR1    | _         | ADIF         | RCIF         | TXIF   | _     | CCP1IF | TMR2IF | TMR1IF | -000 -000            | -000 -000                       |

| PIE1    | _         | ADIE         | RCIE         | TXIE   |       | CCP1IE | TMR2IE | TMR1IE | -000 -000            | -000 -000                       |

| IPR1    | —         | ADIP         | RCIP         | TXIP   | _     | CCP1IP | TMR2IP | TMR1IP | -111 -111            | -111 -111                       |

| RCSTA   | SPEN      | RX9          | SREN         | CREN   | ADDEN | FERR   | OERR   | RX9D   | x000 000x            | 0000 000x                       |

| RCREG   | EUSART R  | eceive Regis | ter          |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA   | CSRC      | TX9          | TXEN         | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |

| BAUDCTL | _         | RCIDL        | —            | SCKP   | BRG16 | _      | WUE    | ABDEN  | -1-1 0-00            | -1-1 0-00                       |

| SPBRGH  | Baud Rate | Generator Re | egister High | n Byte |       |        |        |        | 0000 0000            | 0000 0000                       |

| SPBRG   | Baud Rate | Generator Re | egister Low  | Byte   |       |        |        |        | 0000 0000            | 0000 0000                       |

### TABLE 16-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception.

| U-0             | U-0             | U-0                                                                                  | U-0           | U-0             | U-0               | R/P-1            | R/P-1       |  |  |  |

|-----------------|-----------------|--------------------------------------------------------------------------------------|---------------|-----------------|-------------------|------------------|-------------|--|--|--|

| _               | —               | —                                                                                    | —             | —               | _                 | EBTR1            | EBTR0       |  |  |  |

| bit 7           |                 |                                                                                      |               |                 |                   |                  | bit 0       |  |  |  |

|                 |                 |                                                                                      |               |                 |                   |                  |             |  |  |  |

| Legend:         |                 |                                                                                      |               |                 |                   |                  |             |  |  |  |

| R = Readabl     | le bit          | W = Writable                                                                         | bit           | U = Unimpler    | mented bit, read  | as '0'           |             |  |  |  |

| u = Bit is und  | changed         | x = Bit is unkr                                                                      | nown          | -n/n = Value a  | at POR and BOI    | R/Value at all o | ther Resets |  |  |  |

| '1' = Bit is se | et              | '0' = Bit is clea                                                                    | ared          | P = Program     | mable bit         |                  |             |  |  |  |

|                 |                 |                                                                                      |               |                 |                   |                  |             |  |  |  |

| bit 7-2         | Unimplemen      | ted: Read as '                                                                       | כ'            |                 |                   |                  |             |  |  |  |

| bit 1           | EBTR1: Table    | e Read Protecti                                                                      | on bit (PIC18 | F1320)          |                   |                  |             |  |  |  |

|                 | ,               |                                                                                      | <i>'</i>      |                 | reads executed    |                  |             |  |  |  |

|                 | 0 = Block 1(0)  | 001000-001FFF                                                                        | h) protected  | from table read | is executed in o  | ther blocks      |             |  |  |  |

| bit 0           | EBTR0: Table    | e Read Protect                                                                       | on bit (PIC18 | F1320)          |                   |                  |             |  |  |  |

|                 | •               |                                                                                      | <i>,</i> .    |                 | eads executed in  |                  |             |  |  |  |

|                 |                 |                                                                                      | <i>·</i> •    |                 | s executed in oth | her blocks       |             |  |  |  |

| bit 1           |                 | e Read Protect                                                                       | •             | ,               |                   |                  |             |  |  |  |

|                 |                 |                                                                                      |               |                 | reads executed    |                  |             |  |  |  |

| hit O           |                 |                                                                                      | <i>,</i> .    |                 | is executed in o  | THEI DIOCKS      |             |  |  |  |

| bit 0           |                 | e Read Protecti                                                                      | •             | ,               |                   |                  |             |  |  |  |

|                 | T = BIOCK 0 (0) | 1 = Block 0 (000200-0007FFh) not protected from table reads executed in other blocks |               |                 |                   |                  |             |  |  |  |

# REGISTER 19-11: CONFIG7H: CONFIGURATION REGISTER 7 HIGH (BYTE ADDRESS 30000Dh)

0 = Block 0 (000200-0007FFh) protected from table reads executed in other blocks

| U-0   | R/P-1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| —     | EBTRB | —   | —   | —   | —   | —   | —     |

| bit 7 |       |     |     |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | P = Programmable bit                                  |

bit 7 Unimplemented: Read as '0'

| bit 6   | EBTRB: Boot Block Table Read Protection bit                                             |

|---------|-----------------------------------------------------------------------------------------|

|         | 1 = Boot Block (000000-0001FFh) not protected from table reads executed in other blocks |

|         | 0 = Boot Block (000000-0001FFh) protected from table reads executed in other blocks     |

| bit 5-0 | Unimplemented: Read as '0'                                                              |

| DAW                 | Decimal A                                                                       | djust W Re                                                                                                         | gister                                                                                    |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:             | [label] D                                                                       | WAW                                                                                                                |                                                                                           |  |  |  |  |

| Operands:           | None                                                                            |                                                                                                                    |                                                                                           |  |  |  |  |

| Operation:          | (W<3:0>)<br>else                                                                | If $[W<3:0>>9]$ or $[DC = 1]$ then<br>(W<3:0>) + 6 $\rightarrow$ W<3:0>;<br>else<br>(W<3:0>) $\rightarrow$ W<3:0>; |                                                                                           |  |  |  |  |

| Status Affected:    | (W<7:4>)<br>else                                                                | > 9] or [C =<br>+ 6 → W<7:4<br>→ W<7:4>;                                                                           |                                                                                           |  |  |  |  |

| Encoding:           | 0000                                                                            | 0000 000                                                                                                           | 00 0111                                                                                   |  |  |  |  |

| Description:        | DAW adjus<br>resulting fr<br>two variab<br>format) an<br>packed BC<br>may be se | ests the 8-bit work of the earlied les (each in produces a CD result. The toy DAW regard or to the DAW             | value in W,<br>er addition of<br>backed BCD<br>a correct<br>e Carry bit<br>ardless of its |  |  |  |  |

| Words:              | 1                                                                               |                                                                                                                    |                                                                                           |  |  |  |  |

| Cycles:             | 1                                                                               |                                                                                                                    |                                                                                           |  |  |  |  |

| Q Cycle Activity:   |                                                                                 |                                                                                                                    |                                                                                           |  |  |  |  |

| Q1                  | Q2                                                                              | Q3                                                                                                                 | Q4                                                                                        |  |  |  |  |

| Decode              | Read<br>register W                                                              | Process<br>Data                                                                                                    | Write<br>W                                                                                |  |  |  |  |

| Example 1:          | DAW                                                                             |                                                                                                                    |                                                                                           |  |  |  |  |

| Before Instru       |                                                                                 |                                                                                                                    |                                                                                           |  |  |  |  |

| W<br>C              | = 0xA5<br>= 0                                                                   |                                                                                                                    |                                                                                           |  |  |  |  |

| DC                  | = 0                                                                             |                                                                                                                    |                                                                                           |  |  |  |  |

| After Instruct<br>W | ion<br>= 0x05                                                                   |                                                                                                                    |                                                                                           |  |  |  |  |

| C<br>DC             | = 1<br>= 0                                                                      |                                                                                                                    |                                                                                           |  |  |  |  |

| Example 2:          | - 0                                                                             |                                                                                                                    |                                                                                           |  |  |  |  |

| Before Instru       | iction                                                                          |                                                                                                                    |                                                                                           |  |  |  |  |

| W                   | = 0xCE                                                                          |                                                                                                                    |                                                                                           |  |  |  |  |

| C<br>DC             | = 0<br>= 0                                                                      |                                                                                                                    |                                                                                           |  |  |  |  |

| After Instruct      | tion                                                                            |                                                                                                                    |                                                                                           |  |  |  |  |

| W<br>C<br>DC        | = 0x34<br>= 1<br>= 0                                                            |                                                                                                                    |                                                                                           |  |  |  |  |

|                     |                                                                                 |                                                                                                                    |                                                                                           |  |  |  |  |

| DECF        |          | Decreme                                                                                             | ent f                                                                        |                                                                            |                                                                 |  |  |  |  |

|-------------|----------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|

| Syntax:     |          | [ label ]                                                                                           | [ <i>label</i> ] DECF f [,d [,a]]                                            |                                                                            |                                                                 |  |  |  |  |

| Operands:   |          | $0 \le f \le 25$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                  |                                                                              |                                                                            |                                                                 |  |  |  |  |

| Operation:  |          | (f) – 1 $\rightarrow$                                                                               | dest                                                                         |                                                                            |                                                                 |  |  |  |  |

| Status Affe | cted:    | C, DC, N                                                                                            | , OV, Z                                                                      |                                                                            |                                                                 |  |  |  |  |

| Encoding:   |          | 0000                                                                                                | 01da                                                                         | ffff                                                                       | ffff                                                            |  |  |  |  |

| Description |          | Decreme<br>the result<br>the result<br>'f' (defaul<br>Bank will<br>the BSR<br>bank will<br>BSR valu | is stored<br>is stored<br>t). If 'a' is<br>be seled<br>value. If<br>be seled | d in W. I<br>d back in<br>s '0', the<br>ted, ove<br>'a' = 1, f<br>ted as p | f 'd' is '1',<br>n register<br>e Access<br>erriding<br>then the |  |  |  |  |

| Words:      |          | 1                                                                                                   |                                                                              |                                                                            |                                                                 |  |  |  |  |

| Cycles:     |          | 1                                                                                                   |                                                                              |                                                                            |                                                                 |  |  |  |  |

| Q Cycle A   | ctivity: |                                                                                                     |                                                                              |                                                                            |                                                                 |  |  |  |  |

| Q           | 1        | Q2                                                                                                  | Q3                                                                           | }                                                                          | Q4                                                              |  |  |  |  |

| Dece        | ode      | ReadProcessWrite toregister 'f'Datadestination                                                      |                                                                              |                                                                            |                                                                 |  |  |  |  |

| Example:    | Inotr    | DECF                                                                                                | CNT                                                                          |                                                                            |                                                                 |  |  |  |  |

$\begin{array}{rrrr} Before Instruction \\ CNT &=& 0 \\ Z &=& 0 \\ \\ After Instruction \\ CNT &=& 0 \\ Z &=& 1 \end{array}$

| LFSI  | R              | Load FSR                                                           | 2                                   |                                      | MOVF                          | Move f                                                          |                 |                                                       |

|-------|----------------|--------------------------------------------------------------------|-------------------------------------|--------------------------------------|-------------------------------|-----------------------------------------------------------------|-----------------|-------------------------------------------------------|

| Synt  | ax:            | [ label ]                                                          | LFSR f,k                            |                                      | Syntax:                       | [ label ]                                                       | MOVF f          | [,d [,a]]                                             |

| Oper  | rands:         | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 40 \end{array}$ | 95                                  |                                      | Operands:                     | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \end{array}$ | 5               |                                                       |

| Oper  | ration:        | $k \rightarrow FSRf$                                               |                                     |                                      |                               | a ∈ [0,1]                                                       |                 |                                                       |

| Statu | is Affected:   | None                                                               |                                     |                                      | Operation:                    | $f \rightarrow dest$                                            |                 |                                                       |

| Enco  | oding:         | 1110<br>1111                                                       | 1110 00<br>0000 k <sub>7</sub> k    |                                      | Status Affected:<br>Encoding: | N, Z                                                            | 00da i          | ffff ffff                                             |

| Desc  | cription:      |                                                                    | literal 'k' is lo<br>ect register p |                                      | Description:                  |                                                                 | a destinati     | ster 'f' are<br>on dependent<br>'. If 'd' is 'f', the |

| Word  | ds:            | 2                                                                  |                                     |                                      |                               |                                                                 |                 | . If 'd' is 'f', the                                  |

| Cycle | es:            | 2                                                                  |                                     |                                      |                               |                                                                 |                 | k in register 'f'<br>' can be any-                    |

| QC    | ycle Activity: |                                                                    |                                     |                                      |                               |                                                                 |                 | te bank. If 'a' is                                    |

| -     | Q1             | Q2                                                                 | Q3                                  | Q4                                   |                               | '0', the Ac                                                     |                 |                                                       |

|       | Decode         | Read literal<br>'k' MSB                                            | Process<br>Data                     | Write literal<br>'k' MSB to<br>FSRfH |                               | lf 'a' = 1, t                                                   | hen the ba      | the BSR value.<br>ank will be<br>BSR value            |

|       | Decode         | Read literal                                                       | Process                             | Write literal                        |                               | (default).                                                      |                 |                                                       |

| ļ     |                | ʻk' LSB                                                            | Data                                | 'k' to FSRfL                         | Words:                        | 1                                                               |                 |                                                       |

| Exar  | nole:          | LFSR 2, (                                                          | )x3AB                               |                                      | Cycles:                       | 1                                                               |                 |                                                       |

|       | After Instruct |                                                                    |                                     |                                      | Q Cycle Activity:             |                                                                 |                 |                                                       |

|       | FSR2H          | = 0x0                                                              |                                     |                                      | Q1                            | Q2                                                              | Q3              | Q4                                                    |

|       | FSR2L          | = 0x/                                                              | AB                                  |                                      | Decode                        | Read<br>register 'f'                                            | Process<br>Data | Write W                                               |

|       |                |                                                                    |                                     |                                      | Example:                      | MOVF RI                                                         | EG, W           |                                                       |

|       |                |                                                                    |                                     |                                      | Before Instru                 | ction                                                           |                 |                                                       |

|       |                |                                                                    |                                     |                                      | REG<br>W                      | = 0x<br>= 0x                                                    |                 |                                                       |

After Instruction REG W

0x22 0x22

= =

| NEGF                 | Negate f                                                                                             |                                                       |                                                                     |                                                   |  |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------|--|--|--|--|

| Syntax:              | [ label ]                                                                                            | NEGF                                                  | f [,a]                                                              |                                                   |  |  |  |  |

| Operands:            | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                             | 5                                                     |                                                                     |                                                   |  |  |  |  |

| Operation:           | $(\overline{f}) + 1 \rightarrow f$                                                                   | :                                                     |                                                                     |                                                   |  |  |  |  |

| Status Affected:     | N, OV, C,                                                                                            | N, OV, C, DC, Z                                       |                                                                     |                                                   |  |  |  |  |

| Encoding:            | 0110                                                                                                 | 110a                                                  | ffff                                                                | ffff                                              |  |  |  |  |

| Description:         | Location 'f<br>complement<br>the data m<br>'0', the Ac<br>selected, o<br>If 'a' = 1, t<br>selected a | ent. The<br>nemory<br>cess Ba<br>overridir<br>hen the | result is p<br>location 'f<br>ank will be<br>ng the BS<br>bank will | blaced in<br>i'. If 'a' is<br>e<br>R value.<br>be |  |  |  |  |

| Words:               | 1                                                                                                    |                                                       |                                                                     |                                                   |  |  |  |  |

| Cycles:              | 1                                                                                                    |                                                       |                                                                     |                                                   |  |  |  |  |

| Q Cycle Activity:    |                                                                                                      |                                                       |                                                                     |                                                   |  |  |  |  |

| Q1                   | Q2                                                                                                   | Q                                                     | 3                                                                   | Q4                                                |  |  |  |  |

| Decode               | Read<br>register 'f'                                                                                 | Proce<br>Dat                                          |                                                                     | Write<br>gister 'f'                               |  |  |  |  |

| Example:             | NEGF R                                                                                               | REG, 1                                                |                                                                     |                                                   |  |  |  |  |

| Before Instru<br>REG | Before Instruction<br>REG = 0011 1010 [0x3A]                                                         |                                                       |                                                                     |                                                   |  |  |  |  |

| NOP               |        | No Operation |              |      |    |          |  |  |

|-------------------|--------|--------------|--------------|------|----|----------|--|--|

| Synt              | ax:    | [label] NOP  |              |      |    |          |  |  |

| Operands:         |        | None         | None         |      |    |          |  |  |

| Operation:        |        | No opera     | No operation |      |    |          |  |  |

| Status Affected:  |        | None         | None         |      |    |          |  |  |

| Encoding:         |        | 0000         | 0000         | 000  | 0  | 0000     |  |  |

|                   |        | 1111         | xxxx         | XXX  | x  | XXXX     |  |  |