Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 7x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1320-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                                                       |     |

|-------|---------------------------------------------------------------------------------------|-----|

| 2.0   | Oscillator Configurations                                                             | 10  |

| 3.0   | Power Managed Modes                                                                   |     |

| 4.0   | Reset                                                                                 |     |

| 5.0   | Memory Organization                                                                   | 39  |

| 6.0   | Flash Program Memory                                                                  | 55  |

| 7.0   | Data EEPROM Memory                                                                    | 64  |

| 8.0   | 8 x 8 Hardware Multiplier                                                             | 68  |

| 9.0   | Interrupts                                                                            |     |

| 10.0  | I/O Ports                                                                             | 83  |

| 11.0  | Timer0 Module                                                                         | 95  |

| 12.0  | Timer1 Module                                                                         | 98  |

| 13.0  | Timer2 Module                                                                         | 104 |

| 14.0  |                                                                                       |     |

| 15.0  |                                                                                       |     |

| 16.0  | Enhanced Addressable Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | 126 |

| 17.0  | 10-Bit Analog-to-Digital Converter (A/D) Module                                       | 149 |

| 18.0  | Low-Voltage Detect                                                                    | 160 |

| 19.0  | Special Features of the CPU                                                           | 165 |

| 20.0  | Instruction Set Summary                                                               | 184 |

| 21.0  | Development Support                                                                   | 226 |

| 22.0  |                                                                                       |     |

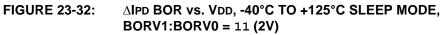

| 23.0  | DC and AC Characteristics Graphs and Tables                                           | 262 |

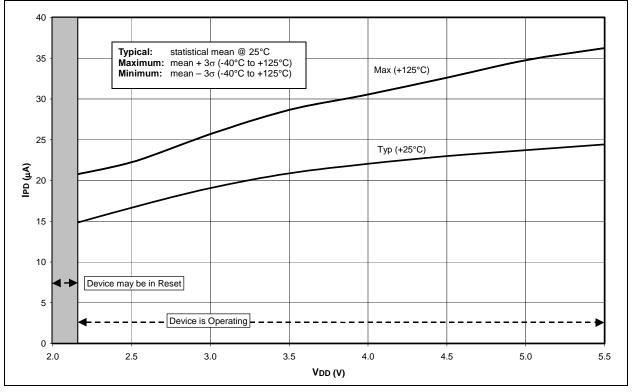

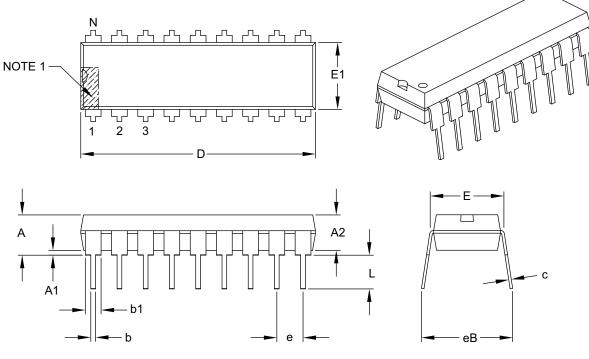

| 24.0  | Packaging Information                                                                 | 280 |

| Appe  | andix A: Revision History                                                             | 290 |

| Appe  | andix B: Device Differences                                                           | 290 |

| Appe  | andix C: Conversion Considerations                                                    | 291 |

| Appe  | andix D: Migration from Baseline to Enhanced Devices                                  | 291 |

|       | andix E: Migration from Mid-Range to Enhanced Devices                                 |     |

| Appe  | andix F: Migration from High-End to Enhanced Devices                                  | 292 |

|       | Microchip Web Site                                                                    |     |

| Custo | omer Change Notification Service                                                      | 293 |

| Custo | omer Support                                                                          | 293 |

| PIC1  | 8F1220/1320 Product Identification System                                             |     |

|                                                                                   | Pi                                                     | n Numb                 | er        | <b>D</b> ' 1              | D                                |                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------|--------------------------------------------------------|------------------------|-----------|---------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                          | 8 9 9 1/O TTL Digital I/O.<br>I Analog Analog input 4. |                        |           | Description               |                                  |                                                                                                                                                                                                   |

|                                                                                   | _                                                      |                        | _         |                           |                                  | PORTB is a bidirectional I/O port. PORTB can be softwa<br>programmed for internal weak pull-ups on all inputs.                                                                                    |

| RB0/AN4/INT0<br>RB0<br>AN4<br>INT0                                                | 8                                                      | 9                      | 9         |                           |                                  |                                                                                                                                                                                                   |

| RB1/AN5/TX/CK/INT1<br>RB1<br>AN5<br>TX<br>CK<br>INT1                              | 9                                                      | 10                     | 10        | I/O<br>I<br>0<br>I/O<br>I | TTL<br>Analog<br>—<br>ST<br>ST   | Digital I/O.<br>Analog input 5.<br>EUSART asynchronous transmit.<br>EUSART synchronous clock (see related RX/DT).<br>External interrupt 1.                                                        |

| RB2/P1B/INT2<br>RB2<br>P1B<br>INT2                                                | 17                                                     | 19                     | 23        | I/O<br>O<br>I             | TTL<br>—<br>ST                   | Digital I/O.<br>Enhanced CCP1/PWM output.<br>External interrupt 2.                                                                                                                                |

| RB3/CCP1/P1A<br>RB3<br>CCP1<br>P1A                                                | 18                                                     | 20                     | 24        | I/O<br>I/O<br>O           | TTL<br>ST                        | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM 1 output.<br>Enhanced CCP1/PWM output.                                                                                                       |

| RB4/AN6/RX/DT/KBI0<br>RB4<br>AN6<br>RX<br>DT<br>KBI0                              | 10                                                     | 11                     | 12        | I/O<br>I<br>I<br>I/O<br>I | TTL<br>Analog<br>ST<br>ST<br>TTL | Digital I/O.<br>Analog input 6.<br>EUSART asynchronous receive.<br>EUSART synchronous data (see related TX/CK).<br>Interrupt-on-change pin.                                                       |

| RB5/PGM/KBI1<br>RB5<br>PGM<br>KBI1                                                | 11                                                     | 12                     | 13        | I/O<br>I/O<br>I           | TTL<br>ST<br>TTL                 | Digital I/O.<br>Low-Voltage ICSP™ Programming enable pin.<br>Interrupt-on-change pin.                                                                                                             |

| RB6/PGC/T10S0/<br>T13CKI/P1C/KBI2<br>RB6<br>PGC<br>T10S0<br>T13CKI<br>P1C<br>KBI2 | 12                                                     | 13                     | 15        | I/O<br>I/O<br>I<br>O<br>I | TTL<br>ST<br>—<br>ST<br>—<br>TTL | Digital I/O.<br>In-Circuit Debugger and ICSP programming clock pin.<br>Timer1 oscillator output.<br>Timer1/Timer3 external clock output.<br>Enhanced CCP1/PWM output.<br>Interrupt-on-change pin. |

| RB7/PGD/T1OSI/<br>P1D/KBI3<br>RB7<br>PGD<br>T1OSI<br>P1D<br>KBI3                  | 13                                                     | 14                     | 16        | I/O<br>I/O<br>I<br>O<br>I | TTL<br>ST<br>CMOS<br>—<br>TTL    | Digital I/O.<br>In-Circuit Debugger and ICSP programming data pin.<br>Timer1 oscillator input.<br>Enhanced CCP1/PWM output.<br>Interrupt-on-change pin.                                           |

| Vss                                                                               | 5                                                      | 5, 6                   | 3, 5      | Р                         | —                                | Ground reference for logic and I/O pins.                                                                                                                                                          |

| Vdd                                                                               | 14                                                     | 15, 16                 | 17, 19    | Р                         |                                  | Positive supply for logic and I/O pins.                                                                                                                                                           |

| NC                                                                                | —                                                      | —                      | 18        | —                         | —                                | No connect.                                                                                                                                                                                       |

| ST = Sc                                                                           | hmitt Tri<br>Itput                                     | atible inp<br>gger inp | ut with ( |                           | evels                            | CMOS = CMOS compatible input or output<br>I = Input<br>P = Power                                                                                                                                  |

O = Output OD = Open-drain (no P diode to VDD)

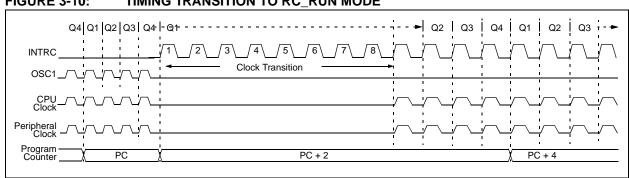

### 3.4.3 RC\_RUN MODE

In RC\_RUN mode, the CPU and peripherals are clocked from the internal oscillator block using the INTOSC multiplexer and the primary clock is shut down. When using the INTRC source, this mode provides the best power conservation of all the Run modes, while still executing code. It works well for user applications which are not highly timing sensitive, or do not require high-speed clocks at all times.

If the primary clock source is the internal oscillator block (either of the INTIO1 or INTIO2 oscillators), there are no distinguishable differences between PRI\_RUN and RC\_RUN modes during execution. However, a clock switch delay will occur during entry to and exit from RC\_RUN mode. Therefore, if the primary clock source is the internal oscillator block, the use of RC\_RUN mode is not recommended.

This mode is entered by clearing the IDLEN bit, setting SCS1 (SCS0 is ignored) and executing a SLEEP instruction. The IRCF bits may select the clock frequency before the SLEEP instruction is executed. When the clock source is switched to the INTOSC multiplexer (see Figure 3-10), the primary oscillator is shut down and the OSTS bit is cleared.

The IRCF bits may be modified at any time to immediately change the system clock speed. Executing a SLEEP instruction is not required to select a new clock frequency from the INTOSC multiplexer. Note: Caution should be used when modifying a single IRCF bit. If VDD is less than 3V, it is possible to select a higher clock speed than is supported by the low VDD. Improper device operation may result if the VDD/Fosc specifications are violated.

If the IRCF bits are all clear, the INTOSC output is not enabled and the IOFS bit will remain clear; there will be no indication of the current clock source. The INTRC source is providing the system clocks.

If the IRCF bits are changed from all clear (thus, enabling the INTOSC output), the IOFS bit becomes set after the INTOSC output becomes stable. Clocks to the system continue while the INTOSC source stabilizes, in approximately 1 ms.

If the IRCF bits were previously at a non-zero value before the SLEEP instruction was executed and the INTOSC source was already stable, the IOFS bit will remain set.

When a wake event occurs, the system continues to be clocked from the INTOSC multiplexer while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 3-8). When the clock switch is complete, the IOFS bit is cleared, the OSTS bit is set and the primary clock is providing the system clock. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

## FIGURE 3-10: TIMING TRANSITION TO RC\_RUN MODE

## 8.0 8 x 8 HARDWARE MULTIPLIER

## 8.1 Introduction

An 8 x 8 hardware multiplier is included in the ALU of the PIC18F1220/1320 devices. By making the multiply a hardware operation, it completes in a single instruction cycle. This is an unsigned multiply that gives a 16-bit result. The result is stored into the 16-bit product register pair (PRODH:PRODL). The multiplier does not affect any flags in the Status register. Making the 8 x 8 multiplier execute in a single cycle gives the following advantages:

- Higher computational throughput

- Reduces code size requirements for multiply algorithms

The performance increase allows the device to be used in applications previously reserved for Digital Signal Processors.

Table 8-1 shows a performance comparison between Enhanced devices using the single-cycle hardware multiply and performing the same function without the hardware multiply.

|                  |                           | Program           | Cycles | Time     |          |         |  |

|------------------|---------------------------|-------------------|--------|----------|----------|---------|--|

| Routine          | Multiply Method           | Memory<br>(Words) | (Max)  | @ 40 MHz | @ 10 MHz | @ 4 MHz |  |

|                  | Without hardware multiply | 13                | 69     | 6.9 μs   | 27.6 μs  | 69 μs   |  |

| 8 x 8 unsigned   | Hardware multiply         | 1                 | 1      | 100 ns   | 400 ns   | 1 μs    |  |

| 8 x 8 signed     | Without hardware multiply | 33                | 91     | 9.1 μs   | 36.4 μs  | 91 μs   |  |

|                  | Hardware multiply         | 6                 | 6      | 600 ns   | 2.4 μs   | 6 μs    |  |

|                  | Without hardware multiply | 21                | 242    | 24.2 μs  | 96.8 μs  | 242 μs  |  |

| 16 x 16 unsigned | Hardware multiply         | 28                | 28     | 2.8 μs   | 11.2 μs  | 28 μs   |  |

|                  | Without hardware multiply | 52                | 254    | 25.4 μs  | 102.6 μs | 254 μs  |  |

| 16 x 16 signed   | Hardware multiply         | 35                | 40     | 4 μs     | 16 μs    | 40 μs   |  |

## TABLE 8-1: PERFORMANCE COMPARISON

## 8.2 Operation

Example 8-1 shows the sequence to do an  $8 \times 8$  unsigned multiply. Only one instruction is required when one argument of the multiply is already loaded in the WREG register.

Example 8-2 shows the sequence to do an 8 x 8 signed multiply. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

## EXAMPLE 8-1: 8 x 8 UNSIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, W | ;                |

|-------|---------|------------------|

| MULWF | ARG2    | ; ARG1 * ARG2 -> |

|       |         | ; PRODH:PRODL    |

## EXAMPLE 8-2: 8 x 8 SIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, W  |                  |

|-------|----------|------------------|

| MULWF | ARG2     | ; ARG1 * ARG2 -> |

|       |          | ; PRODH:PRODL    |

| BTFSC | ARG2, SB | ; Test Sign Bit  |

| SUBWF | PRODH, F | ; PRODH = PRODH  |

|       |          | ; – ARG1         |

| MOVF  | ARG2, W  |                  |

| BTFSC | ARG1, SB | ; Test Sign Bit  |

| SUBWF | PRODH, F | ; PRODH = PRODH  |

|       |          | ; – ARG2         |

|       |          |                  |

| R/W-0/0                                                                                      | U-0                         | U-0                | R/W-0/0        | U-0              | R/W-0/0          | R/W-0/0  | U-0   |  |  |

|----------------------------------------------------------------------------------------------|-----------------------------|--------------------|----------------|------------------|------------------|----------|-------|--|--|

| OSCFIE                                                                                       | —                           | — EEIE             |                | —                | LVDIE            | TMR3IE   | —     |  |  |

| bit 7                                                                                        |                             |                    |                |                  |                  |          | bit 0 |  |  |

| Legend:                                                                                      |                             |                    |                |                  |                  |          |       |  |  |

| R = Readable                                                                                 | e bit                       | W = Writable       | bit            | U = Unimpler     | nented bit, read | l as '0' |       |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Reset |                             |                    |                |                  |                  |          |       |  |  |

| '1' = Bit is set '0' = Bit is cleared                                                        |                             |                    |                |                  |                  |          |       |  |  |

|                                                                                              |                             |                    |                |                  |                  |          |       |  |  |

| bit 7                                                                                        |                             | cillator Fail Inte | rrupt Enable b | pit              |                  |          |       |  |  |

|                                                                                              | 1 = Enabled<br>0 = Disabled |                    |                |                  |                  |          |       |  |  |

|                                                                                              |                             | -                  |                |                  |                  |          |       |  |  |

| bit 6-5                                                                                      | Unimpleme                   | nted: Read as '    | 0′             |                  |                  |          |       |  |  |

| bit 4                                                                                        | EEIE: Data E                | EEPROM/Flash       | Write Operati  | ion Interrupt Er | able bit         |          |       |  |  |

|                                                                                              | 1 = Enabled<br>0 = Disabled | =                  |                |                  |                  |          |       |  |  |

| bit 3                                                                                        | Unimpleme                   | nted: Read as '    | 0'             |                  |                  |          |       |  |  |

| bit 2                                                                                        | LVDIE: Low-                 | -Voltage Detect    | Interrupt Enat | ole bit          |                  |          |       |  |  |

| 1 = Enabled                                                                                  |                             |                    |                |                  |                  |          |       |  |  |

|                                                                                              | 0 = Disabled                |                    |                |                  |                  |          |       |  |  |

| bit 1                                                                                        | TMR3IE: TM                  | IR3 Overflow In    | terrupt Enable | e bit            |                  |          |       |  |  |

|                                                                                              | 1 = Enabled                 | -                  |                |                  |                  |          |       |  |  |

|                                                                                              | 0 = Disabled                | -                  |                |                  |                  |          |       |  |  |

| bit 0                                                                                        | Unimpleme                   | nted: Read as '    | 0'             |                  |                  |          |       |  |  |

|                                                                                              |                             |                    |                |                  |                  |          |       |  |  |

## REGISTER 9-7: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

#### 15.5.6 PROGRAMMABLE DEAD-BAND DELAY

In half-bridge applications where all power switches are modulated at the PWM frequency at all times, the power switches normally require more time to turn off than to turn on. If both the upper and lower power switches are switched at the same time (one turned on and the other turned off), both switches may be on for a short period of time until one switch completely turns off. During this brief interval, a very high current (shootthrough current) may flow through both power switches, shorting the bridge supply. To avoid this potentially destructive shoot-through current from flowing during switching, turning on either of the power switches is normally delayed to allow the other switch to completely turn off.

In the Half-Bridge Output mode, a digitally programmable dead-band delay is available to avoid shoot-through current from destroying the bridge power switches. The delay occurs at the signal transition from the non-active state to the active state. See Figure 15-6 for an illustration. The lower seven bits of the PWM1CON register (Register 15-2) sets the delay period in terms of microcontroller instruction cycles (TCY or 4 ToSC).

#### 15.5.7 ENHANCED PWM AUTO-SHUTDOWN

When the ECCP is programmed for any of the Enhanced PWM modes, the active output pins may be configured for auto-shutdown. Auto-shutdown immediately places the Enhanced PWM output pins into a defined shutdown state when a shutdown event occurs.

A shutdown event can be caused by the INT0, INT1 or INT2 pins (or any combination of these three sources). The auto-shutdown feature can be disabled by not selecting any auto-shutdown sources. The auto-shutdown sources to be used are selected using the ECCPAS2:ECCPAS0 bits (bits <6:4> of the ECCPAS register).

When a shutdown occurs, the output pins are asynchronously placed in their shutdown states, specified by the PSSAC1:PSSAC0 and PSSBD1:PSSBD0 bits (ECCPAS<3:0>). Each pin pair (P1A/P1C and P1B/P1D) may be set to drive high, drive low or be tristated (not driving). The ECCPASE bit (ECCPAS<7>) is also set to hold the Enhanced PWM outputs in their shutdown states.

The ECCPASE bit is set by hardware when a shutdown event occurs. If automatic restarts are not enabled, the ECCPASE bit is cleared by firmware when the cause of the shutdown clears. If automatic restarts are enabled, the ECCPASE bit is automatically cleared when the cause of the auto-shutdown has cleared. If the ECCPASE bit is set when a PWM period begins, the PWM outputs remain in their shutdown state for that entire PWM period. When the ECCPASE bit is cleared, the PWM outputs will return to normal operation at the beginning of the next PWM period.

**Note:** Writing to the ECCPASE bit is disabled while a shutdown condition is active.

### REGISTER 15-3: ECCPAS: ENHANCED CAPTURE/COMPARE/PWM/AUTO-SHUTDOWN CONTROL REGISTER

| R/W-0/0          | R/W-0/0                                                        | R/W-0/0                            | R/W-0/0       | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |  |  |

|------------------|----------------------------------------------------------------|------------------------------------|---------------|----------------|------------------|------------------|-------------|--|--|--|

| ECCPASE          | ECCPAS2                                                        | ECCPAS1                            | ECCPAS0       | PSSAC1         | PSSAC0           | PSSBD1           | PSSBD0      |  |  |  |

| bit 7            |                                                                |                                    |               |                |                  |                  | bit 0       |  |  |  |

|                  |                                                                |                                    |               |                |                  |                  |             |  |  |  |

| Legend:          |                                                                |                                    |               |                |                  |                  |             |  |  |  |

| R = Readable     | bit                                                            | W = Writable                       | bit           | U = Unimplen   | nented bit, read | as '0'           |             |  |  |  |

| u = Bit is unch  | anged                                                          | x = Bit is unkr                    | nown          | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |  |  |  |

| '1' = Bit is set |                                                                | '0' = Bit is clea                  | ared          |                |                  |                  |             |  |  |  |

|                  |                                                                |                                    |               |                |                  |                  |             |  |  |  |

| bit 7            |                                                                | CCP Auto-Shu                       |               | Status bit     |                  |                  |             |  |  |  |

|                  |                                                                | tputs are opera                    | 0             |                |                  | _                |             |  |  |  |

|                  |                                                                |                                    |               | outputs are in | n shutdown stat  | e                |             |  |  |  |

| bit 6            |                                                                | CCP Auto-Shu                       | tdown bit 2   |                |                  |                  |             |  |  |  |

|                  | 0 = INT0 pin has no effect<br>1 = INT0 pin low causes shutdown |                                    |               |                |                  |                  |             |  |  |  |

| bit 5            | •                                                              | CCP Auto-Shu                       |               |                |                  |                  |             |  |  |  |

| bit 5            | 0 = INT2 pin                                                   |                                    |               |                |                  |                  |             |  |  |  |

|                  | 1 = INT2 pin low causes shutdown                               |                                    |               |                |                  |                  |             |  |  |  |

| bit 4            | ECCPAS0: E                                                     | CCP Auto-Shu                       | tdown bit 0   |                |                  |                  |             |  |  |  |

|                  | 0 = INT1 pin                                                   | has no effect                      |               |                |                  |                  |             |  |  |  |

|                  | 1 = INT1 pin                                                   | low causes shu                     | Itdown        |                |                  |                  |             |  |  |  |

| bit 3-2          | PSSACn: Pir                                                    | ns A and C Shu                     | tdown State C | ontrol bits    |                  |                  |             |  |  |  |

|                  | 00 = Drive Pins A and C to '0'                                 |                                    |               |                |                  |                  |             |  |  |  |

|                  | 01 = Drive Pins A and C to '1'<br>1x = Pins A and C tri-state  |                                    |               |                |                  |                  |             |  |  |  |

| <b>h</b> #4.0    |                                                                |                                    |               | a stral bita   |                  |                  |             |  |  |  |

| bit 1-0          |                                                                | ns B and D Shu                     |               | ontrol dits    |                  |                  |             |  |  |  |

|                  |                                                                | ns B and D to '<br>ns B and D to ' | -             |                |                  |                  |             |  |  |  |

|                  | 1x = Pins B a                                                  |                                    | ±             |                |                  |                  |             |  |  |  |

| Name    | Bit 7                                             | Bit 6                                   | Bit 5    | Bit 4     | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|---------------------------------------------------|-----------------------------------------|----------|-----------|---------|--------|---------|---------|----------------------|---------------------------------|

| INTCON  | GIE/GIEH                                          | PEIE/GIEL                               | TMR0IE   | INT0IE    | RBIE    | TMR0IF | INT0IF  | RBIF    | 0000 000:            | c 0000 000u                     |

| RCON    | IPEN                                              | -                                       | -        | RI        | TO      | PD     | POR     | BOR     | 01 11q               | q 0q qquu                       |

| PIR1    | _                                                 | ADIF                                    | RCIF     | TXIF      | _       | CCP1IF | TMR2IF  | TMR1IF  | -000 -00             | 0 -000 -000                     |

| PIE1    | _                                                 | ADIE                                    | RCIE     | TXIE      | _       | CCP1IE | TMR2IE  | TMR1IE  | -000 -00             | 0 -000 -000                     |

| IPR1    | _                                                 | - ADIP RCIP TXIP - CCP1IP TMR2IP TMR1IP |          |           |         |        |         |         | -111 -11             | L -111 -111                     |

| TMR2    | Timer2 Mo                                         |                                         | 0000 000 | 0000 0000 |         |        |         |         |                      |                                 |

| PR2     | Timer2 Mo                                         | dule Period I                           | Register |           |         |        |         |         | 1111 111             | l 1111 1111                     |

| T2CON   | _                                                 | TOUTPS3                                 | TOUTPS2  | TOUTPS1   | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 000             | 0 -000 0000                     |

| TRISB   | PORTB Da                                          | ta Direction                            | Register |           |         |        |         |         | 1111 111             | l 1111 1111                     |

| CCPR1H  | Enhanced Capture/Compare/PWM Register 1 High Byte |                                         |          |           |         |        |         |         |                      | k uuuu uuuu                     |

| CCPR1L  | Enhanced Capture/Compare/PWM Register 1 Low Byte  |                                         |          |           |         |        |         |         |                      | k uuuu uuuu                     |

| CCP1CON | P1M1                                              | P1M0                                    | DC1B1    | DC1B0     | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 0000 000             | 0000 0000                       |

| ECCPAS  | ECCPASE                                           | ECCPAS2                                 | ECCPAS1  | ECCPAS0   | PSSAC1  | PSSAC0 | PSSBD1  | PSSBD0  | 0000 000             | 0000 0000                       |

| PWM1CON | PRSEN                                             | PDC6                                    | PDC5     | PDC4      | PDC3    | PDC2   | PDC1    | PDC0    | 0000 000             | ) uuuu uuuu                     |

| OSCCON  | IDLEN                                             | IRCF2                                   | IRCF1    | IRCF0     | OSTS    | IOFS   | SCS1    | SCS0    | 0000 qq0             | 000p qq00                       |

| TABLE 15-5: REGISTERS ASSOCIATED WITH ENHANCED PWM AND TIMER2 |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

$\label{eq:loss} \begin{array}{ll} \mbox{Legend:} & x = \mbox{unknown}, \mbox{u} = \mbox{unchanged}, \mbox{-} = \mbox{unimplemented}, \mbox{read as '0'}. \\ & \mbox{Shaded cells are not used by the ECCP module in Enhanced PWM mode}. \end{array}$

## 16.5 EUSART Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTA<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the RB1/AN5/TX/CK/INT1 pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any low-power mode.

### 16.5.1 EUSART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical, except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in the TXREG register.

- c) Flag bit, TXIF, will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit, TXIF, will now be set.

- e) If enable bit, TXIE, is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name    | Bit 7       | Bit 6          | Bit 5       | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------|----------------|-------------|-----------|-----------|--------|--------|--------|----------------------|---------------------------------|

| INTCON  | GIE/GIEH    | PEIE/GIEL      | TMR0IE      | INT0IE    | RBIE      | TMR0IF | INT0IF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1    | _           | ADIF           | RCIF        | TXIF      | —         | CCP1IF | TMR2IF | TMR1IF | -000 -000            | -000 -000                       |

| PIE1    | _           | ADIE           | RCIE        | TXIE      | —         | CCP1IE | TMR2IE | TMR1IE | -000 -000            | -000 -000                       |

| IPR1    |             | ADIP           | RCIP        | TXIP      | _         | CCP1IP | TMR2IP | TMR1IP | -111 -111            | -111 -111                       |

| RCSTA   | SPEN        | RX9            | SREN        | CREN      | ADDEN     | FERR   | OERR   | RX9D   | x000 000x            | 0000 000x                       |

| TXREG   | EUSART Tra  | ansmit Registe | er          |           |           |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA   | CSRC        | TX9            | TXEN        | SYNC      | SENDB     | BRGH   | TRMT   | TX9D   | 0000 0010            | 0000 0010                       |

| BAUDCTL | —           | RCIDL          | _           | SCKP      | BRG16     | _      | WUE    | ABDEN  | -1-1 0-00            | -1-1 0-00                       |

| SPBRGH  | Baud Rate G | Generator Reg  |             | 0000 0000 | 0000 0000 |        |        |        |                      |                                 |

| SPBRG   | Baud Rate G | Generator Reg  | ister Low E | Byte      |           |        |        |        | 0000 0000            | 0000 0000                       |

## TABLE 16-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

## REGISTER 17-1: ADCON0: A/D CONTROL REGISTER 0

| R/W-0/0 | R/W-0/0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|-----|---------|---------|---------|---------|---------|

| VCFG1   | VCFG0   | —   | CHS2    | CHS1    | CHS0    | GO/DONE | ADON    |

| bit 7   |         |     |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 VCFG<1:0>: Voltage Reference Configuration bits

|    | A/D VREF+      | A/D VREF-      |

|----|----------------|----------------|

| 00 | AVdd           | AVss           |

| 01 | External VREF+ | AVss           |

| 10 | AVdd           | External VREF- |

| 11 | External VREF+ | External VREF- |

bit 5 Unimplemented: Read as '0'

| bit 4-2 | CHS<2:0>: Analog Channel Select bits                                          |

|---------|-------------------------------------------------------------------------------|

|         | 000 = Channel 0 (AN0)                                                         |

|         | 001 = Channel 1 (AN1)                                                         |

|         | 010 = Channel 2 (AN2)                                                         |

|         | 011 = Channel 3 (AN3)                                                         |

|         | 100 = Channel 4 (AN4)                                                         |

|         | 101 = Channel 5 (AN5)                                                         |

|         | 110 = Channel 6 (AN6)                                                         |

|         | 111 = Unimplemented <sup>(1)</sup>                                            |

| bit 1   | GO/DONE: A/D Conversion Status bit                                            |

|         | When ADON = 1:                                                                |

|         | 1 = A/D conversion in progress                                                |

|         | 0 = A/D Idle                                                                  |

| bit 0   | ADON: A/D On bit                                                              |

|         | 1 = A/D converter module is enabled                                           |

|         | 0 = A/D converter module is disabled                                          |

|         | Performing a conversion on unimplemented channels returns full-scale results. |

|         |                                                                               |

Note 1: Performing a conversion on unimplemented channels returns full-scale results.

## 19.0 SPECIAL FEATURES OF THE CPU

PIC18F1220/1320 devices include several features intended to maximize system reliability, minimize cost through elimination of external components and offer code protection. These are:

- Oscillator Selection

- Resets:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor

- Two-Speed Start-up

- Code Protection

- ID Locations

- In-Circuit Serial Programming

Several oscillator options are available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. These are discussed in detail in **Section 2.0 "Oscillator Configurations"**.

A complete discussion of device Resets and interrupts is available in previous sections of this data sheet.

In addition to their Power-up and Oscillator Start-up Timers provided for Resets, PIC18F1220/1320 devices have a Watchdog Timer, which is either permanently enabled via the Configuration bits, or software controlled (if configured as disabled). The inclusion of an internal RC oscillator also provides the additional benefits of a Fail-Safe Clock Monitor (FSCM) and Two-Speed Start-up. FSCM provides for background monitoring of the peripheral clock and automatic switchover in the event of its failure. Two-Speed Start-up enables code to be executed almost immediately on start-up, while the primary clock source completes its start-up delays.

All of these features are enabled and configured by setting the appropriate Configuration register bits.

## **19.1 Configuration Bits**

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 300000h.

The user will note that address 300000h is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h-3FFFFh), which can only be accessed using table reads and table writes.

Programming the Configuration registers is done in a manner similar to programming the Flash memory. The EECON1 register WR bit starts a self-timed write to the Configuration register. In normal operation mode, a TBLWT instruction, with the TBLPTR pointing to the Configuration register, sets up the address and the data for the Configuration register write. Setting the WR bit starts a long write to the Configuration register. The Configuration registers are written a byte at a time. To write or erase a configuration cell, a TBLWT instruction can write a '1' or a '0' into the cell. For additional details on Flash programming, refer to Section 6.5 "Writing to Flash Program Memory".

| File    | Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Default/<br>Unprogrammed<br>Value |

|---------|-----------------------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------------------------|

| 300001h | CONFIG1H              | IESO  | FSCM  |       |        | FOSC3  | FOSC2  | FOSC1  | FOSC0  | 11 1111                           |

| 300002h | CONFIG2L              | _     |       |       |        | BORV1  | BORV0  | BOR    | PWRTEN | 1111                              |

| 300003h | CONFIG2H              | _     | _     | _     | WDTPS3 | WDTPS2 | WDTPS1 | WDTPS0 | WDT    | 1 1111                            |

| 300005h | CONFIG3H              | MCLRE |       |       |        |        | —      |        |        | 1                                 |

| 300006h | CONFIG4L              | DEBUG | _     | _     | _      | _      | LVP    | _      | STVR   | 11-1                              |

| 300008h | CONFIG5L              | —     |       |       |        |        | —      | CP1    | CP0    | 11                                |

| 300009h | CONFIG5H              | CPD   | CPB   | _     |        | _      | —      |        |        | 11                                |

| 30000Ah | CONFIG6L              | —     |       |       |        |        | _      | WRT1   | WRT0   | 11                                |

| 30000Bh | CONFIG6H              | WRTD  | WRTB  | WRTC  |        |        | -      |        |        | 111                               |

| 30000Ch | CONFIG7L              | —     |       |       |        |        | _      | EBTR1  | EBTR0  | 11                                |

| 30000Dh | CONFIG7H              | —     | EBTRB | _     | _      | _      | _      | _      |        | -1                                |

| 3FFFFEh | DEVID1 <sup>(1)</sup> | DEV2  | DEV1  | DEV0  | REV4   | REV3   | REV2   | REV1   | REV0   | xxxx xxxx(1)                      |

| 3FFFFFh | DEVID2 <sup>(1)</sup> | DEV10 | DEV9  | DEV8  | DEV7   | DEV6   | DEV5   | DEV4   | DEV3   | 0000 0111                         |

TABLE 19-1:CONFIGURATION BITS AND DEVICE IDS

**Legend:** x = unknown, u = unchanged, - = unimplemented. Shaded cells are unimplemented, read as '0'.

Note 1: See Register 19-12 for DEVID1 values. DEVID registers are read-only and cannot be programmed by the user.

#### 19.5.2 DATA EEPROM CODE PROTECTION

The entire data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of data EEPROM. WRTD inhibits external writes to data EEPROM. The CPU can continue to read and write data EEPROM, regardless of the protection bit settings.

#### 19.5.3 CONFIGURATION REGISTER PROTECTION

The Configuration registers can be write-protected. The WRTC bit controls protection of the Configuration registers. In normal execution mode, the WRTC bit is readable only. WRTC can only be written via ICSP or an external programmer.

## 19.6 ID Locations

Eight memory locations (20000h-200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are both readable and writable during normal execution through the TBLRD and TBLWT instructions, or during program/verify. The ID locations can be read when the device is code-protected.

## 19.7 In-Circuit Serial Programming

PIC18F1220/1320 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed (see Table 19-4).

| Note: | The Timer1 oscillator shares the T1OSI<br>and T1OSO pins with the PGD and PGC<br>pins used for programming and<br>debugging.                                                                                                                                                                             |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | When using the Timer1 oscillator, In-Circuit<br>Serial Programming (ICSP) may not<br>function correctly (high voltage or low<br>voltage), or the In-Circuit Debugger (ICD)<br>may not communicate with the controller.<br>As a result of using either ICSP or ICD, the<br>Timer1 crystal may be damaged. |

|       | If ICSP or ICD operations are required,<br>the crystal should be disconnected from<br>the circuit (disconnect either lead), or<br>installed after programming. The oscillator<br>loading capacitors may remain in-circuit<br>during ICSP or ICD operation.                                               |

#### TABLE 19-4: ICSP/ICD CONNECTIONS

| Signal | Pin                               | Notes                                     |

|--------|-----------------------------------|-------------------------------------------|

| PGD    | RB7/PGD/T1OSI/<br>P1D/KBI3        | Shared with T1OSC – protect crystal       |

| PGC    | RB6/PGC/T1OSO/<br>T13CKI/P1C/KBI2 | Shared with T1OSC – protect<br>crystal    |

| MCLR   | MCLR/Vpp/RA5                      |                                           |

| Vdd    | Vdd                               |                                           |

| Vss    | Vss                               |                                           |

| PGM    | RB5/PGM/KBI1                      | Optional – pull RB5 low is<br>LVP enabled |

## 19.8 In-Circuit Debugger

When the DEBUG bit in Configuration register, CONFIG4L, is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some resources are not available for general use. Table 19-5 shows which resources are required by the background debugger.

#### TABLE 19-5: DEBUGGER RESOURCES

| I/O pins:       | RB6, RB7  |

|-----------------|-----------|

| Stack:          | 2 levels  |

| Program Memory: | 512 bytes |

| Data Memory:    | 10 bytes  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, Vss, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip, or one of the third party development tool companies (see the note following **Section 19.7 "In-Circuit Serial Programming"** for more information).

## 20.0 INSTRUCTION SET SUMMARY

The PIC18 instruction set adds many enhancements to the previous PIC instruction sets, while maintaining an easy migration from these PIC instruction sets.

Most instructions are a single program memory word (16 bits), but there are three instructions that require two program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal operations

- Control operations

The PIC18 instruction set summary in Table 20-1 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 20-1 shows the opcode field descriptions.

Most byte-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator 'f' specifies which file register is to be used by the instruction.

The destination designator 'd' specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the WREG register. If 'd' is one, the result is placed in the file register specified in the instruction.

All **bit-oriented** instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator 'b' selects the number of the bit affected by the operation, while the file register designator 'f' represents the number of the file in which the bit is located.

The **literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The **control** instructions may use some of the following operands:

- A program memory address (specified by 'n')

- The mode of the CALL or RETURN instructions (specified by 's')

- The mode of the table read and table write instructions (specified by 'm')

- No operand required (specified by '—')

All instructions are a single word, except for three double-word instructions. These three instructions were made double-word instructions so that all the required information is available in these 32 bits. In the second word, the 4 MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP.

The double-word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 20-1 shows the general formats that the instructions can have.

All examples use the format 'nnh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

The Instruction Set Summary, shown in Table 20-1, lists the instructions recognized by the Microchip Assembler (MPASM<sup>TM</sup>). **Section 20.2** "Instruction **Set**" provides a description of each instruction.

## 20.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified and the result is stored according to either the instruction or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a "BCF PORTB, 1" instruction will read PORTB, clear bit 1 of the data, then write the result back to PORTB. The read operation would have the unintended result that any condition that sets the RBIF flag would be cleared. The R-M-W operation may also copy the level of an input pin to its corresponding output latch.

| DAW                 | Decimal A                                                                       | djust W Re                                                                                             | gister                                                                                    |

|---------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Syntax:             | [label] D                                                                       | WAW                                                                                                    |                                                                                           |

| Operands:           | None                                                                            |                                                                                                        |                                                                                           |

| Operation:          | (W<3:0>)<br>else                                                                | > 9] or [DC<br>+ 6 → W<3:0<br>→ W<3:0>;                                                                | -                                                                                         |

| Status Affected:    | (W<7:4>)<br>else                                                                | > 9] or [C =<br>+ 6 → W<7:4<br>→ W<7:4>;                                                               |                                                                                           |

| Encoding:           | 0000                                                                            | 0000 000                                                                                               | 00 0111                                                                                   |

| Description:        | DAW adjus<br>resulting fr<br>two variab<br>format) an<br>packed BC<br>may be se | ests the 8-bit work of the earlied les (each in produces a CD result. The toy DAW regard or to the DAW | value in W,<br>er addition of<br>backed BCD<br>a correct<br>e Carry bit<br>ardless of its |

| Words:              | 1                                                                               |                                                                                                        |                                                                                           |

| Cycles:             | 1                                                                               |                                                                                                        |                                                                                           |

| Q Cycle Activity:   |                                                                                 |                                                                                                        |                                                                                           |

| Q1                  | Q2                                                                              | Q3                                                                                                     | Q4                                                                                        |

| Decode              | Read<br>register W                                                              | Process<br>Data                                                                                        | Write<br>W                                                                                |

| Example 1:          | DAW                                                                             |                                                                                                        |                                                                                           |

| Before Instru       |                                                                                 |                                                                                                        |                                                                                           |

| W<br>C              | = 0xA5<br>= 0                                                                   |                                                                                                        |                                                                                           |

| DC                  | = 0                                                                             |                                                                                                        |                                                                                           |

| After Instruct<br>W | ion<br>= 0x05                                                                   |                                                                                                        |                                                                                           |

| C<br>DC             | = 1<br>= 0                                                                      |                                                                                                        |                                                                                           |

| Example 2:          | - 0                                                                             |                                                                                                        |                                                                                           |

| Before Instru       | iction                                                                          |                                                                                                        |                                                                                           |

| W                   | = 0xCE                                                                          |                                                                                                        |                                                                                           |

| C<br>DC             | = 0<br>= 0                                                                      |                                                                                                        |                                                                                           |

| After Instruct      | tion                                                                            |                                                                                                        |                                                                                           |

| W<br>C<br>DC        | = 0x34<br>= 1<br>= 0                                                            |                                                                                                        |                                                                                           |

|                     |                                                                                 |                                                                                                        |                                                                                           |

| DECF        |          | Decreme                                                                                             | ent f                                                                        |                                                                            |                                                                 |

|-------------|----------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------|

| Syntax:     |          | [ label ]                                                                                           | DECF f                                                                       | [,d [,a]]                                                                  |                                                                 |

| Operands:   |          | $0 \le f \le 25$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                  | 5                                                                            |                                                                            |                                                                 |

| Operation:  |          | (f) – 1 $\rightarrow$                                                                               | dest                                                                         |                                                                            |                                                                 |

| Status Affe | cted:    | C, DC, N                                                                                            | , OV, Z                                                                      |                                                                            |                                                                 |

| Encoding:   |          | 0000                                                                                                | 01da                                                                         | ffff                                                                       | ffff                                                            |

| Description |          | Decreme<br>the result<br>the result<br>'f' (defaul<br>Bank will<br>the BSR<br>bank will<br>BSR valu | is stored<br>is stored<br>t). If 'a' is<br>be seled<br>value. If<br>be seled | d in W. I<br>d back in<br>s '0', the<br>ted, ove<br>'a' = 1, f<br>ted as p | f 'd' is '1',<br>n register<br>e Access<br>erriding<br>then the |

| Words:      |          | 1                                                                                                   |                                                                              |                                                                            |                                                                 |

| Cycles:     |          | 1                                                                                                   |                                                                              |                                                                            |                                                                 |

| Q Cycle A   | ctivity: |                                                                                                     |                                                                              |                                                                            |                                                                 |

| Q           | 1        | Q2                                                                                                  | Q3                                                                           | }                                                                          | Q4                                                              |

| Dece        | ode      | Read<br>register 'f'                                                                                | Proce<br>Dat                                                                 |                                                                            | Write to estination                                             |

| Example:    | Inotr    | DECF                                                                                                | CNT                                                                          |                                                                            |                                                                 |

$\begin{array}{rrrr} Before Instruction \\ CNT & = & 0 \\ Z & = & 0 \\ \\ After Instruction \\ CNT & = & 0 \\ Z & = & 1 \end{array}$

| INCFSZ                          | Increment                                                                                                                                                                         | t f, skip if 0                                                                                                                                                                                                          |                                                                                                                                                      |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                         | [label]                                                                                                                                                                           | NCFSZ f[                                                                                                                                                                                                                | ,d [,a]]                                                                                                                                             |

| Operands:                       | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                             | 5                                                                                                                                                                                                                       |                                                                                                                                                      |

| Operation:                      | (f) + 1 $\rightarrow$ c<br>skip if resu                                                                                                                                           |                                                                                                                                                                                                                         |                                                                                                                                                      |

| Status Affected:                | None                                                                                                                                                                              |                                                                                                                                                                                                                         |                                                                                                                                                      |

| Encoding:                       | 0011                                                                                                                                                                              | 11da ffi                                                                                                                                                                                                                | f ffff                                                                                                                                               |

| Description:                    | incrementer<br>is placed in<br>is placed b<br>(default).<br>If the result<br>tion, which<br>discarded<br>instead, m<br>tion. If 'a' is<br>will be selevalue. If 'a<br>be selecter | nts of registe<br>ed. If 'd' is '0<br>n W. If 'd' is '<br>back in regist<br>it is '0', the n<br>n is already fe<br>and a NOP is<br>aking it a 2-c<br>s '0', the Acc<br>ected, overric<br>' = 1, then th<br>d as per the | ', the result<br>1', the result<br>er 'f'<br>ext instruc-<br>etched, is<br>s executed<br>cycle instruc-<br>cess Bank<br>ling the BSR<br>te bank will |