Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 25MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 7x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1320t-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

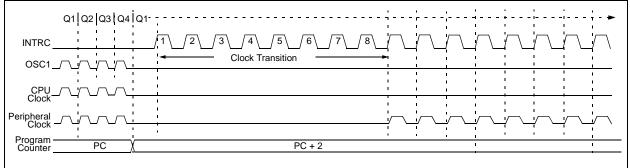

#### 3.3.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled, but the peripherals continue to be clocked from the internal oscillator block using the INTOSC multiplexer. This mode allows for controllable power conservation during Idle periods.

This mode is entered by setting the IDLEN bit, setting SCS1 (SCS0 is ignored) and executing a SLEEP instruction. The INTOSC multiplexer may be used to select a higher clock frequency by modifying the IRCF bits before executing the SLEEP instruction. When the clock source is switched to the INTOSC multiplexer (see Figure 3-7), the primary oscillator is shut down and the OSTS bit is cleared.

If the IRCF bits are set to a non-zero value (thus, enabling the INTOSC output), the IOFS bit becomes set after the INTOSC output becomes stable, in about 1 ms. Clocks to the peripherals continue while the INTOSC source stabilizes. If the IRCF bits were previously at a non-zero value before the SLEEP instruction was executed and the INTOSC source was already stable, the IOFS bit will remain set. If the IRCF bits are all clear, the INTOSC output is not enabled and the IOFS bit will remain clear; there will be no indication of the current clock source.

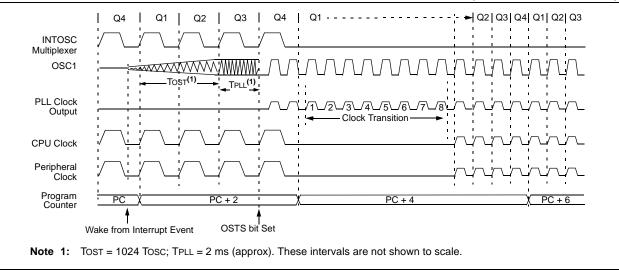

When a wake event occurs, the peripherals continue to be clocked from the INTOSC multiplexer. After a 10  $\mu$ s delay following the wake event, the CPU begins executing code, being clocked by the INTOSC multiplexer. The microcontroller operates in RC\_RUN mode until the primary clock becomes ready. When the primary clock becomes ready, a clock switchback to the primary clock occurs (see Figure 3-8). When the clock switch is complete, the IOFS bit is cleared, the OSTS bit is set and the primary clock is providing the system clock. The IDLEN and SCS bits are not affected by the wakeup. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

FIGURE 3-8: TIMING TRANSITION FOR WAKE FROM RC\_RUN MODE (RC\_RUN TO PRI\_RUN)

#### 3.4.4 EXIT TO IDLE MODE

An exit from a power managed Run mode to its corresponding Idle mode is executed by setting the IDLEN bit and executing a SLEEP instruction. The CPU is halted at the beginning of the instruction following the SLEEP instruction. There are no changes to any of the clock source status bits (OSTS, IOFS or T1RUN). While the CPU is halted, the peripherals continue to be clocked from the previously selected clock source.

#### 3.4.5 EXIT TO SLEEP MODE

An exit from a power managed Run mode to Sleep mode is executed by clearing the IDLEN and SCS1:SCS0 bits and executing a SLEEP instruction. The code is no different than the method used to invoke Sleep mode from the normal operating (full-power) mode.

The primary clock and internal oscillator block are disabled. The INTRC will continue to operate if the WDT is enabled. The Timer1 oscillator will continue to run, if enabled in the T1CON register (Register 12-1). All clock source Status bits are cleared (OSTS, IOFS and T1RUN).

#### 3.5 Wake from Power Managed Modes

An exit from any of the power managed modes is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power managed modes. The clocking subsystem actions are discussed in each of the power managed modes (see Sections 3.2 through 3.4).

| Note: | If application code is timing sensitive, it |

|-------|---------------------------------------------|

|       | should wait for the OSTS bit to become      |

|       | set before continuing. Use the interval     |

|       | during the low-power exit sequence          |

|       | (before OSTS is set) to perform timing      |

|       | insensitive "housekeeping" tasks.           |

Device behavior during Low-Power mode exits is summarized in Table 3-3.

#### 3.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit a power managed mode and resume fullpower operation. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set. On all exits from Low-Power mode by interrupt, code execution branches to the interrupt vector if the GIE/GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see Section 9.0 "Interrupts").

| TABLE 4-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |                       |      |                                    |                                                               |                                 |  |  |  |  |  |

|--------------------------------------------------------------------|-----------------------|------|------------------------------------|---------------------------------------------------------------|---------------------------------|--|--|--|--|--|

| Register                                                           | Applicable<br>Devices |      | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |  |  |  |  |

| BSR                                                                | 1220                  | 1320 | 0000                               | 0000                                                          | uuuu                            |  |  |  |  |  |

| INDF2                                                              | 1220                  | 1320 | N/A                                | N/A                                                           | N/A                             |  |  |  |  |  |

| POSTINC2                                                           | 1220                  | 1320 | N/A                                | N/A                                                           | N/A                             |  |  |  |  |  |

| POSTDEC2                                                           | 1220                  | 1320 | N/A                                | N/A                                                           | N/A                             |  |  |  |  |  |

| PREINC2                                                            | 1220                  | 1320 | N/A                                | N/A                                                           | N/A                             |  |  |  |  |  |

| PLUSW2                                                             | 1220                  | 1320 | N/A                                | N/A                                                           | N/A                             |  |  |  |  |  |

| FSR2H                                                              | 1220                  | 1320 | 0000                               | 0000                                                          | uuuu                            |  |  |  |  |  |

| FSR2L                                                              | 1220                  | 1320 | XXXX XXXX                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |  |  |

| STATUS                                                             | 1220                  | 1320 | x xxxx                             | u uuuu                                                        | u uuuu                          |  |  |  |  |  |

| TMR0H                                                              | 1220                  | 1320 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |  |  |  |  |  |

| TMR0L                                                              | 1220                  | 1320 | XXXX XXXX                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |  |  |

| TOCON                                                              | 1220                  | 1320 | 1111 1111                          | 1111 1111                                                     | uuuu uuuu                       |  |  |  |  |  |

| OSCCON                                                             | 1220                  | 1320 | 0000 q000                          | 0000 q000                                                     | uuuu qquu                       |  |  |  |  |  |

| LVDCON                                                             | 1220                  | 1320 | 00 0101                            | 00 0101                                                       | uu uuuu                         |  |  |  |  |  |

| WDTCON                                                             | 1220                  | 1320 | 0                                  | 0                                                             | u                               |  |  |  |  |  |

| RCON <sup>(4)</sup>                                                | 1220                  | 1320 | 01 11q0                            | 0q qquu                                                       | uu qquu                         |  |  |  |  |  |

| TMR1H                                                              | 1220                  | 1320 | XXXX XXXX                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |  |  |

| TMR1L                                                              | 1220                  | 1320 | XXXX XXXX                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |  |  |

| T1CON                                                              | 1220                  | 1320 | 0000 0000                          | u0uu uuuu                                                     | uuuu uuuu                       |  |  |  |  |  |

| TMR2                                                               | 1220                  | 1320 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |  |  |  |  |  |

| PR2                                                                | 1220                  | 1320 | 1111 1111                          | 1111 1111                                                     | 1111 1111                       |  |  |  |  |  |

| T2CON                                                              | 1220                  | 1320 | -000 0000                          | -000 0000                                                     | -uuu uuuu                       |  |  |  |  |  |

| ADRESH                                                             | 1220                  | 1320 | XXXX XXXX                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |  |  |

| ADRESL                                                             | 1220                  | 1320 | xxxx xxxx                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |  |  |

| ADCON0                                                             | 1220                  | 1320 | 00-0 0000                          | 00-0 0000                                                     | uu-u uuuu                       |  |  |  |  |  |

| ADCON1                                                             | 1220                  | 1320 | -000 0000                          | -000 0000                                                     | -uuu uuuu                       |  |  |  |  |  |

| ADCON2                                                             | 1220                  | 1320 | 0-00 0000                          | 0-00 0000                                                     | u-uu uuuu                       |  |  |  |  |  |

| CCPR1H                                                             | 1220                  | 1320 | XXXX XXXX                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |  |  |

| CCPR1L                                                             | 1220                  | 1320 | XXXX XXXX                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |  |  |  |

| CCP1CON                                                            | 1220                  | 1320 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |  |  |  |  |  |

| PWM1CON                                                            | 1220                  | 1320 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |  |  |  |  |  |

| ECCPAS                                                             | 1220                  | 1320 | 0000 0000                          | 0000 0000                                                     | uuuu uuuu                       |  |  |  |  |  |

| TABLE 4-3: | INITIALIZATION CONDITIONS FOR ALL REGISTERS ( | CONTINUED) |  |

|------------|-----------------------------------------------|------------|--|

|            |                                               |            |  |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 4-2 for Reset value for specific condition.

- **5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the Oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

- **6:** Bit 5 of PORTA is enabled if  $\overline{\text{MCLR}}$  is disabled.

#### 6.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and place it into data RAM. Table reads from program memory are performed one byte at a time.

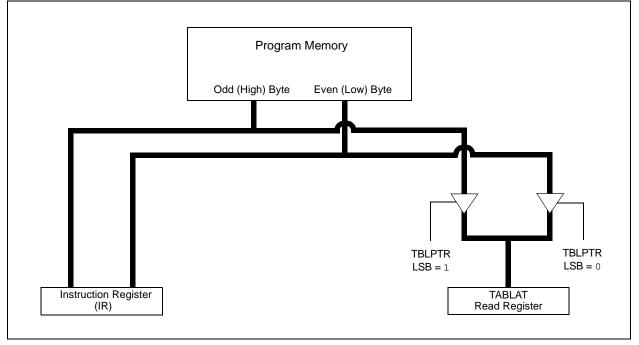

TBLPTR points to a byte address in program space. Executing a TBLRD instruction places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation. The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 6-4 shows the interface between the internal program memory and the TABLAT.

#### FIGURE 6-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 6-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW   | CODE_ADDR_UPPER | ; | Load TBLPTR with the base             |

|-----------|---------|-----------------|---|---------------------------------------|

|           | MOVWF   | TBLPTRU         | ; | address of the word                   |

|           | MOVLW   | CODE_ADDR_HIGH  |   |                                       |

|           | MOVWF   | TBLPTRH         |   |                                       |

|           | MOVLW   | CODE_ADDR_LOW   |   |                                       |

|           | MOVWF   | TBLPTRL         |   |                                       |

| READ_WORD |         |                 |   |                                       |

|           | TBLRD*+ | -               | ; | read into TABLAT and increment TBLPTR |

|           | MOVFW   | TABLAT          | ; | get data                              |

|           | MOVWF   | WORD_EVEN       |   |                                       |

|           | TBLRD*+ | -               | ; | read into TABLAT and increment TBLPTR |

|           | MOVFW   | TABLAT          | ; | get data                              |

|           | MOVWF   | WORD_ODD        |   |                                       |

|           |         |                 |   |                                       |

#### EXAMPLE 6-3: WRITING TO FLASH PROGRAM MEMORY

|            | MOVLW<br>MOVWF | D'64<br>COUNTER  | ; | number of bytes in erase block           |

|------------|----------------|------------------|---|------------------------------------------|

|            | MOVWF          |                  | ; | point to buffer                          |

|            | MOVWF          | FSR0H            |   |                                          |

|            | MOVLW          | BUFFER_ADDR_LOW  |   |                                          |

|            | MOVWF          | FSROL            |   |                                          |

|            | MOVLW          | CODE_ADDR_UPPER  | ; | Load TBLPTR with the base                |

|            | MOVWF          | TBLPTRU          | ; | address of the memory block              |

|            | MOVLW          | CODE_ADDR_HIGH   |   | -                                        |

|            | MOVWF          | TBLPTRH          |   |                                          |

|            | MOVLW          |                  | ; | 6 LSB = 0                                |

|            | MOVWF          | TBLPTRL          |   |                                          |

| READ_BLOCK | _              |                  |   |                                          |

|            | TBLRD*+        | F                | ; | read into TABLAT, and inc                |

|            | MOVF           | TABLAT, W        | ; | get data                                 |

|            | MOVWF          | POSTINC0         | ; | store data and increment FSR0            |

|            | DECFSZ         | COUNTER          | ; | done?                                    |

|            | GOTO           | READ_BLOCK       | ; | repeat                                   |

| MODIFY_WOR | D              |                  |   |                                          |

|            | MOVLW          | DATA_ADDR_HIGH   | ; | point to buffer                          |

|            | MOVWF          | FSROH            |   |                                          |

|            | MOVLW          | DATA_ADDR_LOW    |   |                                          |

|            | MOVWF          | FSROL            |   |                                          |

|            | MOVLW          | NEW_DATA_LOW     | ; | update buffer word and increment FSR0    |

|            | MOVWF          | POSTINC0         |   |                                          |

|            | MOVLW          | NEW_DATA_HIGH    | ; | update buffer word                       |

|            | MOVWF          | INDF0            |   |                                          |

| ERASE_BLOC | !K             |                  |   |                                          |

|            | MOVLW          | CODE_ADDR_UPPER  | ; | load TBLPTR with the base                |

|            | MOVWF          | TBLPTRU          | ; | address of the memory block              |

|            | MOVLW          | CODE_ADDR_HIGH   |   |                                          |

|            | MOVWF          | TBLPTRH          |   |                                          |

|            | MOVLW          | CODE_ADDR_LOW    | ; | 6 LSB = 0                                |

|            | MOVWF          | TBLPTRL          |   |                                          |

|            | BCF            | EECON1, CFGS     | ; | point to PROG/EEPROM memory              |

|            | BSF            | EECON1, EEPGD    | ; | point to FLASH program memory            |

|            | BSF            | EECON1, WREN     | ; | enable write to memory                   |

|            | BSF            | EECON1, FREE     | ; | enable Row Erase operation               |

|            | BCF            | INTCON, GIE      | ; | disable interrupts                       |

|            | MOVLW          | 55h              | ; | Required sequence                        |

|            | MOVWF          | EECON2           | ; | write 55H                                |

|            | MOVLW          | AAh              |   |                                          |

|            | MOVWF          | EECON2           | ; | write AAH                                |

|            | BSF            | EECON1, WR       | ; | start erase (CPU stall)                  |

|            | NOP            |                  |   |                                          |

|            | BSF            | INTCON, GIE      | ; | re-enable interrupts                     |

| WRITE_BUFF | 'ER_BACK       |                  |   |                                          |

|            | MOVLW          | 8                | ; | number of write buffer groups of 8 bytes |

|            | MOVWF          | COUNTER_HI       |   |                                          |

|            | MOVLW          | BUFFER_ADDR_HIGH | ; | point to buffer                          |

|            | MOVWF          | FSROH            |   |                                          |

|            | MOVLW          | BUFFER_ADDR_LOW  |   |                                          |

|            | MOVWF          | FSROL            |   |                                          |

| PROGRAM_LC | OP             |                  |   |                                          |

|            | MOVLW          | 8                | ; | number of bytes in holding register      |

|            | MOVWF          | COUNTER          |   |                                          |

|            |                |                  |   |                                          |

### 9.5 RCON Register

The RCON register contains bits used to determine the cause of the last Reset or wake-up from a low-power mode. RCON also contains the bit that enables interrupt priorities (IPEN).

#### REGISTER 9-10: RCON: RESET CONTROL REGISTER

| R/W-0 | U-0 | U-0 | R/W-1 | R-1 | R-1 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-----|-----|-------|-------|

| IPEN  | —   | _   | RI    | TO  | PD  | POR   | BOR   |

| bit 7 |     |     |       |     |     |       | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | <b>IPEN:</b> Interrupt Priority Enable bit<br>1 = Enable priority levels on interrupts<br>0 = Disable priority levels on interrupts (PIC16CXXX Compatibility mode) |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-5 | Unimplemented: Read as '0'                                                                                                                                         |

| bit 4   | RI: RESET Instruction Flag bit                                                                                                                                     |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

| bit 3   | TO: Watchdog Time-out Flag bit                                                                                                                                     |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

| bit 2   | PD: Power-down Detection Flag bit                                                                                                                                  |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

| bit 1   | POR: Power-on Reset Status bit                                                                                                                                     |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

| bit 0   | BOR: Brown-out Reset Status bit                                                                                                                                    |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

|         |                                                                                                                                                                    |

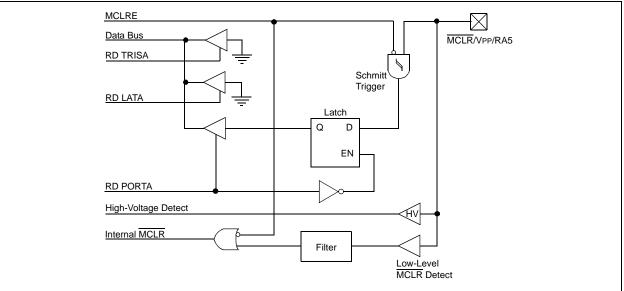

#### TABLE 10-1: PORTA FUNCTIONS

| Name          | Bit#  | Buffer | Function                                                                                                                                      |

|---------------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| RA0/AN0       | bit 0 | ST     | Input/output port pin or analog input.                                                                                                        |

| RA1/AN1/LVDIN | bit 1 | ST     | Input/output port pin, analog input or Low-Voltage Detect input.                                                                              |

| RA2/AN2/VREF- | bit 2 | ST     | Input/output port pin, analog input or VREF                                                                                                   |

| RA3/AN3/VREF+ | bit 3 | ST     | Input/output port pin, analog input or VREF+.                                                                                                 |

| RA4/T0CKI     | bit 4 | ST     | Input/output port pin or external clock input for Timer0.<br>Output is open-drain type.                                                       |

| MCLR/Vpp/RA5  | bit 5 | ST     | Master Clear input or programming voltage input (if MCLR is enabled); input only port pin or programming voltage input (if MCLR is disabled). |

| OSC2/CLKO/RA6 | bit 6 | ST     | OSC2, clock output or I/O pin.                                                                                                                |

| OSC1/CLKI/RA7 | bit 7 | ST     | OSC1, clock input or I/O pin.                                                                                                                 |

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

#### TABLE 10-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name   | Bit 7                 | Bit 6                 | Bit 5              | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-----------------------|-----------------------|--------------------|-------------------------------|-------|-------|-------|-------|----------------------|---------------------------------|

| PORTA  | RA7 <sup>(1)</sup>    | RA6 <sup>(1)</sup>    | RA5 <sup>(2)</sup> | RA4                           | RA3   | RA2   | RA1   | RA0   | xx0x 0000            | uu0u 0000                       |

| LATA   | LATA7 <sup>(1)</sup>  | LATA6 <sup>(1)</sup>  | —                  | LATA Data Output Register     |       |       |       |       | xx-x xxxx            | uu-u uuuu                       |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | _                  | PORTA Data Direction Register |       |       |       |       | 11-1 1111            | 11-1 1111                       |

| ADCON1 | _                     | PCFG6                 | PCFG5              | PCFG4                         | PCFG3 | PCFG2 | PCFG1 | PCFG0 | -000 0000            | -000 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

**Note 1:** RA7:RA6 and their associated latch and data direction bits are enabled as I/O pins based on oscillator configuration; otherwise, they are read as '0'.

2: RA5 is an input only if MCLR is disabled.

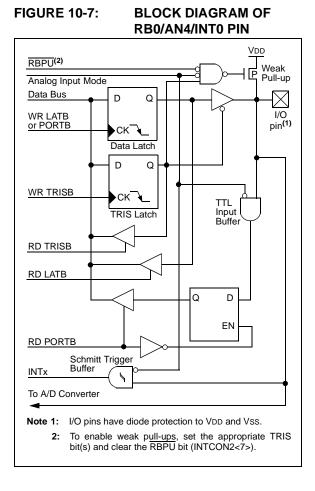

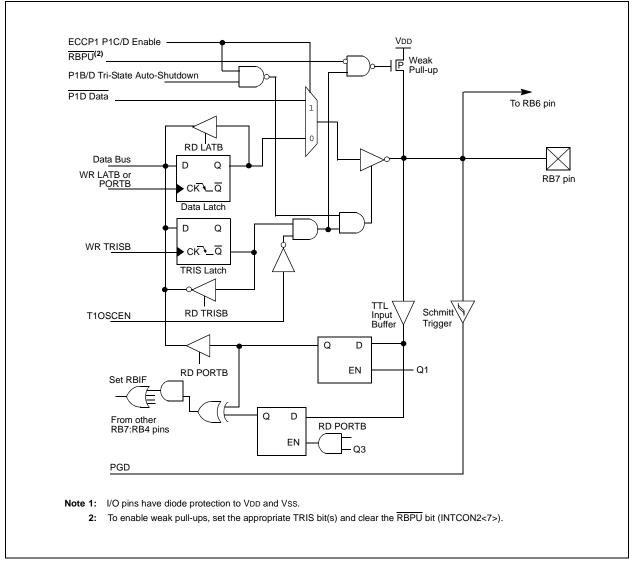

#### 10.2 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATB) is also memory mapped. Read-modify-write operations on the LATB register read and write the latched output value for PORTB.

| CLRF  | PORTB  | ; Initialize PORTB by   |

|-------|--------|-------------------------|

|       |        | ; clearing output       |

|       |        | ; data latches          |

| CLRF  | LATB   | ; Alternate method      |

|       |        | ; to clear output       |

|       |        | ; data latches          |

| MOVLW | 0x70   | ; Set RBO, RB1, RB4 as  |

| MOVWF | ADCON1 | ; digital I/O pins      |

| MOVLW | 0xCF   | ; Value used to         |

|       |        | ; initialize data       |

|       |        | ; direction             |

| MOVWF | TRISB  | ; Set RB<3:0> as inputs |

|       |        | ; RB<5:4> as outputs    |

|       |        | ; RB<7:6> as inputs     |

| 1     |        |                         |

Pins RB0-RB2 are multiplexed with INT0-INT2; pins RB0, RB1 and RB4 are multiplexed with A/D inputs; pins RB1 and RB4 are multiplexed with EUSART; and pins RB2, RB3, RB6 and RB7 are multiplexed with ECCP.

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit, RBPU (INTCON2<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Note: On a Power-on Reset, RB4:RB0 are configured as analog inputs by default and read as '0'; RB7:RB5 are configured as digital inputs.

Four of the PORTB pins (RB7:RB4) have an interrupton-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>). This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB (except with the MOVFF instruction). This will end the mismatch condition.

- b) Clear flag bit, RBIF.

A mismatch condition will continue to set flag bit, RBIF. Reading PORTB will end the mismatch condition and allow flag bit, RBIF, to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

#### 14.2 Timer1 Oscillator

The Timer1 oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. The oscillator is a lowpower oscillator rated for 32 kHz crystals. See **Section 12.2 "Timer1 Oscillator"** for further details.

#### 14.3 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR3 interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled/disabled by setting/clearing TMR3 Interrupt Enable bit, TMR3IE (PIE2<1>).

#### 14.4 Resetting Timer3 Using a CCP Trigger Output

If the CCP module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer3. See **Section 15.4.4** "**Special Event Trigger**" for more information.

| Note: | The special event triggers from the CCP |

|-------|-----------------------------------------|

|       | module will not set interrupt flag bit, |

|       | TMR3IF (PIR1<0>).                       |

Timer3 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer3 is running in Asynchronous Counter mode, this Reset operation may not work. In the event that a write to Timer3 coincides with a special event trigger from CCP1, the write will take precedence. In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer3.

| Name   | Bit 7                                                                      | Bit 6         | Bit 5        | Bit 4         | Bit 3         | Bit 2      | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------------------------------------------------------------------------|---------------|--------------|---------------|---------------|------------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE/<br>GIEH                                                               | PEIE/<br>GIEL | TMR0IE       | INTOIE        | RBIE          | TMR0IF     | INT0IF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR2   | OSCFIF                                                                     | —             | _            | EEIF          | _             | LVDIF      | TMR3IF | _      | 00 -00-              | 00 -00-                         |

| PIE2   | OSCFIE                                                                     | —             | _            | EEIE          | _             | LVDIE      | TMR3IE | _      | 00 -00-              | 00 -00-                         |

| IPR2   | OSCFIP                                                                     | —             | _            | EEIP          | _             | LVDIP      | TMR3IP | _      | 11 -11-              | 11 -11-                         |

| TMR3L  | Holding R                                                                  | egister for t | he Least Sig | gnificant Byt | e of the 16-b | it TMR3 Re | gister |        | xxxx xxxx            | uuuu uuuu                       |

| TMR3H  | Holding Register for the Most Significant Byte of the 16-bit TMR3 Register |               |              |               |               |            |        |        | xxxx xxxx            | uuuu uuuu                       |

| T1CON  | RD16                                                                       | T1RUN         | T1CKPS1      | T1CKPS0       | T1OSCEN       | T1SYNC     | TMR1CS | TMR10N | 0000 0000            | u0uu uuuu                       |

| T3CON  | RD16                                                                       | _             | T3CKPS1      | T3CKPS0       | T3CCP1        | T3SYNC     | TMR3CS | TMR3ON | 0-00 0000            | u-uu uuuu                       |

#### TABLE 14-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

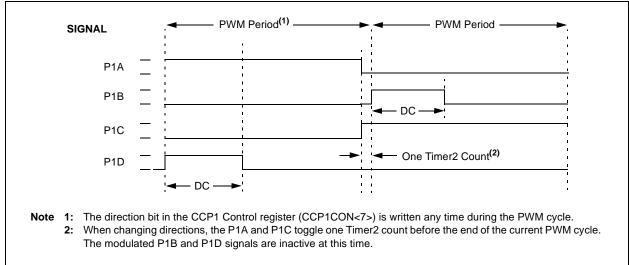

FIGURE 15-11: PWM DIRECTION CHANGE AT NEAR 100% DUTY CYCLE (ACTIVE-HIGH)

9.615

19.231

62.500

125.000

0.16

0.16

8.51

8.51

25

12

3

1

9615

—

\_

\_\_\_\_

-0.16

\_

\_

\_\_\_\_

9.6

19.2

57.6

115.2

|             |                       | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |                       |            |                             |

|-------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fosc                  | = 40.000                      | ) MHz                       | Fosc                  | = 20.000   | 0 MHz                       | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |

| (K)         | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 2.4         | —                     |                               | _                           | _                     | _          | _                           | 2.441                 | 1.73       | 255                         | 2403                  | -0.16      | 207                         |

| 9.6         | 9.766                 | 1.73                          | 255                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16       | 64                          | 9615                  | -0.16      | 51                          |

| 19.2        | 19.231                | 0.16                          | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73       | 31                          | 19230                 | -0.16      | 25                          |

| 57.6        | 58.140                | 0.94                          | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36      | 10                          | 55555                 | 3.55       | 8                           |

| 115.2       | 113.636               | -1.36                         | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51       | 4                           |                       | —          | —                           |

|             |                       |                               | S                           | YNC = 0, E            | BRGH = 1   | L, BRG16 =                  | 0                     |            |                             |                       |            |                             |

| BAUD        | Foso                  | c = 4.000                     | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |                       |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |                       |            |                             |

| 0.3         | —                     | _                             | —                           | —                     | _          | —                           | 300                   | -0.16      | 207                         |                       |            |                             |

| 1.2         | 1.202                 | 0.16                          | 207                         | 1201                  | -0.16      | 103                         | 1201                  | -0.16      | 51                          |                       |            |                             |

| 2.4         | 2.404                 | 0.16                          | 103                         | 2403                  | -0.16      | 51                          | 2403                  | -0.16      | 25                          |                       |            |                             |

12

\_\_\_\_

\_

\_

\_

\_

\_

—

\_

—

\_\_\_\_

#### TABLE 16-3: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|              |                       |            |                             |                       | SYNC              | = 0, BRGH                   | <b>I</b> = 0, BRG     | 16 = 1           |                             |                       |            |                             |

|--------------|-----------------------|------------|-----------------------------|-----------------------|-------------------|-----------------------------|-----------------------|------------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD         | Fosc = 40.000 MHz     |            | O MHz Fosc = 20.000 MHz     |                       | Fosc = 10.000 MHz |                             |                       | Fosc = 8.000 MHz |                             |                       |            |                             |

| RATE<br>(K)  | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | 0.300                 | 0.00       | 8332                        | 0.300                 | 0.02              | 4165                        | 0.300                 | 0.02             | 2082                        | 300                   | -0.04      | 1665                        |

| 1.2          | 1.200                 | 0.02       | 2082                        | 1.200                 | -0.03             | 1041                        | 1.200                 | -0.03            | 520                         | 1201                  | -0.16      | 415                         |

| 2.4          | 2.402                 | 0.06       | 1040                        | 2.399                 | -0.03             | 520                         | 2.404                 | 0.16             | 259                         | 2403                  | -0.16      | 207                         |

| 9.6          | 9.615                 | 0.16       | 259                         | 9.615                 | 0.16              | 129                         | 9.615                 | 0.16             | 64                          | 9615                  | -0.16      | 51                          |

| 19.2         | 19.231                | 0.16       | 129                         | 19.231                | 0.16              | 64                          | 19.531                | 1.73             | 31                          | 19230                 | -0.16      | 25                          |

| 57.6         | 58.140                | 0.94       | 42                          | 56.818                | -1.36             | 21                          | 56.818                | -1.36            | 10                          | 55555                 | 3.55       | 8                           |

| 115.2        | 113.636               | -1.36      | 21                          | 113.636               | -1.36             | 10                          | 125.000               | 8.51             | 4                           | _                     | _          | _                           |

|              |                       |            | S                           | YNC = 0, E            | BRGH = (          | ), <b>BRG16 =</b>           | 1                     |                  |                             |                       |            |                             |

| BAUD<br>RATE | FOSC = 4.00           |            | MHz                         | Fost                  | c = 2.000         | MHz                         | Fost                  | c = 1.000        | MHz                         |                       |            |                             |

| RAIE         | Actual                |            | SPBRG                       | Actual                |                   | SPBRG                       | Actual                |                  | SPBRG                       |                       |            |                             |

| BAUD  | FOSC = 4.000 WHZ      |            |                             | Fosc = 4.000 MHz Fosc = 2.000 MHz |            |                             |                       | Fosc = 1.000 MHz |                             |  |

|-------|-----------------------|------------|-----------------------------|-----------------------------------|------------|-----------------------------|-----------------------|------------------|-----------------------------|--|

| (K)   | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K)             | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 0.3   | 0.300                 | 0.04       | 832                         | 300                               | -0.16      | 415                         | 300                   | -0.16            | 207                         |  |

| 1.2   | 1.202                 | 0.16       | 207                         | 1201                              | -0.16      | 103                         | 1201                  | -0.16            | 51                          |  |

| 2.4   | 2.404                 | 0.16       | 103                         | 2403                              | -0.16      | 51                          | 2403                  | -0.16            | 25                          |  |

| 9.6   | 9.615                 | 0.16       | 25                          | 9615                              | -0.16      | 12                          | —                     | _                | _                           |  |

| 19.2  | 19.231                | 0.16       | 12                          | —                                 | _          | —                           | —                     | _                | _                           |  |

| 57.6  | 62.500                | 8.51       | 3                           | —                                 | _          | _                           | _                     | _                | _                           |  |

| 115.2 | 125.000               | 8.51       | 1                           | —                                 | _          | —                           | —                     | _                | —                           |  |

#### 16.3.6.2 Receiving a Break Sync

To receive a Break Sync:

- 1. Configure the EUSART for asynchronous transmit and receive. TXEN should remain clear. SPBRGH:SPBRG may be left as is.

- 2. Enable auto-wake-up. Set WUE.

- 3. Enable RXIF interrupts. Set RCIE, PEIE, GIE.

- 4. The controller may be placed in any power managed mode.

- 5. An RCIF will be generated at the beginning of the Break signal. When the interrupt is received, read RCREG to clear RCIF and discard. Allow the controller to return to PRI\_RUN mode.

- 6. Wait for the RX line to go high at the end of the Break signal. Wait for any of the following: WUE to clear automatically (poll), RB4/RX to go high (poll) or for RBIF to be set (poll or interrupt). If RBIF is used, check to be sure that RB4/RX is high before continuing.

- 7. Enable Auto-Baud Rate Detect. Set ABDEN.

- 8. Return from the interrupt. Allow the primary clock to start and stabilize (PRI\_RUN or PRI\_I-DLE).

- 9. When the next RCIF interrupt occurs, the received baud rate has been measured. Read RCREG to clear RCIF and discard. Check SPBRGH:SPBRG for a valid value. The EUSART is ready for normal communications. Return from the interrupt. Allow the primary clock to run (PRI\_RUN or PRI\_IDLE).

- 10. Process subsequent RCIF interrupts normally as in asynchronous reception. TXEN should now be set if transmissions are needed. TXIF and TXIE may be set if transmit interrupts are desired. Remain in PRI\_RUN or PRI\_IDLE until communications are complete. Clear TXEN and return to step 2.

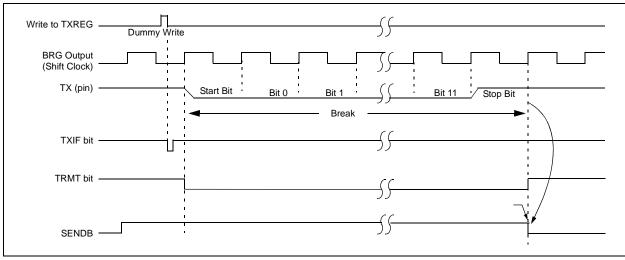

#### FIGURE 16-9: SEND BREAK CHARACTER SEQUENCE

#### 19.5.2 DATA EEPROM CODE PROTECTION

The entire data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of data EEPROM. WRTD inhibits external writes to data EEPROM. The CPU can continue to read and write data EEPROM, regardless of the protection bit settings.

#### 19.5.3 CONFIGURATION REGISTER PROTECTION

The Configuration registers can be write-protected. The WRTC bit controls protection of the Configuration registers. In normal execution mode, the WRTC bit is readable only. WRTC can only be written via ICSP or an external programmer.

#### 19.6 ID Locations

Eight memory locations (20000h-200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are both readable and writable during normal execution through the TBLRD and TBLWT instructions, or during program/verify. The ID locations can be read when the device is code-protected.

#### 19.7 In-Circuit Serial Programming

PIC18F1220/1320 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed (see Table 19-4).

| Note: | The Timer1 oscillator shares the T1OSI<br>and T1OSO pins with the PGD and PGC<br>pins used for programming and<br>debugging.                                                                                                                                                                             |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | When using the Timer1 oscillator, In-Circuit<br>Serial Programming (ICSP) may not<br>function correctly (high voltage or low<br>voltage), or the In-Circuit Debugger (ICD)<br>may not communicate with the controller.<br>As a result of using either ICSP or ICD, the<br>Timer1 crystal may be damaged. |

|       | If ICSP or ICD operations are required,<br>the crystal should be disconnected from<br>the circuit (disconnect either lead), or<br>installed after programming. The oscillator<br>loading capacitors may remain in-circuit<br>during ICSP or ICD operation.                                               |

#### TABLE 19-4: ICSP/ICD CONNECTIONS

| Signal | Pin                               | Notes                                     |

|--------|-----------------------------------|-------------------------------------------|

| PGD    | RB7/PGD/T1OSI/<br>P1D/KBI3        | Shared with T1OSC – protect crystal       |

| PGC    | RB6/PGC/T1OSO/<br>T13CKI/P1C/KBI2 | Shared with T1OSC – protect<br>crystal    |

| MCLR   | MCLR/Vpp/RA5                      |                                           |

| Vdd    | Vdd                               |                                           |

| Vss    | Vss                               |                                           |

| PGM    | RB5/PGM/KBI1                      | Optional – pull RB5 low is<br>LVP enabled |

#### 19.8 In-Circuit Debugger

When the DEBUG bit in Configuration register, CONFIG4L, is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some resources are not available for general use. Table 19-5 shows which resources are required by the background debugger.

#### TABLE 19-5: DEBUGGER RESOURCES

| I/O pins:       | RB6, RB7  |

|-----------------|-----------|

| Stack:          | 2 levels  |

| Program Memory: | 512 bytes |

| Data Memory:    | 10 bytes  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, Vss, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip, or one of the third party development tool companies (see the note following **Section 19.7 "In-Circuit Serial Programming"** for more information).

# PIC18F1220/1320

#### 20.2 **Instruction Set**

W = 0x25

| ADD               | DLW             | ADD liter                              | al to W           |     |    |          |  |  |  |

|-------------------|-----------------|----------------------------------------|-------------------|-----|----|----------|--|--|--|

| Synt              | tax:            | [label] A                              | DDLW              | k   |    |          |  |  |  |

| Ope               | rands:          | $0 \le k \le 25$                       | $0 \le k \le 255$ |     |    |          |  |  |  |

| Ope               | ration:         | (W) + k →                              | • W               |     |    |          |  |  |  |

| State             | us Affected:    | N, OV, C,                              | DC, Z             |     |    |          |  |  |  |

| Enc               | oding:          | 0000                                   | 1111              | kkk | k  | kkkk     |  |  |  |

| Des               | cription:       | The conte<br>8-bit litera<br>placed in | l 'k' and         |     |    |          |  |  |  |

| Wor               | ds:             | 1                                      | 1                 |     |    |          |  |  |  |

| Cycl              | les:            | 1                                      | 1                 |     |    |          |  |  |  |

| QC                | Cycle Activity: |                                        |                   |     |    |          |  |  |  |

|                   | Q1              | Q2                                     | Q3                | 3   |    | Q4       |  |  |  |

|                   | Decode          | Read<br>literal 'k'                    | Proce<br>Dat      |     | Wi | ite to W |  |  |  |

| <u>Exa</u>        | mple:           | ADDLW (                                | 0x15              |     |    |          |  |  |  |

|                   | Before Instru   | iction                                 |                   |     |    |          |  |  |  |

|                   | W =             | 0x10                                   |                   |     |    |          |  |  |  |

| After Instruction |                 |                                        |                   |     |    |          |  |  |  |

| Cycl        | es:            | 1    |

|-------------|----------------|------|

| QC          | ycle Activity: |      |

|             | Q1             |      |

|             | Decode         |      |

|             |                | reg  |

|             |                |      |

| <u>Exar</u> | nple:          | AI   |

|             | Defere Instru  | otio |

| ADDWF             | ADD W to                                            | o f                                                                              |                        |

|-------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|------------------------|

| Syntax:           | [ <i>label</i> ] Al                                 | DDWF f[,                                                                         | d [,a]]                |

| Operands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ | 5                                                                                |                        |

| Operation:        | (W) + (f) -                                         | → dest                                                                           |                        |

| Status Affected:  | N, OV, C,                                           | DC, Z                                                                            |                        |

| Encoding:         | 0010                                                | 01da ffi                                                                         | ff ffff                |

|                   | result is st<br>(default).                          | tored in W. If<br>tored back in<br>If 'a' is '0', the<br>be selected.<br>s used. | register 'f'<br>Access |

| Words:            | 1                                                   |                                                                                  |                        |

| Cycles:           | 1                                                   |                                                                                  |                        |

| Q Cycle Activity: |                                                     |                                                                                  |                        |

| Q1                | Q2                                                  | Q3                                                                               | Q4                     |

| Decode            | Read<br>register 'f'                                | Process<br>Data                                                                  | Write to destination   |

| Example:          | ADDWF                                               | REG, W                                                                           |                        |

| Before Instru     |                                                     |                                                                                  |                        |

| W                 | = 0x17                                              |                                                                                  |                        |

| W             | =     | 0x17 |

|---------------|-------|------|

| REG           | =     | 0xC2 |

| After Instruc | ction |      |

| W   | = | 0xD9 |

|-----|---|------|

| REG | = | 0xC2 |

# PIC18F1220/1320

| DECFSZ                                                | Decrement f, skip if 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                            |                 |  |  |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------|--|--|

| Syntax:                                               | [label] D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ECFSZ f[,                                                                  | d [,a]]         |  |  |

| Operands:                                             | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \left[0,1\right] \end{array}$ |                 |  |  |

| Operation:                                            | (f) – 1 $\rightarrow$ d<br>skip if resu                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                            |                 |  |  |

| Status Affected:                                      | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |                 |  |  |

| Encoding:                                             | 0010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11da fff                                                                   | f ffff          |  |  |

| Description:                                          | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in W. If 'd' is '1', the result<br>is placed back in register 'f'<br>(default).<br>If the result is '0', the next instruc-<br>tion, which is already fetched, is<br>discarded and a NOP is executed<br>instead, making it a 2-cycle instruc-<br>tion. If 'a' is '0', the Access Bank<br>will be selected, overriding the<br>BSR value. If 'a' = 1, then the bank<br>will be selected as per the BSR |                                                                            |                 |  |  |

| Words:                                                | value (defa<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ault).                                                                     |                 |  |  |

| Cycles:                                               | 1(2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |                 |  |  |

| Q Cycle Activity:                                     | Note: 3 cy<br>by a                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | a 2-word inst                                                              | _               |  |  |

| Decode                                                | Q2<br>Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Q3<br>Process                                                              | Q4<br>Write to  |  |  |

| Decode                                                | register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Data                                                                       | destination     |  |  |

| If skip:                                              | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                            |                 |  |  |

| Q1                                                    | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Q3                                                                         | Q4              |  |  |

| No                                                    | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | No                                                                         | No              |  |  |

| operation<br>If skip and follow                       | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | operation                                                                  | operation       |  |  |

| Q1                                                    | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Q3                                                                         | Q4              |  |  |

| No                                                    | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | No                                                                         | No              |  |  |

| operation                                             | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | operation                                                                  | operation       |  |  |

| No<br>operation                                       | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | No<br>operation                                                            | No<br>operation |  |  |

| Example:                                              | HERE<br>CONTINUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | GOTO LOOP                                                                  |                 |  |  |

| Before Instruction<br>PC = Address (HERE)             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                            |                 |  |  |