Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 7x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f1320t-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.0 POWER MANAGED MODES

The PIC18F1220/1320 devices offer a total of six operating modes for more efficient power management (see Table 3-1). These provide a variety of options for selective power conservation in applications where resources may be limited (i.e., battery powered devices).

There are three categories of power managed modes:

- Sleep mode

- Idle modes

- Run modes

These categories define which portions of the device are clocked and sometimes, what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or INTOSC multiplexer); the Sleep mode does not use a clock source.

The clock switching feature offered in other PIC18 devices (i.e., using the Timer1 oscillator in place of the primary oscillator) and the Sleep mode offered by all PIC<sup>®</sup> devices (where all system clocks are stopped) are both offered in the PIC18F1220/1320 devices (SEC\_RUN and Sleep modes, respectively). However, additional power managed modes are available that allow the user greater flexibility in determining what portions of the device are operating. The power managed modes are event driven; that is, some specific event must occur for the device to enter or (more particularly) exit these operating modes.

For PIC18F1220/1320 devices, the power managed modes are invoked by using the existing SLEEP instruction. All modes exit to PRI\_RUN mode when triggered by an interrupt, a Reset or a WDT time-out (PRI\_RUN mode is the normal full-power execution mode; the CPU and peripherals are clocked by the primary oscillator source). In addition, power managed Run modes may also exit to Sleep mode, or their corresponding Idle mode.

### 3.1 Selecting Power Managed Modes

Selecting a power managed mode requires deciding if the CPU is to be clocked or not and selecting a clock source. The IDLEN bit controls CPU clocking, while the SCS1:SCS0 bits select a clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 3-1.

#### 3.1.1 CLOCK SOURCES

The clock source is selected by setting the SCS bits of the OSCCON register (Register 2-2). Three clock sources are available for use in power managed Idle modes: the primary clock (as configured in Configuration Register 1H), the secondary clock (Timer1 oscillator) and the internal oscillator block. The secondary and internal oscillator block sources are available for the power managed modes (PRI\_RUN mode is the normal full-power execution mode; the CPU and peripherals are clocked by the primary oscillator source).

|          | osco         | CON Bits           | Module  | Clocking    |                                                                                                            |  |

|----------|--------------|--------------------|---------|-------------|------------------------------------------------------------------------------------------------------------|--|

| Mode     | IDLEN<br><7> | SCS1:SCS0<br><1:0> | CPU     | Peripherals | Available Clock and Oscillator Source                                                                      |  |

| Sleep    | 0            | 00                 | Off     | Off         | None – All clocks are disabled                                                                             |  |

| PRI_RUN  | 0            | 00                 | Clocked | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC, INTRC <sup>(1)</sup><br>This is the normal full-power execution mode. |  |

| SEC_RUN  | 0            | 01                 | Clocked | Clocked     | Secondary – Timer1 Oscillator                                                                              |  |

| RC_RUN   | 0            | 1x                 | Clocked | Clocked     | Internal Oscillator Block <sup>(1)</sup>                                                                   |  |

| PRI_IDLE | 1            | 00                 | Off     | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC                                                                        |  |

| SEC_IDLE | 1            | 01                 | Off     | Clocked     | Secondary – Timer1 Oscillator                                                                              |  |

| RC_IDLE  | 1            | 1x                 | Off     | Clocked     | Internal Oscillator Block <sup>(1)</sup>                                                                   |  |

#### TABLE 3-1: POWER MANAGED MODES

**Note 1:** Includes INTOSC and INTOSC postscaler, as well as the INTRC source.

### 3.4 Run Modes

If the IDLEN bit is clear when a SLEEP instruction is executed, the CPU and peripherals are both clocked from the source selected using the SCS1:SCS0 bits. While these operating modes may not afford the power conservation of Idle or Sleep modes, they do allow the device to continue executing instructions by using a lower frequency clock source. RC\_RUN mode also offers the possibility of executing code at a frequency greater than the primary clock.

Wake-up from a power managed Run mode can be triggered by an interrupt, or any Reset, to return to fullpower operation. As the CPU is executing code in Run modes, several additional exits from Run modes are possible. They include exit to Sleep mode, exit to a corresponding Idle mode and exit by executing a RESET instruction. While the device is in any of the power managed Run modes, a WDT time-out will result in a WDT Reset.

#### 3.4.1 PRI\_RUN MODE

The PRI\_RUN mode is the normal full-power execution mode. If the SLEEP instruction is never executed, the microcontroller operates in this mode (a SLEEP instruction is executed to enter all other power managed modes). All other power managed modes exit to PRI\_RUN mode when an interrupt or WDT time-out occur.

There is no entry to PRI\_RUN mode. The OSTS bit is set. The IOFS bit may be set if the internal oscillator block is the primary clock source (see **Section 2.7.1** "Oscillator Control Register").

#### 3.4.2 SEC\_RUN MODE

The SEC\_RUN mode is the compatible mode to the "clock switching" feature offered in other PIC18 devices. In this mode, the CPU and peripherals are clocked from the Timer1 oscillator. This gives users the option of lower power consumption while still using a high accuracy clock source.

SEC\_RUN mode is entered by clearing the IDLEN bit, setting SCS1:SCS0 = 01 and executing a SLEEP instruction. The system clock source is switched to the Timer1 oscillator (see Figure 3-9), the primary oscillator is shut down, the T1RUN bit (T1CON<6>) is set and the OSTS bit is cleared.

Note: The Timer1 oscillator should already be running prior to entering SEC\_RUN mode. If the T1OSCEN bit is not set when the SLEEP instruction is executed, the SLEEP instruction will be ignored and entry to SEC\_RUN mode will not occur. If the Timer1 oscillator is enabled, but not yet running, system clocks will be delayed until the oscillator has started; in such situations, initial oscillator operation is far from stable and unpredictable operation may result.

When a wake event occurs, the peripherals and CPU continue to be clocked from the Timer1 oscillator while the primary clock is started. When the primary clock becomes ready, a clock switchback to the primary clock occurs (see Figure 3-6). When the clock switch is complete, the T1RUN bit is cleared, the OSTS bit is set and the primary clock is providing the system clock. The IDLEN and SCS bits are not affected by the wake-up. The Timer1 oscillator continues to run.

Firmware can force an exit from SEC\_RUN mode. By clearing the T1OSCEN bit (T1CON<3>), an exit from SEC\_RUN back to normal full-power operation is triggered. The Timer1 oscillator will continue to run and provide the system clock, even though the T1OSCEN bit is cleared. The primary clock is started. When the primary clock becomes ready, a clock switchback to the primary clock occurs (see Figure 3-6). When the clock switch is cleared, the Timer1 oscillator is disabled, the T1RUN bit is cleared, the OSTS bit is set and the primary clock is providing the system clock. The IDLEN and SCS bits are not affected by the wake-up.

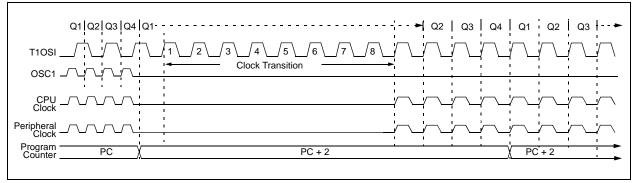

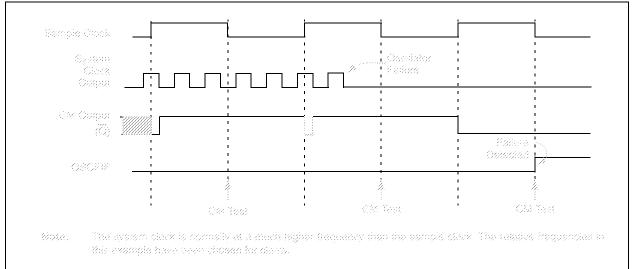

### FIGURE 3-9: TIMING TRANSITION FOR ENTRY TO SEC\_RUN MODE

### 6.3 Reading the Flash Program Memory

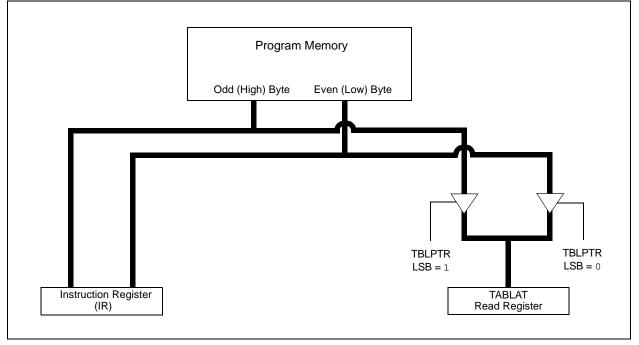

The TBLRD instruction is used to retrieve data from program memory and place it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing a TBLRD instruction places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation. The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 6-4 shows the interface between the internal program memory and the TABLAT.

## FIGURE 6-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 6-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW   | CODE_ADDR_UPPER | ; | Load TBLPTR with the base             |

|-----------|---------|-----------------|---|---------------------------------------|

|           | MOVWF   | TBLPTRU         | ; | address of the word                   |

|           | MOVLW   | CODE_ADDR_HIGH  |   |                                       |

|           | MOVWF   | TBLPTRH         |   |                                       |

|           | MOVLW   | CODE_ADDR_LOW   |   |                                       |

|           | MOVWF   | TBLPTRL         |   |                                       |

| READ_WORD |         |                 |   |                                       |

|           | TBLRD*+ | -               | ; | read into TABLAT and increment TBLPTR |

|           | MOVFW   | TABLAT          | ; | get data                              |

|           | MOVWF   | WORD_EVEN       |   |                                       |

|           | TBLRD*+ | -               | ; | read into TABLAT and increment TBLPTR |

|           | MOVFW   | TABLAT          | ; | get data                              |

|           | MOVWF   | WORD_ODD        |   |                                       |

|           |         |                 |   |                                       |

| R/W-1/1          | R/W-1/1                                  | U-0                                                                                                                                               | R/W-0/0                            | R/W-0/0         | U-0            | R/W-0/0           | R/W-0/0     |  |  |

|------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------|----------------|-------------------|-------------|--|--|

| INT2IP           | INT1IP                                   | —                                                                                                                                                 | INT2IE                             | INT1IE          | _              | INT2IF            | INT1IF      |  |  |

| bit 7            |                                          |                                                                                                                                                   |                                    |                 |                |                   | bit 0       |  |  |

| Legend:          |                                          |                                                                                                                                                   |                                    |                 |                |                   |             |  |  |

| R = Readable     | e bit                                    | W = Writable                                                                                                                                      | e bit                              | U = Unimplem    | ented bit, rea | d as '0'          |             |  |  |

| u = Bit is unc   | hanged                                   | x = Bit is unl                                                                                                                                    | known                              | •               |                | DR/Value at all o | ther Resets |  |  |

| '1' = Bit is set | t                                        | '0' = Bit is cl                                                                                                                                   | eared                              |                 |                |                   |             |  |  |

| bit 7            | INT2IP: INT2                             | 2 External Inte                                                                                                                                   | rrupt Priority bit                 | t               |                |                   |             |  |  |

|                  | 1 = High prid0 = Low prid                |                                                                                                                                                   |                                    |                 |                |                   |             |  |  |

| bit 6            | INT1IP: INT1                             | External Inte                                                                                                                                     | rrupt Priority bit                 | t               |                |                   |             |  |  |

|                  | 1 = High prid0 = Low prid                | ,                                                                                                                                                 |                                    |                 |                |                   |             |  |  |

| bit 5            | Unimplemer                               | nted: Read as                                                                                                                                     | '0'                                |                 |                |                   |             |  |  |

| bit 4            | INT2IE: INT2                             | 2 External Inte                                                                                                                                   | rrupt Enable bit                   | t               |                |                   |             |  |  |

|                  |                                          | the INT2 extent<br>the INT2 extent                                                                                                                |                                    |                 |                |                   |             |  |  |

| bit 3            | INT1IE: INT1                             | External Inte                                                                                                                                     | rrupt Enable bit                   | t               |                |                   |             |  |  |

|                  |                                          | the INT1 extent<br>the INT1 extent                                                                                                                |                                    |                 |                |                   |             |  |  |

| bit 2            | Unimplemer                               | nted: Read as                                                                                                                                     | '0'                                |                 |                |                   |             |  |  |

| bit 1            | INT2IF: INT2                             | 2 External Inte                                                                                                                                   | rrupt Flag bit                     |                 |                |                   |             |  |  |

|                  |                                          | <ul> <li>1 = The INT2 external interrupt occurred (must be cleared in software)</li> <li>0 = The INT2 external interrupt did not occur</li> </ul> |                                    |                 |                |                   |             |  |  |

| bit 0            | INT1IF: INT1 External Interrupt Flag bit |                                                                                                                                                   |                                    |                 |                |                   |             |  |  |

|                  |                                          |                                                                                                                                                   | rrupt occurred<br>rrupt did not oc | (must be cleare | d in software) | 1                 |             |  |  |

| Note: Int        | terrupt flag bits a                      | are set when a                                                                                                                                    | n interrupt                        |                 |                |                   |             |  |  |

### REGISTER 9-3: INTCON3: INTERRUPT CONTROL REGISTER 3

| Note: | Interrupt flag bits are set when an interrupt |

|-------|-----------------------------------------------|

|       | condition occurs, regardless of the state of  |

|       | its corresponding enable bit or the Global    |

|       | Interrupt Enable bit. User software should    |

|       | ensure the appropriate interrupt flag bits    |

|       | are clear prior to enabling an interrupt.     |

|       | This feature allows for software polling.     |

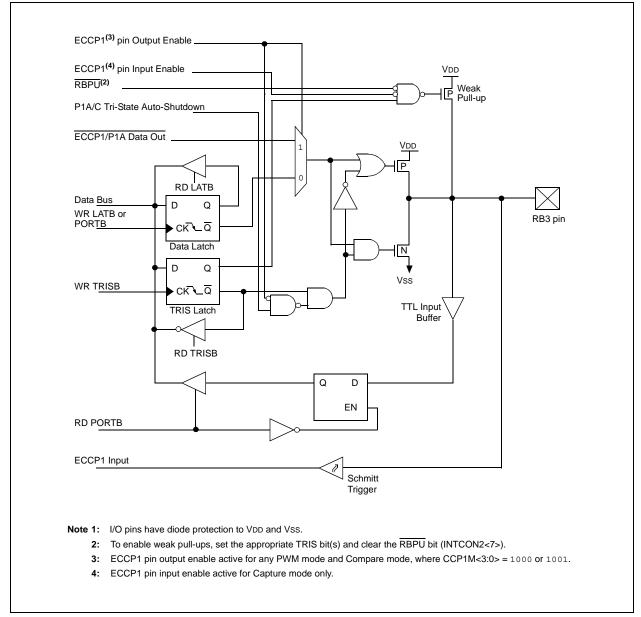

#### FIGURE 10-10: BLOCK DIAGRAM OF RB3/CCP1/P1A PIN

#### TABLE 10-3: PORTB FUNCTIONS

| Name                              | Bit#  | Buffer                                  | Function                                                                                                                                                                                 |

|-----------------------------------|-------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/AN4/INT0                      | bit 0 | TTL <sup>(1)</sup> /ST <sup>(2)</sup>   | Input/output port pin, analog input or external interrupt input 0.                                                                                                                       |

| RB1/AN5/TX/CK/INT1                | bit 1 | TTL <sup>(1)</sup> /ST <sup>(2)</sup>   | Input/output port pin, analog input, Enhanced USART<br>Asynchronous Transmit, Addressable USART<br>Synchronous Clock or external interrupt input 1.                                      |

| RB2/P1B/INT2                      | bit 2 | TTL <sup>(1)</sup> /ST <sup>(2)</sup>   | Input/output port pin or external interrupt input 2.<br>Internal software programmable weak pull-up.                                                                                     |

| RB3/CCP1/P1A                      | bit 3 | TTL <sup>(1)</sup> /ST <sup>(3)</sup>   | Input/output port pin or Capture1 input/Compare1 output/<br>PWM output. Internal software programmable weak pull-up.                                                                     |

| RB4/AN6/RX/DT/KBI0                | bit 4 | TTL <sup>(1)</sup> /ST <sup>(4)</sup>   | Input/output port pin (with interrupt-on-change), analog input,<br>Enhanced USART Asynchronous Receive or Addressable<br>USART Synchronous Data.                                         |

| RB5/PGM/KBI1                      | bit 5 | TTL <sup>(1)</sup> /ST <sup>(5)</sup>   | Input/output port pin (with interrupt-on-change).<br>Internal software programmable weak pull-up.<br>Low-Voltage ICSP™ enable pin.                                                       |

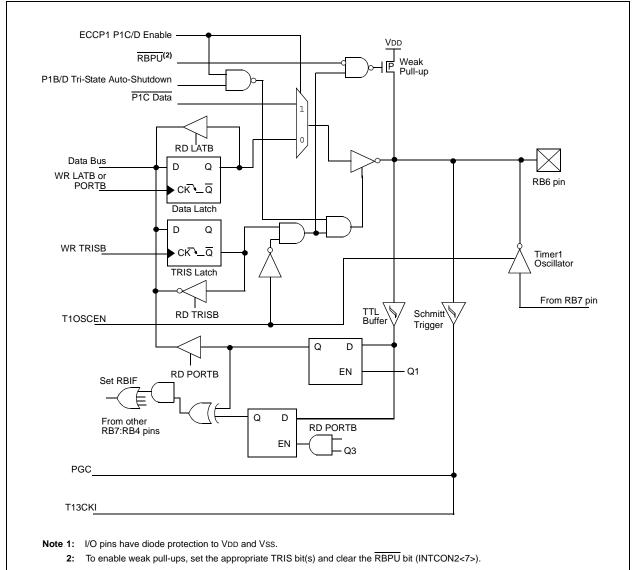

| RB6/PGC/T1OSO/T13CKI/<br>P1C/KBI2 | bit 6 | TTL <sup>(1)</sup> /ST <sup>(5,6)</sup> | Input/output port pin (with interrupt-on-change), Timer1/<br>Timer3 clock input or Timer1oscillator output.<br>Internal software programmable weak pull-up.<br>Serial programming clock. |

| RB7/PGD/T1OSI/P1D/KBI3            | bit 7 | TTL <sup>(1)</sup> /ST <sup>(5)</sup>   | Input/output port pin (with interrupt-on-change) or Timer1<br>oscillator input. Internal software programmable weak pull-up.<br>Serial programming data.                                 |

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

**Note 1:** This buffer is a TTL input when configured as a port input pin.

- **2:** This buffer is a Schmitt Trigger input when configured as the external interrupt.

- 3: This buffer is a Schmitt Trigger input when configured as the CCP1 input.

- 4: This buffer is a Schmitt Trigger input when used as EUSART receive input.

- 5: This buffer is a Schmitt Trigger input when used in Serial Programming mode.

- 6: This buffer is a TTL input when used as the T13CKI input.

#### TABLE 10-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Name    | Bit 7     | Bit 6        | Bit 5    | Bit 4   | Bit 3  | Bit 2  | Bit 1         | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-----------|--------------|----------|---------|--------|--------|---------------|--------|----------------------|---------------------------------|

| PORTB   | RB7       | RB6          | RB5      | RB4     | RB3    | RB2    | RB1           | RB0    | xxxd dddd            | uuuu uuuu                       |

| LATB    | LATB Data | Output Regi  | ster     |         |        |        |               |        | xxxx xxxx            | uuuu uuuu                       |

| TRISB   | PORTB Da  | ta Direction | Register |         |        |        |               |        | 1111 1111            | 1111 1111                       |

| INTCON  | GIE/GIEH  | PEIE/GIEL    | TMR0IE   | INT0IE  | RBIE   | TMR0IF | <b>INT0IF</b> | RBIF   | 0000 000x            | 0000 000u                       |

| INTCON2 | RBPU      | INTEDG0      | INTEDG1  | INTEDG2 | _      | TMR0IP | _             | RBIP   | 1111 -1-1            | 1111 -1-1                       |

| INTCON3 | INT2IP    | INT1IP       | —        | INT2IE  | INT1IE | _      | INT2IF        | INT1IF | 11-0 0-00            | 11-0 0-00                       |

| ADCON1  | —         | PCFG6        | PCFG5    | PCFG4   | PCFG3  | PCFG2  | PCFG1         | PCFG0  | -000 0000            | -000 0000                       |

$\label{eq:logend: Legend: Legend: u = unchanged, q = value depends on condition. Shaded cells are not used by PORTB.$

### 17.7 A/D Conversions

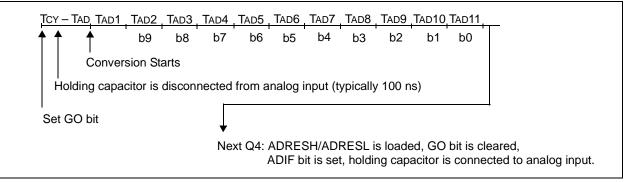

Figure 17-3 shows the operation of the A/D converter after the GO bit has been set and the ACQT2:ACQT0 bits are cleared. A conversion is started after the following instruction to allow entry into Low-Power Sleep mode before the conversion begins.

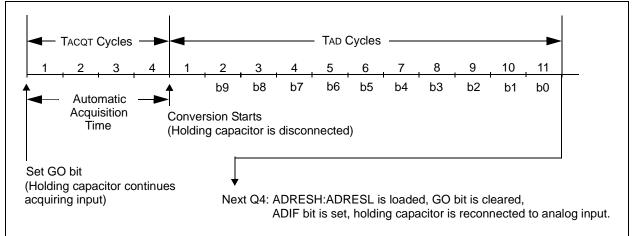

Figure 17-4 shows the operation of the A/D converter after the GO bit has been set and the ACQT2:ACQT0 bits are set to '010' and selecting a 4 TAD acquisition time before the conversion starts.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/ D conversion sample. This means the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers).

After the A/D conversion is completed or aborted, a 2 TAD wait is required before the next acquisition can be started. After this wait, acquisition on the selected channel is automatically started.

**Note:** The GO/DONE bit should **NOT** be set in the same instruction that turns on the A/D.

### FIGURE 17-3: A/D CONVERSION TAD CYCLES (Acqt<2:0> = 000, Tacq = 0)

#### FIGURE 17-4: A/D CONVERSION TAD CYCLES (Acqt<2:0> = 010, Tacq = 4 TaD)

| U-0              | U-0                          | U-0               | U-0                       | R/P-1          | R/P-1            | R/P-1              | R/P-1                 |  |

|------------------|------------------------------|-------------------|---------------------------|----------------|------------------|--------------------|-----------------------|--|

| _                | —                            | _                 | _                         | BORV1          | BORV0            | BOR <sup>(1)</sup> | PWRTEN <sup>(1)</sup> |  |

| bit 7            |                              |                   |                           |                |                  |                    | bit 0                 |  |

|                  |                              |                   |                           |                |                  |                    |                       |  |

| Legend:          |                              |                   |                           |                |                  |                    |                       |  |

| R = Readable b   | bit                          | W = Writable      | bit                       | U = Unimpler   | mented bit, read | as '0'             |                       |  |

| u = Bit is uncha | anged                        | x = Bit is unkn   | iown                      | -n/n = Value a | at POR and BOI   | R/Value at all o   | other Resets          |  |

| '1' = Bit is set |                              | '0' = Bit is clea | ared                      | P = Program    | mable bit        |                    |                       |  |

|                  |                              |                   |                           |                |                  |                    |                       |  |

| bit 7-4          | Unimplement                  | ted: Read as '    | כ'                        |                |                  |                    |                       |  |

| bit 3-2          | BORV<1:0>:                   | Brown-out Res     | et Voltage bit            | S              |                  |                    |                       |  |

|                  | 11 = Reserve                 |                   |                           |                |                  |                    |                       |  |

|                  | 10 = VBOR se<br>01 = VBOR se |                   |                           |                |                  |                    |                       |  |

|                  | 01 = VBOR Se<br>00 = VBOR Se |                   |                           |                |                  |                    |                       |  |

| bit 1            | BOR: Brown-                  | out Reset Enat    | ole bit <sup>(1)</sup>    |                |                  |                    |                       |  |

|                  | 1 = Brown-out Reset enabled  |                   |                           |                |                  |                    |                       |  |

|                  | 0 = Brown-out Reset disabled |                   |                           |                |                  |                    |                       |  |

| bit 0            | PWRTEN: Po                   | wer-up Timer B    | Enable bit <sup>(1)</sup> |                |                  |                    |                       |  |

|                  | 1 = PWRT disabled            |                   |                           |                |                  |                    |                       |  |

|                  | 0 = PWRT en                  | abled             |                           |                |                  |                    |                       |  |

### REGISTER 19-2: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

**Note 1:** The Power-up Timer is decoupled from Brown-out Reset, allowing these features to be independently controlled.

| R/P-1                             | U-0     | U-0               | U-0  | U-0                                                   | U-0 | U-0 | U-0   |  |

|-----------------------------------|---------|-------------------|------|-------------------------------------------------------|-----|-----|-------|--|

| MCLRE                             | —       | —                 | —    | —                                                     | —   | —   | —     |  |

| bit 7                             |         |                   |      |                                                       |     |     | bit 0 |  |

|                                   |         |                   |      |                                                       |     |     |       |  |

| Legend:                           | Legend: |                   |      |                                                       |     |     |       |  |

| R = Readable bit W = Writable bit |         |                   |      | U = Unimplemented bit, read as '0'                    |     |     |       |  |

| u = Bit is uncha                  | anged   | x = Bit is unkn   | nown | -n/n = Value at POR and BOR/Value at all other Resets |     |     |       |  |

| '1' = Bit is set                  |         | '0' = Bit is clea | ared | P = Programmable bit                                  |     |     |       |  |

### REGISTER 19-4: CONFIG3H: CONFIGURATION REGISTER 3 HIGH (BYTE ADDRESS 300005h)

| bit 7   | MCLRE: MCLR Pin Enable bit                                |

|---------|-----------------------------------------------------------|

|         | $1 = \overline{MCLR}$ pin enabled, RA5 input pin disabled |

|         | 0 = RA5 input pin enabled, MCLR disabled                  |

| bit 6-0 | Unimplemented: Read as '0'                                |

#### REGISTER 19-5: CONFIG4L: CONFIGURATION REGISTER 4 LOW (BYTE ADDRESS 300006h)

| R/P-1 | U-0 | U-0 | U-0 | U-0 | R/P-1 | U-0 | R/P-1 |

|-------|-----|-----|-----|-----|-------|-----|-------|

| DEBUG | —   | —   | _   |     | LVP   |     | STVR  |

| bit 7 |     |     |     |     |       |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | P = Programmable bit                                  |

| bit 7   | <b>DEBUG</b> : Background Debugger Enable bit (see note)                                                                                                                                         |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|         | <ul> <li>1 = Background debugger disabled, RB6 and RB7 configured as general purpose I/O pins</li> <li>0 = Background debugger enabled, RB6 and RB7 are dedicated to In-Circuit Debug</li> </ul> |  |  |  |

| bit 6-3 | Unimplemented: Read as '0'                                                                                                                                                                       |  |  |  |

| bit 2   | LVP: Low-Voltage ICSP Enable bit                                                                                                                                                                 |  |  |  |

|         | 1 = Low-Voltage ICSP enabled<br>0 = Low-Voltage ICSP disabled                                                                                                                                    |  |  |  |

| bit 1   | Unimplemented: Read as '0'                                                                                                                                                                       |  |  |  |

| bit 0   | STVR: Stack Full/Underflow Reset Enable bit                                                                                                                                                      |  |  |  |

|         | <ul><li>1 = Stack full/underflow will cause Reset</li><li>0 = Stack full/underflow will not cause Reset</li></ul>                                                                                |  |  |  |

**Note:** The Timer1 oscillator shares the T1OSI and T1OSO pins with the PGD and PGC pins used for programming and debugging.

When using the Timer1 oscillator, In-Circuit Serial Programming (ICSP) may not function correctly (high voltage or low voltage), or the In-Circuit Debugger (ICD) may not communicate with the controller. As a result of using either ICSP or ICD, the Timer1 crystal may be damaged.

If ICSP or ICD operations are required, the crystal should be disconnected from the circuit (disconnect either lead) or installed after programming. The oscillator loading capacitors may remain in-circuit during ICSP or ICD operation.

#### 19.4.2 EXITING FAIL-SAFE OPERATION

The Fail-Safe condition is terminated by either a device Reset, or by entering a power managed mode. On Reset, the controller starts the primary clock source specified in Configuration Register 1H (with any required start-up delays that are required for the oscillator mode, such as OST or PLL timer). The INTOSC multiplexer provides the system clock until the primary clock source becomes ready (similar to a Two-Speed Start-up). The clock system source is then switched to the primary clock (indicated by the OSTS bit in the OSCCON register becoming set). The Fail-Safe Clock Monitor then resumes monitoring the peripheral clock.

The primary clock source may never become ready during start-up. In this case, operation is clocked by the INTOSC multiplexer. The OSCCON register will remain in its Reset state until a power managed mode is entered.

Entering a power managed mode by loading the OSCCON register and executing a SLEEP instruction will clear the Fail-Safe condition. When the Fail-Safe condition is cleared, the clock monitor will resume monitoring the peripheral clock.

#### 19.4.3 FSCM INTERRUPTS IN POWER MANAGED MODES

As previously mentioned, entering a power managed mode clears the Fail-Safe condition. By entering a power managed mode, the clock multiplexer selects the clock source selected by the OSCCON register. Fail-Safe monitoring of the power managed clock source resumes in the power managed mode.

If an oscillator failure occurs during power managed operation, the subsequent events depend on whether or not the oscillator failure interrupt is enabled. If enabled (OSCFIF = 1), code execution will be clocked by the INTOSC multiplexer. An automatic transition back to the failed clock source will not occur.

If the interrupt is disabled, the device will not exit the power managed mode on oscillator failure. Instead, the device will continue to operate as before, but clocked by the INTOSC multiplexer. While in Idle mode, subsequent interrupts will cause the CPU to begin executing instructions while being clocked by the INTOSC multiplexer. The device will not transition to a different clock source until the Fail-Safe condition is cleared.

#### FIGURE 19-4: FSCM TIMING DIAGRAM

#### 20.2 **Instruction Set**

W = 0x25

| ADD          | DLW             | ADD literal to W                       |                          |     |    |          |

|--------------|-----------------|----------------------------------------|--------------------------|-----|----|----------|

| Synt         | tax:            | [label] A                              | [ <i>label</i> ] ADDLW k |     |    |          |

| Ope          | rands:          | $0 \le k \le 25$                       | 5                        |     |    |          |

| Operation:   |                 | (W) + k →                              | • W                      |     |    |          |

| State        | us Affected:    | N, OV, C,                              | DC, Z                    |     |    |          |

| Enc          | oding:          | 0000                                   | 1111                     | kkk | k  | kkkk     |

| Description: |                 | The conte<br>8-bit litera<br>placed in | l 'k' and                |     |    |          |

| Wor          | ds:             | 1                                      |                          |     |    |          |

| Cycl         | les:            | 1                                      | 1                        |     |    |          |

| QC           | Cycle Activity: |                                        |                          |     |    |          |

|              | Q1              | Q2                                     | Q3                       | 3   |    | Q4       |

|              | Decode          | Read<br>literal 'k'                    | Proce<br>Dat             |     | Wi | ite to W |

| Example:     |                 | ADDLW (                                | 0x15                     |     |    |          |

|              | Before Instru   | iction                                 |                          |     |    |          |

|              | W =             | 0x10                                   |                          |     |    |          |

|              | After Instruct  | ion                                    |                          |     |    |          |

| Cycl        | es:            | 1    |

|-------------|----------------|------|

| QC          | ycle Activity: |      |

|             | Q1             |      |

|             | Decode         |      |

|             |                | reg  |

|             |                |      |

| <u>Exar</u> | nple:          | AI   |

|             | Defere Instru  | otio |

| ADDWF             | ADD W to                                            | o f                                                                              |                        |

|-------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|------------------------|

| Syntax:           | [ <i>label</i> ] Al                                 | DDWF f[,                                                                         | d [,a]]                |

| Operands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ | 5                                                                                |                        |

| Operation:        | (W) + (f) -                                         | → dest                                                                           |                        |

| Status Affected:  | N, OV, C,                                           | DC, Z                                                                            |                        |

| Encoding:         | 0010                                                | 01da ffi                                                                         | ff ffff                |

|                   | result is st<br>(default).                          | tored in W. If<br>tored back in<br>If 'a' is '0', the<br>be selected.<br>s used. | register 'f'<br>Access |

| Words:            | 1                                                   |                                                                                  |                        |

| Cycles:           | 1                                                   |                                                                                  |                        |

| Q Cycle Activity: |                                                     |                                                                                  |                        |

| Q1                | Q2                                                  | Q3                                                                               | Q4                     |

| Decode            | Read<br>register 'f'                                | Process<br>Data                                                                  | Write to destination   |

| Example:          | ADDWF                                               | REG, W                                                                           |                        |

| Before Instru     |                                                     |                                                                                  |                        |

| W                 | = 0x17                                              |                                                                                  |                        |

| W             | =     | 0x17 |

|---------------|-------|------|

| REG           | =     | 0xC2 |

| After Instruc | ction |      |

| W   | = | 0xD9 |

|-----|---|------|

| REG | = | 0xC2 |

| ANDWF AND W with f |                                                                                                          |                                                                     |                                                             |                                                            |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------|--|--|

| Syntax:            | [label] A                                                                                                | [ <i>label</i> ] ANDWF f[,d[,a]]                                    |                                                             |                                                            |  |  |

| Operands:          | $0 \le f \le 255$                                                                                        | 5                                                                   |                                                             |                                                            |  |  |

|                    | u ∈ [0,1]<br>a ∈ [0,1]                                                                                   | d ∈ [0,1]<br>a ∈ [0,1]                                              |                                                             |                                                            |  |  |

| Operation:         | (W) .AND.                                                                                                | (f) $\rightarrow$ de                                                | est                                                         |                                                            |  |  |

| Status Affected:   | N, Z                                                                                                     |                                                                     |                                                             |                                                            |  |  |

| Encoding:          | 0001                                                                                                     | 01da                                                                | ffff                                                        | ffff                                                       |  |  |

| Description:       | The conter<br>register 'f'.<br>stored in V<br>stored bac<br>If 'a' is '0',<br>selected. I<br>not be over | If 'd' is '<br>V. If 'd' is<br>k in regi<br>the Acco<br>f 'a' is '1 | 0', the res '1', the<br>ster 'f' (d<br>ess Ban<br>', the BS | esult is<br>result is<br>default).<br>k will be<br>SR will |  |  |

| Words:             | 1                                                                                                        |                                                                     |                                                             |                                                            |  |  |

| Cycles:            | 1                                                                                                        |                                                                     |                                                             |                                                            |  |  |

| Q Cycle Activity:  |                                                                                                          |                                                                     |                                                             |                                                            |  |  |

| Q1                 | Q2                                                                                                       | Q3                                                                  |                                                             | Q4                                                         |  |  |

| Decode             | Read<br>register 'f'                                                                                     | Proces<br>Data                                                      |                                                             | Vrite to<br>stination                                      |  |  |

| Example:           | ANDWF                                                                                                    | REG, W                                                              | I                                                           |                                                            |  |  |

| Before Instru      | ction                                                                                                    |                                                                     |                                                             |                                                            |  |  |

| W<br>REG           | = 0x17<br>= 0xC2                                                                                         |                                                                     |                                                             |                                                            |  |  |

| After Instruct     | ion                                                                                                      |                                                                     |                                                             |                                                            |  |  |

| W<br>REG           | = 0x02<br>= 0xC2                                                                                         |                                                                     |                                                             |                                                            |  |  |

|                    |                                                                                                          |                                                                     |                                                             |                                                            |  |  |

| Suntava                       |                                                        | [label] D                                                                        | [/abe/] BC n                                                                                                                     |                                                           |  |  |

|-------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|

| Syntax:                       |                                                        |                                                                                  | [ <i>label</i> ] BC n                                                                                                            |                                                           |  |  |

| Operands:                     |                                                        | -128 ≤ n ≤                                                                       | $-128 \le n \le 127$                                                                                                             |                                                           |  |  |

| Operation:                    |                                                        |                                                                                  | if Carry bit is '1'<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                            |                                                           |  |  |

| Status Affected:              |                                                        | None                                                                             |                                                                                                                                  |                                                           |  |  |

| Encoding                      | g:                                                     | 1110                                                                             | 0010 nni                                                                                                                         | nn nnnn                                                   |  |  |

| Description:                  |                                                        | program w<br>The 2's co<br>added to t<br>have incre<br>instruction<br>PC + 2 + 2 | y bit is '1', th<br>vill branch.<br>mplement nu<br>he PC. Since<br>mented to fe<br>, the new ad<br>n. This instru<br>nstruction. | umber '2n'<br>e the PC wi<br>etch the new<br>dress will b |  |  |

| Words:                        |                                                        | 1                                                                                |                                                                                                                                  |                                                           |  |  |

| Words:                        |                                                        | 1                                                                                |                                                                                                                                  |                                                           |  |  |

| Words:<br>Cycles:             |                                                        | 1(2)                                                                             |                                                                                                                                  |                                                           |  |  |

| Cycles:                       | e Activity:                                            | 1(2)                                                                             |                                                                                                                                  |                                                           |  |  |

| Cycles:<br>Q Cycle            | •                                                      | 1(2)                                                                             | Q3                                                                                                                               | Q4                                                        |  |  |

| Cycles:<br>Q Cycle<br>If Jump | :                                                      | 1(2)                                                                             | Q3<br>Process<br>Data                                                                                                            |                                                           |  |  |

| Cycles:<br>Q Cycle<br>If Jump | :<br>Q1                                                | 1(2)<br>Q2<br>Read literal                                                       | Process                                                                                                                          | Q4<br>Write to P0<br>No                                   |  |  |

| Cycles:<br>Q Cycle<br>If Jump | :<br>Q1<br>Decode                                      | 1(2)<br>Q2<br>Read literal<br>'n'                                                | Process<br>Data                                                                                                                  | Write to PO                                               |  |  |

| Cycles:<br>Q Cycle<br>If Jump | Q1<br>Decode<br>No<br>Deration                         | 1(2)<br>Q2<br>Read literal<br>'n'<br>No                                          | Process<br>Data<br>No                                                                                                            | Write to PO                                               |  |  |

| Cycles:<br>Q Cycle<br>If Jump | Q1<br>Decode<br>No<br>Deration                         | 1(2)<br>Q2<br>Read literal<br>'n'<br>No                                          | Process<br>Data<br>No                                                                                                            | Write to PO                                               |  |  |

| Cycles:<br>Q Cycle<br>If Jump | Calleration                                            | 1(2)<br>Q2<br>Read literal<br>'n'<br>No<br>operation                             | Process<br>Data<br>No<br>operation                                                                                               | Write to PO<br>No<br>operation<br>Q4<br>No                |  |  |

| Cycles:<br>Q Cycle<br>If Jump | Q1<br>Decode<br>No<br>peration<br>Imp:<br>Q1           | 1(2)<br>Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2<br>Read literal       | Process<br>Data<br>No<br>operation<br>Q3<br>Process                                                                              | Write to PO<br>No<br>operation<br>Q4                      |  |  |

| Cycles:<br>Q Cycle<br>If Jump | Q1<br>Decode<br>No<br>Decation<br>Imp:<br>Q1<br>Decode | 1(2)<br>Q2<br>Read literal<br>'n'<br>No<br>operation<br>Q2<br>Read literal       | Process<br>Data<br>No<br>operation<br>Q3<br>Process                                                                              | Write to PO<br>No<br>operation<br>Q4<br>No                |  |  |

| fter Instruction |   |                    |

|------------------|---|--------------------|

| If Carry         | = | 1;                 |

| PC               | = | address (JUMP)     |

| If Carry         | = | 0;                 |

| PC               | = | address (HERE + 2) |

| RCA   | LL             | Relative (                                                                                   | Relative Call                                                                                                                                                                                                                                                                                                                  |             |  |  |

|-------|----------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| Synt  | ax:            | [ <i>label</i> ] R                                                                           | [ <i>label</i> ] RCALL n                                                                                                                                                                                                                                                                                                       |             |  |  |

| Ope   | rands:         | -1024 ≤ n                                                                                    | $-1024 \le n \le 1023$                                                                                                                                                                                                                                                                                                         |             |  |  |

| Ope   | ration:        | . ,                                                                                          | $(PC) + 2 \rightarrow TOS,$<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                                                  |             |  |  |

| Statu | us Affected:   | None                                                                                         |                                                                                                                                                                                                                                                                                                                                |             |  |  |

| Enco  | oding:         | 1101                                                                                         | 1nnn nn                                                                                                                                                                                                                                                                                                                        | nn nnnn     |  |  |

| Dest  | cription:      | from the c<br>return add<br>onto the s<br>compleme<br>Since the<br>to fetch the<br>address w | Subroutine call with a jump up to 1K from the current location. First, return address (PC + 2) is pushed onto the stack. Then, add the 2's complement number '2n' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is a 2-cycle instruction. |             |  |  |

| Wor   | ds:            | 1                                                                                            | 1                                                                                                                                                                                                                                                                                                                              |             |  |  |

| Cycl  | es:            | 2                                                                                            | 2                                                                                                                                                                                                                                                                                                                              |             |  |  |

| QC    | ycle Activity: |                                                                                              |                                                                                                                                                                                                                                                                                                                                |             |  |  |

|       | Q1             | Q2                                                                                           | Q3                                                                                                                                                                                                                                                                                                                             | Q4          |  |  |

|       | Decode         | Read literal<br>'n'                                                                          | Process<br>Data                                                                                                                                                                                                                                                                                                                | Write to PC |  |  |

| RES               | ET           | Reset         |                                                                  |       |          |  |

|-------------------|--------------|---------------|------------------------------------------------------------------|-------|----------|--|

| Synt              | ax:          | [ label ]     | RESET                                                            |       |          |  |

| Ope               | rands:       | None          |                                                                  |       |          |  |

| Operation:        |              |               | Reset all registers and flags that are affected by a MCLR Reset. |       |          |  |

| State             | us Affected: | All           |                                                                  |       |          |  |

| Encoding:         |              | 0000          | 0000                                                             | 1111  | 1111     |  |

| Description:      |              | This instruet |                                                                  |       |          |  |

| Wor               | ds:          | 1             |                                                                  |       |          |  |

| Cycl              | es:          | 1             |                                                                  |       |          |  |

| Q Cycle Activity: |              |               |                                                                  |       |          |  |

|                   | Q1           | Q2            | Q3                                                               |       | Q4       |  |

|                   | Decode       | Start         | No                                                               |       | No       |  |

|                   |              | Reset         | operat                                                           | ion o | peration |  |

|                   |              |               |                                                                  |       |          |  |

Example: RESET

| After Instruction |             |

|-------------------|-------------|

| Registers =       | Reset Value |

| Flags* =          | Reset Value |

Example: HERE RCALL Jump

Push PC to stack

No

operation

No

operation

No

operation

**Before Instruction**

No

operation

PC = Address (HERE) After Instruction PC = Address (Jump) TOS = Address (HERE + 2)

| RLNCF                                 | Rotate Lo                                                                                  | Rotate Left f (no carry)                                                                                                                                                                                                                                                                                                                                     |  |                      |  |

|---------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----------------------|--|

| Syntax:                               | [ label ]                                                                                  | [ label ] RLNCF f [,d [,a]]                                                                                                                                                                                                                                                                                                                                  |  |                      |  |

| Operands:                             | 0 ≤ f ≤ 25<br>d ∈ [0,1]<br>a ∈ [0,1]                                                       |                                                                                                                                                                                                                                                                                                                                                              |  |                      |  |

| Operation:                            |                                                                                            | $(f < n >) \rightarrow dest < n + 1 >,$<br>$(f < 7 >) \rightarrow dest < 0 >$                                                                                                                                                                                                                                                                                |  |                      |  |

| Status Affected:                      | N, Z                                                                                       | N, Z                                                                                                                                                                                                                                                                                                                                                         |  |                      |  |

| Encoding:                             | 0100                                                                                       | 0100 01da ffff ffff                                                                                                                                                                                                                                                                                                                                          |  |                      |  |

| Description:                          | rotated or<br>the result<br>the result<br>'f' (defaul<br>Bank will<br>the BSR<br>bank will | The contents of register 'f' are<br>rotated one bit to the left. If 'd' is '0',<br>the result is placed in W. If 'd' is '1',<br>the result is stored back in register<br>'f' (default). If 'a' is '0', the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' is '1', then the<br>bank will be selected as per the<br>BSR value (default). |  |                      |  |

| Words:                                | 1                                                                                          |                                                                                                                                                                                                                                                                                                                                                              |  |                      |  |

| Cycles:                               | 1                                                                                          |                                                                                                                                                                                                                                                                                                                                                              |  |                      |  |

| Q Cycle Activity:                     |                                                                                            |                                                                                                                                                                                                                                                                                                                                                              |  |                      |  |

| Q1                                    | Q2                                                                                         | Q3                                                                                                                                                                                                                                                                                                                                                           |  | Q4                   |  |

| Decode                                | Read<br>register 'f'                                                                       | Process<br>Data                                                                                                                                                                                                                                                                                                                                              |  | rite to<br>stination |  |

| Example:                              | RLNCF                                                                                      | REG                                                                                                                                                                                                                                                                                                                                                          |  |                      |  |

| Before Instruction<br>REG = 1010 1011 |                                                                                            |                                                                                                                                                                                                                                                                                                                                                              |  |                      |  |

| After Instruction<br>REG = 0101 0111  |                                                                                            |                                                                                                                                                                                                                                                                                                                                                              |  |                      |  |

| RRCF                                         | Rotate Right f through Carry                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                      | [ <i>label</i> ] RRCF f[,d[,a]]                                                                                                                                                                                                                                                                                                                     |

| Operands:                                    | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                 |