Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 4KB (2K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

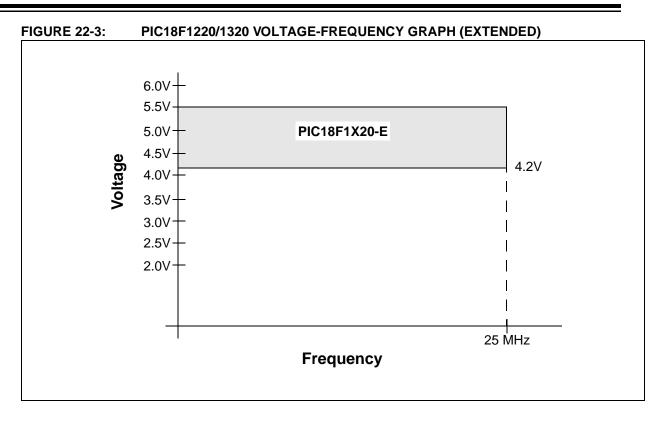

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 7x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf1220-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Register Applicable Devices |      | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt |                          |

|-----------------------------|------|------------------------------------|---------------------------------------------------------------|---------------------------------|--------------------------|

| TOSU                        | 1220 | 1320                               | 0 0000                                                        | 0 0000                          | 0 uuuu <b>(3)</b>        |

| TOSH                        | 1220 | 1320                               | 0000 0000                                                     | 0000 0000                       | uuuu uuuu <sup>(3)</sup> |

| TOSL                        | 1220 | 1320                               | 0000 0000                                                     | 0000 0000                       | uuuu uuuu <sup>(3)</sup> |

| STKPTR                      | 1220 | 1320                               | 00-0 0000                                                     | 00-0 0000                       | uu-u uuuu <b>(3)</b>     |

| PCLATU                      | 1220 | 1320                               | 0 0000                                                        | 0 0000                          | u uuuu                   |

| PCLATH                      | 1220 | 1320                               | 0000 0000                                                     | 0000 0000                       | uuuu uuuu                |

| PCL                         | 1220 | 1320                               | 0000 0000                                                     | 0000 0000                       | PC + 2 <sup>(2)</sup>    |

| TBLPTRU                     | 1220 | 1320                               | 00 0000                                                       | 00 0000                         | uu uuuu                  |

| TBLPTRH                     | 1220 | 1320                               | 0000 0000                                                     | 0000 0000                       | uuuu uuuu                |

| TBLPTRL                     | 1220 | 1320                               | 0000 0000                                                     | 0000 0000                       | uuuu uuuu                |

| TABLAT                      | 1220 | 1320                               | 0000 0000                                                     | 0000 0000                       | uuuu uuuu                |

| PRODH                       | 1220 | 1320                               | XXXX XXXX                                                     | uuuu uuuu                       | uuuu uuuu                |

| PRODL                       | 1220 | 1320                               | XXXX XXXX                                                     | uuuu uuuu                       | uuuu uuuu                |

| INTCON                      | 1220 | 1320                               | 0000 000x                                                     | 0000 000u                       | uuuu uuuu <b>(1)</b>     |

| INTCON2                     | 1220 | 1320                               | 1111 -1-1                                                     | 1111 -1-1                       | uuuu -u-u <b>(1)</b>     |

| INTCON3                     | 1220 | 1320                               | 11-0 0-00                                                     | 11-0 0-00                       | uu-u u-uu <b>(1)</b>     |

| INDF0                       | 1220 | 1320                               | N/A                                                           | N/A                             | N/A                      |

| POSTINC0                    | 1220 | 1320                               | N/A                                                           | N/A                             | N/A                      |

| POSTDEC0                    | 1220 | 1320                               | N/A                                                           | N/A                             | N/A                      |

| PREINC0                     | 1220 | 1320                               | N/A                                                           | N/A                             | N/A                      |

| PLUSW0                      | 1220 | 1320                               | N/A                                                           | N/A                             | N/A                      |

| FSR0H                       | 1220 | 1320                               | 0000                                                          | 0000                            | uuuu                     |

| FSR0L                       | 1220 | 1320                               | XXXX XXXX                                                     | uuuu uuuu                       | uuuu uuuu                |

| WREG                        | 1220 | 1320                               | XXXX XXXX                                                     | uuuu uuuu                       | uuuu uuuu                |

| INDF1                       | 1220 | 1320                               | N/A                                                           | N/A                             | N/A                      |

| POSTINC1                    | 1220 | 1320                               | N/A                                                           | N/A                             | N/A                      |

| POSTDEC1                    | 1220 | 1320                               | N/A                                                           | N/A                             | N/A                      |

| PREINC1                     | 1220 | 1320                               | N/A                                                           | N/A                             | N/A                      |

| PLUSW1                      | 1220 | 1320                               | N/A                                                           | N/A                             | N/A                      |

| FSR1H                       | 1220 | 1320                               | 0000                                                          | 0000                            | uuuu                     |

| FSR1L                       | 1220 | 1320                               | XXXX XXXX                                                     | <u>uuuu</u> uuuu                | นนนน นนนน                |

### TABLE 4-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

**2:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 4-2 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled, depending on the Oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

**6:** Bit 5 of PORTA is enabled if  $\overline{\text{MCLR}}$  is disabled.

# 7.0 DATA EEPROM MEMORY

The data EEPROM is readable and writable during normal operation over the entire VDD range. The data memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers (SFR).

There are four SFRs used to read and write the program and data EEPROM memory. These registers are:

- EECON1

- EECON2

- EEDATA

- EEADR

The EEPROM data memory allows byte read and write. When interfacing to the data memory block, EEDATA holds the 8-bit data for read/write and EEADR holds the address of the EEPROM location being accessed. These devices have 256 bytes of data EEPROM with an address range from 00h to FFh.

The EEPROM data memory is rated for high erase/ write cycle endurance. A byte write automatically erases the location and writes the new data (erasebefore-write). The write time is controlled by an on-chip timer. The write time will vary with voltage and temperature, as well as from chip to chip. Please refer to parameter D122 (Table 22-1 in **Section 22.0** "**Electrical Characteristics**") for exact limits.

# 7.1 EEADR

The address register can address 256 bytes of data EEPROM.

# 7.2 EECON1 and EECON2 Registers

EECON1 is the control register for memory accesses.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the memory write and erase sequences.

Control bit, EEPGD, determines if the access will be to program or data EEPROM memory. When clear, operations will access the data EEPROM memory. When set, program memory is accessed. Control bit, CFGS, determines if the access will be to the Configuration registers or to program memory/data EEPROM memory. When set, subsequent operations access Configuration registers. When CFGS is clear, the EEPGD bit selects either program Flash or data EEPROM memory.

The WREN bit enables and disables erase and write operations. When set, erase and write operations are allowed. When clear, erase and write operations are disabled – the WR bit cannot be set while the WREN bit is clear. This mechanism helps to prevent accidental writes to memory due to errant (unexpected) code execution.

Firmware should keep the WREN bit clear at all times, except when starting erase or write operations. Once firmware has set the WR bit, the WREN bit may be cleared. Clearing the WREN bit will not affect the operation in progress.

The WRERR bit is set when a write operation is interrupted by a Reset. In these situations, the user can check the WRERR bit and rewrite the location. It is necessary to reload the data and address registers (EEDATA and EEADR), as these registers have cleared as a result of the Reset.

Control bits, RD and WR, start read and erase/write operations, respectively. These bits are set by firmware and cleared by hardware at the completion of the operation.

The RD bit cannot be set when accessing program memory (EEPGD = 1). Program memory is read using table read instructions. See **Section 6.1 "Table Reads and Table Writes"** regarding table reads.

Note: Interrupt flag bit, EEIF in the PIR2 register, is set when write is complete. It must be cleared in software.

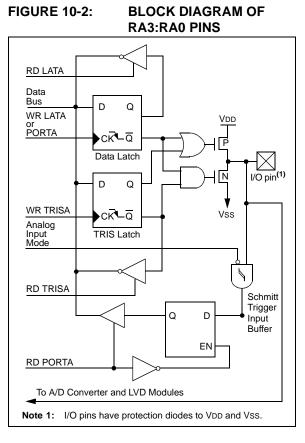

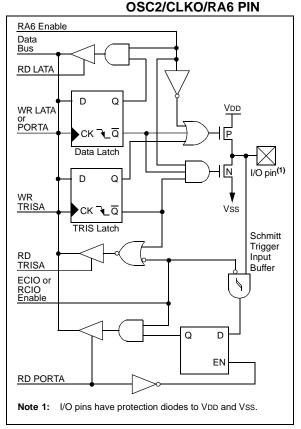

#### FIGURE 10-3:

# BLOCK DIAGRAM OF

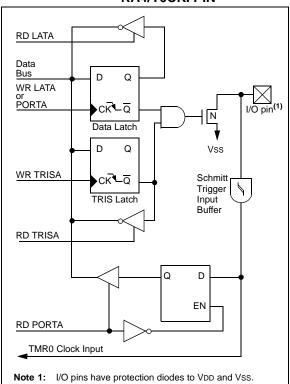

#### FIGURE 10-4: BLOCK DIAGRAM OF RA4/T0CKI PIN

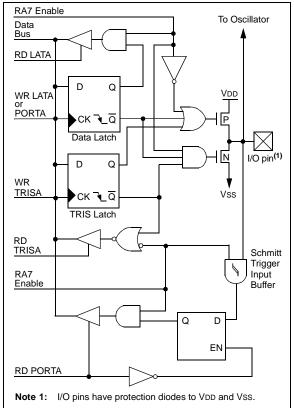

# FIGURE 10-5:

#### BLOCK DIAGRAM OF OSC1/CLKI/RA7 PIN

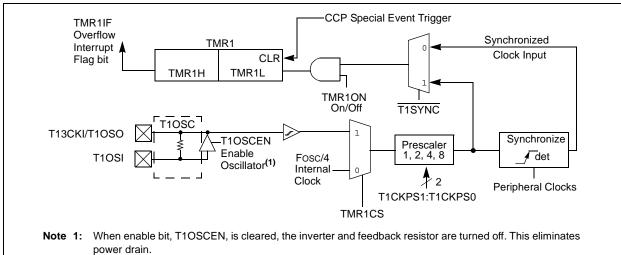

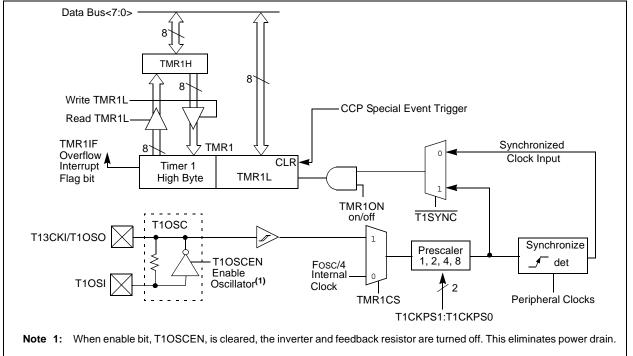

# 12.1 Timer1 Operation

Timer1 can operate in one of these modes:

- As a timer

- As a synchronous counter

- As an asynchronous counter

The operating mode is determined by the clock select bit, TMR1CS (T1CON<1>).

When TMR1CS = 0, Timer1 increments every instruction cycle. When TMR1CS = 1, Timer1 increments on every rising edge of the external clock input, or the Timer1 oscillator, if enabled.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RB7/PGD/T1OSI/P1D/KBI3 and RB6/T1OSO/T13CKI/P1C/KBI2 pins become inputs. That is, the TRISB7:TRISB6 values are ignored and the pins read as '0'.

Timer1 also has an internal "Reset input". This Reset can be generated by the CCP module (see **Section 15.4.4 "Special Event Trigger"**).

### FIGURE 12-1: TIMER1 BLOCK DIAGRAM

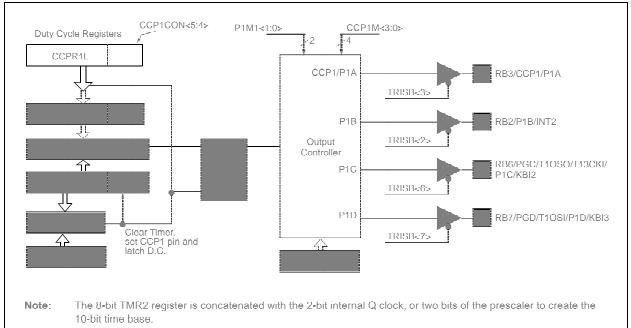

# 15.0 ENHANCED CAPTURE/ COMPARE/PWM (ECCP) MODULE

The Enhanced CCP module is implemented as a standard CCP module with Enhanced PWM capabilities. These capabilities allow for two or four output channels, user-selectable polarity, dead-band control and automatic shutdown and restart and are discussed in detail in **Section 15.5 "Enhanced PWM Mode"**.

The control register for CCP1 is shown in Register 15-1.

In addition to the expanded functions of the CCP1CON register, the ECCP module has two additional registers associated with Enhanced PWM operation and auto-shutdown features:

- PWM1CON

- ECCPAS

#### **REGISTER 15-1: CCP1CON REGISTER FOR ENHANCED CCP OPERATION**

| R/W-0/0 | U-0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|------|---------|---------|---------|---------|---------|---------|

| P1M1    | P1M0 | DC1B1   | DC1B0   | CCP1M3  | CCP1M2  | CCP1M1  | CCP1M0  |

| bit 7   |      |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | P1M<1:0>: PWM Output Configuration bits                                                                                 |  |  |  |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|         | I <u>f CCP1M&lt;3:2&gt; = 00, 01, 10:</u>                                                                               |  |  |  |  |  |  |

|         | xx = P1A assigned as Capture/Compare input; P1B, P1C, P1D assigned as port pins                                         |  |  |  |  |  |  |

|         | If CCP1M<3:2> = <u>11:</u>                                                                                              |  |  |  |  |  |  |

|         | 00 = Single output; P1A modulated; P1B, P1C, P1D assigned as port pins                                                  |  |  |  |  |  |  |

|         | 01 = Full-bridge output forward; P1D modulated; P1A active; P1B, P1C inactive                                           |  |  |  |  |  |  |

|         | 10 = Half-bridge output; P1A, P1B modulated with dead-band control; P1C, P1D assigned as                                |  |  |  |  |  |  |

|         | port pins                                                                                                               |  |  |  |  |  |  |

|         | 11 = Full-bridge output reverse; P1B modulated; P1C active; P1A, P1D inactive                                           |  |  |  |  |  |  |

| bit 5-4 | DC1B<1:0>: PWM Duty Cycle Least Significant bits                                                                        |  |  |  |  |  |  |

|         | Capture mode:                                                                                                           |  |  |  |  |  |  |

|         | Unused.                                                                                                                 |  |  |  |  |  |  |

|         | Compare mode:                                                                                                           |  |  |  |  |  |  |

|         | Unused.                                                                                                                 |  |  |  |  |  |  |

|         | PWM mode:                                                                                                               |  |  |  |  |  |  |

|         | These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPR1L.                                  |  |  |  |  |  |  |

| bit 3-0 | CCP1M<3:0>: ECCP1 Mode Select bits                                                                                      |  |  |  |  |  |  |

|         | 0000 = Capture/Compare/PWM off (resets ECCP module)                                                                     |  |  |  |  |  |  |

|         | 0001 = Unused (reserved)                                                                                                |  |  |  |  |  |  |

|         | 0010 = Compare mode, toggle output on match (ECCP1IF bit is set)                                                        |  |  |  |  |  |  |

|         | 0011 = Unused (reserved)                                                                                                |  |  |  |  |  |  |

|         | 0100 = Capture mode, every falling edge                                                                                 |  |  |  |  |  |  |

|         | 0101 = Capture mode, every rising edge                                                                                  |  |  |  |  |  |  |

|         | 0110 = Capture mode, every 4th rising edge                                                                              |  |  |  |  |  |  |

|         | 0111 = Capture mode, every 16th rising edge                                                                             |  |  |  |  |  |  |

|         | 1000 = Compare mode, set output on match (ECCP1IF bit is set)                                                           |  |  |  |  |  |  |

|         | 1001 = Compare mode, clear output on match (ECCP1IF bit is set)                                                         |  |  |  |  |  |  |

|         | 1010 = Compare mode, generate software interrupt on match (ECCP1IF bit is set,                                          |  |  |  |  |  |  |

|         | ECCP1 pin returns to port pin operation)                                                                                |  |  |  |  |  |  |

|         | 1011 = Compare mode, trigger special event (ECCP1IF bit is set; ECCP resets TMR1 or                                     |  |  |  |  |  |  |

|         | TMR3 and starts an A/D conversion if the A/D module is enabled)                                                         |  |  |  |  |  |  |

|         | 1100 = PWM mode; P1A, P1C active-high; P1B, P1D active-high                                                             |  |  |  |  |  |  |

|         | 1101 = PWM mode; P1A, P1C active-high; P1B, P1D active-low                                                              |  |  |  |  |  |  |

|         | 1110 = PWM mode; P1A, P1C active-low; P1B, P1D active-high<br>1111 = PWM mode; P1A, P1C active-low; P1B, P1D active-low |  |  |  |  |  |  |

|         | TTTT - F VIVI HIDDE, F IA, F IC ACTIVE-IOW, F ID, F ID ACTIVE-IOW                                                       |  |  |  |  |  |  |

### 15.1 ECCP Outputs

The Enhanced CCP module may have up to four outputs, depending on the selected operating mode. These outputs, designated P1A through P1D, are multiplexed with I/O pins on PORTB. The pin assignments are summarized in Table 15-1.

To configure I/O pins as PWM outputs, the proper PWM mode must be selected by setting the P1Mn and CCP1Mn bits (CCP1CON<7:6> and <3:0>, respectively). The appropriate TRISB direction bits for the port pins must also be set as outputs.

| ECCP Mode      | CCP1CON<br>Configuration | RB3  | RB2      | RB6                       | RB7                |

|----------------|--------------------------|------|----------|---------------------------|--------------------|

| Compatible CCP | 00xx 11xx                | CCP1 | RB2/INT2 | RB6/PGC/T1OSO/T13CKI/KBI2 | RB7/PGD/T1OSI/KBI3 |

| Dual PWM       | 10xx 11xx                | P1A  | P1B      | RB6/PGC/T1OSO/T13CKI/KBI2 | RB7/PGD/T1OSI/KBI3 |

| Quad PWM       | x1xx 11xx                | P1A  | P1B      | P1C                       | P1D                |

**Legend:** x = Don't care. Shaded cells indicate pin assignments not used by ECCP in a given mode.

**Note 1:** TRIS register values must be configured appropriately.

#### 15.2 CCP Module

Capture/Compare/PWM Register 1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

# TABLE 15-2:CCP MODE – TIMER<br/>RESOURCE

| CCP Mode           | Timer Resource                       |

|--------------------|--------------------------------------|

| Capture<br>Compare | Timer1 or Timer3<br>Timer1 or Timer3 |

| PWM                | Timer2                               |

# 15.3 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on pin RB3/CCP1/P1A. An event is defined as one of the following:

- every falling edge

- every rising edge

- every 4th rising edge

- · every 16th rising edge

The event is selected by control bits, CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit, CCP1IF (PIR1<2>), is set; it must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value is overwritten by the new captured value.

### 15.3.1 CCP PIN CONFIGURATION

In Capture mode, the RB3/CCP1/P1A pin should be configured as an input by setting the TRISB<3> bit.

| Note: | If the RB3/CCP1/P1A is configured as an |

|-------|-----------------------------------------|

|       | output, a write to the port can cause a |

|       | capture condition.                      |

#### 15.3.2 TIMER1/TIMER3 MODE SELECTION

The timers that are to be used with the capture feature (either Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work. The timer to be used with the CCP module is selected in the T3CON register.

#### 15.3.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit, CCP1IE (PIE1<2>), clear while changing capture modes to avoid false interrupts and should clear the flag bit, CCP1IF, following any such change in operating mode.

#### FIGURE 15-3: SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODULE

|                                         | CCP1CON<7:6>    | SIGNAL        | 0 Duty               | PR2+1                |

|-----------------------------------------|-----------------|---------------|----------------------|----------------------|

|                                         |                 |               | Cycle                | – Period –           |

| 00                                      | (Single Output) | P1A Modulated | Delay <sup>(1)</sup> | Delay <sup>(1)</sup> |

|                                         |                 | P1A Modulated |                      |                      |

| 10                                      | (Half-Bridge)   | P1B Modulated |                      |                      |

|                                         |                 | P1A Active    |                      |                      |

| (Full-Bridge,<br><sup>01</sup> Forward) | P1B Inactive    |               |                      |                      |

|                                         | P1C Inactive    |               |                      |                      |

|                                         |                 | P1D Modulated | İ                    | -ii                  |

|                                         |                 | P1A Inactive  |                      |                      |

|                                         | (Full-Bridge,   | P1B Modulated |                      |                      |

|                                         | Reverse)        | P1C Active    |                      | 1 1<br>1 1<br>1 1    |

|                                         |                 | P1D Inactive  |                      |                      |

|                                         |                 |               |                      |                      |

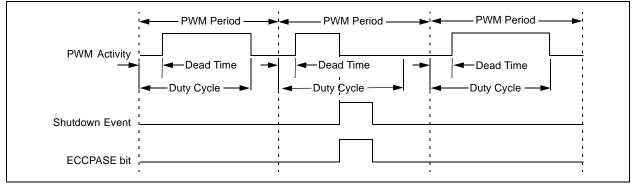

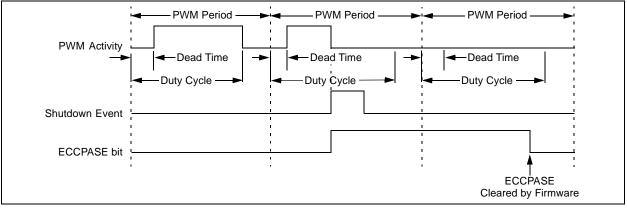

#### 15.5.7.1 Auto-Shutdown and Automatic Restart

The auto-shutdown feature can be configured to allow automatic restarts of the module, following a shutdown event. This is enabled by setting the PRSEN bit of the PWM1CON register (PWM1CON<7>).

In Shutdown mode with PRSEN = 1 (Figure 15-12), the ECCPASE bit will remain set for as long as the cause of the shutdown continues. When the shutdown condition clears, the ECCPASE bit is automatically cleared. If PRSEN = 0 (Figure 15-13), once a shutdown condition occurs, the ECCPASE bit will remain set until it is cleared by firmware. Once ECCPASE is cleared, the Enhanced PWM will resume at the beginning of the next PWM period.

| Note: | Writing to the ECCPASE bit is disabled |

|-------|----------------------------------------|

|       | while a shutdown condition is active.  |

Independent of the PRSEN bit setting, the ECCPASE bit cannot be cleared as long as the cause of the shutdown persists.

The Auto-Shutdown mode can be forced by writing a '1' to the ECCPASE bit.

# 15.5.8 START-UP CONSIDERATIONS

When the ECCP module is used in the PWM mode, the application hardware must use the proper external pullup and/or pull-down resistors on the PWM output pins. When the microcontroller is released from Reset, all of the I/O pins are in the high-impedance state. The external circuits must keep the power switch devices in the off state, until the microcontroller drives the I/O pins with the proper signal levels, or activates the PWM output(s).

The CCP1M1:CCP1M0 bits (CCP1CON<1:0>) allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (P1A/P1C and P1B/P1D). The PWM output polarities must be selected before the PWM pins are configured as outputs. Changing the polarity configuration while the PWM pins are configured as outputs is not recommended, since it may result in damage to the application circuits.

The P1A, P1B, P1C and P1D output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pins for output at the same time as the ECCP module may cause damage to the application circuit. The ECCP module must be enabled in the proper output mode and complete a full PWM cycle, before configuring the PWM pins as outputs. The completion of a full PWM cycle is indicated by the TMR2IF bit being set as the second PWM period begins.

#### FIGURE 15-12: PWM AUTO-SHUTDOWN (PRSEN = 1, AUTO-RESTART ENABLED)

© 2002-2015 Microchip Technology Inc.

### 16.2.3 AUTO-BAUD RATE DETECT

The Enhanced USART module supports the automatic detection and calibration of baud rate. This feature is active only in Asynchronous mode and while the WUE bit is clear.

The automatic baud rate measurement sequence (Figure 16-1) begins whenever a Start bit is received and the ABDEN bit is set. The calculation is self-averaging.

In the Auto-Baud Rate Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. In ABD mode, the internal Baud Rate Generator is used as a counter to time the bit period of the incoming serial byte stream.

Once the ABDEN bit is set, the state machine will clear the BRG and look for a Start bit. The Auto-Baud Detect must receive a byte with the value 55h (ASCII "U", which is also the LIN bus Sync character), in order to calculate the proper bit rate. The measurement is taken over both a low and a high bit time in order to minimize any effects caused by asymmetry of the incoming signal. After a Start bit, the SPBRG begins counting up using the preselected clock source on the first rising edge of RX. After eight bits on the RX pin, or the fifth rising edge, an accumulated value totaling the proper BRG period is left in the SPBRGH:SPBRG registers. Once the fifth edge is seen (should correspond to the Stop bit), the ABDEN bit is automatically cleared.

While calibrating the baud rate period, the BRG registers are clocked at 1/8th the preconfigured clock rate. Note that the BRG clock will be configured by the BRG16 and BRGH bits. Independent of the BRG16 bit setting, both the SPBRG and SPBRGH will be used as a 16-bit counter. This allows the user to verify that no carry occurred for 8-bit modes, by checking for 00h in the SPBRGH register. Refer to Table 16-4 for counter clock rates to the BRG.

While the ABD sequence takes place, the EUSART state machine is held in Idle. The RCIF interrupt is set once the fifth rising edge on RX is detected. The value in the RCREG needs to be read to clear the RCIF interrupt. RCREG content should be discarded.

Note 1: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible due to bit error rates. Overall system timing and communication baud rates must be taken into consideration when using the Auto-Baud Rate Detection feature.

# 16.2.4 RECEIVING A SYNC (AUTO-BAUD RATE DETECT)

To receive a Sync (Auto-Baud Rate Detect):

- 1. Configure the EUSART for asynchronous receive. TXEN should remain clear. SPBRGH:SPBRG may be left as is. The controller should operate in either PRI\_RUN or PRI\_IDLE.

- 2. Enable RXIF interrupts. Set RCIE, PEIE, GIE.

- 3. Enable Auto-Baud Rate Detect. Set ABDEN.

- 4. When the next RCIF interrupt occurs, the received baud rate has been measured. Read RCREG to clear RCIF and discard. Check SPBRGH:SPBRG for a valid value. The EUSART is ready for normal communications. Return from the interrupt. Allow the primary clock to run (PRI\_RUN or PRI\_IDLE).

- Process subsequent RCIF interrupts normally as in asynchronous reception. Remain in PRI\_RUN or PRI\_IDLE until communications are complete.

| TABLE 16-4: | BRG COUNTER CLOCK |

|-------------|-------------------|

|             | RATES             |

| BRG16 | BRGH | BRG Counter Clock |

|-------|------|-------------------|

| 0     | 0    | Fosc/512          |

| 0     | 1    | Fosc/128          |

| 1     | 0    | Fosc/128          |

| 1     | 1    | Fosc/32           |

**Note:** During the ABD sequence, SPBRG and SPBRGH are both used as a 16-bit counter, independent of BRG16 setting.

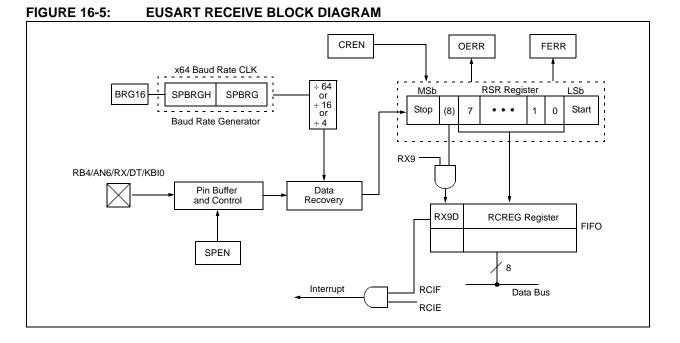

#### 16.3.2 EUSART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 16-5. The data is received on the RB4/AN6/RX/DT/KBI0 pin and drives the data recovery block. The data recovery block is actually a high-speed shifter, operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, set enable bit RCIE.

- 4. If 9-bit reception is desired, set bit RX9.

- 5. Enable the reception by setting bit CREN.

- Flag bit, RCIF, will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREG register.

- 9. If any error occurred, clear the error by clearing enable bit CREN.

- 10. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

# 16.3.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are required, set the RCEN bit and select the desired priority level with the RCIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- 5. Set the ADDEN bit to enable address detect.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF bit will be set when reception is complete. The interrupt will be Acknowledged if the RCIE and GIE bits are set.

- 8. Read the RCSTA register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 9. Read RCREG to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

#### 16.4.2 EUSART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either the Single Receive Enable bit, SREN (RCSTA<5>), or the Continuous Receive Enable bit, CREN (RCSTA<4>). Data is sampled on the RB4/AN6/RX/DT/KBI0 pin on the falling edge of the clock.

If enable bit, SREN, is set, only a single word is received. If enable bit, CREN, is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, set enable bit RCIE.

- 5. If 9-bit reception is desired, set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception, set bit CREN.

- 7. Interrupt flag bit, RCIF, will be set when reception is complete and an interrupt will be generated if the enable bit, RCIE, was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

- 11. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| RB4/AN6/RX/<br>DT/KBI0 pin               |            | <u> </u>           | bit 0            | $\sim$ | bit 1 | $\times$         | bit 2 | $\sim$ | bit 3       | $\sim$ | bit 4            | $\sim$ | bit 5            | $\searrow$ | bit 6       | $\sim$ | bit 7            |                  |    |

|------------------------------------------|------------|--------------------|------------------|--------|-------|------------------|-------|--------|-------------|--------|------------------|--------|------------------|------------|-------------|--------|------------------|------------------|----|

| RB1/AN5/TX/<br>CK/INT1 pin<br>(SCKP = 0) |            | ·/                 |                  |        |       |                  |       |        |             |        |                  |        |                  |            | ;<br>;      |        | <u>.</u>         | 1<br>1<br>1<br>1 |    |

| RB1/AN5/TX/<br>CK/INT1 pin<br>(SCKP = 1) |            | 1<br><u>1</u><br>1 |                  |        |       |                  |       |        |             |        |                  |        |                  |            | ;<br>       |        |                  | 1<br>1<br>1      |    |

| Write to<br>bit SREN                     |            | 1<br>1<br>1<br>1   | 1<br>1<br>1      | 1<br>  |       | י<br>י<br>י      |       |        | 1<br>1<br>1 |        |                  |        | 1<br>1<br>1      |            | •<br>•<br>• |        | 1<br>1<br>1      |                  |    |

| SREN bit                                 |            | :                  |                  |        |       | ı                |       |        | L           |        |                  |        |                  |            |             |        | <u>.</u>         | i                |    |

| CREN bit                                 | '0'        |                    | ,<br>,           |        |       |                  |       |        | I           |        |                  |        |                  |            |             |        |                  |                  | "( |

| RCIF bit<br>(Interrupt)                  | . <u> </u> | 1<br>1<br>1        | 1<br>1<br>1<br>1 | ·<br>· |       | ,<br>,<br>,<br>, |       |        | 1<br>1<br>1 |        | 1<br>1<br>1<br>1 |        | 1<br>1<br>1<br>1 |            | ,<br>,<br>, |        | 1<br>1<br>1<br>1 | ;                |    |

| Read<br>RXREG                            |            | 1<br>1             |                  |        |       | ,<br>,           |       |        | •           |        |                  |        |                  |            | ;           |        | ,<br>,           | :                |    |

#### FIGURE 16-12: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

# 20.0 INSTRUCTION SET SUMMARY

The PIC18 instruction set adds many enhancements to the previous PIC instruction sets, while maintaining an easy migration from these PIC instruction sets.

Most instructions are a single program memory word (16 bits), but there are three instructions that require two program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal operations

- Control operations

The PIC18 instruction set summary in Table 20-1 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 20-1 shows the opcode field descriptions.

Most byte-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator 'f' specifies which file register is to be used by the instruction.

The destination designator 'd' specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the WREG register. If 'd' is one, the result is placed in the file register specified in the instruction.

All **bit-oriented** instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator 'b' selects the number of the bit affected by the operation, while the file register designator 'f' represents the number of the file in which the bit is located.

The **literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The **control** instructions may use some of the following operands:

- A program memory address (specified by 'n')

- The mode of the CALL or RETURN instructions (specified by 's')

- The mode of the table read and table write instructions (specified by 'm')

- No operand required (specified by '—')

All instructions are a single word, except for three double-word instructions. These three instructions were made double-word instructions so that all the required information is available in these 32 bits. In the second word, the 4 MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP.

The double-word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 20-1 shows the general formats that the instructions can have.

All examples use the format 'nnh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

The Instruction Set Summary, shown in Table 20-1, lists the instructions recognized by the Microchip Assembler (MPASM<sup>TM</sup>). **Section 20.2** "Instruction **Set**" provides a description of each instruction.

# 20.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified and the result is stored according to either the instruction or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a "BCF PORTB, 1" instruction will read PORTB, clear bit 1 of the data, then write the result back to PORTB. The read operation would have the unintended result that any condition that sets the RBIF flag would be cleared. The R-M-W operation may also copy the level of an input pin to its corresponding output latch.

| CLRF             | Clear f                                                                 | CLRWDT           | Clear Watchdog Timer                                       |  |  |  |  |

|------------------|-------------------------------------------------------------------------|------------------|------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label]CLRF f[,a]                                                       | Syntax:          | [ label ] CLRWDT                                           |  |  |  |  |

| Operands:        | $0 \leq f \leq 255$                                                     | Operands:        | None                                                       |  |  |  |  |

|                  | a ∈ [0,1]                                                               | Operation:       | 000h $\rightarrow$ WDT,                                    |  |  |  |  |

| Operation:       | $\begin{array}{l} 000h \rightarrow f \\ 1 \rightarrow Z \end{array}$    |                  | $000h \rightarrow WDT$ postscaler,<br>1 $\rightarrow TO$ , |  |  |  |  |

| Status Affected: | Z                                                                       |                  | $1 \rightarrow \overline{PD}$                              |  |  |  |  |

| Encoding:        |                                                                         | Status Affected: | TO, PD                                                     |  |  |  |  |

| Description:     | Clears the contents of the specified                                    | Encoding:        | 0000 0000 0000 0100                                        |  |  |  |  |

| Decemption       | register. If 'a' is '0', the Access                                     | Description:     | CLRWDT instruction resets the                              |  |  |  |  |

|                  | Bank will be selected, overriding                                       |                  | Watchdog Timer. It also resets the                         |  |  |  |  |

|                  | the BSR value. If 'a' = 1, then the bank will be selected as per the    |                  | postscaler of the WDT. Status bits, TO and PD, are set.    |  |  |  |  |

|                  | BSR value (default).                                                    | Words:           | 1                                                          |  |  |  |  |

| Words:           | 1                                                                       | Cycles:          | 1                                                          |  |  |  |  |

| Cycles:          | 1                                                                       | Q Cycle Activity |                                                            |  |  |  |  |

| Q Cycle Activity | :                                                                       | Q1               | Q2 Q3 Q4                                                   |  |  |  |  |

| Q1               | Q2 Q3 Q4                                                                | Decode           | No Process No                                              |  |  |  |  |

| Decode           | Read     Process     Write       register 'f'     Data     register 'f' |                  | operation Data operation                                   |  |  |  |  |

|                  |                                                                         | Example:         | CLRWDT                                                     |  |  |  |  |

| Example:         | CLRF FLAG_REG                                                           | Before Instru    |                                                            |  |  |  |  |

| Before Instru    | uction                                                                  | WDT Co           |                                                            |  |  |  |  |

| FLAG_R           |                                                                         | After Instruc    | tion                                                       |  |  |  |  |

| After Instruc    |                                                                         | WDT Co<br>WDT Po |                                                            |  |  |  |  |

| FLAG_R           | EG = 0x00                                                               | TO               | = 1                                                        |  |  |  |  |

|                  |                                                                         | PD               | = 1                                                        |  |  |  |  |

| XOR         | WF                         | Exclusive                                                                      | Exclusive OR W with f                                                                                                                                                                                                                                                                                                                                |                                    |         |      |  |  |  |  |

|-------------|----------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------|------|--|--|--|--|

| Synt        | ax:                        | [ label ]                                                                      | XORWF                                                                                                                                                                                                                                                                                                                                                | f [,                               | ,d [,a] | ]]   |  |  |  |  |

| Opei        | rands:                     | $0 \le f \le 25$<br>$d \in [0,1]$<br>$a \in [0,1]$                             |                                                                                                                                                                                                                                                                                                                                                      |                                    |         |      |  |  |  |  |

| Oper        | ration:                    | (W) .XOR                                                                       | (W) .XOR. (f) $\rightarrow$ dest                                                                                                                                                                                                                                                                                                                     |                                    |         |      |  |  |  |  |

| Statu       | is Affected:               | N, Z                                                                           | N, Z                                                                                                                                                                                                                                                                                                                                                 |                                    |         |      |  |  |  |  |

| Enco        | oding:                     | 0001                                                                           | 10da                                                                                                                                                                                                                                                                                                                                                 | fff                                | f       | ffff |  |  |  |  |

| Desc        | cription:                  | with regis<br>is stored I<br>(default).<br>Bank will<br>the BSR v<br>bank will | Exclusive OR the contents of W<br>with register 'f'. If 'd' is '0', the result<br>is stored in W. If 'd' is '1', the result<br>is stored back in the register 'f'<br>(default). If 'a' is '0', the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' is '1', then the<br>bank will be selected as per the<br>BSR value (default). |                                    |         |      |  |  |  |  |

| Word        | ds:                        | 1                                                                              | 1                                                                                                                                                                                                                                                                                                                                                    |                                    |         |      |  |  |  |  |

| Cycl        | es:                        | 1                                                                              | 1                                                                                                                                                                                                                                                                                                                                                    |                                    |         |      |  |  |  |  |

| QC          | ycle Activity:             |                                                                                |                                                                                                                                                                                                                                                                                                                                                      |                                    |         |      |  |  |  |  |

|             | Q1                         | Q2                                                                             | Q3                                                                                                                                                                                                                                                                                                                                                   | 5                                  | Q4      |      |  |  |  |  |

|             | Decode                     | Read<br>register 'f'                                                           |                                                                                                                                                                                                                                                                                                                                                      | ocess Write to<br>Data destination |         |      |  |  |  |  |

| <u>Exar</u> | nple:                      | XORWF                                                                          | REG                                                                                                                                                                                                                                                                                                                                                  |                                    |         |      |  |  |  |  |

|             | Before Instru<br>REG<br>W  | = 0xAF<br>= 0xB5                                                               |                                                                                                                                                                                                                                                                                                                                                      |                                    |         |      |  |  |  |  |

|             | After Instruct<br>REG<br>W | tion<br>= 0x1A<br>= 0xB5                                                       |                                                                                                                                                                                                                                                                                                                                                      |                                    |         |      |  |  |  |  |

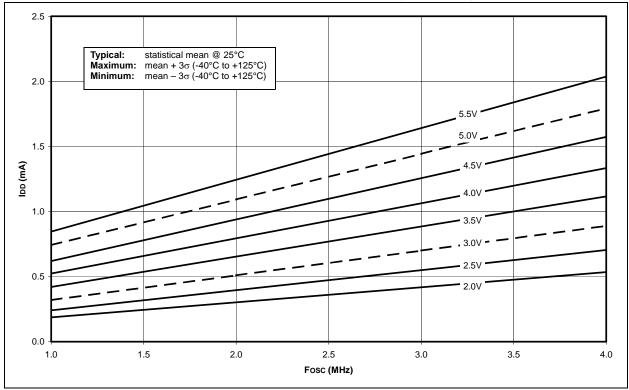

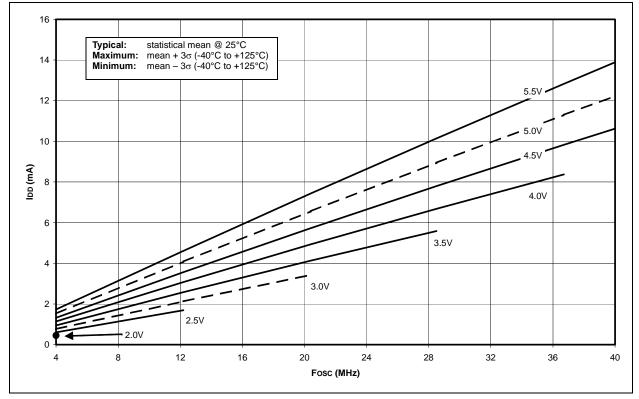

# 22.2 DC Characteristics: Power-Down and Supply Current PIC18F1220/1320 (Industrial) PIC18LF1220/1320 (Industrial) (Continued)

| PIC18LF<br>(Indus  | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                                                                                                                                                                         |      |       |            |            |                              |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|------------|------------------------------|--|--|--|

| PIC18F1:<br>(Indu: |                                                                                                                                    | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |       |            |            |                              |  |  |  |

| Param<br>No.       | Device                                                                                                                             | Тур.                                                                                                                                                                                    | Max. | Units | Conditions |            |                              |  |  |  |

|                    | Supply Current (IDD) <sup>(2,3)</sup>                                                                                              |                                                                                                                                                                                         |      |       |            |            |                              |  |  |  |

|                    | PIC18LF1220/1320                                                                                                                   | 9.2                                                                                                                                                                                     | 15   | μA    | -10°C      | VDD = 2.0V |                              |  |  |  |

|                    |                                                                                                                                    | 9.6                                                                                                                                                                                     | 15   | μA    | +25°C      |            |                              |  |  |  |

|                    |                                                                                                                                    | 12.7                                                                                                                                                                                    | 18   | μA    | +70°C      |            |                              |  |  |  |

|                    | PIC18LF1220/1320                                                                                                                   | 22                                                                                                                                                                                      | 30   | μA    | -10°C      |            | Fosc = 32 kHz <sup>(4)</sup> |  |  |  |

|                    |                                                                                                                                    | 21                                                                                                                                                                                      | 30   | μA    | +25°C      | VDD = 3.0V | (SEC_IDLE mode,              |  |  |  |

|                    |                                                                                                                                    | 20                                                                                                                                                                                      | 35   | μA    | +70°C      |            | Timer1 as clock)             |  |  |  |

|                    | All devices                                                                                                                        | 50                                                                                                                                                                                      | 80   | μΑ    | -10°C      |            |                              |  |  |  |

|                    |                                                                                                                                    | 45                                                                                                                                                                                      | 80   | μA    | +25°C      | VDD = 5.0V |                              |  |  |  |

|                    |                                                                                                                                    | 45                                                                                                                                                                                      | 80   | μA    | +70°C      |            |                              |  |  |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.

- **3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be estimated by the formula Ir = VDD/2REXT (mA) with REXT in kΩ.

- 4: Standard low-cost 32 kHz crystals have an operating temperature range of -10°C to +70°C. Extended temperature crystals are available at a much higher cost.

| Param.<br>No. | Symbol   | Characteristic                                                              | Min. | Max. | Units | Conditions |

|---------------|----------|-----------------------------------------------------------------------------|------|------|-------|------------|

| 125           | TdtV2ckl | <u>SYNC RCV (MASTER &amp; SLAVE)</u><br>Data Hold before CK↓ (DT hold time) | 10   |      | ns    |            |

| 126           | TckL2dtl | Data Hold after $CK \downarrow$ (DT hold time)                              | 15   |      | ns    |            |

#### TABLE 22-12: EUSART SYNCHRONOUS RECEIVE REQUIREMENTS

# TABLE 22-13: A/D CONVERTER CHARACTERISTICS: PIC18F1220/1320 (INDUSTRIAL) PIC18LF1220/1320 (INDUSTRIAL)

| Param<br>No. | Symbol        | Charact                                    | eristic     | Min.        | Тур.             | Max.        | Units                  | Conditions                                                  |

|--------------|---------------|--------------------------------------------|-------------|-------------|------------------|-------------|------------------------|-------------------------------------------------------------|

| A01          | NR            | Resolution                                 | —           | _           | 10               | bit         | $\Delta VREF \ge 3.0V$ |                                                             |

| A03          | EIL           | Integral Linearity                         | Error       | —           | _                | <±1         | LSb                    | $\Delta VREF \ge 3.0V$                                      |

| A04          | Edl           | Differential Linea                         | rity Error  | —           | _                | <±1         | LSb                    | $\Delta VREF \ge 3.0V$                                      |

| A06          | EOFF          | Offset Error                               |             | _           |                  | <±1         | LSb                    | $\Delta \text{VREF} \geq 3.0 \text{V}$                      |

| A07          | Egn           | Gain Error                                 |             | _           |                  | <±1         | LSb                    | $\Delta VREF \ge 3.0V$                                      |

| A10          | _             | Monotonicity                               | gu          | arantee     | d <sup>(2)</sup> | _           |                        |                                                             |

| A20          | $\Delta VREF$ | Reference Voltage Range<br>(VREFH – VREFL) |             | 3           | _                | AVDD – AVSS | V                      | For 10-bit resolution                                       |

| A21          | Vrefh         | Reference Voltage High                     |             | AVss + 3.0V | _                | AVDD + 0.3V | V                      | For 10-bit resolution                                       |

| A22          | Vrefl         | Reference Voltage Low                      |             | AVss-0.3V   |                  | AVDD - 3.0V | V                      | For 10-bit resolution                                       |

| A25          | Vain          | Analog Input Vol                           | tage        | VREFL       | _                | Vrefh       | V                      |                                                             |

| A28          | AVdd          | Analog Supply V                            | oltage      | Vdd - 0.3   | _                | VDD + 0.3   | V                      |                                                             |

| A29          | AVss          | Analog Supply V                            | oltage      | Vss – 0.3   | _                | Vss + 0.3   | V                      |                                                             |

| A30          | ZAIN          | Recommended I<br>Analog Voltage S          |             | —           | _                | 2.5         | kΩ                     |                                                             |

| A40          | IAD           | A/D Conversion                             | PIC18F1X20  |             | 180              | —           | μΑ                     | Average current                                             |

|              |               | Current (VDD)                              | PIC18LF1X20 | —           | 90               | _           | μΑ                     | consumption when<br>A/D is on <b>(Note 1)</b>               |

| A50          | IREF          | VREF Input Current (Note 3)                |             |             |                  | ±5<br>±150  | μΑ<br>μΑ               | During VAIN acquisition.<br>During A/D conversion<br>cycle. |

**Note 1:** When A/D is off, it will not consume any current other than minor leakage current. The power-down current specification includes any such leakage from the A/D module.

2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

**3:** VREFH current is from RA3/AN3/VREF+ pin or AVDD, whichever is selected as the VREFH source. VREFL current is from RA2/AN2/VREF- pin or AVss, whichever is selected as the VREFL source.

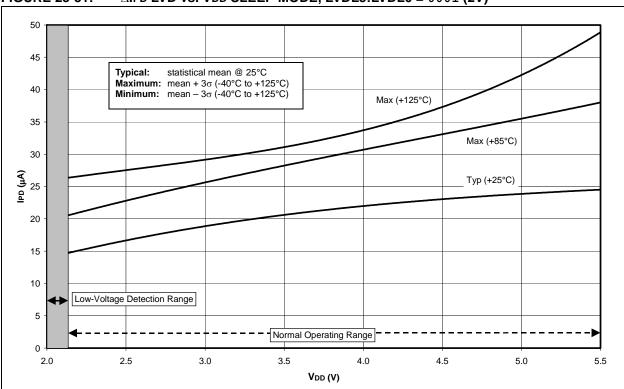

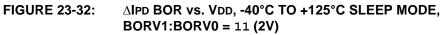

FIGURE 23-31: △IPD LVD vs. VDD SLEEP MODE, LVDL3:LVDL0 = 0001 (2V)

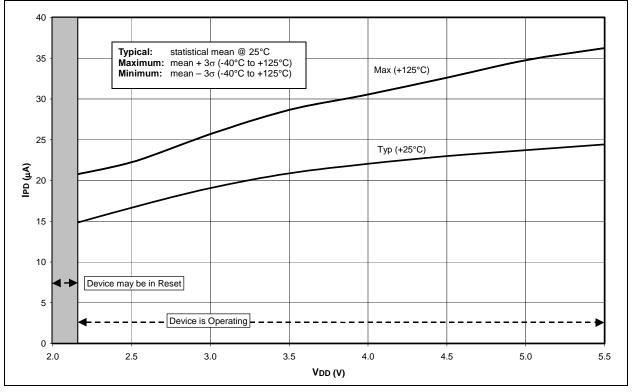

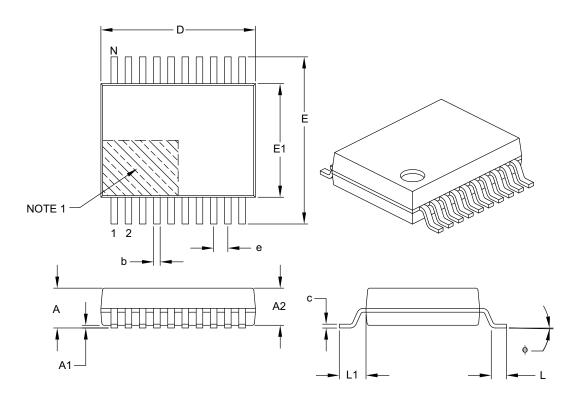

### 20-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units         | MILLIMETERS |          |      |  |  |

|--------------------------|---------------|-------------|----------|------|--|--|

| Dim                      | ension Limits | MIN         | NOM      | MAX  |  |  |

| Number of Pins           | N             |             | 20       |      |  |  |

| Pitch                    | е             |             | 0.65 BSC |      |  |  |

| Overall Height           | А             | -           | -        | 2.00 |  |  |

| Molded Package Thickness | A2            | 1.65        | 1.75     | 1.85 |  |  |

| Standoff                 | A1            | 0.05        | -        | -    |  |  |

| Overall Width            | E             | 7.40        | 7.80     | 8.20 |  |  |

| Molded Package Width     | E1            | 5.00        | 5.30     | 5.60 |  |  |

| Overall Length           | D             | 6.90        | 7.20     | 7.50 |  |  |

| Foot Length              | L             | 0.55        | 0.75     | 0.95 |  |  |

| Footprint                | L1            | 1.25 REF    |          |      |  |  |

| Lead Thickness           | С             | 0.09        | -        | 0.25 |  |  |

| Foot Angle               | φ             | 0°          | 4°       | 8°   |  |  |

| Lead Width               | b             | 0.22        | _        | 0.38 |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B