Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | UART/USART                                                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 7x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf1320-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

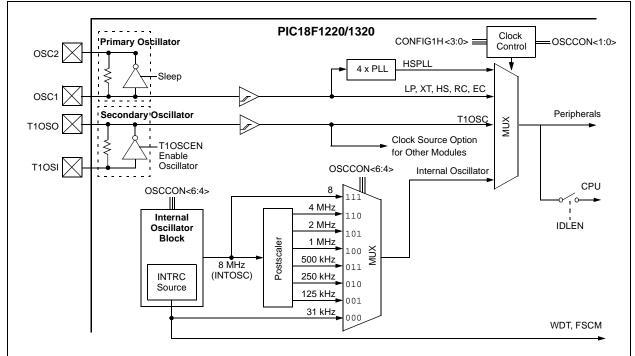

# 2.7.1 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 2-2) controls several aspects of the system clock's operation, both in full-power operation and in power managed modes.

The System Clock Select bits, SCS1:SCS0, select the clock source that is used when the device is operating in power managed modes. The available clock sources are the primary clock (defined in Configuration Register 1H), the secondary clock (Timer1 oscillator) and the internal oscillator block. The clock selection has no effect until a SLEEP instruction is executed and the device enters a power managed mode of operation. The SCS bits are cleared on all forms of Reset.

The Internal Oscillator Select bits, IRCF2:IRCF0, select the frequency output of the internal oscillator block that is used to drive the system clock. The choices are the INTRC source, the INTOSC source (8 MHz), or one of the six frequencies derived from the INTOSC postscaler (125 kHz to 4 MHz). If the internal oscillator block is supplying the system clock, changing the states of these bits will have an immediate change on the internal oscillator's output.

The OSTS, IOFS and T1RUN bits indicate which clock source is currently providing the system clock. The OSTS indicates that the Oscillator Start-up Timer has timed out and the primary clock is providing the system clock in Primary Clock modes. The IOFS bit indicates when the internal oscillator block has stabilized and is providing the system clock in RC Clock modes or during Two-Speed Start-ups. The T1RUN bit (T1CON<6>) indicates when the Timer1 oscillator is providing the system clock in Secondary Clock modes. In power managed modes, only one of these three bits will be set at any time. If none of these bits are set, the INTRC is providing the system clock, or the internal oscillator block has just started and is not yet stable.

The IDLEN bit controls the selective shutdown of the controller's CPU in power managed modes. The uses of these bits are discussed in more detail in **Section 3.0 "Power Managed Modes"**.

- Note 1: The Timer1 oscillator must be enabled to select the secondary clock source. The Timer1 oscillator is enabled by setting the T1OSCEN bit in the Timer1 Control register (T1CON<3>). If the Timer1 oscillator is not enabled, then any attempt to select a secondary clock source when executing a SLEEP instruction will be ignored.

- 2: It is recommended that the Timer1 oscillator be operating and stable before executing the SLEEP instruction or a very long delay may occur while the Timer1 oscillator starts.

### FIGURE 2-8: PIC18F1220/1320 CLOCK DIAGRAM

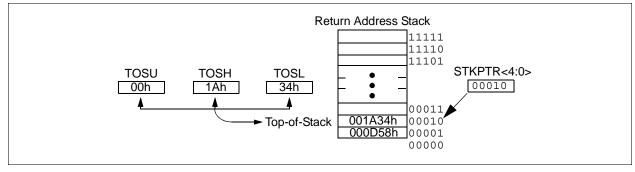

# 5.2 Return Address Stack

The return address stack allows any combination of up to 31 program calls and interrupts to occur. The PC (Program Counter) is pushed onto the stack when a CALL or RCALL instruction is executed, or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions.

The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer, with the Stack Pointer initialized to 00000B after all Resets. There is no RAM associated with Stack Pointer, 00000B. This is only a Reset value. During a CALL type instruction, causing a push onto the stack, the Stack Pointer is first incremented and the RAM location pointed to by the Stack Pointer (STKPTR) register is written with the contents of the PC (already pointing to the instruction, causing a pop from the stack, the COMPUTED TO THE STACK, the COMPUTED TO THE STACK POINTER ARE TURN THE INSTRUCTION, CAUSING A POP FOR THE STACK, THE COMPUTED TO THE STACK POINTER ARE TURN TO THE STACK POINTER ARE TRANSFERRED TO THE STACK POINTER ARE TRANSFERRED TO THE STACK POINTER IS DESTINATED TO THE STACK POINTER ARE TRANSFERRED TO THE STACK POINTER ARE TRANSFERRED TO THE STACK POINTER ARE TRANSFERRED TO THE STACK POINTER ARE TRANSFERRED.

The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the top-of-stack Special File Registers. Data can also be pushed to or popped from the stack using the top-of-stack SFRs. Status bits indicate if the stack is full, has overflowed or underflowed.

#### 5.2.1 TOP-OF-STACK ACCESS

The top of the stack is readable and writable. Three register locations, TOSU, TOSH and TOSL, hold the contents of the stack location pointed to by the STKPTR register (Figure 5-3). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU, TOSH and TOSL registers. These values can be placed on a user defined software stack. At return time, the software can replace the TOSU, TOSH and TOSL and do a return.

The user must disable the Global Interrupt Enable bits while accessing the stack to prevent inadvertent stack corruption.

#### 5.2.2 RETURN STACK POINTER (STKPTR)

The STKPTR register (Register 5-1) contains the Stack Pointer value, the STKFUL (Stack Full) Status bit and the STKUNF (Stack Underflow) Status bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. At Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVR (Stack Overflow Reset Enable) Configuration bit. (Refer to **Section 19.1 "Configuration Bits**" for a description of the device Configuration bits.) If STVR is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVR is cleared, the STKFUL bit will be set on the 31st push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31st push and STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and sets the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or a POR occurs.

**Note:** Returning a value of zero to the PC on an underflow has the effect of vectoring the program to the Reset vector, where the stack conditions can be verified and appropriate actions can be taken. This is not the same as a Reset, as the contents of the SFRs are not affected.

#### FIGURE 5-3: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

# 5.3 Fast Register Stack

A "fast return" option is available for interrupts. A fast register stack is provided for the Status, WREG and BSR registers and is only one in depth. The stack is not readable or writable and is loaded with the current value of the corresponding register when the processor vectors for an interrupt. The values in the registers are then loaded back into the working registers, if the RETFIE, FAST instruction is used to return from the interrupt.

All interrupt sources will push values into the stack registers. If both low and high priority interrupts are enabled, the stack registers cannot be used reliably to return from low priority interrupts. If a high priority interrupt occurs while servicing a low priority interrupt, the stack register values stored by the low priority interrupt will be overwritten. Users must save the key registers in software during a low priority interrupt.

If interrupt priority is not used, all interrupts may use the fast register stack for returns from interrupt.

If no interrupts are used, the fast register stack can be used to restore the Status, WREG and BSR registers at the end of a subroutine call. To use the fast register stack for a subroutine call, a CALL LABEL, FAST instruction must be executed to save the Status, WREG and BSR registers to the fast register stack. A RETURN, FAST instruction is then executed to restore these registers from the fast register stack.

Example 5-1 shows a source code example that uses the fast register stack during a subroutine call and return.

#### EXAMPLE 5-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST | ;STATUS, WREG, BSR      |

|-----------------|-------------------------|

|                 | ;SAVED IN FAST REGISTER |

|                 | ; STACK                 |

| •               |                         |

| •               |                         |

|                 |                         |

| SUB1 •          |                         |

| •               |                         |

| RETURN, FAST    | ;RESTORE VALUES SAVED   |

|                 | ;IN FAST REGISTER STACK |

|                 |                         |

# 5.4 PCL, PCLATH and PCLATU

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide. The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits and is not directly readable or writable. Updates to the PCH register may be performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits and is not directly readable or writable. Updates to the PCLATH register. Updates to the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits and is not directly readable or writable. Updates to the PCU register may be performed through the PCLATU register.

The contents of PCLATH and PCLATU will be transferred to the program counter by any operation that writes PCL. Similarly, the upper two bytes of the program counter will be transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 5.8.1** "**Computed GOTO**").

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the LSB of PCL is fixed to a value of '0'. The PC increments by two to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter. Example 8-3 shows the sequence to do a 16 x 16 unsigned multiply. Equation 8-1 shows the algorithm that is used. The 32-bit result is stored in four registers, RES3:RES0.

#### EQUATION 8-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

RES3:RES0

= ARG1H:ARG1L • ARG2H:ARG2L = (ARG1H • ARG2H •  $2^{16}$ ) + (ARG1H • ARG2L •  $2^{8}$ ) + (ARG1L • ARG2L •  $2^{8}$ ) +

(ARG1L • ARG2L)

### EXAMPLE 8-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

| MOVFARG1L, W     |                    |

|------------------|--------------------|

| MULWFARG2L       | ; ARG1L * ARG2L -> |

|                  | ; PRODH:PRODL      |

| MOVFFPRODH, RES1 | ;                  |

| MOVFFPRODL, RESO | ;                  |

| ;                |                    |

| MOVFARG1H, W     |                    |

| MULWFARG2H       | ; ARG1H * ARG2H -> |

|                  | ; PRODH:PRODL      |

| MOVFFPRODH, RES3 | ;                  |

| MOVFFPRODL, RES2 | ;                  |

| ;                |                    |

| MOVFARG1L, W     |                    |

| MULWFARG2H       | ; ARG1L * ARG2H -> |

|                  | ; PRODH:PRODL      |

| MOVFPRODL, W     | ;                  |

|                  | ; Add cross        |

|                  | ; products         |

| ADDWFCRES2, F    | ;                  |

| CLRFWREG         | ;                  |

| ADDWFCRES3,F     | ;                  |

| ;                |                    |

| MOVFARG1H, W     | ;                  |

| MULWFARG2L       | ; ARG1H * ARG2L -> |

|                  | ; PRODH:PRODL      |

| MOVFPRODL, W     | ;                  |

|                  | ; Add cross        |

|                  | ; products         |

| ADDWFCRES2, F    | ;                  |

| CLRFWREG         | ;                  |

| ADDWFCRES3, F    | ;                  |

Example 8-4 shows the sequence to do a 16 x 16 signed multiply. Equation 8-2 shows the algorithm used. The 32-bit result is stored in four registers, RES3:RES0. To account for the sign bits of the arguments, each argument pairs' Most Significant bit (MSb) is tested and the appropriate subtractions are done.

#### EQUATION 8-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

#### RES3:RES0

- = ARG1H:ARG1L ARG2H:ARG2L

- =  $(ARG1H \bullet ARG2H \bullet 2^{16}) +$  $(ARG1H \bullet ARG2L \bullet 2^{8}) +$  $(ARG1L \bullet ARG2H \bullet 2^{8}) +$  $(ARG1L \bullet ARG2L) +$  $(-1 \bullet ARG2H < 7 > \bullet ARG1H: ARG1L \bullet 2^{16}) +$  $(-1 \bullet ARG1H < 7 > \bullet ARG2H: ARG2L \bullet 2^{16})$

#### EXAMPLE 8-4: 16 x 16 SIGNED MULTIPLY ROUTINE

| MOVF ARG1L, W<br>MULWF ARG2L ; ARG1L * ARG2L ·<br>; PRODH:PRODL<br>MOVFF PRODH, RES1 ; | ->         |

|----------------------------------------------------------------------------------------|------------|

| ; PRODH:PRODL<br>MOVFF PRODH, RES1 ;                                                   | ->         |

| MOVFF PRODH, RES1 ;                                                                    |            |

|                                                                                        |            |

|                                                                                        |            |

| MOVFF PRODL, RESO ;                                                                    |            |

| i                                                                                      |            |

| MOVF ARG1H, W                                                                          |            |

| MULWF ARG2H ; ARG1H * ARG2H                                                            | ->         |

| ; PRODH:PRODL                                                                          |            |

| MOVFF PRODH, RES3 ;                                                                    |            |

| MOVFF PRODL, RES2 ;                                                                    |            |

| ;                                                                                      |            |

| ,<br>MOVF ARG1L, W                                                                     |            |

|                                                                                        |            |

| MULWF ARG2H ; ARG1L * ARG2H ·                                                          | - >        |

| ; PRODH:PRODL                                                                          |            |

| MOVF PRODL, W ;                                                                        |            |

| ADDWF RES1, F ; Add cross                                                              |            |

| MOVF PRODH, W ; products                                                               |            |

| ADDWFC RES2, F ;                                                                       |            |

| CLRF WREG ;                                                                            |            |

| ADDWFC RES3, F ;                                                                       |            |

| ;                                                                                      |            |

| MOVF ARG1H, W ;                                                                        |            |

| MULWF ARG2L ; ARG1H * ARG2L ·                                                          | ->         |

| ; PRODH:PRODL                                                                          |            |

| MOVF PRODL, W ;                                                                        |            |

| ADDWF RES1, F ; Add cross                                                              |            |

| MOVF PRODH, W ; products                                                               |            |

| ADDWFC RES2, F ;                                                                       |            |

| CLRF WREG ;                                                                            |            |

| ADDWFC RES3, F ;                                                                       |            |

| ;                                                                                      |            |

| BTFSS ARG2H, 7 ; ARG2H:ARG2L neg                                                       | <b>a</b> ? |

| BRA SIGN_ARG1 ; no, check ARG1                                                         |            |

| MOVF ARGIL, W ;                                                                        |            |

| SUBWF RES2 ;                                                                           |            |

| MOVF ARG1H, W ;                                                                        |            |

|                                                                                        |            |

| SUBWFB RES3                                                                            |            |

| ;                                                                                      |            |

| SIGN_ARG1                                                                              |            |

| BTFSS ARG1H, 7 ; ARG1H:ARG1L neg                                                       | g.5        |

| BRA CONT_CODE ; no, done                                                               |            |

| MOVF ARG2L, W ;                                                                        |            |

| SUBWF RES2 ;                                                                           |            |

| MOVF ARG2H, W ;                                                                        |            |

| SUBWFB RES3                                                                            |            |

| ;                                                                                      |            |

| CONT_CODE                                                                              |            |

| :                                                                                      |            |

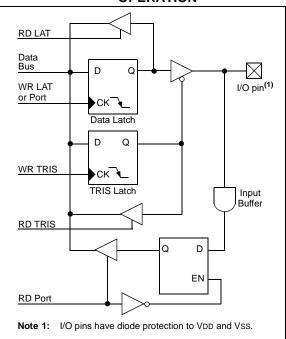

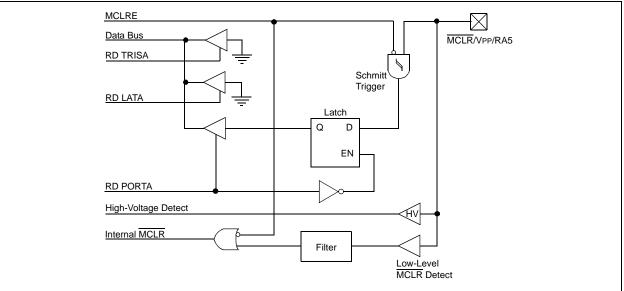

# 10.0 I/O PORTS

Depending on the device selected and features enabled, there are up to five ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (data direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (output latch)

The Data Latch (LATA) register is useful for read-modify-write operations on the value that the I/O pins are driving.

A simplified model of a generic I/O port without the interfaces to other peripherals is shown in Figure 10-1.

FIGURE 10-1: GENERIC I/O PORT OPERATION

# 10.1 PORTA, TRISA and LATA Registers

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch.

The Data Latch register (LATA) is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin.

The sixth pin of PORTA (MCLR/VPP/RA5) is an input only pin. Its operation is controlled by the MCLRE configuration bit in Configuration Register 3H (CONFIG3H<7>). When selected as a port pin (MCLRE = 0), it functions as a digital input only pin; as such, it does not have TRIS or LAT bits associated with its operation. Otherwise, it functions as the device's Master Clear input. In either configuration, RA5 also functions as the programming voltage input during programming.

| Note: | On a Power-on Reset, RA5 is enabled as a         |

|-------|--------------------------------------------------|

|       | digital input only if Master Clear functionality |

|       | is disabled.                                     |

|       |                                                  |

Pins RA6 and RA7 are multiplexed with the main oscillator pins; they are enabled as oscillator or I/O pins by the selection of the main oscillator in Configuration Register 1H (see **Section 19.1 "Configuration Bits"** for details). When they are not used as port pins, RA6 and RA7 and their associated TRIS and LAT bits are read as '0'.

The other PORTA pins are multiplexed with analog inputs, the analog VREF+ and VREF- inputs and the LVD input. The operation of pins RA3:RA0 as A/D converter inputs is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register 1).

The RA4/T0CKI pin is a Schmitt Trigger input and an open-drain output. All other PORTA pins have TTL input levels and full CMOS output drivers.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

#### EXAMPLE 10-1: INITIALIZING PORTA

|       | -      |                          |

|-------|--------|--------------------------|

| CLRF  | PORTA  | ; Initialize PORTA by    |

|       |        | ; clearing output        |

|       |        | ; data latches           |

| CLRF  | LATA   | ; Alternate method       |

|       |        | ; to clear output        |

|       |        | ; data latches           |

| MOVLW | 0x7F   | ; Configure A/D          |

| MOVWF | ADCON1 | ; for digital inputs     |

| MOVLW | 0xD0   | ; Value used to          |

|       |        | ; initialize data        |

|       |        | ; direction              |

| MOVWF | TRISA  | ; Set RA<3:0> as outputs |

|       |        | ; RA<7:4> as inputs      |

|       |        |                          |

**Note:** On a Power-on Reset, RA3:RA0 are configured as analog inputs and read as '0'. RA4 is always a digital pin.

#### TABLE 10-1: PORTA FUNCTIONS

| Name          | Bit#  | Buffer | Function                                                                                                                                      |

|---------------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| RA0/AN0       | bit 0 | ST     | Input/output port pin or analog input.                                                                                                        |

| RA1/AN1/LVDIN | bit 1 | ST     | Input/output port pin, analog input or Low-Voltage Detect input.                                                                              |

| RA2/AN2/VREF- | bit 2 | ST     | Input/output port pin, analog input or VREF                                                                                                   |

| RA3/AN3/VREF+ | bit 3 | ST     | Input/output port pin, analog input or VREF+.                                                                                                 |

| RA4/T0CKI     | bit 4 | ST     | Input/output port pin or external clock input for Timer0.<br>Output is open-drain type.                                                       |

| MCLR/Vpp/RA5  | bit 5 | ST     | Master Clear input or programming voltage input (if MCLR is enabled); input only port pin or programming voltage input (if MCLR is disabled). |

| OSC2/CLKO/RA6 | bit 6 | ST     | OSC2, clock output or I/O pin.                                                                                                                |

| OSC1/CLKI/RA7 | bit 7 | ST     | OSC1, clock input or I/O pin.                                                                                                                 |

**Legend:** TTL = TTL input, ST = Schmitt Trigger input

### TABLE 10-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Name   | Bit 7                 | Bit 6                 | Bit 5              | Bit 4    | Bit 3                         | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-----------------------|-----------------------|--------------------|----------|-------------------------------|-------|-------|-------|----------------------|---------------------------------|

| PORTA  | RA7 <sup>(1)</sup>    | RA6 <sup>(1)</sup>    | RA5 <sup>(2)</sup> | RA4      | RA3                           | RA2   | RA1   | RA0   | xx0x 0000            | uu0u 0000                       |

| LATA   | LATA7 <sup>(1)</sup>  | LATA6 <sup>(1)</sup>  | —                  | LATA Dat | ATA Data Output Register      |       |       |       |                      | uu-u uuuu                       |

| TRISA  | TRISA7 <sup>(1)</sup> | TRISA6 <sup>(1)</sup> | _                  | PORTA D  | PORTA Data Direction Register |       |       |       |                      | 11-1 1111                       |

| ADCON1 | _                     | PCFG6                 | PCFG5              | PCFG4    | PCFG3                         | PCFG2 | PCFG1 | PCFG0 | -000 0000            | -000 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

**Note 1:** RA7:RA6 and their associated latch and data direction bits are enabled as I/O pins based on oscillator configuration; otherwise, they are read as '0'.

2: RA5 is an input only if MCLR is disabled.

# 14.2 Timer1 Oscillator

The Timer1 oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. The oscillator is a lowpower oscillator rated for 32 kHz crystals. See **Section 12.2 "Timer1 Oscillator"** for further details.

# 14.3 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and rolls over to 0000h. The TMR3 interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled/disabled by setting/clearing TMR3 Interrupt Enable bit, TMR3IE (PIE2<1>).

# 14.4 Resetting Timer3 Using a CCP Trigger Output

If the CCP module is configured in Compare mode to generate a "special event trigger" (CCP1M3:CCP1M0 = 1011), this signal will reset Timer3. See **Section 15.4.4** "**Special Event Trigger**" for more information.

| Note: | The special event triggers from the CCP |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|--|--|

|       | module will not set interrupt flag bit, |  |  |  |  |  |  |  |  |

|       | TMR3IF (PIR1<0>).                       |  |  |  |  |  |  |  |  |

Timer3 must be configured for either Timer or Synchronized Counter mode to take advantage of this feature. If Timer3 is running in Asynchronous Counter mode, this Reset operation may not work. In the event that a write to Timer3 coincides with a special event trigger from CCP1, the write will take precedence. In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer3.

| Name   | Bit 7                                                                      | Bit 6         | Bit 5        | Bit 4         | Bit 3         | Bit 2      | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------------------------------------------------------------------------|---------------|--------------|---------------|---------------|------------|--------|-----------|----------------------|---------------------------------|

| INTCON | GIE/<br>GIEH                                                               | PEIE/<br>GIEL | TMR0IE       | INTOIE        | RBIE          | TMR0IF     | INT0IF | RBIF      | 0000 000x            | 0000 000u                       |

| PIR2   | OSCFIF                                                                     | —             | _            | EEIF          | _             | LVDIF      | TMR3IF | _         | 00 -00-              | 00 -00-                         |

| PIE2   | OSCFIE                                                                     | —             | _            | EEIE          | _             | LVDIE      | TMR3IE | _         | 00 -00-              | 00 -00-                         |

| IPR2   | OSCFIP                                                                     | —             | _            | EEIP          | _             | LVDIP      | TMR3IP | _         | 11 -11-              | 11 -11-                         |

| TMR3L  | Holding R                                                                  | egister for t | he Least Sig | gnificant Byt | e of the 16-b | it TMR3 Re | gister |           | xxxx xxxx            | uuuu uuuu                       |

| TMR3H  | Holding Register for the Most Significant Byte of the 16-bit TMR3 Register |               |              |               |               |            |        | xxxx xxxx | uuuu uuuu            |                                 |

| T1CON  | RD16                                                                       | T1RUN         | T1CKPS1      | T1CKPS0       | T1OSCEN       | T1SYNC     | TMR1CS | TMR10N    | 0000 0000            | u0uu uuuu                       |

| T3CON  | RD16                                                                       | _             | T3CKPS1      | T3CKPS0       | T3CCP1        | T3SYNC     | TMR3CS | TMR3ON    | 0-00 0000            | u-uu uuuu                       |

#### TABLE 14-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

# 17.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The Analog-to-Digital (A/D) converter module has seven inputs for the PIC18F1220/1320 devices. This module allows conversion of an analog input signal to a corresponding 10-bit digital number.

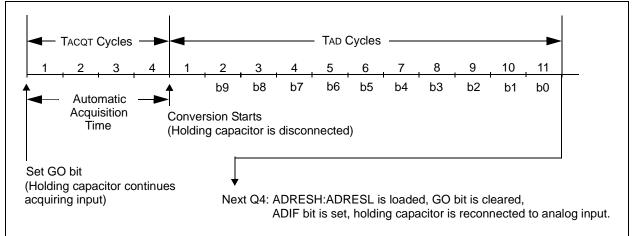

A new feature for the A/D converter is the addition of programmable acquisition time. This feature allows the user to select a new channel for conversion and to set the GO/DONE bit immediately. When the GO/DONE bit is set, the selected channel is sampled for the programmed acquisition time before a conversion is actually started. This removes the firmware overhead that may have been required to allow for an acquisition (sampling) period (see Register 17-3 and Section 17.3 "Selecting and Configuring Automatic Acquisition Time").

The module has five registers:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

- A/D Control Register 2 (ADCON2)

The ADCON0 register, shown in Register 17-1, controls the operation of the A/D module. The ADCON1 register, shown in Register 17-2, configures the functions of the port pins. The ADCON2 register, shown in Register 17-3, configures the A/D clock source, programmed acquisition time and justification.

# 17.7 A/D Conversions

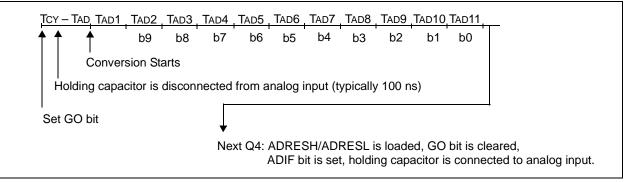

Figure 17-3 shows the operation of the A/D converter after the GO bit has been set and the ACQT2:ACQT0 bits are cleared. A conversion is started after the following instruction to allow entry into Low-Power Sleep mode before the conversion begins.

Figure 17-4 shows the operation of the A/D converter after the GO bit has been set and the ACQT2:ACQT0 bits are set to '010' and selecting a 4 TAD acquisition time before the conversion starts.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The A/D Result register pair will NOT be updated with the partially completed A/ D conversion sample. This means the ADRESH:ADRESL registers will continue to contain the value of the last completed conversion (or the last value written to the ADRESH:ADRESL registers).

After the A/D conversion is completed or aborted, a 2 TAD wait is required before the next acquisition can be started. After this wait, acquisition on the selected channel is automatically started.

Note: The GO/DONE bit should NOT be set in the same instruction that turns on the A/D.

### FIGURE 17-3: A/D CONVERSION TAD CYCLES (Acqt<2:0> = 000, Tacq = 0)

#### FIGURE 17-4: A/D CONVERSION TAD CYCLES (Acqt<2:0> = 010, Tacq = 4 TaD)

# 19.4 Fail-Safe Clock Monitor

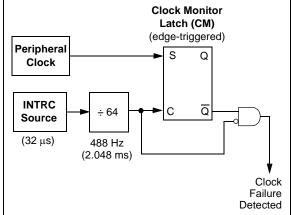

The Fail-Safe Clock Monitor (FSCM) allows the microcontroller to continue operation, in the event of an external oscillator failure, by automatically switching the system clock to the internal oscillator block. The FSCM function is enabled by setting the Fail-Safe Clock Monitor Enable bit, FSCM (CONFIG1H<6>).

When FSCM is enabled, the INTRC oscillator runs at all times to monitor clocks to peripherals and provide an instant backup clock in the event of a clock failure. Clock monitoring (shown in Figure 19-3) is accomplished by creating a sample clock signal, which is the INTRC output divided by 64. This allows ample time between FSCM sample clocks for a peripheral clock edge to occur. The peripheral system clock and the sample clock are presented as inputs to the Clock Monitor latch (CM). The CM is set on the falling edge of the system clock source, but cleared on the rising edge of the sample clock.

Clock failure is tested for on the falling edge of the sample clock. If a sample clock falling edge occurs while CM is still set, a clock failure has been detected (Figure 19-4). This causes the following:

- the FSCM generates an oscillator fail interrupt by setting bit, OSCFIF (PIR2<7>);

- the system clock source is switched to the internal oscillator block (OSCCON is not updated to show the current clock source – this is the Fail-Safe condition); and

- the WDT is reset.

Since the postscaler frequency from the internal oscillator block may not be sufficiently stable, it may be desirable to select another clock configuration and enter an alternate power managed mode (see Section 19.3.1 "Special Considerations for Using Two-Speed Start-up" and Section 3.1.3 "Multiple Sleep Commands" for more details). This can be done to attempt a partial recovery, or execute a controlled shutdown.

To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IFRC2:IFRC0, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting IFRC2:IFRC0 prior to entering Sleep mode.

Adjustments to the internal oscillator block, using the OSCTUNE register, also affect the period of the FSCM by the same factor. This can usually be neglected, as the clock frequency being monitored is generally much higher than the sample clock frequency.

The FSCM will detect failures of the primary or secondary clock sources only. If the internal oscillator block fails, no failure would be detected, nor would any action be possible.

#### 19.4.1 FSCM AND THE WATCHDOG TIMER

Both the FSCM and the WDT are clocked by the INTRC oscillator. Since the WDT operates with a separate divider and counter, disabling the WDT has no effect on the operation of the INTRC oscillator when the FSCM is enabled.

As already noted, the clock source is switched to the INTOSC clock when a clock failure is detected. Depending on the frequency selected by the IRCF2:IRCF0 bits, this may mean a substantial change in the speed of code execution. If the WDT is enabled with a small prescale value, a decrease in clock speed allows a WDT time-out to occur and a subsequent device Reset. For this reason, Fail-Safe Clock events also reset the WDT and postscaler, allowing it to start timing from when execution speed was changed and decreasing the likelihood of an erroneous time-out.

| DAW                 | Decimal A                                                                       | Decimal Adjust W Register                                                                                            |                                                                                           |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:             | [label] D                                                                       | WAW                                                                                                                  |                                                                                           |  |  |  |  |

| Operands:           | None                                                                            | None                                                                                                                 |                                                                                           |  |  |  |  |

| Operation:          | (W<3:0>)<br>else                                                                | If $[W<3:0> > 9]$ or $[DC = 1]$ then<br>(W<3:0>) + 6 $\rightarrow$ W<3:0>;<br>else<br>(W<3:0>) $\rightarrow$ W<3:0>; |                                                                                           |  |  |  |  |

| Status Affected:    | (W<7:4>)<br>else                                                                | > 9] or [C =<br>+ 6 → W<7:4<br>→ W<7:4>;                                                                             |                                                                                           |  |  |  |  |

| Encoding:           | 0000                                                                            | 0000 000                                                                                                             | 00 0111                                                                                   |  |  |  |  |

| Description:        | DAW adjus<br>resulting fr<br>two variab<br>format) an<br>packed BC<br>may be se | ests the 8-bit work of the earlied les (each in produces a CD result. The toy DAW regard or to the DAW               | value in W,<br>er addition of<br>backed BCD<br>a correct<br>e Carry bit<br>ardless of its |  |  |  |  |

| Words:              | 1                                                                               |                                                                                                                      |                                                                                           |  |  |  |  |

| Cycles:             | 1                                                                               |                                                                                                                      |                                                                                           |  |  |  |  |

| Q Cycle Activity:   |                                                                                 |                                                                                                                      |                                                                                           |  |  |  |  |

| Q1                  | Q2                                                                              | Q3                                                                                                                   | Q4                                                                                        |  |  |  |  |

| Decode              | Read<br>register W                                                              | Process<br>Data                                                                                                      | Write<br>W                                                                                |  |  |  |  |

| Example 1:          | DAW                                                                             |                                                                                                                      |                                                                                           |  |  |  |  |

| Before Instru       |                                                                                 |                                                                                                                      |                                                                                           |  |  |  |  |

| W<br>C              | = 0xA5<br>= 0                                                                   |                                                                                                                      |                                                                                           |  |  |  |  |

| DC                  | = 0                                                                             |                                                                                                                      |                                                                                           |  |  |  |  |

| After Instruct<br>W | ion<br>= 0x05                                                                   |                                                                                                                      |                                                                                           |  |  |  |  |

| C<br>DC             | = 1<br>= 0                                                                      |                                                                                                                      |                                                                                           |  |  |  |  |

| Example 2:          | - 0                                                                             |                                                                                                                      |                                                                                           |  |  |  |  |

| Before Instruction  |                                                                                 |                                                                                                                      |                                                                                           |  |  |  |  |

| W                   | = 0xCE                                                                          |                                                                                                                      |                                                                                           |  |  |  |  |

| C<br>DC             | = 0<br>= 0                                                                      |                                                                                                                      |                                                                                           |  |  |  |  |

| After Instruct      | tion                                                                            |                                                                                                                      |                                                                                           |  |  |  |  |

| W<br>C<br>DC        | = 0x34<br>= 1<br>= 0                                                            |                                                                                                                      |                                                                                           |  |  |  |  |

|                     |                                                                                 |                                                                                                                      |                                                                                           |  |  |  |  |

| DECF        | CF Decrement f |                                                                                                                                                                                                                                                                                                                  |                                   |      |      |  |  |  |  |

|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------|------|--|--|--|--|

| Syntax:     |                | [ label ]                                                                                                                                                                                                                                                                                                        | [ <i>label</i> ] DECF f [,d [,a]] |      |      |  |  |  |  |

| Operands:   |                | $0 \le f \le 25$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                               |                                   |      |      |  |  |  |  |

| Operation:  |                | (f) – 1 $\rightarrow$                                                                                                                                                                                                                                                                                            | dest                              |      |      |  |  |  |  |

| Status Affe | cted:          | C, DC, N                                                                                                                                                                                                                                                                                                         | , OV, Z                           |      |      |  |  |  |  |

| Encoding:   |                | 0000                                                                                                                                                                                                                                                                                                             | 01da                              | ffff | ffff |  |  |  |  |

| Description |                | Decrement register 'f'. If 'd' is '0',<br>the result is stored in W. If 'd' is '1',<br>the result is stored back in register<br>'f' (default). If 'a' is '0', the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' = 1, then the<br>bank will be selected as per the<br>BSR value (default). |                                   |      |      |  |  |  |  |

| Words:      |                | 1                                                                                                                                                                                                                                                                                                                |                                   |      |      |  |  |  |  |

| Cycles:     |                | 1                                                                                                                                                                                                                                                                                                                |                                   |      |      |  |  |  |  |

| Q Cycle A   | ctivity:       |                                                                                                                                                                                                                                                                                                                  |                                   |      |      |  |  |  |  |

| Q           | 1              | Q2                                                                                                                                                                                                                                                                                                               | Q3                                | }    | Q4   |  |  |  |  |

| Dece        | ode            | ReadProcessWrite toregister 'f'Datadestination                                                                                                                                                                                                                                                                   |                                   |      |      |  |  |  |  |

| Example:    | Inotr          | DECF                                                                                                                                                                                                                                                                                                             | CNT                               |      |      |  |  |  |  |

$\begin{array}{rrrr} Before Instruction \\ CNT & = & 0 \\ Z & = & 0 \\ \\ After Instruction \\ CNT & = & 0 \\ Z & = & 1 \end{array}$

| IORLW         |         | Inc   | Inclusive OR literal with W |                                |     |      |           |  |  |

|---------------|---------|-------|-----------------------------|--------------------------------|-----|------|-----------|--|--|

| Syntax:       |         | [ la  | bel]                        | IORLW                          | k   |      |           |  |  |

| Operands:     |         | 0≤    | k ≤ 25                      | 55                             |     |      |           |  |  |

| Operation:    |         | (W)   | ) .OR.                      | $k \rightarrow W$              |     |      |           |  |  |

| Status Affect | ted:    | Ν, Ι  | Z                           |                                |     |      |           |  |  |

| Encoding:     |         | C     | 000                         | 1001                           | kk} | ck   | kkkk      |  |  |

| Description:  |         | the   |                             | ents of W<br>iteral 'k'.<br>W. |     | •••• |           |  |  |

| Words:        |         | 1     |                             |                                |     |      |           |  |  |

| Cycles:       |         | 1     |                             |                                |     |      |           |  |  |

| Q Cycle Ac    | tivity: |       |                             |                                |     |      |           |  |  |

| Q1            |         | (     | Q2                          | Q3                             |     | Q4   |           |  |  |

| Deco          | de      |       | ead<br>ral 'k'              | Proce<br>Dat                   |     | Wi   | rite to W |  |  |

| Example:      |         | IOF   | RTM                         | 0x35                           |     |      |           |  |  |

| Before        | Instru  | ction |                             |                                |     |      |           |  |  |

| W             |         | =     | 0x9A                        |                                |     |      |           |  |  |

| After In      | struct  | ion   |                             |                                |     |      |           |  |  |

| W             |         | =     | 0xBF                        |                                |     |      |           |  |  |

|               |         |       |                             |                                |     |      |           |  |  |

| IORWF                    | Inclusive                                                                                                                                                                                                                                                             | Inclusive OR W with f |                      |  |  |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|--|--|--|--|

| Syntax:                  | [ label ]                                                                                                                                                                                                                                                             | IORWF f               | [,d [,a]]            |  |  |  |  |

| Operands:                | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                 | 5                     |                      |  |  |  |  |

| Operation:               | Operation: (W) .OR. (f) $\rightarrow$ dest                                                                                                                                                                                                                            |                       |                      |  |  |  |  |

| Status Affected:         |                                                                                                                                                                                                                                                                       |                       |                      |  |  |  |  |

| Encoding:                | 0001                                                                                                                                                                                                                                                                  | 00da ff               | ff ffff              |  |  |  |  |

|                          | 'd' is '0', the result is placed in W<br>'d' is '1', the result is placed back<br>register 'f' (default). If 'a' is '0', th<br>Access Bank will be selected, ov<br>riding the BSR value. If 'a' = 1, th<br>the bank will be selected as per t<br>BSR value (default). |                       |                      |  |  |  |  |

| Words:                   | 1                                                                                                                                                                                                                                                                     |                       |                      |  |  |  |  |

| Cycles:                  | 1                                                                                                                                                                                                                                                                     |                       |                      |  |  |  |  |

| Q Cycle Activity         | :                                                                                                                                                                                                                                                                     |                       |                      |  |  |  |  |

| Q1                       | Q2                                                                                                                                                                                                                                                                    | Q3                    | Q4                   |  |  |  |  |

| Decode                   | Read<br>register 'f'                                                                                                                                                                                                                                                  | Process<br>Data       | Write to destination |  |  |  |  |

| Example: IORWF RESULT, W |                                                                                                                                                                                                                                                                       |                       |                      |  |  |  |  |

Before Instruction RESULT = 0x13 W = 0x91

After Instruction  $\begin{array}{rcl} \mathsf{RESULT} &= & 0x13 \\ \mathsf{W} &= & 0x93 \end{array}$

$\ensuremath{\textcircled{}^{\odot}}$  2002-2015 Microchip Technology Inc.

| RCA   | LL             | Relative Call                                                                                |                                                                                   |                                                                                             |  |  |  |  |  |  |

|-------|----------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Synt  | ax:            | [ <i>label</i> ] R                                                                           | CALL n                                                                            |                                                                                             |  |  |  |  |  |  |

| Ope   | rands:         | -1024 ≤ n                                                                                    | ≤ 1023                                                                            |                                                                                             |  |  |  |  |  |  |

| Ope   | ration:        | (PC) + 2 -<br>(PC) + 2 +                                                                     |                                                                                   |                                                                                             |  |  |  |  |  |  |

| Statu | us Affected:   | None                                                                                         |                                                                                   |                                                                                             |  |  |  |  |  |  |

| Enco  | oding:         | 1101                                                                                         | 1nnn nn:                                                                          | nn nnnn                                                                                     |  |  |  |  |  |  |

| Dest  | cription:      | from the c<br>return add<br>onto the s<br>compleme<br>Since the<br>to fetch the<br>address w | urrent locatio<br>Iress (PC + 2<br>tack. Then, a<br>ent number '2<br>PC will have | 2) is pushed<br>add the 2's<br>2n' to the PC.<br>incremented<br>tion, the new<br>+ 2n. This |  |  |  |  |  |  |

| Wore  | ds:            | 1                                                                                            |                                                                                   |                                                                                             |  |  |  |  |  |  |

| Cycl  | es:            | 2                                                                                            | 2                                                                                 |                                                                                             |  |  |  |  |  |  |

| QC    | ycle Activity: |                                                                                              |                                                                                   |                                                                                             |  |  |  |  |  |  |

|       | Q1             | Q2                                                                                           | Q3                                                                                | Q4                                                                                          |  |  |  |  |  |  |

|       | Decode         | Read literal<br>'n'                                                                          | Process<br>Data                                                                   | Write to PC                                                                                 |  |  |  |  |  |  |

| RES   | ET              | Reset     |                                                                      |       |          |  |  |  |

|-------|-----------------|-----------|----------------------------------------------------------------------|-------|----------|--|--|--|

| Synt  | ax:             | [ label ] | RESET                                                                |       |          |  |  |  |

| Ope   | rands:          | None      |                                                                      |       |          |  |  |  |

| Ope   | ration:         |           | Reset all registers and flags that are affected by a MCLR Reset.     |       |          |  |  |  |

| State | us Affected:    | All       |                                                                      |       |          |  |  |  |

| Enco  | oding:          | 0000      | 0000                                                                 | 1111  | 1111     |  |  |  |

| Des   | cription:       |           | This instruction provides a way to execute a MCLR Reset in software. |       |          |  |  |  |

| Wor   | ds:             | 1         | 1                                                                    |       |          |  |  |  |

| Cycl  | es:             | 1         |                                                                      |       |          |  |  |  |

| QC    | cycle Activity: |           |                                                                      |       |          |  |  |  |

|       | Q1              | Q2        | Q3                                                                   |       | Q4       |  |  |  |

|       | Decode          | Start     | No                                                                   |       | No       |  |  |  |

|       |                 | Reset     | operat                                                               | ion o | peration |  |  |  |

|       |                 |           |                                                                      |       |          |  |  |  |

Example: RESET

| After Instruction |             |

|-------------------|-------------|

| Registers =       | Reset Value |

| Flags* =          | Reset Value |

Example: HERE RCALL Jump

Push PC to stack

No

operation

No

operation

No

operation

**Before Instruction**

No

operation

PC = Address (HERE) After Instruction PC = Address (Jump) TOS = Address (HERE + 2)

# 22.2 DC Characteristics: Power-Down and Supply Current PIC18F1220/1320 (Industrial) PIC18LF1220/1320 (Industrial)

| PIC18LF1220/1320<br>(Industrial) |                                           | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |            |          |            |            |                                                      |  |  |  |

|----------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------|----------|------------|------------|------------------------------------------------------|--|--|--|

|                                  | PIC18F1220/1320<br>(Industrial, Extended) |                                                                                                                                    |            |          |            |            |                                                      |  |  |  |

| Param<br>No.                     | Device                                    | Тур.                                                                                                                               | Max.       | Units    | Conditions |            |                                                      |  |  |  |

|                                  | Power-Down Current (IPD)                  | (1)                                                                                                                                |            |          |            |            |                                                      |  |  |  |

|                                  | PIC18LF1220/1320                          | 0.1                                                                                                                                | 0.5        | μΑ       | -4         | O°C        |                                                      |  |  |  |

|                                  |                                           | 0.1                                                                                                                                | 0.5        | μΑ       | +2         | 5°C        | VDD = 2.0V,<br>( <b>Sleep</b> mode)                  |  |  |  |

|                                  |                                           | 0.2                                                                                                                                | 1.9        | μΑ       | +8         | 5°C        | ()                                                   |  |  |  |

|                                  | PIC18LF1220/1320                          | 0.1                                                                                                                                | 0.5        | μΑ       | -          | 0°C        | VDD = 3.0V,                                          |  |  |  |

|                                  |                                           | 0.1                                                                                                                                | 0.5        | μΑ       |            | 25°C       | ( <b>Sleep</b> mode)                                 |  |  |  |

|                                  |                                           | 0.3                                                                                                                                | 1.9        | μA       |            | 5°C        |                                                      |  |  |  |

|                                  | All devices                               | 0.1                                                                                                                                | 2.0        | μA       | -          | 0°C        |                                                      |  |  |  |

|                                  |                                           | 0.1                                                                                                                                | 2.0<br>6.5 | μA       |            | 5°C        | VDD = 5.0V,<br>( <b>Sleep</b> mode)                  |  |  |  |

|                                  | Extended devices                          | 0.4                                                                                                                                | 6.5<br>50  | μΑ<br>μΑ |            | 25°C       | (Oleep mode)                                         |  |  |  |

|                                  | Supply Current (IDD) <sup>(2,3)</sup>     | 11.2                                                                                                                               | 50         | μΛ       | +12        | 20 0       |                                                      |  |  |  |

|                                  | PIC18LF1220/1320                          | 8                                                                                                                                  | 40         | μA       | -40°C      |            |                                                      |  |  |  |

|                                  |                                           | 9                                                                                                                                  | 40         | μΑ       | +25°C      | VDD = 2.0V |                                                      |  |  |  |

|                                  |                                           | 11                                                                                                                                 | 40         | μA       | +85°C      |            |                                                      |  |  |  |

|                                  | PIC18LF1220/1320                          | 25                                                                                                                                 | 68         | μΑ       | -40°C      |            |                                                      |  |  |  |

|                                  |                                           | 25                                                                                                                                 | 68         | μA       | +25°C      | VDD = 3.0V | Fosc = 31 kHz                                        |  |  |  |

|                                  |                                           | 20                                                                                                                                 | 68         | μΑ       | +85°C      |            | ( <b>RC_RUN</b> mode,<br>Internal oscillator source) |  |  |  |

|                                  | All devices                               | 55                                                                                                                                 | 80         | μΑ       | -40°C      |            | ,                                                    |  |  |  |

|                                  |                                           | 55                                                                                                                                 | 80         | μΑ       | +25°C      | VDD = 5.0V |                                                      |  |  |  |

|                                  |                                           | 50                                                                                                                                 | 80         | μΑ       | +85°C      | 100 - 0.01 |                                                      |  |  |  |

|                                  | Extended devices                          | 50                                                                                                                                 | 80         | μΑ       | +125°C     |            |                                                      |  |  |  |

Legend: Shading of rows is to assist in readability of the table.

**Note 1:** The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or VSS and all features that add delta current disabled (such as WDT, Timer1 Oscillator, BOR, etc.).

2: The supply current is mainly a function of operating voltage, frequency and mode. Other factors, such as I/O pin loading and switching rate, oscillator type and circuit, internal code execution pattern and temperature, also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD;

MCLR = VDD; WDT enabled/disabled as specified.