Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 7x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf1320-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

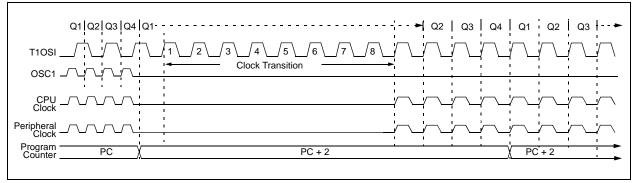

## 2.7.2 OSCILLATOR TRANSITIONS

The PIC18F1220/1320 devices contain circuitry to prevent clocking "glitches" when switching between clock sources. A short pause in the system clock occurs during the clock switch. The length of this pause is between eight and nine clock periods of the new clock source. This ensures that the new clock source is stable and that its pulse width will not be less than the shortest pulse width of the two clock sources.

Clock transitions are discussed in greater detail in **Section 3.1.2 "Entering Power Managed Modes"**.

## 2.8 Effects of Power Managed Modes on the Various Clock Sources

When the device executes a SLEEP instruction, the system is switched to one of the power managed modes, depending on the state of the IDLEN and SCS1:SCS0 bits of the OSCCON register. See **Section 3.0 "Power Managed Modes"** for details.

When PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power managed modes, the oscillator using the OSC1 pin is disabled. The OSC1 pin (and OSC2 pin, if used by the oscillator) will stop oscillating.

In Secondary Clock modes (SEC\_RUN and SEC\_I-DLE), the Timer1 oscillator is operating and providing the system clock. The Timer1 oscillator may also run in all power managed modes if required to clock Timer1 or Timer3.

In Internal Oscillator modes (RC\_RUN and RC\_IDLE), the internal oscillator block provides the system clock source. The INTRC output can be used directly to provide the system clock and may be enabled to support various special features, regardless of the power managed mode (see Section 19.2 "Watchdog Timer (WDT)" through Section 19.4 "Fail-Safe Clock Monitor"). The INTOSC output at 8 MHz may be used directly to clock the system, or may be divided down first. The INTOSC output is disabled if the system clock is provided directly from the INTRC output. If the Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The INTRC is required to support WDT operation. The Timer1 oscillator may be operating to support a realtime clock. Other features may be operating that do not require a system clock source (i.e., INTn pins, A/D conversions and others).

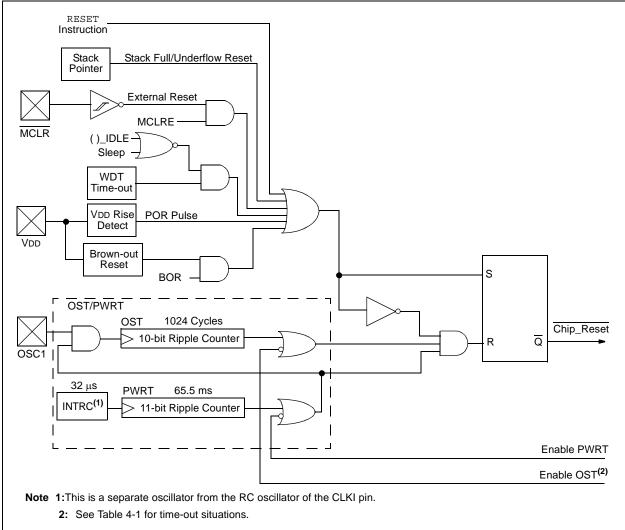

## 2.9 Power-up Delays

Power-up delays are controlled by two timers, so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see Sections 4.1 through 4.5.

The first timer is the Power-up Timer (PWRT), which provides a fixed delay on power-up (parameter 33, Table 22-8) if enabled in Configuration Register 2L. The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (LP, XT and HS modes). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

When the HSPLL Oscillator mode is selected, the device is kept in Reset for an additional 2 ms following the HS mode OST delay, so the PLL can lock to the incoming clock frequency.

There is a delay of 5 to 10  $\mu s$  following POR while the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the EC, RC or INTIO modes are used as the primary clock source.

| Oscillator Mode | OSC1 Pin                                              | OSC2 Pin                                              |

|-----------------|-------------------------------------------------------|-------------------------------------------------------|

| RC, INTIO1      | Floating, external resistor should pull high          | At logic low (clock/4 output)                         |

| RCIO, INTIO2    | Floating, external resistor should pull high          | Configured as PORTA, bit 6                            |

| ECIO            | Floating, pulled by external clock                    | Configured as PORTA, bit 6                            |

| EC              | Floating, pulled by external clock                    | At logic low (clock/4 output)                         |

| LP, XT and HS   | Feedback inverter disabled at quiescent voltage level | Feedback inverter disabled at quiescent voltage level |

TABLE 2-3:

OSC1 AND OSC2 PIN STATES IN SLEEP MODE

**Note:** See Table 4-1 in **Section 4.0** "**Reset**" for time-outs due to Sleep and MCLR Reset.

## 3.4 Run Modes

If the IDLEN bit is clear when a SLEEP instruction is executed, the CPU and peripherals are both clocked from the source selected using the SCS1:SCS0 bits. While these operating modes may not afford the power conservation of Idle or Sleep modes, they do allow the device to continue executing instructions by using a lower frequency clock source. RC\_RUN mode also offers the possibility of executing code at a frequency greater than the primary clock.

Wake-up from a power managed Run mode can be triggered by an interrupt, or any Reset, to return to fullpower operation. As the CPU is executing code in Run modes, several additional exits from Run modes are possible. They include exit to Sleep mode, exit to a corresponding Idle mode and exit by executing a RESET instruction. While the device is in any of the power managed Run modes, a WDT time-out will result in a WDT Reset.

### 3.4.1 PRI\_RUN MODE

The PRI\_RUN mode is the normal full-power execution mode. If the SLEEP instruction is never executed, the microcontroller operates in this mode (a SLEEP instruction is executed to enter all other power managed modes). All other power managed modes exit to PRI\_RUN mode when an interrupt or WDT time-out occur.

There is no entry to PRI\_RUN mode. The OSTS bit is set. The IOFS bit may be set if the internal oscillator block is the primary clock source (see **Section 2.7.1** "Oscillator Control Register").

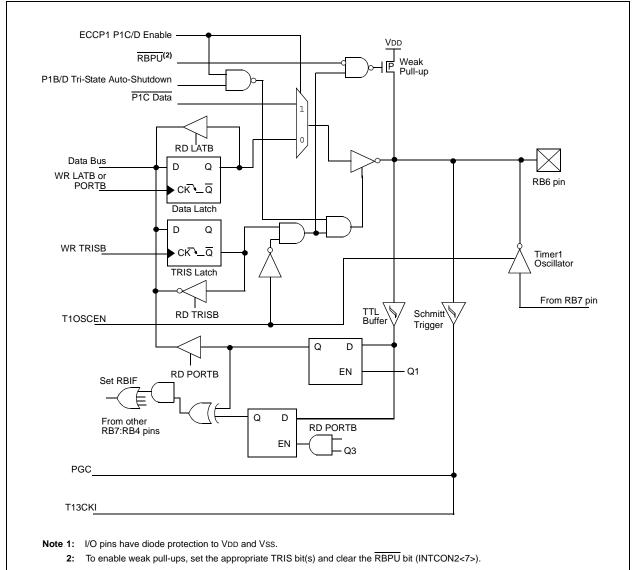

#### 3.4.2 SEC\_RUN MODE

The SEC\_RUN mode is the compatible mode to the "clock switching" feature offered in other PIC18 devices. In this mode, the CPU and peripherals are clocked from the Timer1 oscillator. This gives users the option of lower power consumption while still using a high accuracy clock source.

SEC\_RUN mode is entered by clearing the IDLEN bit, setting SCS1:SCS0 = 01 and executing a SLEEP instruction. The system clock source is switched to the Timer1 oscillator (see Figure 3-9), the primary oscillator is shut down, the T1RUN bit (T1CON<6>) is set and the OSTS bit is cleared.

Note: The Timer1 oscillator should already be running prior to entering SEC\_RUN mode. If the T1OSCEN bit is not set when the SLEEP instruction is executed, the SLEEP instruction will be ignored and entry to SEC\_RUN mode will not occur. If the Timer1 oscillator is enabled, but not yet running, system clocks will be delayed until the oscillator has started; in such situations, initial oscillator operation is far from stable and unpredictable operation may result.

When a wake event occurs, the peripherals and CPU continue to be clocked from the Timer1 oscillator while the primary clock is started. When the primary clock becomes ready, a clock switchback to the primary clock occurs (see Figure 3-6). When the clock switch is complete, the T1RUN bit is cleared, the OSTS bit is set and the primary clock is providing the system clock. The IDLEN and SCS bits are not affected by the wake-up. The Timer1 oscillator continues to run.

Firmware can force an exit from SEC\_RUN mode. By clearing the T1OSCEN bit (T1CON<3>), an exit from SEC\_RUN back to normal full-power operation is triggered. The Timer1 oscillator will continue to run and provide the system clock, even though the T1OSCEN bit is cleared. The primary clock is started. When the primary clock becomes ready, a clock switchback to the primary clock occurs (see Figure 3-6). When the clock switch is cleared, the Timer1 oscillator is disabled, the T1RUN bit is cleared, the OSTS bit is set and the primary clock is providing the system clock. The IDLEN and SCS bits are not affected by the wake-up.

## FIGURE 3-9: TIMING TRANSITION FOR ENTRY TO SEC\_RUN MODE

### 3.5.2 EXIT BY RESET

Normally, the device is held in Reset by the Oscillator Start-up Timer (OST) until the primary clock (defined in Configuration Register 1H) becomes ready. At that time, the OSTS bit is set and the device begins executing code.

Code execution can begin before the primary clock becomes ready. If either the Two-Speed Start-up (see Section 19.3 "Two-Speed Start-up") or Fail-Safe Clock Monitor (see Section 19.4 "Fail-Safe Clock Monitor") are enabled in Configuration Register 1H, the device may begin execution as soon as the Reset source has cleared. Execution is clocked by the INTOSC multiplexer driven by the internal oscillator block. Since the OSCCON register is cleared following all Resets, the INTRC clock source is selected. A higher speed clock may be selected by modifying the IRCF bits in the OSCCON register. Execution is clocked by the internal oscillator block until either the primary clock becomes ready, or a power managed mode is entered before the primary clock becomes ready; the primary clock is then shut down.

#### 3.5.3 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions, depending on which power managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in a wake from the power managed mode (see Sections 3.2 through 3.4).

If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 19.2 "Watchdog Timer (WDT)").

The WDT timer and postscaler are cleared by executing a SLEEP or CLRWDT instruction, the loss of a currently selected clock source (if the Fail-Safe Clock Monitor is enabled) and modifying the IRCF bits in the OSCCON register if the internal oscillator block is the system clock source.

#### 3.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power managed modes do not invoke the OST at all. These are:

- PRI\_IDLE mode, where the primary clock source is not stopped; or

- the primary clock source is not any of LP, XT, HS or HSPLL modes.

In these cases, the primary clock source either does not require an oscillator start-up delay, since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (RC, EC and INTIO Oscillator modes).

However, a fixed delay (approximately  $10 \ \mu$ s) following the wake event is required when leaving Sleep and Idle modes. This delay is required for the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

## 3.6 INTOSC Frequency Drift

The factory calibrates the internal oscillator block output (INTOSC) for 8 MHz (see Table 22-6). However, this frequency may drift as VDD or temperature changes, which can affect the controller operation in a variety of ways.

It is possible to adjust the INTOSC frequency by modifying the value in the OSCTUNE register (Register 2-1). This has the side effect that the INTRC clock source frequency is also affected. However, the features that use the INTRC source often do not require an exact frequency. These features include the Fail-Safe Clock Monitor, the Watchdog Timer and the RC\_RUN/ RC\_IDLE modes when the INTRC clock source is selected.

Being able to adjust the INTOSC requires knowing when an adjustment is required, in which direction it should be made and in some cases, how large a change is needed. Three examples follow but other techniques may be used.

## 4.0 RESET

The PIC18F1220/1320 devices differentiate between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during Sleep

- d) Watchdog Timer (WDT) Reset (during execution)

- e) Programmable Brown-out Reset (BOR)

- f) RESET Instruction

- g) Stack Full Reset

- h) Stack Underflow Reset

Most registers are unaffected by a Reset. Their status is unknown on POR and unchanged by all other Resets. The other registers are forced to a "Reset state", depending on the type of Reset that occurred. Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register (Register 5-2), RI, TO, PD, POR and BOR, are set or cleared differently in different Reset situations, as indicated in Table 4-2. These bits are used in software to determine the nature of the Reset. See Table 4-3 for a full description of the Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 4-1.

The Enhanced MCU devices have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

The  $\overline{\text{MCLR}}$  pin is not driven low by any internal Resets, including the WDT.

The  $\overline{\text{MCLR}}$  input provided by the  $\overline{\text{MCLR}}$  pin can be disabled with the MCLRE bit in Configuration Register 3H (CONFIG3H<7>).

## 9.5 RCON Register

The RCON register contains bits used to determine the cause of the last Reset or wake-up from a low-power mode. RCON also contains the bit that enables interrupt priorities (IPEN).

#### REGISTER 9-10: RCON: RESET CONTROL REGISTER

| R/W-0       | U-0 | U-0 | R/W-1 R-1 |    | R-1 | R-1 R/W-0 |     |  |  |

|-------------|-----|-----|-----------|----|-----|-----------|-----|--|--|

| IPEN        | —   | _   | RI        | TO | PD  | POR       | BOR |  |  |

| bit 7 bit 0 |     |     |           |    |     |           |     |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | <b>IPEN:</b> Interrupt Priority Enable bit<br>1 = Enable priority levels on interrupts<br>0 = Disable priority levels on interrupts (PIC16CXXX Compatibility mode) |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-5 | Unimplemented: Read as '0'                                                                                                                                         |

| bit 4   | RI: RESET Instruction Flag bit                                                                                                                                     |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

| bit 3   | TO: Watchdog Time-out Flag bit                                                                                                                                     |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

| bit 2   | PD: Power-down Detection Flag bit                                                                                                                                  |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

| bit 1   | POR: Power-on Reset Status bit                                                                                                                                     |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

| bit 0   | BOR: Brown-out Reset Status bit                                                                                                                                    |

|         | For details of bit operation, see Register 5-3.                                                                                                                    |

|         |                                                                                                                                                                    |

| TABLE 12-2: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER |

|-----------------------------------------------------------------|

|-----------------------------------------------------------------|

| Name   | Bit 7                                                                       | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-----------------------------------------------------------------------------|-----------|---------|---------|---------|--------|--------|-----------|----------------------|---------------------------------|

| INTCON | GIE/GIEH                                                                    | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF      | 0000 000x            | 0000 000u                       |

| PIR1   | _                                                                           | ADIF      | RCIF    | TXIF    | —       | CCP1IF | TMR2IF | TMR1IF    | -000 -000            | -000 -000                       |

| PIE1   | _                                                                           | ADIE      | RCIE    | TXIE    | —       | CCP1IE | TMR2IE | TMR1IE    | -000 -000            | -000 -000                       |

| IPR1   | _                                                                           | ADIP      | RCIP    | TXIP    | —       | CCP1IP | TMR2IP | TMR1IP    | -111 -111            | -111 -111                       |

| TMR1L  | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |           |         |         |         |        |        | xxxx xxxx | uuuu uuuu            |                                 |

| TMR1H  | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |           |         |         |         |        |        |           | xxxx xxxx            | uuuu uuuu                       |

| T1CON  | RD16                                                                        | T1RUN     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N    | 0000 0000            | u0uu uuuu                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

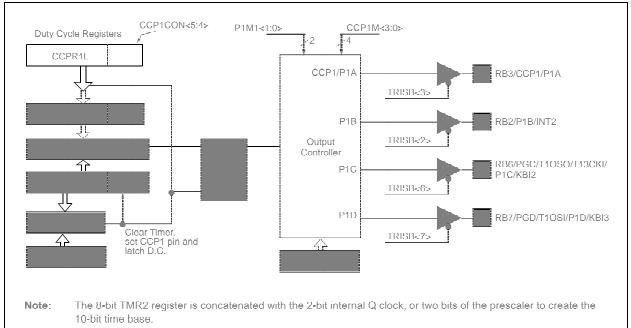

## 15.0 ENHANCED CAPTURE/ COMPARE/PWM (ECCP) MODULE

The Enhanced CCP module is implemented as a standard CCP module with Enhanced PWM capabilities. These capabilities allow for two or four output channels, user-selectable polarity, dead-band control and automatic shutdown and restart and are discussed in detail in **Section 15.5 "Enhanced PWM Mode"**.

The control register for CCP1 is shown in Register 15-1.

In addition to the expanded functions of the CCP1CON register, the ECCP module has two additional registers associated with Enhanced PWM operation and auto-shutdown features:

- PWM1CON

- ECCPAS

### **REGISTER 15-1: CCP1CON REGISTER FOR ENHANCED CCP OPERATION**

| R/W-0/0 | U-0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|------|---------|---------|---------|---------|---------|---------|

| P1M1    | P1M0 | DC1B1   | DC1B0   | CCP1M3  | CCP1M2  | CCP1M1  | CCP1M0  |

| bit 7   |      |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | P1M<1:0>: PWM Output Configuration bits                                                                                 |

|---------|-------------------------------------------------------------------------------------------------------------------------|

|         | I <u>f CCP1M&lt;3:2&gt; = 00, 01, 10:</u>                                                                               |

|         | xx = P1A assigned as Capture/Compare input; P1B, P1C, P1D assigned as port pins                                         |

|         | <u>If CCP1M&lt;3:2&gt; = 11:</u>                                                                                        |

|         | 00 = Single output; P1A modulated; P1B, P1C, P1D assigned as port pins                                                  |

|         | 01 = Full-bridge output forward; P1D modulated; P1A active; P1B, P1C inactive                                           |

|         | 10 = Half-bridge output; P1A, P1B modulated with dead-band control; P1C, P1D assigned as                                |

|         | port pins                                                                                                               |

|         | 11 = Full-bridge output reverse; P1B modulated; P1C active; P1A, P1D inactive                                           |

| bit 5-4 | DC1B<1:0>: PWM Duty Cycle Least Significant bits                                                                        |

|         | Capture mode:                                                                                                           |

|         | Unused.                                                                                                                 |

|         | Compare mode:                                                                                                           |

|         | Unused.                                                                                                                 |

|         | PWM mode:                                                                                                               |

|         | These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPR1L.                                  |

| bit 3-0 | CCP1M<3:0>: ECCP1 Mode Select bits                                                                                      |

|         | 0000 = Capture/Compare/PWM off (resets ECCP module)                                                                     |

|         | 0001 = Unused (reserved)                                                                                                |

|         | 0010 = Compare mode, toggle output on match (ECCP1IF bit is set)                                                        |

|         | 0011 = Unused (reserved)                                                                                                |

|         | 0100 = Capture mode, every falling edge                                                                                 |

|         | 0101 = Capture mode, every rising edge                                                                                  |

|         | 0110 = Capture mode, every 4th rising edge                                                                              |

|         | 0111 = Capture mode, every 16th rising edge                                                                             |

|         | 1000 = Compare mode, set output on match (ECCP1IF bit is set)                                                           |

|         | 1001 = Compare mode, clear output on match (ECCP1IF bit is set)                                                         |

|         | 1010 = Compare mode, generate software interrupt on match (ECCP1IF bit is set,                                          |

|         | ECCP1 pin returns to port pin operation)                                                                                |

|         | 1011 = Compare mode, trigger special event (ECCP1IF bit is set; ECCP resets TMR1 or                                     |

|         | TMR3 and starts an A/D conversion if the A/D module is enabled)                                                         |

|         | 1100 = PWM mode; P1A, P1C active-high; P1B, P1D active-high                                                             |

|         | 1101 = PWM mode; P1A, P1C active-high; P1B, P1D active-low                                                              |

|         | 1110 = PWM mode; P1A, P1C active-low; P1B, P1D active-high<br>1111 = PWM mode; P1A, P1C active-low; P1B, P1D active-low |

|         | TTTT - F VIVI HIDDE, F IA, F IC ACTIVE-IOW, F ID, F ID ACTIVE-IOW                                                       |

#### FIGURE 15-3: SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODULE

|    | CCP1CON<7:6>           | SIGNAL        | 0 Duty               | PR2+1                |

|----|------------------------|---------------|----------------------|----------------------|

|    |                        |               | Cycle                | – Period –           |

| 00 | (Single Output)        | P1A Modulated | Delay <sup>(1)</sup> | Delay <sup>(1)</sup> |

|    |                        | P1A Modulated |                      |                      |

| 10 | (Half-Bridge)          | P1B Modulated |                      |                      |

|    |                        | P1A Active    |                      |                      |

| 01 | (Full-Bridge,          | P1B Inactive  |                      |                      |

| UI | <sup>01</sup> Forward) | P1C Inactive  |                      |                      |

|    |                        | P1D Modulated | İ                    | -ii                  |

|    |                        | P1A Inactive  |                      |                      |

| 11 | (Full-Bridge,          | P1B Modulated |                      |                      |

| ΤT | Reverse)               | P1C Active    |                      | 1 1<br>1 1<br>1 1    |

|    |                        | P1D Inactive  |                      |                      |

|    |                        |               |                      |                      |

## 15.5.9 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the ECCP1 module for PWM operation:

- 1. Configure the PWM pins P1A and P1B (and P1C and P1D, if used) as inputs by setting the corresponding TRISB bits.

- 2. Set the PWM period by loading the PR2 register.

- Configure the ECCP module for the desired PWM mode and configuration by loading the CCP1CON register with the appropriate values:

- Select one of the available output configurations and direction with the P1M1:P1M0 bits.

- Select the polarities of the PWM output signals with the CCP1M3:CCP1M0 bits.

- 4. Set the PWM duty cycle by loading the CCPR1L register and CCP1CON<5:4> bits.

- 5. For Half-Bridge Output mode, set the deadband delay by loading PWM1CON<6:0> with the appropriate value.

- 6. If auto-shutdown operation is required, load the ECCPAS register:

- Select the auto-shutdown sources using the ECCPAS<2:0> bits.

- Select the shutdown states of the PWM output pins using PSSAC1:PSSAC0 and PSSBD1:PSSBD0 bits.

- Set the ECCPASE bit (ECCPAS<7>).

- 7. If auto-restart operation is required, set the PRSEN bit (PWM1CON<7>).

- 8. Configure and start TMR2:

- Clear the TMR2 interrupt flag bit by clearing the TMR2IF bit (PIR1<1>).

- Set the TMR2 prescale value by loading the T2CKPS bits (T2CON<1:0>).

- Enable Timer2 by setting the TMR2ON bit (T2CON<2>).

- 9. Enable PWM outputs after a new PWM cycle has started:

- Wait until TMR2 overflows (TMR2IF bit is set).

- Enable the CCP1/P1A, P1B, P1C and/or P1D pin outputs by clearing the respective TRISB bits.

- Clear the ECCPASE bit (ECCPAS<7>).

### 15.5.10 OPERATION IN LOW-POWER MODES

In the Low-Power Sleep mode, all clock sources are disabled. Timer2 will not increment and the state of the module will not change. If the ECCP pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state. If Two-Speed Start-ups are enabled, the initial start-up frequency may not be stable if the INTOSC is being used.

In PRI\_IDLE mode, the primary clock will continue to clock the ECCP module without change.

In all other low-power modes, the selected low-power mode clock will clock Timer2. Other low-power mode clocks will most likely be different than the primary clock frequency.

#### 15.5.10.1 Operation with Fail-Safe Clock Monitor

If the Fail-Safe Clock Monitor is enabled (CONFIG1H<6> is programmed), a clock failure will force the device into the Low-Power RC\_RUN mode and the OSCFIF bit (PIR2<7>) will be set. The ECCP will then be clocked from the INTRC clock source, which may have a different clock frequency than the primary clock. By loading the IRCF2:IRCF0 bits on Resets, the user can enable the INTOSC at a high clock speed in the event of a clock failure.

See the previous section for additional details.

#### 15.5.11 EFFECTS OF A RESET

Both power-on and subsequent Resets will force all ports to input mode and the CCP registers to their Reset states.

This forces the Enhanced CCP module to reset to a state compatible with the standard CCP module.

| Name    | Bit 7                                   | Bit 6         | Bit 5     | Bit 4        | Bit 3     | Bit 2  | Bit 1    | Bit 0       | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-----------------------------------------|---------------|-----------|--------------|-----------|--------|----------|-------------|----------------------|---------------------------------|

| INTCON  | GIE/GIEH                                | PEIE/GIEL     | TMR0IE    | INT0IE       | RBIE      | TMR0IF | INT0IF   | RBIF        | 0000 000:            | c 0000 000u                     |

| RCON    | IPEN                                    | -             | -         | RI           | TO        | PD     | POR      | BOR         | 01 11q               | q 0q qquu                       |

| PIR1    | _                                       | ADIF          | RCIF      | TXIF         | _         | CCP1IF | TMR2IF   | TMR1IF      | -000 -00             | 0 -000 -000                     |

| PIE1    | _                                       | ADIE          | RCIE      | TXIE         | _         | CCP1IE | TMR2IE   | TMR1IE      | -000 -00             | 0 -000 -000                     |

| IPR1    | - ADIP RCIP TXIP - CCP1IP TMR2IP TMR1IP |               |           |              |           |        | -111 -11 | L -111 -111 |                      |                                 |

| TMR2    | Timer2 Mo                               | dule Registe  | r         |              |           |        |          |             | 0000 000             | 0000 0000                       |

| PR2     | Timer2 Mo                               | dule Period I | Register  |              |           |        |          |             | 1111 111             | l 1111 1111                     |

| T2CON   | _                                       | TOUTPS3       | TOUTPS2   | TOUTPS1      | TOUTPS0   | TMR2ON | T2CKPS1  | T2CKPS0     | -000 000             | 0 -000 0000                     |

| TRISB   | PORTB Da                                | ta Direction  | Register  |              |           |        |          |             | 1111 111             | l 1111 1111                     |

| CCPR1H  | Enhanced                                | Capture/Con   | npare/PWM | Register 1 H | ligh Byte |        |          |             | XXXX XXX             | k uuuu uuuu                     |

| CCPR1L  | Enhanced                                | Capture/Con   | npare/PWM | Register 1 L | ow Byte   |        |          |             | XXXX XXX             | k uuuu uuuu                     |

| CCP1CON | P1M1                                    | P1M0          | DC1B1     | DC1B0        | CCP1M3    | CCP1M2 | CCP1M1   | CCP1M0      | 0000 000             | 0000 0000                       |

| ECCPAS  | ECCPASE                                 | ECCPAS2       | ECCPAS1   | ECCPAS0      | PSSAC1    | PSSAC0 | PSSBD1   | PSSBD0      | 0000 000             | 0000 0000                       |

| PWM1CON | PRSEN                                   | PDC6          | PDC5      | PDC4         | PDC3      | PDC2   | PDC1     | PDC0        | 0000 000             | ) uuuu uuuu                     |

| OSCCON  | IDLEN                                   | IRCF2         | IRCF1     | IRCF0        | OSTS      | IOFS   | SCS1     | SCS0        | 0000 qq0             | 000p qq00                       |

|  | TABLE 15-5: | REGISTERS ASSOCIATED WITH ENHANCED PWM AND TIMER2 |

|--|-------------|---------------------------------------------------|

|--|-------------|---------------------------------------------------|

$\label{eq:loss} \begin{array}{ll} \mbox{Legend:} & x = \mbox{unknown}, \mbox{u} = \mbox{unchanged}, \mbox{-} = \mbox{unimplemented}, \mbox{read as '0'}. \\ & \mbox{Shaded cells are not used by the ECCP module in Enhanced PWM mode}. \end{array}$

| U-0                                                                                         | R-1                                         | U-0                                                                              | R/W-0/0                         | R/W-0/0     | U-0              | R/W-0/0          | R/W-0/0        |  |

|---------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------|---------------------------------|-------------|------------------|------------------|----------------|--|

| —                                                                                           | RCIDL                                       | _                                                                                | SCKP                            | BRG16       | —                | WUE              | ABDEN          |  |

| bit 7                                                                                       |                                             |                                                                                  |                                 |             |                  |                  | bit 0          |  |

|                                                                                             |                                             |                                                                                  |                                 |             |                  |                  |                |  |

| Legend:                                                                                     |                                             |                                                                                  |                                 |             |                  |                  |                |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'                          |                                             |                                                                                  |                                 |             |                  |                  |                |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Rese |                                             |                                                                                  |                                 |             |                  |                  | ther Resets    |  |

| '1' = Bit is se                                                                             | et                                          | '0' = Bit is cle                                                                 | ared                            |             |                  |                  |                |  |

| bit 7                                                                                       | Unimplemen                                  | ted: Read as                                                                     | 0'                              |             |                  |                  |                |  |

| bit 6                                                                                       | =                                           | ive Operation                                                                    |                                 |             |                  |                  |                |  |

|                                                                                             | 1 = Receiver<br>0 = Receiver                | is Idle                                                                          |                                 |             |                  |                  |                |  |

| bit 5                                                                                       | Unimplemen                                  | ted: Read as                                                                     | 0'                              |             |                  |                  |                |  |

| bit 4                                                                                       | SCKP: Synchronous Clock Polarity Select bit |                                                                                  |                                 |             |                  |                  |                |  |

|                                                                                             | Asynchronous mode:<br>Unused in this mode.  |                                                                                  |                                 |             |                  |                  |                |  |

|                                                                                             |                                             | mode:<br>for clock (CK)<br>for clock (CK)                                        | •                               |             |                  |                  |                |  |

| bit 3                                                                                       | <b>BRG16:</b> 16-b                          | it Baud Rate F                                                                   | egister Enabl                   | e bit       |                  |                  |                |  |

|                                                                                             |                                             |                                                                                  |                                 | H and SPBRC |                  | RGH value igno   | bred           |  |

| bit 2                                                                                       | Unimplemen                                  | ted: Read as                                                                     | 0'                              |             |                  |                  |                |  |

| bit 1                                                                                       | WUE: Wake-                                  | up Enable bit                                                                    |                                 |             |                  |                  |                |  |

|                                                                                             | hardware                                    | will continue<br>on following of<br>ot monitored o<br><u>mode:</u>               | ising edge                      |             | rupt generated   | on falling edge  | bit cleared in |  |

| bit 0                                                                                       | ABDEN: Auto                                 | -Baud Detect                                                                     | Enable bit                      |             |                  |                  |                |  |

|                                                                                             | Asynchronous<br>1 = Enable b<br>cleared in  | <u>s mode:</u><br>aud rate meas<br>n hardware up<br>e measuremer<br><u>mode:</u> | surement on th<br>on completion |             | er – requires re | eception of a Sy | nc byte (55h); |  |

## REGISTER 16-3: BAUDCTL: BAUD RATE CONTROL REGISTER

#### 16.5.2 EUSART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep, or any Idle mode and bit SREN, which is a "don't care" in Slave mode.

If receive is enabled by setting the CREN bit prior to entering Sleep or any Idle mode, then a word may be received while in this low-power mode. Once the word is received, the RSR register will transfer the data to the RCREG register; if the RCIE enable bit is set, the interrupt generated will wake the chip from low-power mode. If the global interrupt is enabled, the program will branch to the interrupt vector. To set up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, set enable bit RCIE.

- 3. If 9-bit reception is desired, set bit RX9.

- 4. To enable reception, set enable bit CREN.

- 5. Flag bit, RCIF, will be set when reception is complete. An interrupt will be generated if enable bit, RCIE, was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

### TABLE 16-10: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Name    | Bit 7                                       | Bit 6                                   | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|---------------------------------------------|-----------------------------------------|-------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| INTCON  | GIE/GIEH                                    | PEIE/GIEL                               | TMR0IE      | INT0IE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1    | —                                           | ADIF                                    | RCIF        | TXIF   | —     | CCP1IF | TMR2IF | TMR1IF | -000 -000            | -000 -000                       |

| PIE1    | —                                           | ADIE                                    | RCIE        | TXIE   | —     | CCP1IE | TMR2IE | TMR1IE | -000 -000            | -000 -000                       |

| IPR1    | —                                           | ADIP                                    | RCIP        | TXIP   | —     | CCP1IP | TMR2IP | TMR1IP | -111 -111            | -111 -111                       |

| RCSTA   | SPEN                                        | RX9                                     | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| RCREG   | EUSART Receive Register                     |                                         |             |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA   | CSRC                                        | CSRC TX9 TXEN SYNC SENDB BRGH TRMT TX9D |             |        |       |        |        | TX9D   | 0000 0010            | 0000 0010                       |

| BAUDCTL | _                                           | RCIDL                                   | _           | SCKP   | BRG16 | —      | WUE    | ABDEN  | -1-1 0-00            | -1-1 0-00                       |

| SPBRGH  | BRGH Baud Rate Generator Register High Byte |                                         |             |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| SPBRG   | Baud Rate G                                 | Generator Reg                           | ister Low B | yte    |       |        |        |        | 0000 0000            | 0000 0000                       |

|         |                                             |                                         |             |        |       |        |        |        |                      |                                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave reception.

| U-0                                                                                                                      | U-0                        | U-0               | U-0           | U-0           | U-0              | R/C-1            | R/C-1       |  |

|--------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------|---------------|---------------|------------------|------------------|-------------|--|

| —                                                                                                                        | —                          | —                 | —             | —             | —                | CP1              | CP0         |  |

| bit 7                                                                                                                    |                            |                   |               |               |                  |                  | bit 0       |  |

|                                                                                                                          |                            |                   |               |               |                  |                  |             |  |

| Legend:                                                                                                                  |                            |                   |               |               |                  |                  |             |  |

| R = Readab                                                                                                               | le bit                     | W = Writable      | bit           | U = Unimpler  | mented bit, read | as '0'           |             |  |

| u = Bit is un                                                                                                            | changed                    | x = Bit is unkr   | nown          | -n/n = Value  | at POR and BOI   | R/Value at all o | ther Resets |  |

| '1' = Bit is se                                                                                                          | et                         | '0' = Bit is clea | ared          | C = Clearable | e bit            |                  |             |  |

|                                                                                                                          |                            |                   |               |               |                  |                  |             |  |

| bit 7-2                                                                                                                  | Unimplemented: Read as '0' |                   |               |               |                  |                  |             |  |

| bit 1                                                                                                                    | CP1: Code P                | rotection bit (P  | C18F1320)     |               |                  |                  |             |  |

|                                                                                                                          | · ·                        | 001000-001FFF     | , i           |               |                  |                  |             |  |

|                                                                                                                          | 0 = Block 1(0)             | 001000-001FFF     | h) code-prote | ected         |                  |                  |             |  |

| bit 0                                                                                                                    | CP0: Code P                | rotection bit (P  | C18F1320)     |               |                  |                  |             |  |

|                                                                                                                          | ``                         | 00200-000FFFI     | , i           |               |                  |                  |             |  |

|                                                                                                                          | · ·                        | 00200-000FFFI     | · ·           | cted          |                  |                  |             |  |

| bit 1 CP1: Code Protection bit (PIC18F1220)                                                                              |                            |                   |               |               |                  |                  |             |  |

| <ul> <li>1 = Block 1 (000800-000FFFh) not code-protected</li> <li>0 = Block 1 (000800-000FFFh) code-protected</li> </ul> |                            |                   |               |               |                  |                  |             |  |

| 1 1 0                                                                                                                    | •                          |                   | , .           | ected         |                  |                  |             |  |

| bit 0                                                                                                                    |                            | rotection bit (P  | -             |               |                  |                  |             |  |

| 1 = Block 0 (000200-0007FFh)  not code-protected                                                                         |                            |                   |               |               |                  |                  |             |  |

### REGISTER 19-6: CONFIG5L: CONFIGURATION REGISTER 5 LOW (BYTE ADDRESS 300008h)

| 0 = Block 0 (000200-0007FFh) code-p | orotected |

|-------------------------------------|-----------|

### REGISTER 19-7: CONFIG5H: CONFIGURATION REGISTER 5 HIGH (BYTE ADDRESS 300009h)

| R/C-1 | R/C-1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| CPD   | CPB   | —   | —   | —   | —   |     | —     |

| bit 7 |       |     |     |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | C = Clearable bit                                     |

| bit 7   | CPD: Data EEPROM Code Protection bit                                                                                        |

|---------|-----------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Data EEPROM not code-protected</li> <li>0 = Data EEPROM code-protected</li> </ul>                              |

|         | 0 = Data EEPROW code-protected                                                                                              |

| bit 6   | CPB: Boot Block Code Protection bit                                                                                         |

|         | <ul><li>1 = Boot Block (000000-0001FFh) not code-protected</li><li>0 = Boot Block (000000-0001FFh) code-protected</li></ul> |

| bit 5-0 | Unimplemented: Read as '0'                                                                                                  |

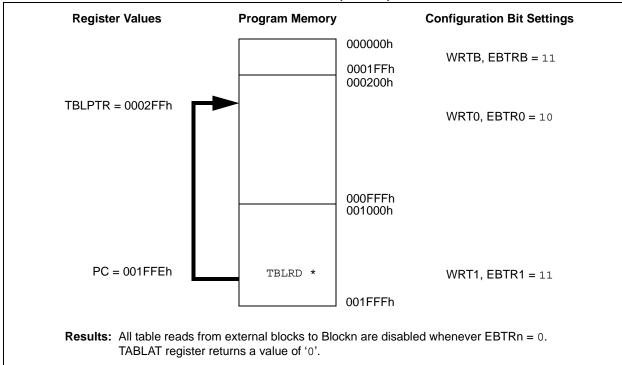

#### FIGURE 19-7: EXTERNAL BLOCK TABLE READ (EBTRn) DISALLOWED: PIC18F1320

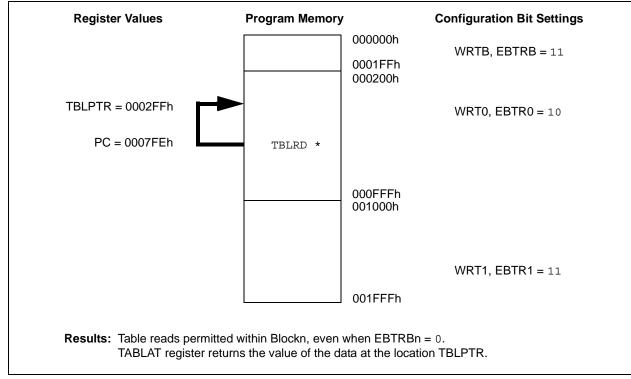

#### FIGURE 19-8: EXTERNAL BLOCK TABLE READ (EBTRn) ALLOWED: PIC18F1320

# 21.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 21.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- Multiple configurations

- · Simultaneous debugging sessions

- File History and Bug Tracking:

- Local file history feature

- Built-in support for Bugzilla issue tracker

| Param<br>No. | Symbol                               | c                                     | haracteristic   |                | Min.                                         | Max.   | Units | Conditions                               |

|--------------|--------------------------------------|---------------------------------------|-----------------|----------------|----------------------------------------------|--------|-------|------------------------------------------|

| 40           | Tt0H                                 | T0CKI High Pulse                      | Width           | No prescaler   | 0.5 TCY + 20                                 |        | ns    |                                          |

|              |                                      |                                       |                 | With prescaler | 10                                           | _      | ns    |                                          |

| 41           | Tt0L                                 | T0CKI Low Pulse                       | Width           | No prescaler   | 0.5 TCY + 20                                 |        | ns    |                                          |

|              |                                      |                                       |                 | With prescaler | 10                                           | _      | ns    |                                          |

| 42           | Tt0P                                 | T0CKI Period                          |                 | No prescaler   | Tcy + 10                                     | _      | ns    |                                          |

|              |                                      |                                       |                 | With prescaler | Greater of:<br>20 ns or <u>Tcy + 40</u><br>N | _      | ns    | N = prescale<br>value<br>(1, 2, 4,, 256) |

| 45           | Tt1H T13CKI High Time Synchronous, n |                                       | o prescaler     | 0.5 TCY + 20   | _                                            | ns     |       |                                          |

|              |                                      | Synchronous, with prescaler           | PIC18F1X20      | 10             | _                                            | ns     |       |                                          |

|              |                                      |                                       | PIC18LF1X20     | 25             | _                                            | ns     |       |                                          |

|              |                                      | Asynchronous                          | PIC18F1X20      | 30             | _                                            | ns     |       |                                          |

|              |                                      |                                       |                 | PIC18LF1X20    | 50                                           |        | ns    |                                          |

| 46           | Tt1L                                 | T13CKI Low Time                       | Synchronous, r  | o prescaler    | 0.5 TCY + 5                                  | _      | ns    |                                          |

|              |                                      |                                       | Synchronous,    | PIC18F1X20     | 10                                           | _      | ns    |                                          |

|              |                                      |                                       | with prescaler  | PIC18LF1X20    | 25                                           |        | ns    |                                          |

|              |                                      |                                       | Asynchronous    | PIC18F1X20     | 30                                           |        | ns    |                                          |

|              |                                      |                                       |                 | PIC18LF1X20    | 50                                           |        | ns    |                                          |

| 47           | Tt1P                                 | T13CKI Input<br>Period                | Synchronous     |                | Greater of:<br>20 ns or <u>Tcy + 40</u><br>N |        | ns    | N = prescale<br>value<br>(1, 2, 4, 8)    |

|              |                                      |                                       | Asynchronous    |                | 60                                           | _      | ns    |                                          |

|              | Ft1                                  | T13CKI Oscillator                     | Input Frequency | Range          | DC                                           | 50     | kHz   |                                          |

| 48           | Tcke2tmrl                            | Delay from Externa<br>Timer Increment | al T13CKI Clock | Edge to        | 2 Tosc                                       | 7 Tosc | —     |                                          |

TABLE 22-9: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

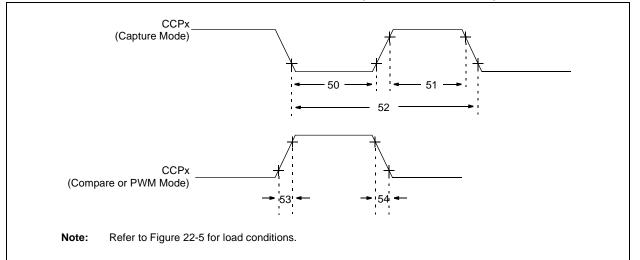

## FIGURE 22-11: CAPTURE/COMPARE/PWM TIMINGS (ALL CCP MODULES)

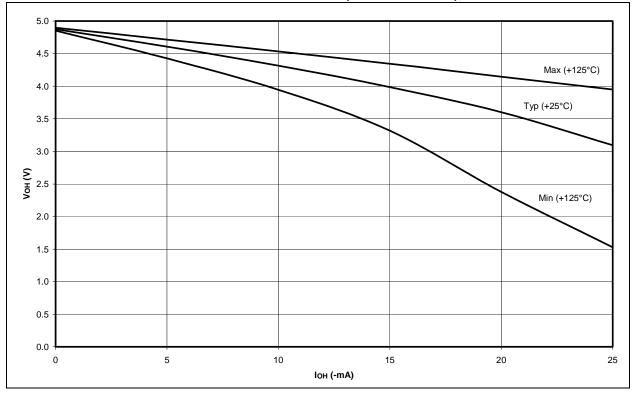

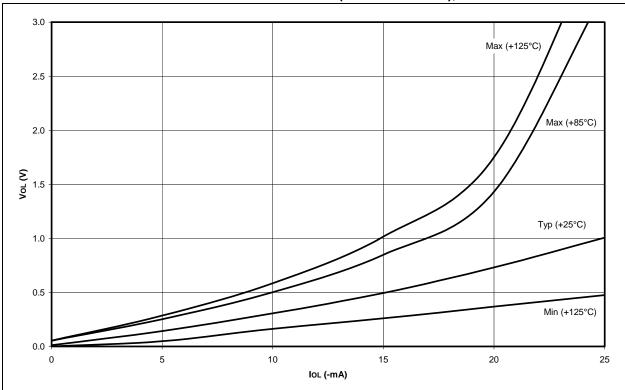

FIGURE 23-25: VOH vs. IOH OVER TEMPERATURE (-40°C TO +125°C), VDD = 5.0V

FIGURE 23-26: Vol vs. IoL OVER TEMPERATURE (-40°C TO +125°C), VDD = 3.0V

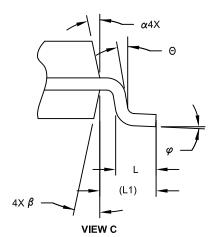

## 18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units | MILLIMETERS |          |      |  |

|--------------------------|-------|-------------|----------|------|--|

| Dimension Lin            | nits  | MIN         | NOM      | MAX  |  |

| Number of Pins           | N     |             | 18       |      |  |

| Pitch                    | е     |             | 1.27 BSC |      |  |

| Overall Height           | A     | -           | -        | 2.65 |  |

| Molded Package Thickness | A2    | 2.05        | -        | -    |  |

| Standoff §               | A1    | 0.10        | -        | 0.30 |  |

| Overall Width            | E     | 10.30 BSC   |          |      |  |

| Molded Package Width     | E1    | 7.50 BSC    |          |      |  |

| Overall Length           | D     | 11.55 BSC   |          |      |  |

| Chamfer (Optional)       | h     | 0.25        | -        | 0.75 |  |

| Foot Length              | L     | 0.40        | -        | 1.27 |  |

| Footprint                | L1    |             | 1.40 REF |      |  |

| Lead Angle               | Θ     | 0°          | -        | -    |  |

| Foot Angle               | φ     | 0°          | -        | 8°   |  |

| Lead Thickness           | С     | 0.20        | -        | 0.33 |  |

| Lead Width               | b     | 0.31        | -        | 0.51 |  |

| Mold Draft Angle Top     | α     | 5°          | -        | 15°  |  |

| Mold Draft Angle Bottom  | β     | 5°          | -        | 15°  |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-051C Sheet 2 of 2

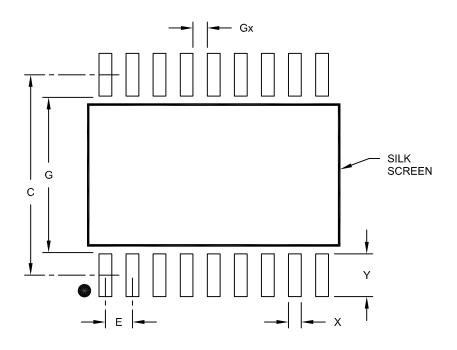

18-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                       | Units            | N    | S        |      |

|-----------------------|------------------|------|----------|------|

| Dimension             | Dimension Limits |      | NOM      | MAX  |

| Contact Pitch         | E                |      | 1.27 BSC |      |

| Contact Pad Spacing   | С                |      | 9.40     |      |

| Contact Pad Width     | X                |      |          | 0.60 |

| Contact Pad Length    | Y                |      |          | 2.00 |

| Distance Between Pads | Gx               | 0.67 |          |      |

| Distance Between Pads | G                | 7.40 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2051A