Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                          |

|----------------------------|------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                   |

| Core Processor             | 8051                                                                                     |

| Core Size                  | 8-Bit                                                                                    |

| Speed                      | 20MHz                                                                                    |

| Connectivity               | EBI/EMI, UART/USART                                                                      |

| Peripherals                | POR, PWM, WDT                                                                            |

| Number of I/O              | 36                                                                                       |

| Program Memory Size        | 128KB (128K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                    |

| EEPROM Size                | -                                                                                        |

| RAM Size                   | 1.25К х 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                                |

| Data Converters            | -                                                                                        |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                                          |

| Mounting Type              | Surface Mount                                                                            |

| Package / Case             | 44-BQFP                                                                                  |

| Supplier Device Package    | -                                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/w79l632a25fl |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4. PIN DESCRIPTION

| SYMBOL      | TYPE | DESCRIPTIONS                                                                                                                                                                                                                                                                                                    |

|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ĒĀ          | I    | <b>EXTERNAL ACCESS ENABLE:</b> This pin forces the processor to execute out of external ROM. It should be kept high to access internal ROM. The ROM address and data will not be present on the bus if EA pin is high and the program counter is within 128 KB area. Otherwise they will be present on the bus. |

| PSEN        | 0    | <b>PROGRAM STORE ENABLE:</b> PSEN enables the external ROM data onto the Port 0 address/data bus during fetch and MOVC operations. When internal ROM access is performed, no PSEN strobe signal outputs from this pin.                                                                                          |

| ALE         | 0    | <b>ADDRESS LATCH ENABLE:</b> ALE is used to enable the address latch that separates the address from the data on Port 0.                                                                                                                                                                                        |

| RST         | Ι    | <b>RESET:</b> A high on this pin for two machine cycles while the oscillator is running resets the device.                                                                                                                                                                                                      |

| XTAL1       | Ι    | <b>CRYSTAL1:</b> This is the crystal oscillator input. This pin may be driven by an external clock.                                                                                                                                                                                                             |

| XTAL2       | 0    | CRYSTAL2: This is the crystal oscillator output. It is the inversion of XTAL1.                                                                                                                                                                                                                                  |

| Vss         | Ι    | GROUND: Ground potential                                                                                                                                                                                                                                                                                        |

| Vdd         | Ι    | POWER SUPPLY: Supply voltage for operation.                                                                                                                                                                                                                                                                     |

| P0.0 - P0.7 | I/O  | <b>PORT 0:</b> Port 0 is an open-drain bi-directional I/O port. This port also provides a multiplexed low order address/data bus during accesses to external memory. Port 0 has internal pull-up resisters enabled by software.                                                                                 |

| P1.0 – P1.7 | I/O  | <b>PORT 1:</b> Port 1 is a bi-directional I/O port with internal pull-ups. The bits have alternate functions which are described below:<br>T2(P1.0): Timer/Counter 2 external count input<br>T2EX(P1.1): Timer/Counter 2 Reload/Capture/Direction control                                                       |

| P2.0 – P2.7 | I/O  | <b>PORT 2:</b> Port 2 is a bi-directional I/O port with internal pull-ups. This port also provides the upper address bits for accesses to external memory.                                                                                                                                                      |

| P3.0 – P3.7 | I/O  | <b>PORT 3:</b> Port 3 is a bi-directional I/O port with internal pull-ups. All bits have alternate functions, which are described below:   RXD(P3.0) : Serial Port 0 input   TXD(P3.1) : Serial Port 0 output   INT0 (P3.2) : External Interrupt 0                                                              |

|             | 24   | INT1(P3.3) : External Interrupt 1<br>T0(P3.4) : Timer 0 External Input<br>T1(P3.5) : Timer 1 External Input<br>WR (P3.6) : External Data Memory Write Strobe<br>RD (P3.7) : External Data Memory Read Strobe                                                                                                    |

| P4.0 – P4.3 | I/O  | <b>PORT 4:</b> Port 4 is a 4-bit bi-directional I/O port. The P4.3 also provides the alternate function REBOOT which is H/W reboot from LD flash.                                                                                                                                                               |

\* Note: TYPE I : input, O: output, I/O: bi-directional.

### nuvoton

#### 5. FUNCTIONAL DESCRIPTION

The W79E(L)632 is 8052 pin compatible and instruction set compatible. It includes the resources of the standard 8052 such as four 8-bit I/O Ports, three 16-bit timer/counters, full duplex serial port and interrupt sources.

The W79E(L)632 features a faster running and better performance 8-bit CPU with a redesigned core processor without wasted clock and memory cycles. it improves the performance not just by running at high frequency but also by reducing the machine cycle duration from the standard 8052 period of twelve clocks to four clock cycles for the majority of instructions. This improves performance by an average of 1.5 to 3 times. It can also adjust the duration of the MOVX instruction (access to off-chip data memory) between two machine cycles and nine machine cycles. This flexibility allows the W79E(L)632 to work efficiently with both fast and slow RAMs and peripheral devices. In addition, the W79E(L)632 contains on-chip 1KB MOVX SRAM, the address of which is between 0000H and 03FFH. It only can be accessed by MOVX instruction; this on-chip SRAM is optional under software control.

The W79E(L)632 is an 8052 compatible device that gives the user the features of the original 8052 device, but with improved speed and power consumption characteristics. It has the same instruction set as the 8051 family. While the original 8051 family was designed to operate at 12 clock periods per machine cycle, the W79E(L)632 operates at a much reduced clock rate of only 4 clock periods per machine cycle. This naturally speeds up the execution of instructions. Consequently, the W79E(L)632 can run at a higher speed as compared to the original 8052, even if the same crystal is used. Since the W79E(L)632 is a fully static CMOS design, it can also be operated at a lower crystal clock, giving the same throughput in terms of instruction execution, yet reducing the power consumption.

The 4 clocks per machine cycle feature in the W79E(L)632 is responsible for a three-fold increase in execution speed. The W79E(L)632 has all the standard features of the 8052, and has a few extra peripherals and features as well.

#### I/O Ports

The W79E(L)632 has four 8-bit ports and one extra 4-bit port. Port 0 can be used as an Address/Data bus when external program is running or external memory/device is accessed by MOVC or MOVX instruction. In these cases, it has strong pull-ups and pull-downs, and does not need any external pullups. Otherwise it can be used as a general I/O port with open-drain circuit. Port 2 is used chiefly as the upper 8-bits of the Address bus when port 0 is used as an address/data bus. It also has strong pull-ups and pull-downs when it serves as an address bus. Port 1 and port 3 act as I/O ports with alternate functions. Port 4 serves as a general purpose I/O port as Port 1 and Port 3.

#### Serial I/O

The W79E(L)632 has one enhanced serial ports that are functionally similar to the serial port of the original 8052 family. However the serial ports on the W79E(L)632 can operate in different modes in order to obtain timing similarity as well. The serial port has the enhanced features of Automatic Address sin Frame recognition and Frame Error detection.

Publication Release Date: Nov. 11, 2009 Revision A10

- 5 -

|    | opeelai i |        | J      |        |         |        |         |        |

|----|-----------|--------|--------|--------|---------|--------|---------|--------|

| F8 | EIP       |        |        |        | - Ale   |        |         |        |

| F0 | В         |        |        |        | 27.     |        |         |        |

| E8 | EIE       |        |        | 2      | 公司      |        |         |        |

| E0 | ACC       |        |        |        | - CON   | Sec.   |         |        |

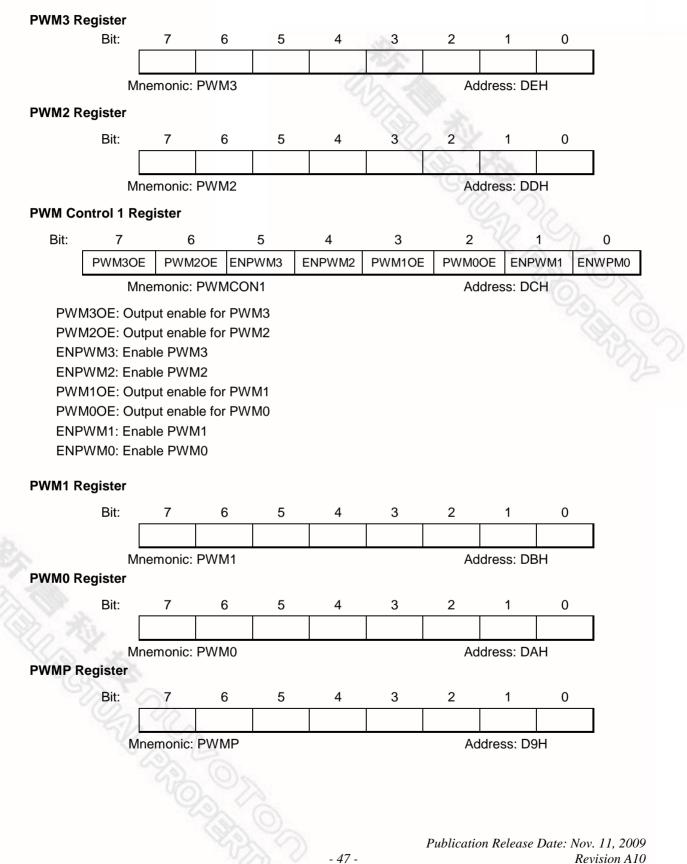

| D8 | WDCON     | PWMP   | PWM0   | PWM1   | PWMCON1 | PWM2   | PWM3    |        |

| D0 | PSW       |        |        |        | 1×      | K L    |         |        |

| C8 | T2CON     | T2MOD  | RCAP2L | RCAP2H | TL2     | TH2    | PWMCON2 | PWM4   |

| C0 |           |        |        | PWM5   | PMR     | STATUS |         | ТА     |

| B8 | IP        | SADEN  |        |        |         | 2      | b Co    | 2      |

| B0 | P3        | 1      |        |        |         |        | SAT     |        |

| A8 | IE        | SADDR  |        | ROMCON | SFRAL   | SFRAH  | SFDFD   | SFRCN  |

| A0 | P2        | XRAMAH | P4CSIN |        |         | P4     | 0       | 20     |

| 98 | SCON0     | SBUF   | P42AL  | P42AH  | P43AL   | P43AH  | 0       | CHPCON |

| 90 | P1        |        | P4CONA | P4CONB | P40AL   | P40AH  | P41AL   | P41AH  |

| 88 | TCON      | TMOD   | TL0    | TL1    | TH0     | TH1    | CKCON   | 00     |

| 80 | P0        | SP     | DPL    | DPH    |         |        |         | PCON   |

Table 1. Special Function Register Location Table

Note: The SFRs in the column with dark borders are bit-addressable.

A brief description of the SFRs is shown follows.

#### Port 0

| Bit: | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|------|

|      | P0.7 | P0.6 | P0.5 | P0.4 | P0.3 | P0.2 | P0.1 | P0.0 |

|      |      |      |      |      |      |      |      |      |

#### Mnemonic: P0

Address: 80h

Port 0 is an open-drain bi-directional I/O port. This port also provides a multiplexed low order address/data bus during accesses to external memory. Besides, it has internal pull-up resisters enabled by setting POUP of P4CSIN (A2H) to high.

#### **Stack Pointer**

| Bit: | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|------|

|      | SP.7 | SP.6 | SP.5 | SP.4 | SP.3 | SP.2 | SP.1 | SP.0 |

|      |      |      |      |      |      |      |      |      |

#### Mnemonic: SP

Address: 81h

The Stack Pointer stores the Scratchpad RAM address where the stack begins. In other words, it always points to the top of the stack.

- 9 -

#### **Data Pointer Low**

|                           | Bit:       | 7          | 6          | 5           | 4       | 3     | 2         | 1     | 0     |

|---------------------------|------------|------------|------------|-------------|---------|-------|-----------|-------|-------|

|                           |            | DPL.7      | DPL.6      | DPL.5       | DPL.4   | DPL.3 | DPL.2     | DPL.1 | DPL.0 |

| N                         | Inemonio   | : DPL      |            |             | S       | A     | ddress: 8 | 2h    |       |

| This is the low byte      | e of the s | tandard 80 | 052 16-bit | data poin   | iter.   |       |           |       |       |

| Data Pointer High         | 1          |            |            |             |         |       |           |       |       |

|                           | Bit:       | 7          | 6          | 5           | 4       | 3     | 2         | 1     | 0     |

|                           |            | DPH.7      | DPH.6      | DPH.5       | DPH.4   | DPH.3 | DPH.2     | DPH.1 | DPH.0 |

| Ν                         | Inemonio   | : DPH      |            |             |         | A     | ddress: 8 | 3h    |       |

| This is the high byt      | e of the   | standard 8 | 3052 16-bi | it data poi | nter.   |       |           |       |       |

| Power Control             |            |            |            |             |         |       |           |       |       |

|                           | Bit:       | 7          | 6          | 5           | 4       | 3     | 2         | 12/3  | 0     |

| SM0D SM0D0 GF1 GF0 PD IDL |            |            |            |             |         |       |           |       |       |

| N                         |            | A          | ddress: 8  | 7h          | Non Non |       |           |       |       |

- SMOD : This bit doubles the serial port baud rate in mode 1, 2, and 3 when set to 1.

- SMOD0: Framing Error Detection Enable: When SMOD0 is set to 1, then SCON.7 indicates a Frame Error and acts as the FE flag. When SMOD0 is 0, then SCON.7 acts as per the standard 8052 function.

- GF1-0: These two bits are general purpose user flags.

- PD: Setting this bit causes the W79E(L)632 to go into the POWER DOWN mode. In this mode all the clocks are stopped and program execution is frozen.

- IDL: Setting this bit causes the W79E(L)632 to go into the IDLE mode. In this mode the clocks to the CPU are stopped, so program execution is frozen. But the clock to the serial, timer and interrupt blocks is not stopped, and these blocks continue operating.

#### **Timer Control**

| Bit:     | 7      | 6   | 5   | 4   | 3   | 2         | 1   | 0   |

|----------|--------|-----|-----|-----|-----|-----------|-----|-----|

|          | TF1    | TR1 | TF0 | TR0 | IE1 | IT1       | IE0 | IT0 |

| Mnemonic | : TCON |     |     |     | A   | ddress: 8 | Bh  |     |

- TF1: Timer 1 overflow flag: This bit is set when Timer 1 overflows. It is cleared automatically when the program does a timer 1 interrupt service routine. Software can also set or clear this bit.

- TR1: Timer 1 run control: This bit is set or cleared by software to turn timer/counter on or off.

- TF0: Timer 0 overflow flag: This bit is set when Timer 0 overflows. It is cleared automatically when the program does a timer 0 interrupt service routine. Software can also set or clear this bit.

- TR0: Timer 0 run control: This bit is set or cleared by software to turn timer/counter on or off.

#### P4.2 Base Address Low Byte Register Bit: 7 6 5 0 4 3 2 1 A4 A3 A2 A1 A0 A7 A6 A5 Mnemonic: P42AL Address: 9Ah P4.2 Base Address High Byte Register Bit: 7 6 5 4 3 2 1 0 A11 A10 A15 A14 A13 A12 Α9 A8 Address: 9Bh Mnemonic: P42AH P4.3 Base Address Low Byte Register Bit: 7 6 3 2 1 0 5 4 A7 A6 A5 A4 A3 A2 A1 A0 Mnemonic: P43AL Address: 9Ch P4.3 Base Address High Byte Register 2 Bit: 7 6 5 4 3 1 0 A15 A14 A13 A12 A11 A10 Α9 A8 Mnemonic: P43AH Address: 9Dh **ISP Control Register** Bit: 7 6 5 3 2 1 0 4 SWRST/HWB LDAP LDSEL \_ \_ -\_ ENP Mnemonic: CHPCON Address: 9Fh

SWRST/HWB: Set this bit to launch a whole device reset that is same as asserting high to RST pin, micro controller will be back to initial state and clear this bit automatically. To read this bit, its alternate function to indicate the ISP hardware reboot mode is invoking when read it in high.

- LDAP: This bit is Read Only. High: device is executing the program in LDFlash. Low: device is executing the program in APFlashs.

- LDSEL: Loader program residence selection. Set to high to route the device fetching code from LDFlash.

- ENP: In System Programming Mode Enable. Set this be to launch the ISP mode. Device will operate ISP procedures, such as Erase. Program and Read operations, according to correlative SFRs settings. During ISP mode, device achieves ISP operations by the way of IDLE state. In the other words, device is not indeed in IDLE mode is set bit PCON.1 while ISP is enabled. Clear this bit to disable ISP mode, device get back to normal operation including IDLE state. e y

## nuvoTon

|                           | P3.3<br>P3.2<br>P3.1<br>P3.0 | INT1<br>INT0<br>TxD<br>RxD | D Exte<br>Seria | rnal interr<br>rnal interr<br>al port 0 o<br>al port 0 ir | upt 0<br>utput |             |               |               |            |     |  |

|---------------------------|------------------------------|----------------------------|-----------------|-----------------------------------------------------------|----------------|-------------|---------------|---------------|------------|-----|--|

| Interru                   | pt Priority                  |                            |                 |                                                           |                |             |               |               |            |     |  |

|                           | B                            | it:                        | 7               | 6                                                         | 5              | 4           | 3             | 2             | 1          | 0   |  |

|                           |                              |                            | -               | -                                                         | PT2            | PS          | PT1           | PX1           | PT0        | PX0 |  |

| Mnemonic: IP Address: B8h |                              |                            |                 |                                                           |                |             |               |               | 8h         |     |  |

| IP.7:                     | This bit is un-ir            | nplem                      | ented ar        | nd will rea                                               | d high.        |             |               |               |            |     |  |

| PT2:                      | This bit defines             | s the T                    | imer 2 ir       | nterrupt pi                                               | riority. PT2   | 2 = 1 sets  | it to highe   | er priority l | evel.      |     |  |

| PS:                       | This bit defines             | s the S                    | erial por       | t 0 interru                                               | pt priority.   | . PS = 1 s  | ets it to hi  | gher prior    | ity level. |     |  |

| PT1:                      | This bit defines             | s the T                    | imer 1 ir       | nterrupt pi                                               | riority. PT1   | 1 = 1 sets  | it to highe   | er priority l | evel.      |     |  |

| PX1:                      | This bit defines             | s the E                    | xternal i       | nterrupt 1                                                | priority. F    | 2X1 = 1 se  | ets it to hig | gher priori   | ty level.  |     |  |

| PT0:                      | This bit defines             | s the T                    | imer 0 ir       | nterrupt pi                                               | riority. PT(   | 0 = 1  sets | it to highe   | er priority l | evel.      |     |  |

| PX0:                      | This bit defines             | s the E                    | xternal i       | nterrupt 0                                                | priority. F    | PX0 = 1 se  | ets it to hig | gher priori   | ty level.  |     |  |

| Slave                     | Address Mask I               | Enable                     | e               |                                                           |                |             |               |               |            |     |  |

|                           | B                            | it:                        | 7               | 6                                                         | 5              | 4           | 3             | 2             | 1          | 0   |  |

|                           |                              |                            |                 |                                                           |                |             |               |               |            |     |  |

|                           | Mnem                         | nonic:                     | SADEN           |                                                           | 1              |             | A             | ddress: B     | 9h         |     |  |

SADEN: This register enables the Automatic Address Recognition feature of the Serial port 0. When a bit in the SADEN is set to 1, the same bit location in SADDR will be compared with the incoming serial data. When SADEN.n is 0, then the bit becomes a "don't care" in the comparison. This register enables the Automatic Address Recognition feature of the Serial port 0. When all the bits of SADEN are 0, interrupt will occur for any incoming address.

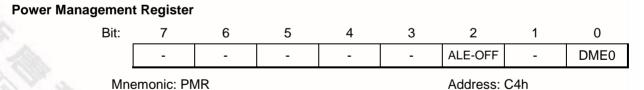

ALEOFF: This bit disables the expression of the ALE signal on the device pin during all on-board program and data memory accesses. External memory accesses will automatically enable ALE independent of ALEOFF.

0 = ALE expression is enable; 1 = ALE expression is disable

DME0: This bit determines the on-chip MOVX SRAM to be enabled or disabled. Set this bit to 1 will enable the on-chip 1KB MOVX SRAM.

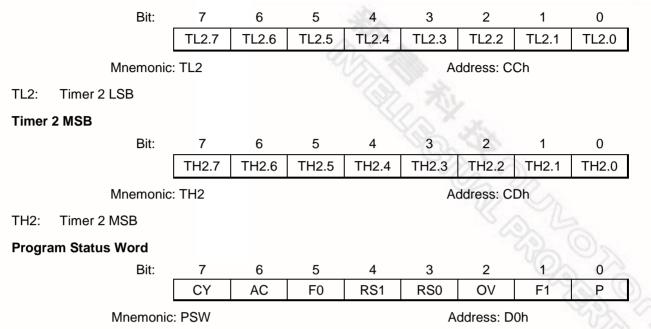

#### Timer 2 LSB

CY: Carry flag: Set for an arithmetic operation which results in a carry being generated from the ALU. It is also used as the accumulator for the bit operations.

AC: Auxiliary carry: Set when the previous operation resulted in a carry from the high order nibble.

F0: User flag 0: General purpose flag that can be set or cleared by the user.

RS.1-0: Register bank select bits:

| RS1 | RS0 | Register bank | Address |

|-----|-----|---------------|---------|

| 0   | 0   | 0             | 00-07h  |

| 0   | 1   | 1             | 08-0Fh  |

| 1   | 0   | 2             | 10-17h  |

| 1   | 1   | 3             | 18-1Fh  |

OV: Overflow flag: Set when a carry was generated from the seventh bit but not from the 8th bit as a result of the previous operation, or vice-versa.

F1: User Flag 1: General purpose flag that can be set or cleared by the user by software.

P: Parity flag: Set/cleared by hardware to indicate odd/even number of 1's in the accumulator.

#### Watchdog Control

| Bit: | 7 | 6   | 5 | 4 | 3    | 2    | 1   | 0   |

|------|---|-----|---|---|------|------|-----|-----|

| 6    | - | POR | - | - | WDIF | WTRF | EWT | RWT |

#### Mnemonic: WDCON

Address: D8h

POR: Power-on reset flag. Hardware will set this flag on a power up condition. This flag can be read or written by software. A write by software is the only way to clear this bit once it is set.

WDIF: Watchdog Timer Interrupt Flag. If the watchdog interrupt is enabled, hardware will set this bit to indicate that the watchdog interrupt has occurred. If the interrupt is not enabled, then this bit indicates that the time-out period has elapsed. This bit must be cleared by software.

### 7. INSTRUCTION

The W79E(L)632 executes all the instructions of the standard 8032 family. The operation of these instructions, their effect on the flag bits and the status bits is exactly the same. However, timing of these instructions is different. The reason for this is two fold. Firstly, in the W79E(L)632, each machine cycle consists of 4 clock periods, while in the standard 8032 it consists of 12 clock periods. Also, in the W79E(L)632 there is only one fetch per machine cycle i.e. 4 clocks per fetch, while in the standard 8032 there can be two fetches per machine cycle, which works out to 6 clocks per fetch.

The advantage the W79E(L)632 has is that since there is only one fetch per machine cycle, the number of machine cycles in most cases is equal to the number of operands that the instruction has. In case of jumps and calls there will be an additional cycle that will be needed to calculate the new address. But overall the W79E(L)632 reduces the number of dummy fetches and wasted cycles, thereby improving efficiency as compared to the standard 8032.

#### 7.1 **Instruction Timing**

The instruction timing for the W79E(L)632 is an important aspect, especially for those users who wish to use software instructions to generate timing delays. Also, it provides the user with an insight into the timing differences between the W79E(L)632 and the standard 8032. In the W79E(L)632 each machine cycle is four clock periods long. Each clock period is designated a state. Thus each machine cycle is made up of four states, C1, C2 C3 and C4, in that order. Due to the reduced time for each instruction execution, both the clock edges are used for internal timing. Hence it is important that the duty cycle of the clock be as close to 50% as possible to avoid timing conflicts. As mentioned earlier, the W79E(L)632 does one op-code fetch per machine cycle. Therefore, in most of the instructions, the number of machine cycles needed to execute the instruction is equal to the number of bytes in the instruction. Of the 256 available op-codes, 128 of them are single cycle instructions. Thus more than half of all opcodes in the W79E(L)632 are executed in just four clock periods. Most of the two-cycle instructions are those that have two byte instruction codes. However there are some instructions that have only one byte instructions, yet they are two cycle instructions. One instruction which is of importance is the MOVX instruction. In the standard 8032, the MOVX instruction is always two machine cycles long. However in the W79E(L)632, the user has a facility to stretch the duration of this instruction from 2 machine cycles to

9 machine cycles. The RD and WR strobe lines are also proportionately elongated. This gives the user flexibility in accessing both fast and slow peripherals without the use of external circuitry and with minimum software overhead. The rest of the instructions are either three, four or five machine cycle instructions. Note that in the W79E(L)632, based on the number of machine cycles, there are five different types, while in the standard 8032 there are only three. However, in the W79E(L)632 each machine cycle is made of only 4 clock periods compared to the 12 clock periods for the standard 8032. Therefore, even though the number of categories has increased, each instruction is at least 1.5 to 3 che. times faster than the standard 8032 in terms of clock periods.

### nuvoTon

|            | MEMORY   |   |   |       |      |         |      |

|------------|----------|---|---|-------|------|---------|------|

| Idle       | Internal | 1 | 1 | Data  | Data | Data    | Data |

| Idle       | External | 1 | 1 | Float | Data | Address | Data |

| Power Down | Internal | 0 | 0 | Data  | Data | Data    | Data |

| Power Down | External | 0 | 0 | Float | Data | Data    | Data |

#### **Reset Conditions**

The user has several hardware related options for placing the W79E(L)632 into reset condition. In general, most register bits go to their reset value irrespective of the reset condition, but there are a few flags whose state depends on the source of reset. The user can use these flags to determine the cause of reset using software. There are two ways of putting the device into reset state. They are External reset and Watchdog reset.

#### **External Reset**

The device continuously samples the RST pin at state C4 of every machine cycle. Therefore the RST pin must be held for at least 2 machine cycles to ensure detection of a valid RST high. The reset circuitry then synchronously applies the internal reset signal. Thus the reset is a synchronous operation and requires the clock to be running to cause an external reset.

Once the device is in reset condition, it will remain so as long as RST is 1. Even after RST is deactivated, the device will continue to be in reset state for up to two machine cycles, and then begin program execution from 0000h. There is no flag associated with the external reset condition. However since the other two reset sources have flags, the external reset can be considered as the default reset if those two flags are cleared.

The software must clear the POR flag after reading it, otherwise it will not be possible to correctly determine future reset sources. If the power fails, i.e. falls below Vrst, then the device will once again go into reset state. When the power returns to the proper operating levels, the device will again perform a power on reset delay and set the POR flag.

#### Watchdog Timer Reset

The Watchdog timer is a free running timer with programmable time-out intervals. The user can clear the watchdog timer at any time, causing it to restart the count. When the time-out interval is reached an interrupt flag is set. If the Watchdog reset is enabled and the watchdog timer is not cleared, then 512 clocks from the flag being set, the watchdog timer will generate a reset. This places the device into the reset condition. The reset condition is maintained by hardware for two machine cycles. Once the reset is removed the device will begin execution from 0000h.

- 33 -

| SFR NAME | RESET VALUE | SFR NAME | RESET VALUE |

|----------|-------------|----------|-------------|

| SFRCN    | 00111111b   | P4       | xxxx1111b   |

| SCON     | 0000000b    | В        | 0000000b    |

| SBUF     | xxxxxxb     | EIP      | xxx00000b   |

| P2       | 1111111b    | PWMCON1  | 0000000b    |

| PWMCON2  | 0000000b    | PWM0     | 0000000b    |

| PWM1     | 0000000b    | PWM2     | 0000000b    |

| PWM3     | 0000000b    | PWM4     | 0000000b    |

| PWM5     | 0000000b    | 6        | 5.40        |

Table 6. SFR Reset Value, continued

The WDCON SFR bits are set/cleared in reset condition depending on the source of the reset.

|       | External reset | Watchdog reset | Power on reset |

|-------|----------------|----------------|----------------|

| WDCON | 0x0x0xx0b      | 0x0x01x0b      | 0100000b       |

The POR bit WDCON.6 is set only by the power on reset. The WTRF bit WDCON.2 is set when the Watchdog timer causes a reset. A power on reset will also clear this bit. The EWT bit WDCON.1 is cleared by power on resets. This disables the Watchdog timer resets. A watchdog or external reset does not affect the EWT bit.

#### 9. INTERRUPTS

The W79E(L)632 has a two priority level interrupt structure with 11 interrupt sources. Each of the interrupt sources has an individual priority bit, flag, interrupt vector and enable bit. In addition, the interrupts can be globally enabled or disabled.

#### Interrupt Sources

The External Interrupts INT0 and INT1 can be either edge triggered or level triggered, depending on bits IT0 and IT1. The bits IE0 and IE1 in the TCON register are the flags which are checked to generate the interrupt. In the edge triggered mode, the INTx inputs are sampled in every machine cycle. If the sample is high in one cycle and low in the next, then a high to low transition is detected and the interrupts request flag IEx in TCON is set. The flag bit requests the interrupt. Since the external interrupts are sampled every machine cycle, they have to be held high or low for at least one complete machine cycle. The IEx flag is automatically cleared when the service routine is called. If the level triggered mode is selected, then the requesting source has to hold the pin low till the interrupt is serviced. The IEx flag will not be cleared by the hardware on entering the service routine. If the interrupt continues to be held low even after the service routine is completed, then the processor may acknowledge another interrupt request from the same source.

The Timer 0 and 1 Interrupts are generated by the TF0 and TF1 flags. These flags are set by the overflow in the Timer 0 and Timer 1. The TF0 and TF1 flags are automatically cleared by the hardware when the timer interrupt is serviced. The Timer 2 interrupt is generated by a logical OR of the TF2 and the EXF2 flags. These flags are set by overflow or capture/reload events in the timer 2 operation. The hardware does not clear these flags when a timer 2 interrupt is executed. Software has to resolve the cause of the interrupt between TF2 and EXF2 and clear the appropriate flag.

The Watchdog timer can be used as a system monitor or a simple timer. In either case, when the timeout count is reached, the Watchdog timer interrupt flag WDIF (WDCON.3) is set. If the interrupt is enabled by the enable bit EIE.4, then an interrupt will occur.

All the bits that generate interrupts can be set or reset by hardware, and thereby software initiated interrupts can be generated. Each of the individual interrupts can be enabled or disabled by setting or clearing a bit in the IE SFR. IE also has a global enable/disable bit EA, which can be cleared to disable

#### **Priority Level Structure**

There are three priority levels for the interrupts, highest, high and low. The interrupt sources can be individually set to either high or low levels. Naturally, a higher priority interrupt cannot be interrupted by a lower priority interrupt. However there exists a pre-defined hierarchy amongst the interrupts themselves. This hierarchy comes into play when the interrupt controller has to resolve simultaneous requests having the same priority level. This hierarchy is defined as shown below; the interrupts are numbered starting from the highest priority to the lowest.

| SOURCE               | FLAG       | VECTOR ADDRESS | PRIORITY LEVEL |

|----------------------|------------|----------------|----------------|

| External Interrupt 0 | IE0        | 0003h          | 1(highest)     |

| Timer 0 Overflow     | TF0        | 000Bh          | 2              |

| External Interrupt 1 | IE1        | 0013h          | 3              |

| Timer 1 Overflow     | TF1        | 001Bh          | 324 0          |

| Serial Port          | RI + TI    | 0023h          | 5              |

| Timer 2 Overflow     | TF2 + EXF2 | 002Bh          | 6              |

| Watchdog Timer       | WDIF       | 0063h          | 7 (lowest)     |

#### Table 7. Priority structure of interrupts

Publication Release Date: Nov. 11, 2009 Revision A10

### nuvoTon

#### Mode 3

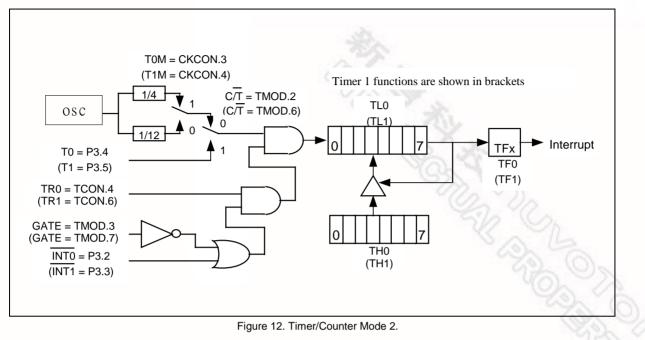

Mode 3 has different operating methods for the two timer/counters. For timer/counter 1, mode 3 simply freezes the counter. Timer/Counter 0, however, configures TL0 and TH0 as two separate 8 bit count registers in this mode. The logic for this mode is shown in the figure. TL0 uses the Timer/Counter 0 control bits  $C/\overline{T}$ , GATE, TR0, INTO and TF0. The TL0 can be used to count clock cycles (clock/12 or clock/4) or 1-to-0 transitions on pin T0 as determined by C/T (TMOD.2). TH0 is forced as a clock cycle counter (clock/12 or clock/4) and takes over the use of TR1 and TF1 from Timer/Counter 1. Mode 3 is used in cases where an extra 8 bit timer is needed. With Timer 0 in Mode 3, Timer 1 can still be used in Modes 0, 1 and 2., but its flexibility is somewhat limited. While its basic functionality is maintained, it no longer has control over its overflow flag TF1 and the enable bit TR1. Timer 1 can still be used as a timer/counter and retains the use of GATE and INT1 pin. In this condition it can be turned on and off by switching it out of and into its own Mode 3. It can also be used as a baud rate generator for the serial port.

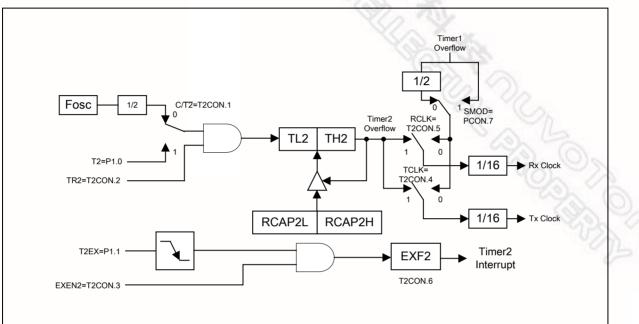

#### **Baud Rate Generator Mode**

The baud rate generator mode is enabled by setting either the RCLK or TCLK bits in T2CON register. While in the baud rate generator mode, Timer/Counter 2 is a 16 bit counter with auto reload when the count rolls over from FFFFh. However, rolling over does not set the TF2 bit. If EXEN2 bit is set, then a negative transition of the T2EX pin will set EXF2 bit in the T2CON register and cause an interrupt request.

Figure 17. Baud Rate Generator Mode

# nuvoTon

;;;;

| mov  | ckcon,#01h  | ; select 2 ^ 17 timer |

|------|-------------|-----------------------|

| mov  | ckcon,#61h  | ; select 2 ^ 20 timer |

| mov  | ckcon,#81h  | ; select 2 ^ 23 timer |

| mov  | ckcon,#c1h  | ; select 2 ^ 26 timer |

| mov  | TA,#aah     |                       |

| mov  | TA,#55h     |                       |

| mov  | WDCON,#0000 | 0011B                 |

| setb | EWDI        |                       |

| setb | ea          |                       |

| jmp  | \$          | ; wait time out       |

|      |             |                       |

|      |             |                       |

Publication Release Date: Nov. 11, 2009 Revision A10

### nuvoTon

Slave 1:

SADDR 1010 0100 SADEN 1111 1010 Given 1010 0x0x

Slave 2:

SADDR 1010 0111 SADEN 1111 1001 Given 1010 0xx1

The Given address for slave 1 and 2 differ in the LSB. For slave 1, it is a don't care, while for slave 2 it is 1. Thus to communicate only with slave 1, the master must send an address with LSB = 0 (1010 0000). Similarly the bit 1 position is 0 for slave 1 and don't care for slave 2. Hence to communicate only with slave 2 the master has to transmit an address with bit 1 = 1 (1010 0011). If the master wishes to communicate with both slaves simultaneously, then the address must have bit 0 = 1 and bit 1 = 0. The bit 3 position is don't care for both the slaves. This allows two different addresses to select both slaves (1010 0001 and 1010 0101).

The master can communicate with all the slaves simultaneously with the Broadcast Address. This address is formed from the logical ORing of the SADDR and SADEN SFRs. The zeros in the result are defined as don't cares In most cases the Broadcast Address is FFh. In the previous case, the Broadcast Address is (1111111X) for slave 1 and (1111111) for slave 2.

The SADDR and SADEN SFRs are located at address A9h and B9h respectively. On reset, these two SFRs are initialized to 00h. This results in Given Address and Broadcast Address being set as XXXX XXXX(i.e. all bits don't care). This effectively removes the multiprocessor communications feature, since any selectivity is disabled.

#### **12. TIMED ACCESS PROTECTION**

The W79E(L)632 has several new features, like the Watchdog timer, on-chip ROM size adjustment, wait state control signal and Power on/fail reset flag, which are crucial to proper operation of the system. If left unprotected, errant code may write to the Watchdog control bits resulting in incorrect operation and loss of control. In order to prevent this, the W79E(L)632 has a protection scheme which controls the write access to critical bits. This protection scheme is done using a timed access.

In this method, the bits which are to be protected have a timed write enable window. A write is successful only if this window is active, otherwise the write will be discarded. This write enable window is open for 3 machine cycles if certain conditions are met. After 3 machine cycles, this window automatically closes. The window is opened by writing AAh and immediately 55h to the Timed Access(TA) SFR. This SFR is located at address C7h. The suggested code for opening the timed access window is

TAREG0C7h;define new register TA, located at 0C7hMOVTA, #0AAhMOVTA, #055h

When the software writes AAh to the TA SFR, a counter is started. This counter waits for 3 machine cycles looking for a write of 55h to TA. If the second write (55h) occurs within 3 machine cycles of the first write (AAh), then the timed access window is opened. It remains open for 3 machine cycles, during which the user may write to the protected bits. Once the window closes the procedure must be repeated to access the other protected bits.

Note: M/C = Machine Cycles

#### Examples of Timed Assessing are shown below.

#### Example 1: Valid access

| MOV | TA, #0AAh   | 3 M/C |

|-----|-------------|-------|

| MOV | TA, #055h   | 3 M/C |

| MOV | WDCON, #00h | 3 M/C |

Example 2: Valid access

| MOV  | TA, #0AAh | 3 M/C |

|------|-----------|-------|

| MOV  | TA, #055h | 3 M/C |

| NOP  |           | 1 M/C |

| SETB | EWT       | 2 M/C |

Example 3: Valid access

| MOV | TA, #0Aah  | 3 M/C        |   |

|-----|------------|--------------|---|

| MOV | TA, #055h  | 3 M/C        |   |

| ORL | WDCON, #00 | 000010B 3M/0 | 2 |

|     |            |              |   |

|     |            |              |   |

|     |            |              |   |

|     |            |              |   |

|     |            |              |   |

|     |            |              |   |

|     |            |              |   |

|     |            |              |   |

|     |            |              |   |

|     |            |              |   |

|     |            |              |   |

|     |            |              |   |

Publication Release Date: Nov. 11, 2009 Revision A10

- 59 -

#### **14. IN-SYSTEM PROGRAMMING**

#### 14.1 The Loader Program Locates at LDFlash Memory

CPU is Free Run at APFlash memory. CHPCON register had been set #03H value before CPU has entered idle state. CPU will switch to LDFlash memory and execute a reset action. H/W reboot mode will switch to LDFlash memory, too. Set SFRCN register where it locates at user's loader program to update APFlash bank 0 or bank 1 memory. Set a SWRESET (CHPCON.7) to switch back APFlash after CPU has updated APFlash program. CPU will restart to run program from reset state.

#### 14.2 The Loader Program Locates at APFlash Memory

CPU is Free Run at APFlash memory. CHPCON register had been set #01H value before CPU has entered idle state. Set SFRCN register to update LDFlash or another bank of APFlash program. CPU will continue to run user's APFlash program after CPU has updated program. Please refer demonstrative code to understand other detail description.

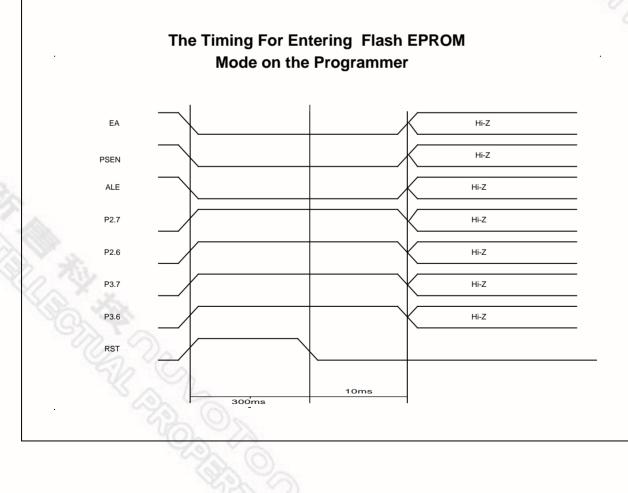

#### **15. H/W WRITER MODE**

This mode is for the writer to write / read Flash EPROM operation. A general user may not enter this mode.

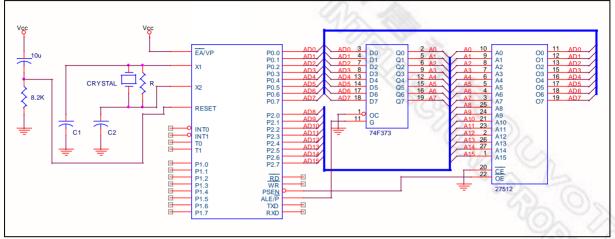

### **18. TYPICAL APPLICATION CIRCUITS**

#### Expanded External Program Memory and Crystal

| Figure A | ١ |

|----------|---|

|----------|---|

| CRYSTAL | C1  | C2  | R    |

|---------|-----|-----|------|

| 16 MHz  | 20P | 20P | - 6  |

| 24 MHz  | 12P | 12P | -    |

| 33 MHz  | 10P | 10P | 3.3K |

| 40 MHz  | 1P  | 1P  | 3.3K |

The above table shows the reference values for crystal applications.

Note: C1, C2, R components refer to Figure A.

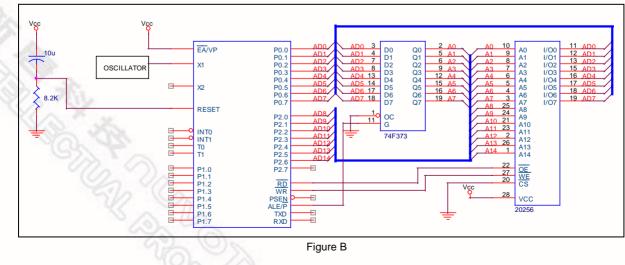

#### **Expanded External Data Memory and Oscillator**

- 71 -