#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                   |

|----------------------------|------------------------------------------------------------------------------------------|

| Core Processor             | 8051                                                                                     |

| Core Size                  | 8-Bit                                                                                    |

| Speed                      | 20MHz                                                                                    |

| Connectivity               | EBI/EMI, UART/USART                                                                      |

| Peripherals                | POR, PWM, WDT                                                                            |

| Number of I/O              | 36                                                                                       |

| Program Memory Size        | 128KB (128K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                    |

| EEPROM Size                | -                                                                                        |

| RAM Size                   | 1.25K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                                |

| Data Converters            | -                                                                                        |

| Oscillator Type            | Internal                                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                                          |

| Mounting Type              | Surface Mount                                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                                          |

| Supplier Device Package    | -                                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/w79l632a25pl |

|                            |                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4. PIN DESCRIPTION

| SYMBOL      | TYPE | DESCRIPTIONS                                                                                                                                                                                                                                                                                                    |

|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ĒĀ          | Ι    | <b>EXTERNAL ACCESS ENABLE:</b> This pin forces the processor to execute out of external ROM. It should be kept high to access internal ROM. The ROM address and data will not be present on the bus if EA pin is high and the program counter is within 128 KB area. Otherwise they will be present on the bus. |

| PSEN        | 0    | <b>PROGRAM STORE ENABLE:</b> PSEN enables the external ROM data onto the Port 0 address/data bus during fetch and MOVC operations. When internal ROM access is performed, no PSEN strobe signal outputs from this pin.                                                                                          |

| ALE         | 0    | <b>ADDRESS LATCH ENABLE:</b> ALE is used to enable the address latch that separates the address from the data on Port 0.                                                                                                                                                                                        |

| RST         | Ι    | <b>RESET:</b> A high on this pin for two machine cycles while the oscillator is running resets the device.                                                                                                                                                                                                      |

| XTAL1       | Ι    | <b>CRYSTAL1:</b> This is the crystal oscillator input. This pin may be driven by an external clock.                                                                                                                                                                                                             |

| XTAL2       | 0    | CRYSTAL2: This is the crystal oscillator output. It is the inversion of XTAL1.                                                                                                                                                                                                                                  |

| Vss         | Ι    | GROUND: Ground potential                                                                                                                                                                                                                                                                                        |

| Vdd         | Ι    | POWER SUPPLY: Supply voltage for operation.                                                                                                                                                                                                                                                                     |

| P0.0 - P0.7 | I/O  | <b>PORT 0:</b> Port 0 is an open-drain bi-directional I/O port. This port also provides a multiplexed low order address/data bus during accesses to external memory. Port 0 has internal pull-up resisters enabled by software.                                                                                 |

| P1.0 – P1.7 | I/O  | <b>PORT 1:</b> Port 1 is a bi-directional I/O port with internal pull-ups. The bits have alternate functions which are described below:<br>T2(P1.0): Timer/Counter 2 external count input<br>T2EX(P1.1): Timer/Counter 2 Reload/Capture/Direction control                                                       |

| P2.0 – P2.7 | I/O  | <b>PORT 2:</b> Port 2 is a bi-directional I/O port with internal pull-ups. This port also provides the upper address bits for accesses to external memory.                                                                                                                                                      |

| P3.0 – P3.7 | I/O  | <b>PORT 3:</b> Port 3 is a bi-directional I/O port with internal pull-ups. All bits have alternate functions, which are described below:   RXD(P3.0) : Serial Port 0 input   TXD(P3.1) : Serial Port 0 output   INT0 (P3.2) : External Interrupt 0                                                              |

|             | 24   | INT1(P3.3) : External Interrupt 1<br>T0(P3.4) : Timer 0 External Input<br>T1(P3.5) : Timer 1 External Input<br>WR (P3.6) : External Data Memory Write Strobe<br>RD (P3.7) : External Data Memory Read Strobe                                                                                                    |

| P4.0 – P4.3 | I/O  | <b>PORT 4:</b> Port 4 is a 4-bit bi-directional I/O port. The P4.3 also provides the alternate function REBOOT which is H/W reboot from LD flash.                                                                                                                                                               |

\* Note: TYPE I : input, O: output, I/O: bi-directional.

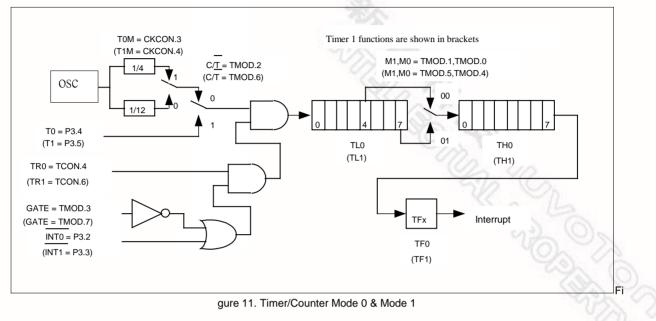

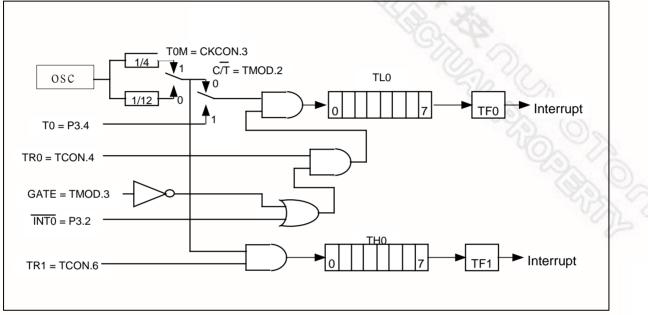

#### Timers

The W79E(L)632 has three 16-bit timers that are functionally similar to the timers of the 8052 family. When used as timers, they can be set to run at either 4 clocks or 12 clocks per count, thus providing the user with the option of operating in a mode that emulates the timing of the original 8052. The W79E(L)632 has an additional feature, the watchdog timer. This timer is used as a System Monitor or as a very long time period timer.

#### Interrupts

The Interrupt structure in the W79E(L)632 is slightly different from that of the standard 8052. Due to the presence of additional features and peripherals, the number of interrupt sources and vectors has been increased. The W79E(L)632 provides 7 interrupt resources with two priority level, including 2 external interrupt sources, timer interrupts, serial I/O interrupts.

#### **Power Management**

Like the standard 80C52, the W79E(L)632 also has IDLE and POWER DOWN modes of operation. In the IDLE mode, the clock to the CPU core is stopped while the timers, serial port and interrupts clock continue to operate. In the POWER DOWN mode, all the clock are stopped and the chip operation is completely stopped. This is the lowest power consumption state.

#### **On-chip Data SRAM**

The W79E(L)632 has 1K Bytes of data space SRAM which is read/write accessible and is memory mapped. This on-chip MOVX SRAM is reached by the MOVX instruction. It is not used for executable program memory. There is no conflict or overlap among the 256 bytes Scratchpad RAM and the 1K Bytes MOVX SRAM as they use different addressing modes and separate instructions. The on-chip MOVX SRAM is enabled by setting the DME0 bit in the PMR register. After a reset, the DME0 bit is cleared such that the on-chip MOVX SRAM is disabled, and all data memory spaces 0000H – FFFFH access to the external memory.

# nuvoTon

|                |                                | TL1.7           | TL1.6      | TL1.5      | TL1.4      | TL1.3      | TL1.2               | TL1.1       | TL1.0      |

|----------------|--------------------------------|-----------------|------------|------------|------------|------------|---------------------|-------------|------------|

|                | • • ·                          |                 | 121.0      | 11.5       | 111.4      |            |                     |             | 121.0      |

|                | Mnemonic                       | : TL1           |            |            |            | A          | ddress: 8l          | Bh          |            |

| TL1.7–0: Timer | 1 LSB                          |                 |            |            |            |            |                     |             |            |

| Timer 0 MSB    |                                |                 |            |            |            |            |                     |             |            |

|                | Bit:                           | 7               | 6          | 5          | 4          | 3          | 2                   | 1           | 0          |

|                |                                | TH0.7           | TH0.6      | TH0.5      | TH0.4      | TH0.3      | TH0.2               | TH0.1       | TH0.0      |

|                | Mnemonic                       | :: TH0          |            |            |            | A          | ddress: 80          | Ch          |            |

| TH0.7–0: Timer | 0 MSB                          |                 |            |            |            |            |                     |             |            |

| Timer 1 MSB    |                                |                 |            |            |            |            |                     |             |            |

|                |                                |                 |            |            |            |            |                     |             |            |

|                | Bit:                           | 7               | 6          | 5          | 4          | 3          | 2                   | Date        | 0          |

|                | Bit:                           | 7<br>TH1.7      | 6<br>TH1.6 | 5<br>TH1.5 | 4<br>TH1.4 | 3<br>TH1.3 | 2<br>TH1.2          | 1<br>TH1.1  | 0<br>TH1.0 |

|                | Bit:<br>Mnemonic               | TH1.7           | 1          | 1          |            | TH1.3      | _                   | TH1.1       |            |

| TH1.7–0: Timer | Mnemonic                       | TH1.7           | 1          | 1          |            | TH1.3      | _<br>TH1.2          | TH1.1       |            |

|                | Mnemonic                       | TH1.7           | 1          | 1          |            | TH1.3      | _<br>TH1.2          | TH1.1       |            |

| TH1.7–0: Timer | Mnemonic                       | TH1.7           | 1          | 1          |            | TH1.3      | _<br>TH1.2          | TH1.1       |            |

| TH1.7–0: Timer | Mnemonic<br><sup>.</sup> 1 MSB | TH1.7<br>:: TH1 | TH1.6      | TH1.5      | TH1.4      | TH1.3<br>A | TH1.2<br>ddress: 8l | TH1.1<br>Dh | TH1.0      |

WD1–0: Watchdog timer mode select bits: These bits determine the time-out period for the watchdog timer. In all four time-out options the reset time-out is 512 clocks more than the interrupt time-out period.

| WD1 | WD0 | Interrupt time-out | Reset time-out        |

|-----|-----|--------------------|-----------------------|

| 0   | 0   | 2 <sup>17</sup>    | 2 <sup>17</sup> + 512 |

| 0   | 1   | 2 <sup>20</sup>    | 2 <sup>20</sup> + 512 |

| 1   | 0   | 2 <sup>23</sup>    | 2 <sup>23</sup> + 512 |

| 1   | 1   | 2 <sup>26</sup>    | 2 <sup>26</sup> + 512 |

- T2M: Timer 2 clock select: When T2M is set to 1, timer 2 uses a divide by 4 clock, and when set to 0 it uses a divide by 12 clock.

- T1M: Timer 1 clock select: When T1M is set to 1, timer 1 uses a divide by 4 clock, and when set to 0 it uses a divide by 12 clock.

- T0M: Timer 0 clock select: When T0M is set to 1, timer 0 uses a divide by 4 clock, and when set to 0 it uses a divide by 12 clock.

#### **Serial Port Control**

| Bit: | 7      | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

|------|--------|-----|-----|-----|-----|-----|----|----|

|      | SM0/FE | SM1 | SM2 | REN | TB8 | RB8 | TI | RI |

|      |        |     |     |     |     |     |    |    |

Mnemonic: SCON

Address: 98h

- SM0/FE: Serial port 0, Mode 0 bit or Framing Error Flag: The SMOD0 bit in PCON SFR determines whether this bit acts as SM0 or as FE. The operation of SM0 is described below. When used as FE, this bit will be set to indicate an invalid stop bit. This bit must be manually cleared in software to clear the FE condition.

- SM1: Serial port Mode bit 1:

| SM0 | SM1 | Mode | Description  | Length | Baud rate  |

|-----|-----|------|--------------|--------|------------|

| 0   | 0   | 0    | Synchronous  | 8      | 4/12 Tclk  |

| 0   | 1   | 1    | Asynchronous | 10     | Variable   |

| 1   | 0   | 2    | Asynchronous | 11     | 64/32 Tclk |

| 1   | 1   | 3    | Asynchronous | 11     | Variable   |

- SM2: Multiple processors communication. Setting this bit to 1 enables the multiprocessor communication feature in mode 2 and 3. In mode 2 or 3, if SM2 is set to 1, then RI will not be activated if the received 9th data bit (RB8) is 0. In mode 1, if SM2 = 1, then RI will not be activated if a valid stop bit was not received. In mode 0, the SM2 bit controls the serial port clock. If set to 0, then the serial port runs at a divide by 12 clock of the oscillator. This gives compatibility with the standard 8052. When set to 1, the serial clock become divide by 4 of the oscillator clock. This results in faster synchronous serial communication.

- REN: Receive enable: When set to 1 serial reception is enabled, otherwise reception is disabled.

- TB8: This is the 9th bit to be transmitted in modes 2 and 3. This bit is set and cleared by software as desired.

- RB8: In modes 2 and 3 this is the received 9th data bit. In mode 1, if SM2 = 0, RB8 is the stop bit that was received. In mode 0 it has no function.

- TI: Transmit interrupt flag: This flag is set by hardware at the end of the 8th bit time in mode 0, or at the beginning of the stop bit in all other modes during serial transmission. This bit must be cleared by software.

- RI: Receive interrupt flag: This flag is set by hardware at the end of the 8th bit time in mode 0, or halfway through the stop bits time in the other modes during serial reception. However the restrictions of SM2 apply to this bit. This bit can be cleared only by software.

#### Serial Data Buffer

| Bit: | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------|--------|--------|--------|--------|--------|--------|--------|--------|

|      | SBUF.7 | SBUF.6 | SBUF.5 | SBUF.4 | SBUF.3 | SBUF.2 | SBUF.1 | SBUF.0 |

|      |        |        |        |        |        |        |        |        |

Mnemonic: SBUF

Address: 99h

SBUF.7-0: Serial data on the serial port 0 is read from or written to this location. It actually consists of two separate internal 8-bit registers. One is the receive resister, and the other is the transmit buffer. Any read access gets data from the receive data buffer, while write access is to the transmit data buffer.

- 15 -

## nuvoton

### 7. INSTRUCTION

The W79E(L)632 executes all the instructions of the standard 8032 family. The operation of these instructions, their effect on the flag bits and the status bits is exactly the same. However, timing of these instructions is different. The reason for this is two fold. Firstly, in the W79E(L)632, each machine cycle consists of 4 clock periods, while in the standard 8032 it consists of 12 clock periods. Also, in the W79E(L)632 there is only one fetch per machine cycle i.e. 4 clocks per fetch, while in the standard 8032 there can be two fetches per machine cycle, which works out to 6 clocks per fetch.

The advantage the W79E(L)632 has is that since there is only one fetch per machine cycle, the number of machine cycles in most cases is equal to the number of operands that the instruction has. In case of jumps and calls there will be an additional cycle that will be needed to calculate the new address. But overall the W79E(L)632 reduces the number of dummy fetches and wasted cycles, thereby improving efficiency as compared to the standard 8032.

#### 7.1 **Instruction Timing**

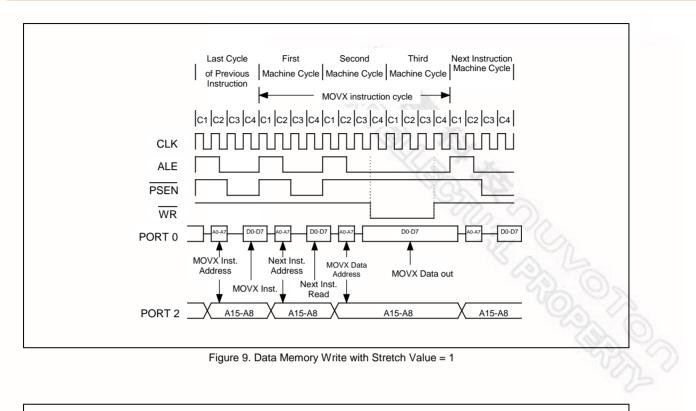

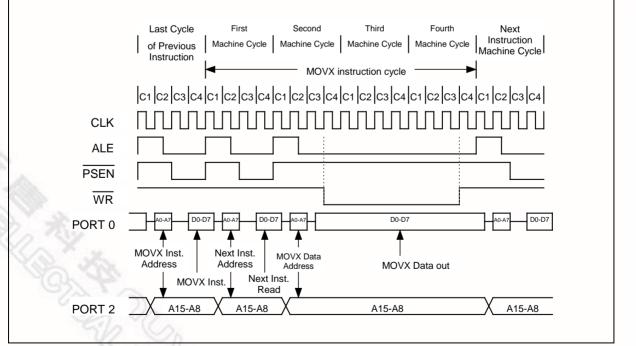

The instruction timing for the W79E(L)632 is an important aspect, especially for those users who wish to use software instructions to generate timing delays. Also, it provides the user with an insight into the timing differences between the W79E(L)632 and the standard 8032. In the W79E(L)632 each machine cycle is four clock periods long. Each clock period is designated a state. Thus each machine cycle is made up of four states, C1, C2 C3 and C4, in that order. Due to the reduced time for each instruction execution, both the clock edges are used for internal timing. Hence it is important that the duty cycle of the clock be as close to 50% as possible to avoid timing conflicts. As mentioned earlier, the W79E(L)632 does one op-code fetch per machine cycle. Therefore, in most of the instructions, the number of machine cycles needed to execute the instruction is equal to the number of bytes in the instruction. Of the 256 available op-codes, 128 of them are single cycle instructions. Thus more than half of all opcodes in the W79E(L)632 are executed in just four clock periods. Most of the two-cycle instructions are those that have two byte instruction codes. However there are some instructions that have only one byte instructions, yet they are two cycle instructions. One instruction which is of importance is the MOVX instruction. In the standard 8032, the MOVX instruction is always two machine cycles long. However in the W79E(L)632, the user has a facility to stretch the duration of this instruction from 2 machine cycles to

9 machine cycles. The RD and WR strobe lines are also proportionately elongated. This gives the user flexibility in accessing both fast and slow peripherals without the use of external circuitry and with minimum software overhead. The rest of the instructions are either three, four or five machine cycle instructions. Note that in the W79E(L)632, based on the number of machine cycles, there are five different types, while in the standard 8032 there are only three. However, in the W79E(L)632 each machine cycle is made of only 4 clock periods compared to the 12 clock periods for the standard 8032. Therefore, even though the number of categories has increased, each instruction is at least 1.5 to 3 che. times faster than the standard 8032 in terms of clock periods.

# nuvoTon

#### Figure 10. Data Memory Write with Stretch Value = 2

Publication Release Date: Nov. 11, 2009 Revision A10

### 8. POWER MANAGEMENT

The W79E(L)632 has several features that help the user to control the power consumption of the device. The power saving features are basically the POWER DOWN mode and the IDLE mode of operation.

### Idle Mode

The user can put the device into idle mode by writing 1 to the bit PCON.0. The instruction that sets the idle bit is the last instruction that will be executed before the device goes into Idle Mode. In the Idle mode, the clock to the CPU is halted, but not to the Interrupt, Timer, Watchdog timer and Serial port blocks. This forces the CPU state to be frozen; the Program counter, the Stack Pointer, the Program Status Word, the Accumulator and the other registers hold their contents. The ALE and PSEN pins are held high during the Idle state. The port pins hold the logical states they had at the time Idle was activated. The Idle mode can be terminated in two ways. Since the interrupt controller is still active, the activation of any enabled interrupt can wake up the processor. This will automatically clear the Idle bit, terminate the Idle mode, and the Interrupt Service Routine(ISR) will be executed. After the ISR, execution of the program will continue from the instruction which put the device into Idle mode.

The Idle mode can also be exited by activating the reset. The device can be put into reset either by applying a high on the external RST pin, a Power on reset condition or a Watchdog timer reset. The external reset pin has to be held high for at least two machine cycles i.e. 8 clock periods to be recognized as a valid reset. In the reset condition the program counter is reset to 0000h and all the SFRs are set to the reset condition. Since the clock is already running there is no delay and execution starts immediately. In the Idle mode, the Watchdog timer continues to run, and if enabled, a time-out will cause a watchdog timer interrupt which will wake up the device. The software must reset the Watchdog timer in order to preempt the reset which will occur after 512 clock periods of the time-out. When the W79E(L)632 is exiting from an Idle mode with a reset, the instruction following the one which put the device into Idle mode is not executed. So there is no danger of unexpected writes.

### **Power Down Mode**

The device can be put into Power Down mode by writing 1 to bit PCON.1. The instruction that does this will be the last instruction to be executed before the device goes into Power Down mode. In the Power Down mode, all the clocks are stopped and the device comes to a halt. All activity is completely stopped and the power consumption is reduced to the lowest possible value. In this state the ALE and PSEN pins are pulled low. The port pins output the values held by their respective SFRs.

The W79E(L)632 will exit the Power Down mode with a reset or by an external interrupt pin enabled as level detect. An external reset can be used to exit the Power down state. The high on RST pin terminates the Power Down mode, and restarts the clock. The program execution will restart from 0000h. In the Power down mode, the clock is stopped, so the Watchdog timer cannot be used to provide the reset to exit Power down mode.

The W79E(L)632 can be woken from the Power Down mode by forcing an external interrupt pin activated, provided the corresponding interrupt is enabled, while the global enable(EA) bit is set and the external input has been set to a level detect mode. If these conditions are met, then the low level on the external pin re-starts the oscillator. Then device executes the interrupt service routine for the corresponding external interrupt. After the interrupt service routine is completed, the program execution returns to the instruction after the one which put the device into Power Down mode and continues from there.

Table 5. Status of external pins during Idle and Power Down

| MODE PROGRAM | ALE | PSEN | PORT0 | PORT1 | PORT2 | PORT3 |

|--------------|-----|------|-------|-------|-------|-------|

|--------------|-----|------|-------|-------|-------|-------|

| SFR NAME | RESET VALUE | SFR NAME | RESET VALUE |

|----------|-------------|----------|-------------|

| SFRCN    | 00111111b   | P4       | xxxx1111b   |

| SCON     | 0000000b    | В        | 0000000b    |

| SBUF     | xxxxxxb     | EIP      | xxx00000b   |

| P2       | 1111111b    | PWMCON1  | 0000000b    |

| PWMCON2  | 0000000b    | PWM0     | 0000000b    |

| PWM1     | 0000000b    | PWM2     | 0000000b    |

| PWM3     | 0000000b    | PWM4     | 0000000b    |

| PWM5     | 0000000b    | 6        | 5.00        |

Table 6. SFR Reset Value, continued

The WDCON SFR bits are set/cleared in reset condition depending on the source of the reset.

|       | External reset | Watchdog reset | Power on reset |

|-------|----------------|----------------|----------------|

| WDCON | 0x0x0xx0b      | 0x0x01x0b      | 0100000b       |

The POR bit WDCON.6 is set only by the power on reset. The WTRF bit WDCON.2 is set when the Watchdog timer causes a reset. A power on reset will also clear this bit. The EWT bit WDCON.1 is cleared by power on resets. This disables the Watchdog timer resets. A watchdog or external reset does not affect the EWT bit.

### **Priority Level Structure**

There are three priority levels for the interrupts, highest, high and low. The interrupt sources can be individually set to either high or low levels. Naturally, a higher priority interrupt cannot be interrupted by a lower priority interrupt. However there exists a pre-defined hierarchy amongst the interrupts themselves. This hierarchy comes into play when the interrupt controller has to resolve simultaneous requests having the same priority level. This hierarchy is defined as shown below; the interrupts are numbered starting from the highest priority to the lowest.

| SOURCE               | FLAG       | VECTOR ADDRESS | PRIORITY LEVEL |

|----------------------|------------|----------------|----------------|

| External Interrupt 0 | IE0        | 0003h          | 1(highest)     |

| Timer 0 Overflow     | TF0        | 000Bh          | 2              |

| External Interrupt 1 | IE1        | 0013h          | 3              |

| Timer 1 Overflow     | TF1        | 001Bh          | 324 0          |

| Serial Port          | RI + TI    | 0023h          | 5              |

| Timer 2 Overflow     | TF2 + EXF2 | 002Bh          | 6              |

| Watchdog Timer       | WDIF       | 0063h          | 7 (lowest)     |

#### Table 7. Priority structure of interrupts

Publication Release Date: Nov. 11, 2009 Revision A10

# nuvoTon

time-base may be either clock cycles/12 or clock cycles/4 as selected by the bits TxM of the CKCON SFR.

#### Mode 1

Mode 1 is similar to Mode 0 except that the counting register forms a 16 bit counter, rather than a 13 bit counter. This means that all the bits of THx and TLx are used. Roll-over occurs when the timer moves from a count of FFFFh to 0000h. The timer overflow flag TFx of the relevant timer is set and if enabled an interrupt will occur. The selection of the time-base in the timer mode is similar to that in Mode 0. The gate function operates similarly to that in Mode 0.

#### Mode 2

In Mode 2, the timer/counter is in the Auto Reload Mode. In this mode, TLx acts as a 8 bit count register, while THx holds the reload value. When the TLx register overflows from FFh to 00h, the TFx bit in TCON is set and TLx is reloaded with the contents of THx, and the counting process continues from here. The reload operation leaves the contents of the THx register unchanged. Counting is enabled by the TRx bit and proper setting of GATE and INTx pins. As in the other two modes 0 and 1 mode 2 allows counting of either clock cycles (clock/12 or clock/4) or pulses on pin Tn.

Publication Release Date: Nov. 11, 2009 Revision A10

### 10.2 Timer/Counter 2

Timer/Counter 2 is a 16 bit up/down counter which is configured by the T2MOD register and controlled by the T2CON register. Timer/Counter 2 is equipped with a capture/reload capability. As with the Timer 0 and Timer 1 counters, there exists considerable flexibility in selecting and controlling the clock, and in defining the operating mode. The clock source for Timer/Counter 2 may be selected for either the external T2 pin (C/T2 = 1) or the crystal oscillator, which is divided by 12 or 4 (C/T2 = 0). The clock is then enabled when TR2 is a 1, and disabled when TR2 is a 0.

Figure 13. Timer/Counter 0 Mode 3

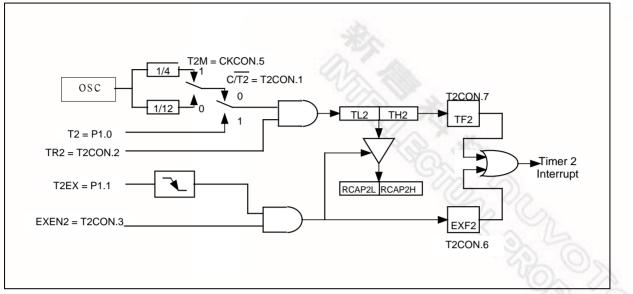

#### Capture Mode

The capture mode is enabled by setting the CP /  $\overline{RL2}$  bit in the T2CON register to a 1. In the capture mode, Timer/Counter 2 serves as a 16 bit up counter. When the counter rolls over from FFFFh to 0000h, the TF2 bit is set, which will generate an interrupt request. If the EXEN2 bit is set, then a negative transition of T2EX pin will cause the value in the TL2 and TH2 register to be captured by the RCAP2L and RCAP2H registers. This action also causes the EXF2 bit in T2CON to be set, which will also generate an interrupt. Setting the T2CR bit (T2MOD.3), the W79E(L)632 allows hardware to reset timer 2 automatically after the value of TL2 and TH2 have been captured.

- 41 -

# nuvoTon

Figure 14. 16-Bit Capture Mode

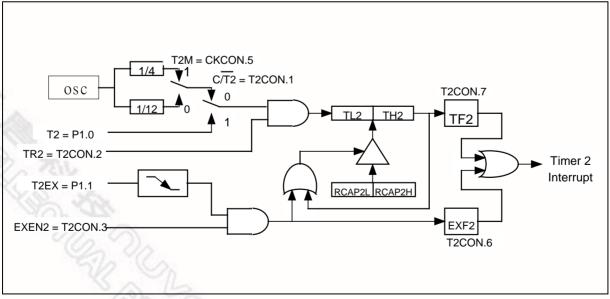

### Auto-reload Mode, Counting up

The auto-reload mode as an up counter is enabled by clearing the CP /  $\overline{RL2}$  bit in the T2CON register and clearing the DCEN bit in T2MOD register. In this mode, Timer/Counter 2 is a 16 bit up counter. When the counter rolls over from FFFFh, a reload is generated that causes the contents of the RCAP2L and RCAP2H registers to be reloaded into the TL2 and TH2 registers. The reload action also sets the TF2 bit. If the EXEN2 bit is set, then a negative transition of T2EX pin will also cause a reload. This action also sets the EXF2 bit in T2CON.

Figure 15. 16-Bit Auto-reload Mode, Counting Up

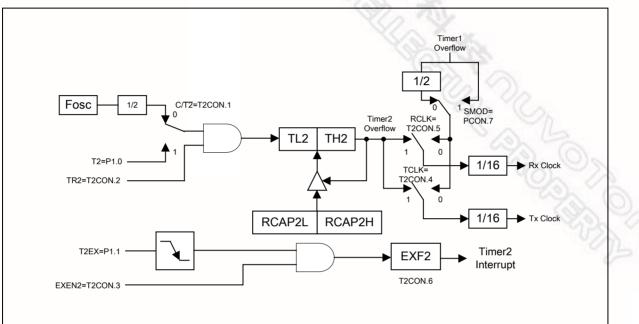

#### **Baud Rate Generator Mode**

The baud rate generator mode is enabled by setting either the RCLK or TCLK bits in T2CON register. While in the baud rate generator mode, Timer/Counter 2 is a 16 bit counter with auto reload when the count rolls over from FFFFh. However, rolling over does not set the TF2 bit. If EXEN2 bit is set, then a negative transition of the T2EX pin will set EXF2 bit in the T2CON register and cause an interrupt request.

Figure 17. Baud Rate Generator Mode

# nuvoton

The Watchdog timer should first be restarted by using RWT. This ensures that the timer starts from a known state. The RWT bit is used to restart the watchdog timer. This bit is self clearing, i.e. after writing a 1 to this bit the software will automatically clear it. The watchdog timer will now count clock cycles. The time-out interval is selected by the two bits WD1 and WD0 (CKCON.7 and CKCON.6). When the selected time-out occurs, the Watchdog interrupt flag WDIF (WDCON.3) is set. After the time-out has occurred, the watchdog timer waits for an additional 512 clock cycles. If the Watchdog Reset EWT (WDCON.1) is enabled, then 512 clocks after the time-out, if there is no RWT, a system reset due to Watchdog timer will occur. This will last for two machine cycles, and the Watchdog timer reset flag WTRF (WDCON.2) will be set. This indicates to the software that the watchdog was the cause of the reset.

When used as a simple timer, the reset and interrupt functions are disabled. The timer will set the WDIF flag each time the timer completes the selected time interval. The WDIF flag is polled to detect a timeout and the RWT allows software to restart the timer. The Watchdog timer can also be used as a very long timer. The interrupt feature is enabled in this case. Every time the time-out occurs an interrupt will occur if the global interrupt enable EA is set.

The main use of the Watchdog timer is as a system monitor. This is important in real-time control applications. In case of some power glitches or electro-magnetic interference, the processor may begin to execute errant code. If this is left unchecked the entire system may crash. Using the watchdog timer interrupt during software development will allow the user to select ideal watchdog reset locations. The code is first written without the watchdog interrupt or reset. Then the watchdog interrupt is enabled to identify code locations where interrupt occurs. The user can now insert instructions to reset the watchdog timer which will allow the code to run without any watchdog timer interrupts. Now the watchdog timer reset is enabled and the watchdog interrupt may be disabled. If any errant code is executed now, then the reset watchdog timer instructions will not be executed at the required instants and watchdog reset will occur.

The watchdog time-out selection will result in different time-out values depending on the clock speed. The reset, when enabled, will occur 512 clocks after the time-out has occurred.

| WD1 | WD0 | WATCHDOG<br>INTERVAL | NUMBER OF<br>CLOCKS | Time<br>@ 1.8432 MHz | Time<br>@ 10 MHz | Time<br>@ 25 MHz |

|-----|-----|----------------------|---------------------|----------------------|------------------|------------------|

| 0   | 0   | 2 <sup>17</sup>      | 131072              | 71.11 mS             | 13.11 mS         | 5.24 mS          |

| 0   | 1   | 2 <sup>20</sup>      | 1048576             | 568.89 mS            | 104.86 mS        | 41.94 mS         |

| 1   | 0   | 2 <sup>23</sup>      | 8388608             | 4551.11 mS           | 838.86 mS        | 335.54 mS        |

| 1   | 1   | 2 <sup>26</sup>      | 67108864            | 36408.88 mS          | 6710.89 mS       | 2684.35 mS       |

The Watchdog timer will de disabled by a power-on/fail reset. The Watchdog timer reset does not disable the watchdog timer, but will restart it. In general, software should restart the timer to put it into a known state.

ADE -The control bits that support the Watchdog timer are discussed below.

- 49 -

#### Watchdog Control

- WDIF: WDCON.3 Watchdog Timer Interrupt flag. This bit is set whenever the time-out occurs in the watchdog timer. If the Watchdog interrupt is enabled (EIE.4), then an interrupt will occur (if the global interrupt enable is set and other interrupt requirements are met). Software or any reset can clear this bit.

- WTRF: WDCON.2 Watchdog Timer Reset flag. This bit is set whenever a watchdog reset occurs. This bit is useful for determined the cause of a reset. Software must read it, and clear it manually. A Power-fail reset will clear this bit. If EWT = 0, then this bit will not be affected by the watchdog timer.

- EWT: WDCON.1 Enable Watchdog timer Reset. This bit when set to 1 will enable the Watchdog timer reset function. Setting this bit to 0 will disable the Watchdog timer reset function, but will leave the timer running.

- RWT: WDCON.0 Reset Watchdog Timer. This bit is used to clear the Watchdog timer and to restart it. This bit is self-clearing, so after the software writes 1 to it the hardware will automatically clear it. If the Watchdog timer reset is enabled, then the RWT has to be set by the user within 512 clocks of the time-out. If this is not done then a Watchdog timer reset will occur.

#### **Clock Control**

WD1, WD0: CKCON.7, CKCON.6 - Watchdog Timer Mode select bits. These two bits select the timeout interval for the watchdog timer. The reset time is 512 clock longer than the interrupt time-out value.

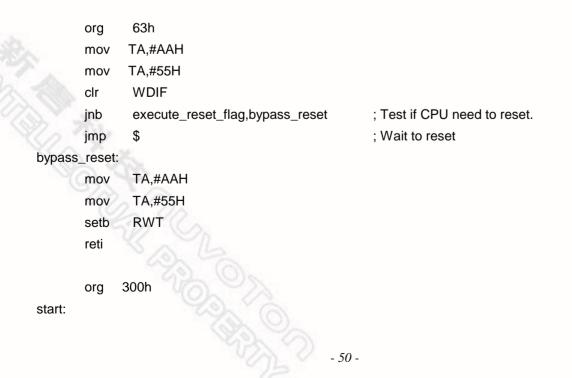

The default Watchdog time-out is 2<sup>17</sup> clocks, which is the shortest time-out period. The EWT, WDIF and RWT bits are protected by the Timed Access procedure. This prevents software from accidentally enabling or disabling the watchdog timer. More importantly, it makes it highly improbable that errant code can enable or disable the watchdog timer. Please refer as below demo program.

#### Mode 2

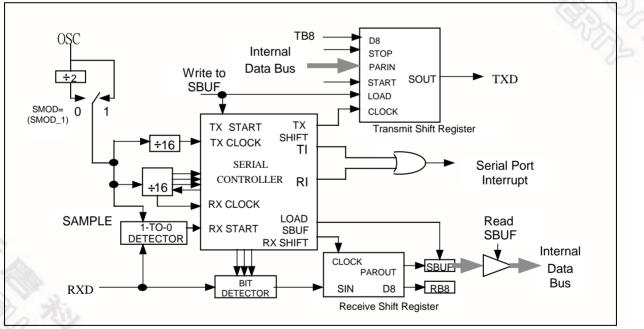

This mode uses a total of 11 bits in asynchronous full-duplex communication. The functional description is shown in the figure below. The frame consists of one start bit (0), 8 data bits (LSB first), a programmable 9th bit (TB8) and a stop bit (0). The 9th bit received is put into RB8. The baud rate is programmable to 1/32 or 1/64 of the oscillator frequency, which is determined by the SMOD bit in PCON SFR. Transmission begins with a write to SBUF. The serial data is brought out on to TxD pin at C1 following the first roll-over of the divide by 16 counter. The next bit is placed on TxD pin at C1 following the next rollover of the divide by 16 counter. Thus the transmission is synchronized to the divide by 16 counter, and not directly to the write to SBUF signal. After all 9 bits of data are transmitted, the stop bit is transmitted. The TI flag is set in the C1 state after the stop bit has been put out on TxD pin. This will be at the 11th rollover of the divide by 16 counter after a write to SBUF. Reception is enabled only if REN is high. The serial port actually starts the receiving of serial data, with the detection of a falling edge on the RxD pin. The 1-to-0 detector continuously monitors the RxD line, sampling it at the rate of 16 times the selected baud rate. When a falling edge is detected, the divide by 16 counter is immediately reset. This helps to align the bit boundaries with the rollovers of the divide by 16 counter. The 16 states of the counter effectively divide the bit time into 16 slices. The bit detection is done on a best of three basis. The bit detector samples the RxD pin, at the 8th, 9th and 10th counter states. By using a majority 2 of 3 voting system, the bit value is selected. This is done to improve the noise rejection feature of the serial port.

Figure 22. Serial Port Mode 2

If the first bit detected after the falling edge of RxD pin, is not 0, then this indicates an invalid start bit, and the reception is immediately aborted. The serial port again looks for a falling edge in the RxD line. If a valid start bit is detected, then the rest of the bits are also detected and shifted into the SBUF. After shifting in 9 data bits, there is one more shift to do, after which the SBUF and RB8 are loaded and RI is set. However certain conditions must be met before the loading and setting of RI can be done.

- 55 -

DC Characteristics, continued

| DADAMETED                                                           | SYM.  | SPECIFICATION |          |      |                           |  |

|---------------------------------------------------------------------|-------|---------------|----------|------|---------------------------|--|

| PARAMETER                                                           |       | MIN.          | MAX.     | UNIT | TEST CONDITIONS           |  |

| Input High Voltage                                                  | Maria | 2.4           | VDD +0.2 | V    | VDD = 5.5V                |  |

| P0, P1, P2, P3, EA                                                  | VIH1  | 1.8           | VDD +0.2 | V    | VDD = 3.3V                |  |

| Innut High Voltage DST                                              | Muse  | 3.5           | VDD +0.2 | V    | VDD = 5.5V                |  |

| Input High Voltage RST                                              | Vih2  | 2.0           | Vdd +0.2 | V    | VDD = 3.3V                |  |

| Input High Voltage<br>XTAL1 <sup>[*3]</sup>                         | Vінз  | 3.5           | Vdd +0.2 | V    | VDD = 5.5V                |  |

| XTAL1 <sup>[*3]</sup>                                               | VIH3  | 2.0           | Vdd +0.2 | V    | VDD = 3.3V                |  |

| Sink current                                                        | Isk1  | 4             | 8        | mA   | VDD = 4.5V, VOL = 0.45    |  |

| P1, P3                                                              | ISKI  | 3.2           | 7        | mA   | VDD = 3.3V, VOL = 0.4     |  |

| Sink current                                                        | 1.1.0 | 10            | 14       | mA   | VDD=4.5V , $VOL=0.45V$    |  |

| P0,P2, ALE, PSEN                                                    | Isk2  | 6.5           | 9.5      | mA   | VDD = 3.3V, VOL=0.4       |  |

| Source current                                                      | T1    | -180          | -330     | uA   | VDD = 4.5V, VOL = 2.4V    |  |

| P1, P2 (I/O), P3                                                    | Isr1  | -100          | -220     | uA   | VDD = 3.3V, VOL = 1.4V    |  |

| Source current                                                      |       |               | -14      | mA   | VDD = 4.5V, VOL = 2.4V    |  |

| P0,P2 (address), ALE,<br>PSEN                                       | Isr2  | -6            | -9       | mA   | VDD = 3.3V, VOL = 1.4V    |  |

| Output Low Voltage                                                  | VOL1  | -             | 0.45     | V    | VDD = 4.5V, IOL = +6 mA   |  |

| P1, P2 (I/O), P3                                                    |       | -             | 0.4      | V    | VDD = 3.3V, IOL = +3.8 mA |  |

| Output Low Voltage<br>P0, P2(address), ALE,<br>PSEN <sup>[*2]</sup> | VOL2  | -             | 0.45     | V    | VDD = 4.5V, IOL = +10 mA  |  |

|                                                                     |       | -             | 0.4      | V    | VDD = 3.3V, IOL = +6.5 mA |  |

| Output High Voltage                                                 | VOH1  | 2.4           | -        | V    | Vdd = 4.5V, Ioh = -180µA  |  |

| P1, P3                                                              |       | 1.4           | -        | V    | VDD = 3.3V, IOL = -100 uA |  |

| Output High Voltage                                                 | VOH2  | 2.4           | -        | V    | VDD = 4.5V, IOH = -10mA   |  |

| P0, P2, ALE, PSEN <sup>[*2]</sup>                                   | V UHZ | 1.4           | -        | V    | VDD = 3.3V, IOL = -6 mA   |  |

Notes:

\*1. RST pin is a Schmitt trigger input.

\*2. P0, ALE and PSEN are tested in the external access mode.

\*3. XTAL1 is a CMOS input.

\*4. Pins of P1, P2, P3 can source a transition current when they are being externally driven from 1 to 0. The transition is me. current reaches its maximum value when VIN approximates to 2V.

- 65 -

### 17.3.2 Operating Frequency vs Voltage

| DEVICE       | OPERATING<br>FREQUENCY | OPERATING<br>VOLTAGE |  |

|--------------|------------------------|----------------------|--|

| W79E632A40PL | Up to 40.0MHz          | 5.0V ~ 5.5V          |  |

|              | Up to 36.8MHz          | 4.5V ~ 5.5V          |  |

| W79L632A25PL | Up to 20.0MHz          | 3.3V ~ 5.5V          |  |

|              | Up to 12.0MHz          | 3.0V ~ 5.5V          |  |

### 17.3.3 MOVX Characteristics Using Strech Memory Cycle

| PARAMETER                                 | SYMBOL             | VARIABLE<br>CLOCK<br>MIN.                            | VARIABLE<br>CLOCK<br>MAX.                                              | UNITS | STRECH                                      |

|-------------------------------------------|--------------------|------------------------------------------------------|------------------------------------------------------------------------|-------|---------------------------------------------|

| Data Access ALE Pulse Width               | t <sub>LLHL2</sub> | 1.5t <sub>CLCL</sub> - 5<br>2.0t <sub>CLCL</sub> - 5 |                                                                        | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$              |

| Address Hold After ALE Low for MOVX write | t <sub>LLAX2</sub> | 0.5t <sub>CLCL</sub> - 5                             |                                                                        | nS    | No.                                         |

| RD Pulse Width                            | t <sub>RLRH</sub>  | 2.0t <sub>CLCL</sub> - 5<br>t <sub>MCS</sub> - 10    |                                                                        | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$              |

| WR Pulse Width                            | t <sub>wLWH</sub>  | 2.0t <sub>CLCL</sub> - 5<br>t <sub>MCS</sub> - 10    |                                                                        | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$              |

| RD Low to Valid Data In                   | t <sub>RLDV</sub>  |                                                      | 2.0t <sub>CLCL</sub> - 20<br>t <sub>MCS</sub> - 20                     | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$              |

| Data Hold after Read                      | t <sub>RHDX</sub>  | 0                                                    |                                                                        | nS    |                                             |

| Data Float after Read                     | t <sub>RHDZ</sub>  |                                                      | t <sub>CLCL</sub> - 5<br>2.0t <sub>CLCL</sub> - 5                      | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$              |

| ALE Low to Valid Data In                  | t <sub>LLDV</sub>  |                                                      | 2.5t <sub>CLCL</sub> - 5<br>t <sub>MCS</sub> + 2t <sub>CLCL</sub> - 40 | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$              |

| Port 0 Address to Valid Data In           | t <sub>AVDV1</sub> |                                                      | 3.0t <sub>CLCL</sub> - 20<br>2.0t <sub>CLCL</sub> - 5                  | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$              |

| ALE Low to RD or WR Low                   | t <sub>LLWL</sub>  | 0.5t <sub>CLCL</sub> - 5<br>1.5t <sub>CLCL</sub> - 5 | 0.5t <sub>CLCL</sub> + 5<br>1.5t <sub>CLCL</sub> + 5                   | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$              |

| Port 0 Address to RD or WR<br>Low         | t <sub>AVWL</sub>  | t <sub>CLCL</sub> - 5<br>2.0t <sub>CLCL</sub> - 5    |                                                                        | nS    | t <sub>MCS</sub> = 0<br>t <sub>MCS</sub> >0 |

| Port 2 Address to RD or WR<br>Low         | t <sub>AVWL2</sub> | 1.5t <sub>CLCL</sub> - 5<br>2.5t <sub>CLCL</sub> - 5 |                                                                        | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$              |

| Data Valid to WR Transition               | t <sub>QVWX</sub>  | -5<br>1.0t <sub>CLCL</sub> - 5                       |                                                                        | nS    | $t_{MCS} = 0$<br>$t_{MCS} > 0$              |

| Data Hold after Write                     | twhqx              | t <sub>CLCL</sub> - 5                                |                                                                        | nS    | t <sub>MCS</sub> = 0                        |

### **18. TYPICAL APPLICATION CIRCUITS**

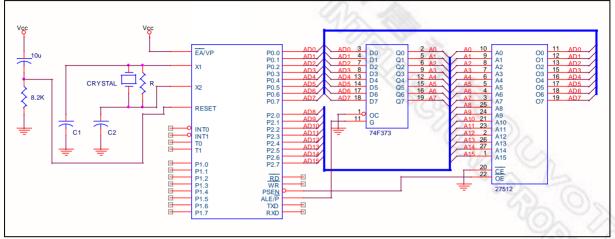

### Expanded External Program Memory and Crystal

| Figure A | ١ |

|----------|---|

|----------|---|

| CRYSTAL | C1  | C2  | R    |

|---------|-----|-----|------|

| 16 MHz  | 20P | 20P | - 6  |

| 24 MHz  | 12P | 12P | -    |

| 33 MHz  | 10P | 10P | 3.3K |

| 40 MHz  | 1P  | 1P  | 3.3K |

The above table shows the reference values for crystal applications.

Note: C1, C2, R components refer to Figure A.

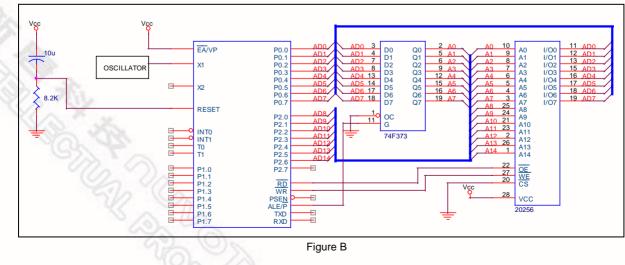

### **Expanded External Data Memory and Oscillator**

- 71 -

### **21. REVISION HISTORY**

| VERSION              | DATE                | PAGE                                                    | DESCRIPTION                                                       |  |  |

|----------------------|---------------------|---------------------------------------------------------|-------------------------------------------------------------------|--|--|

| A1                   | July 8, 2003        | -                                                       | Initial Issued                                                    |  |  |

| A2                   | Apr 28, 2005 2      |                                                         | Add Lead Free package.                                            |  |  |

| A3 Aug 16, 2005      | 2, 4, 10            | Add Port 0 pull-up resisters information                |                                                                   |  |  |

|                      | 59                  | Remove encrypt function of Security bits B2 description |                                                                   |  |  |

| A4 November 6, 2006  | -                   | Add wide voltage device (W79L632)                       |                                                                   |  |  |

|                      |                     | 3                                                       | Add device list.                                                  |  |  |

|                      | 61-62               | Modify DC characteristic.                               |                                                                   |  |  |

|                      |                     | 2                                                       | Remove all Leaded package parts.                                  |  |  |

|                      | 3, 64               | Revise Operating speed to 20MHz on W79L632A25PL.        |                                                                   |  |  |

| 45                   | 2, 3                | Add QFP44 and DIP40 package parts.                      |                                                                   |  |  |

| AD                   | A5 January 03, 2007 | 66, 67                                                  | Add test condition in AC specification.                           |  |  |

| A6                   | February 1, 2007    | 11                                                      | Revise the Timer Mode Setting to "Mode 1: 16-bits, no pre-scale". |  |  |

| A7                   | January 6, 2009     | 2                                                       | 1. Add a note for V <sub>DD</sub> during power on/off.            |  |  |

| A8 February 11, 2009 | February 11, 2000   | 3                                                       | 1. Modify the operating frequency vs voltage                      |  |  |

|                      | rebluary 11, 2009   | 67                                                      | 2. Add 17.3.2 Operating Frequency vs Voltage                      |  |  |

| A9                   | August 18, 2009     | 73                                                      | Add the QFP 44PIN package dimension                               |  |  |

| A10                  | Nov. 11, 2009       | 3                                                       | Remove the DIP40 package                                          |  |  |

### **Important Notice**

Nuvoton Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, "Insecure Usage".

Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, the control or operation of dynamic, brake or safety systems designed for vehicular use, traffic signal instruments, all types of safety devices, and other applications intended to support or sustain life.

All Insecure Usage shall be made at customer's risk, and in the event that third parties lay claims to Nuvoton as a result of customer's Insecure Usage, customer shall indemnify the damages and liabilities thus incurred by Nuvoton.

Please note that all data and specifications are subject to change without notice. All the trademarks of products and companies mentioned in this datasheet belong to their respective owners

- 79 -