Welcome to E-XFL.COM

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | ARM® Cortex®-M3                                                                 |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 40MHz                                                                           |

| Connectivity               | CSIO, EBI/EMI, I <sup>2</sup> C, LINbus, UART/USART, USB                        |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 66                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 12x12b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 80-LQFP                                                                         |

| Supplier Device Package    | 80-LQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb9af314mapmc-g-jne2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### · Watch Counter

The Watch counter is used for wake up from Low-Power Consumption mode.

· Interval timer: up to 64s(Max)@ Sub Clock: 32.768kHz

### · External Interrupt Controller Unit

- · Up to 16 external interrupt input pins.

- · Include one non-maskable interrupt (NMI) input pin.

## · Watch dog Timer (2channels)

A watchdog timer can generate interrupts or a reset when a time-out value is reached.

This series consists of two different watchdogs, a "Hardware" watchdog and a, "Software" watchdog.

The "Hardware" watchdog timer is clocked by the built-in low speed CR oscillator. Therefore, the "Hardware" watchdog is active in any low-power consumption modes except STOP.

#### · CRC (Cyclic Redundancy Check) Accelerator

The CRC accelerator calculates the CRC which has a heavy software processing load, and achieves a reduction of the integrity check processing load for reception data and storage.

CCITT CRC16 and IEEE-802.3 CRC32 are supported.

- · CCITT CRC16 Generator Polynomial: 0x1021

- · IEEE-802.3 CRC32 Generator Polynomial: 0x04C11DB7

#### · Clock and Reset

#### [Clocks]

Selectable from five clock sources (2 external oscillators, 2 built-in CR oscillators, and Main PLL).

Main Clock : 4MHz to 48MHz

Sub Clock : 32.768kHz

Built-in high-speed CR Clock: 4MHz

Built-in low-speed CR Clock: 100kHz

· Main PLL Clock

#### [Resets]

Reset requests from INITX pins, Power on reset, Software reset, watchdog timers reset, low-voltage detection reset and clock supervisor reset.

### · Clock Super Visor (CSV)

Clocks generated by built-in CR oscillators are used to supervise abnormality of the external clocks.

- · External clock failure (clock stop) is detected, reset is asserted.

- · External frequency anomaly is detected, interrupt or reset is asserted.

#### Low-Voltage Detector (LVD)

This Series include 2-stage monitoring of voltage on the VCC. When the voltage falls below the voltage that has been set, Low-Voltage Detector generates an interrupt or reset.

· LVD1: error reporting via interrupt

· LVD2: auto-reset operation

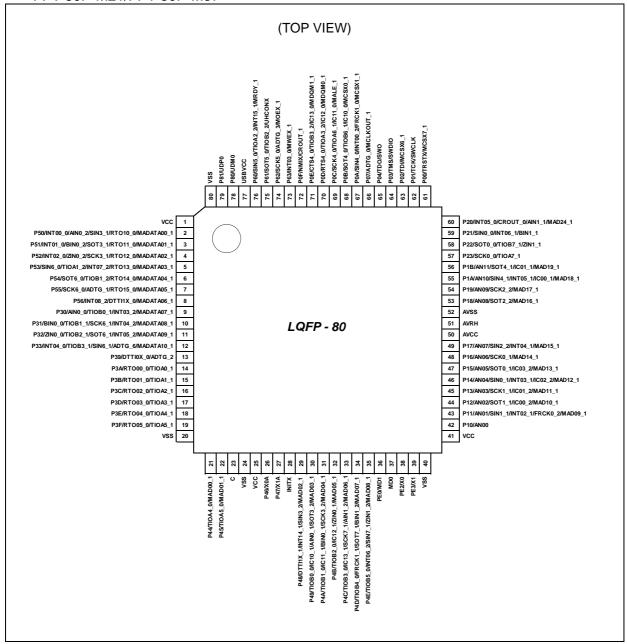

#### FPT-80P-M21/FPT-80P-M37

#### <Note>

The number after the underscore ("\_") in pin names such as XXX\_1 and XXX\_2 indicates the relocated port number. For these pins, there are multiple pins that provide the same function for the same channel. Use the extended port function register (EPFR) to select the pin.

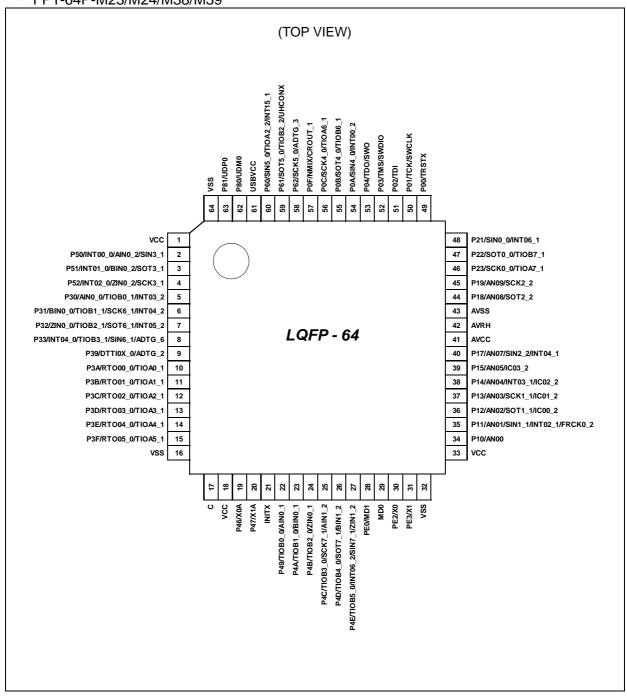

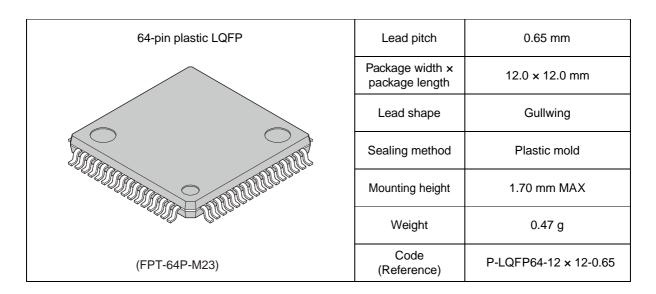

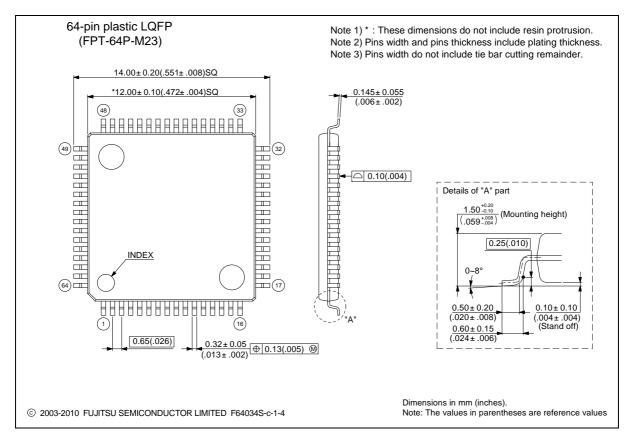

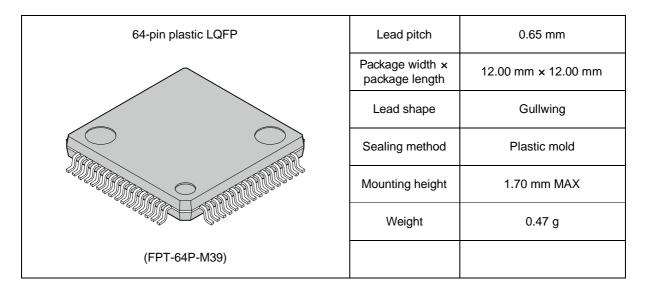

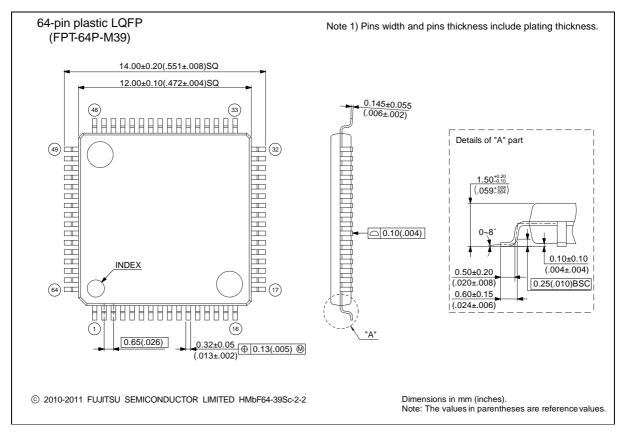

#### · FPT-64P-M23/M24/M38/M39

#### <Note>

The number after the underscore ("\_") in pin names such as XXX\_1 and XXX\_2 indicates the relocated port number. For these pins, there are multiple pins that provide the same function for the same channel. Use the extended port function register (EPFR) to select the pin.

|        |             |                            |       | Pin No |          |       |        |  |  |  |

|--------|-------------|----------------------------|-------|--------|----------|-------|--------|--|--|--|

|        |             |                            | LQFP- | QFP-   |          | LQFP- | I OFP- |  |  |  |

| Module | Pin name    | Function                   | 100   | 100    | 112      | 80    | 64     |  |  |  |

| Wodule | 1 III Haine | 1 diletion                 | 100   | 100    | 112      | 00    | QFN-   |  |  |  |

|        |             |                            |       |        |          |       | 1      |  |  |  |

|        |             |                            |       |        |          |       | 64     |  |  |  |

| GPIO   | P30         |                            | 9     | 87     | E1       | 9     | 5      |  |  |  |

|        | P31         |                            | 10    | 88     | E2       | 10    | 6      |  |  |  |

|        | P32         |                            | 11    | 89     | E3       | 11    | 7      |  |  |  |

|        | P33         |                            | 12    | 90     | E4       | 12    | 8      |  |  |  |

|        | P34         |                            | 13    | 91     | F1       | -     | -      |  |  |  |

|        | P35         |                            | 14    | 92     | F2       | -     | -      |  |  |  |

|        | P36         |                            | 15    | 93     | F3       | -     | -      |  |  |  |

|        | P37         | Comment 2                  | 16    | 94     | G1       | -     | -      |  |  |  |

|        | P38         | General-purpose I/O port 3 | 17    | 95     | G2       | -     | -      |  |  |  |

|        | P39         |                            | 18    | 96     | F4       | 13    | 9      |  |  |  |

|        | P3A         |                            | 19    | 97     | G3       | 14    | 10     |  |  |  |

|        | P3B         |                            | 20    | 98     | H1       | 15    | 11     |  |  |  |

|        | P3C         |                            | 21    | 99     | H2       | 16    | 12     |  |  |  |

|        | P3D         |                            | 22    | 100    | G4       | 17    | 13     |  |  |  |

|        | P3E         |                            | 23    | 1      | H3       | 18    | 14     |  |  |  |

|        | P3F         |                            | 24    | 2      | J2       | 19    | 15     |  |  |  |

|        | P40         |                            | 27    | 5      | J4       | -     | 13     |  |  |  |

|        | P41         |                            | 28    | 6      | L5       | _     | _      |  |  |  |

|        | P42         |                            | 29    | 7      | K5       |       |        |  |  |  |

|        |             |                            |       | 8      |          | -     | -      |  |  |  |

|        | P43<br>P44  |                            | 30    | 9      | J5<br>H5 | 21    | -      |  |  |  |

|        |             |                            | 32    |        |          | 1     |        |  |  |  |

|        | P45         |                            |       | 10     | L6       | 22    | 10     |  |  |  |

|        | P46         |                            | 36    | 14     | L3       | 26    | 19     |  |  |  |

|        | P47         | General-purpose I/O port 4 | 37    | 15     | K3       | 27    | 20     |  |  |  |

|        | P48         |                            | 39    | 17     | K6       | 29    | -      |  |  |  |

|        | P49         |                            | 40    | 18     | J6       | 30    | 22     |  |  |  |

|        | P4A         |                            | 41    | 19     | L7       | 31    | 23     |  |  |  |

|        | P4B         |                            | 42    | 20     | K7       | 32    | 24     |  |  |  |

|        | P4C         |                            | 43    | 21     | Н6       | 33    | 25     |  |  |  |

|        | P4D         |                            | 44    | 22     | J7       | 34    | 26     |  |  |  |

|        | P4E         |                            | 45    | 23     | K8       | 35    | 27     |  |  |  |

|        | P50         |                            | 2     | 80     | C1       | 2     | 2      |  |  |  |

|        | P51         |                            | 3     | 81     | C2       | 3     | 3      |  |  |  |

|        | P52         |                            | 4     | 82     | В3       | 4     | 4      |  |  |  |

|        | P53         | General-purpose I/O port 5 | 5     | 83     | D1       | 5     |        |  |  |  |

|        | P54         |                            | 6     | 84     | D2       | 6     | -      |  |  |  |

|        | P55         |                            | 7     | 85     | D3       | 7     | -      |  |  |  |

|        | P56         |                            | 8     | 86     | D5       | 8     | -      |  |  |  |

|        | P60         |                            | 96    | 74     | C4       | 76    | 60     |  |  |  |

|        | P61         |                            | 95    | 73     | B4       | 75    | 59     |  |  |  |

|        | P62         | General-purpose I/O port 6 | 94    | 72     | C5       | 74    | 58     |  |  |  |

|        | P63         |                            | 93    | 71     | D6       | 73    | -      |  |  |  |

|        | P80         |                            | 98    | 76     | A3       | 78    | 62     |  |  |  |

|        | P81         | General-purpose I/O port 8 | 99    | 77     | A2       | 79    | 63     |  |  |  |

|        | PE0         |                            | 46    | 24     | K9       | 36    | 28     |  |  |  |

|        | PE2         | General-purpose I/O port E | 48    | 26     | L9       | 38    | 30     |  |  |  |

|        | PE3         | General purpose 1/O port E | 49    | 27     | L10      | 39    | 31     |  |  |  |

|        | ГEЭ         |                            | 49    | 41     | LIU      | 39    | 31     |  |  |  |

|          |             |                                                    |       |      | Pin No         | 1     |       |

|----------|-------------|----------------------------------------------------|-------|------|----------------|-------|-------|

|          |             |                                                    | LQFP- | QFP- | BGA-           | LQFP- | LQFP- |

| Module   | Pin name    | Function                                           | 100   | 100  | 112            | 80    | 64    |

|          |             |                                                    |       |      |                |       | QFN-  |

|          |             |                                                    |       |      |                |       | 64    |

| Multi    | SIN2_2      | Multifunction serial interface ch.2                | 59    | 37   | G9             | 49    | 40    |

| Function | 51112_2     | input pin                                          | 39    | 31   | U)             | 47    | 40    |

| Serial   |             | Multifunction serial interface ch.2                |       |      |                |       |       |

| 2        |             | output pin                                         |       |      |                |       |       |

|          | SOT2_2      | This pin operates as SOT2 when it is               | 63    | 41   | G8             | 53    | 44    |

|          | (SDA2_2)    | used in a UART/CSIO/LIN (operation                 | 0.5   | 71   | G <sub>0</sub> | 33    | 7-7   |

|          |             | modes 0 to 3) and as SDA2 when it is               |       |      |                |       |       |

|          |             | used in an I <sup>2</sup> C (operation mode 4).    |       |      |                |       |       |

|          |             | Multifunction serial interface ch.2                |       |      |                |       |       |

|          |             | clock I/O pin                                      |       | 42   | F10            |       |       |

|          | SCK2_2      | This pin operates as SCK2 when it is               | 64    |      |                | 54    | 45    |

|          | (SCL2_2)    | used in a CSIO (operation modes 2)                 |       |      |                |       |       |

|          |             | and as SCL2 when it is used in an I <sup>2</sup> C |       |      |                |       |       |

|          | 27772       | (operation mode 4).                                |       |      | ~.             |       |       |

| Multi    | SIN3_1      | Multifunction serial interface ch.3                | 2     | 80   | C1             | 2     | 2     |

| Function | SIN3_2      | input pin                                          | 39    | 17   | K6             | 29    | -     |

| Serial   | SOT3_1      | Multifunction serial interface ch.3                | 3     | 81   | C2             | 3     | 3     |

| 3        | (SDA3_1)    | output pin                                         |       |      |                |       |       |

|          |             | This pin operates as SOT3 when it is               |       |      |                |       |       |

|          | SOT3_2      | used in a UART/CSIO/LIN (operation                 | 40    | 18   | J6             | 30    | _     |

|          | (SDA3_2)    | modes 0 to 3) and as SDA3 when it is               |       |      |                |       |       |

|          | G GYY 2 . 1 | used in an I <sup>2</sup> C (operation mode 4).    |       |      |                |       |       |

|          | SCK3_1      | Multifunction serial interface ch.3                | 4     | 82   | В3             | 4     | 4     |

|          | (SCL3_1)    | clock I/O pin                                      |       |      |                |       |       |

|          | GGW2 C      | This pin operates as SCK3 when it is               |       |      |                |       |       |

|          | SCK3_2      | used in a CSIO (operation modes 2)                 | 41    | 19   | L7             | 31    | -     |

|          | (SCL3_2)    | and as SCL3 when it is used in an I <sup>2</sup> C |       |      |                |       |       |

|          |             | (operation mode 4).                                |       |      |                |       |       |

| QFP-<br>64<br>QFN-<br>64<br>9<br>-<br>-<br>-<br>-<br>35 |

|---------------------------------------------------------|

| 64<br>QFN-<br>64<br>9<br>-<br>-                         |

| QFN-<br>64<br>9<br>-<br>-                               |

| 9                                                       |

| 9 -                                                     |

| -                                                       |

| -                                                       |

| -                                                       |

| 35                                                      |

| -                                                       |

| -                                                       |

|                                                         |

|                                                         |

| 36                                                      |

| -                                                       |

| -                                                       |

| 37                                                      |

|                                                         |

|                                                         |

| 38                                                      |

| -                                                       |

| -                                                       |

| 39                                                      |

| 10                                                      |

|                                                         |

| _                                                       |

|                                                         |

|                                                         |

| 11                                                      |

|                                                         |

|                                                         |

|                                                         |

| 12                                                      |

|                                                         |

|                                                         |

|                                                         |

| 13                                                      |

|                                                         |

|                                                         |

|                                                         |

| 14                                                      |

|                                                         |

|                                                         |

|                                                         |

|                                                         |

| 15                                                      |

|                                                         |

#### ■ HANDLING PRECAUTIONS

Any semiconductor devices have inherently a certain rate of failure. The possibility of failure is greatly affected by the conditions in which they are used (circuit conditions, environmental conditions, etc.). This page describes precautions that must be observed to minimize the chance of failure and to obtain higher reliability from your FUJITSU SEMICONDUCTOR semiconductor devices.

#### 1. Precautions for Product Design

This section describes precautions when designing electronic equipment using semiconductor devices.

#### Absolute Maximum Ratings

Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of certain established limits, called absolute maximum ratings. Do not exceed these ratings.

## · Recommended Operating Conditions

Recommended operating conditions are normal operating ranges for the semiconductor device. All the device's electrical characteristics are warranted when operated within these ranges.

Always use semiconductor devices within the recommended operating conditions. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their sales representative beforehand.

### · Processing and Protection of Pins

These precautions must be followed when handling the pins which connect semiconductor devices to power supply and input/output functions.

### (1) Preventing Over-Voltage and Over-Current Conditions

Exposure to voltage or current levels in excess of maximum ratings at any pin is likely to cause deterioration within the device, and in extreme cases leads to permanent damage of the device. Try to prevent such overvoltage or over-current conditions at the design stage.

#### (2) Protection of Output Pins

Shorting of output pins to supply pins or other output pins, or connection to large capacitance can cause large current flows. Such conditions if present for extended periods of time can damage the device.

Therefore, avoid this type of connection.

#### (3) Handling of Unused Input Pins

Unconnected input pins with very high impedance levels can adversely affect stability of operation. Such pins should be connected through an appropriate resistance to a power supply pin or ground pin.

#### Latch-up

Semiconductor devices are constructed by the formation of P-type and N-type areas on a substrate. When subjected to abnormally high voltages, internal parasitic PNPN junctions (called thyristor structures) may be formed, causing large current levels in excess of several hundred mA to flow continuously at the power supply pin. This condition is called latch-up.

CAUTION: The occurrence of latch-up not only causes loss of reliability in the semiconductor device, but can cause injury or damage from high heat, smoke or flame. To prevent this from happening, do the following:

- (1) Be sure that voltages applied to pins do not exceed the absolute maximum ratings. This should include attention to abnormal noise, surge levels, etc.

- (2) Be sure that abnormal current flows do not occur during the power-on sequence.

Code: DS00-00004-1Ea

#### Lead-Free Packaging

CAUTION: When ball grid array (BGA) packages with Sn-Ag-Cu balls are mounted using Sn-Pb eutectic soldering, junction strength may be reduced under some conditions of use.

#### Storage of Semiconductor Devices

Because plastic chip packages are formed from plastic resins, exposure to natural environmental conditions will cause absorption of moisture. During mounting, the application of heat to a package that has absorbed moisture can cause surfaces to peel, reducing moisture resistance and causing packages to crack. To prevent, do the following:

- (1) Avoid exposure to rapid temperature changes, which cause moisture to condense inside the product. Store products in locations where temperature changes are slight.

- (2) Use dry boxes for product storage. Products should be stored below 70% relative humidity, and at temperatures between 5°C and 30°C.

When you open Dry Package that recommends humidity 40% to 70% relative humidity.

- (3) When necessary, FUJITSU SEMICONDUCTOR packages semiconductor devices in highly moisture-resistant aluminum laminate bags, with a silica gel desiccant. Devices should be sealed in their aluminum laminate bags for storage.

- (4) Avoid storing packages where they are exposed to corrosive gases or high levels of dust.

### Baking

Packages that have absorbed moisture may be de-moisturized by baking (heat drying). Follow the FUJITSU SEMICONDUCTOR recommended conditions for baking.

Condition: 125°C/24 h

#### Static Electricity

Because semiconductor devices are particularly susceptible to damage by static electricity, you must take the following precautions:

- (1) Maintain relative humidity in the working environment between 40% and 70%. Use of an apparatus for ion generation may be needed to remove electricity.

- (2) Electrically ground all conveyors, solder vessels, soldering irons and peripheral equipment.

- (3) Eliminate static body electricity by the use of rings or bracelets connected to ground through high resistance (on the level of 1  $M\Omega$ ). Wearing of conductive clothing and shoes, use of conductive floor mats and other measures to minimize shock loads is recommended.

- (4) Ground all fixtures and instruments, or protect with anti-static measures.

- (5) Avoid the use of styrofoam or other highly static-prone materials for storage of completed board assemblies.

## · Peripheral Address Map

| · Peripheral Add         | iless iviap              |       | 1                                      |

|--------------------------|--------------------------|-------|----------------------------------------|

| Start address            | End address              | Bus   | Peripherals                            |

| 0x4000_0000 <sub>H</sub> | $0x4000\_0FFF_H$         | AHB   | Flash I/F register                     |

| 0x4000_1000 <sub>H</sub> | $0x4000\_FFFF_H$         | 71112 | Reserved                               |

| 0x4001_0000 <sub>H</sub> | $0x4001\_0FFF_H$         |       | Clock/Reset Control                    |

| $0x4001\_1000_{H}$       | $0x4001\_1FFF_H$         |       | Hardware Watchdog timer                |

| 0x4001_2000 <sub>H</sub> | $0x4001\_2FFF_H$         | APB0  | Software Watchdog timer                |

| 0x4001_3000 <sub>H</sub> | $0x4001\_4FFF_H$         | AIDO  | Reserved                               |

| 0x4001_5000 <sub>H</sub> | $0x4001\_5FFF_H$         |       | Dual-Timer                             |

| 0x4001_6000 <sub>H</sub> | $0x4001\_FFFF_H$         |       | Reserved                               |

| $0x4002\_0000_{H}$       | $0x4002\_0FFF_H$         |       | Multi-function timer unit0             |

| $0x4002\_1000_{H}$       | $0x4002\_1FFF_H$         |       | Multi-function timer unit1             |

| $0x4002\_2000_{H}$       | $0x4002\_3FFF_H$         |       | Reserved                               |

| 0x4002_4000 <sub>H</sub> | $0x4002\_4FFF_H$         |       | PPG                                    |

| 0x4002_5000 <sub>H</sub> | $0x4002\_5FFF_H$         | APB1  | Base Timer                             |

| 0x4002_6000 <sub>H</sub> | $0x4002\_6FFF_H$         | AFDI  | Quadrature Position/Revolution Counter |

| 0x4002_7000 <sub>H</sub> | $0x4002\_7FFF_H$         |       | A/D Converter                          |

| 0x4002_8000 <sub>H</sub> | $0x4002\_DFFF_H$         |       | Reserved                               |

| 0x4002_E000 <sub>H</sub> | 0x4002_EFFF <sub>H</sub> |       | Built-in CR trimming                   |

| 0x4002_F000 <sub>H</sub> | 0x4002_FFFF <sub>H</sub> |       | Reserved                               |

| 0x4003_0000 <sub>H</sub> | 0x4003_0FFF <sub>H</sub> |       | External Interrupt Controller          |

| 0x4003_1000 <sub>H</sub> | 0x4003_1FFF <sub>H</sub> |       | Interrupt Source Check Register        |

| 0x4003_2000 <sub>H</sub> | 0x4003_2FFF <sub>H</sub> |       | Reserved                               |

| 0x4003_3000 <sub>H</sub> | 0x4003_3FFF <sub>H</sub> |       | GPIO                                   |

| 0x4003_4000 <sub>H</sub> | 0x4003_4FFF <sub>H</sub> |       | Reserved                               |

| 0x4003_5000 <sub>H</sub> | 0x4003_5FFF <sub>H</sub> |       | Low-Voltage Detector                   |

| 0x4003_6000 <sub>H</sub> | $0x4003\_6FFF_H$         | APB2  | USB clock generator                    |

| 0x4003_7000 <sub>H</sub> | 0x4003_7FFF <sub>H</sub> |       | Reserved                               |

| 0x4003_8000 <sub>H</sub> | 0x4003_8FFF <sub>H</sub> |       | Multi-function serial                  |

| 0x4003_9000 <sub>H</sub> | 0x4003_9FFF <sub>H</sub> |       | CRC                                    |

| 0x4003_A000 <sub>H</sub> | 0x4003_AFFF <sub>H</sub> |       | Watch Counter                          |

| 0x4003_B000 <sub>H</sub> | 0x4003_EFFF <sub>H</sub> |       | Reserved                               |

| 0x4003_F000 <sub>H</sub> | 0x4003_FFFF <sub>H</sub> |       | External bus interface                 |

| 0x4004_0000 <sub>H</sub> | 0x4004_FFFF <sub>H</sub> |       | USB ch.0                               |

| 0x4005_0000 <sub>H</sub> | 0x4005_FFFF <sub>H</sub> |       | Reserved                               |

| 0x4006_0000 <sub>H</sub> | 0x4006_0FFF <sub>H</sub> |       | DMAC register                          |

| 0x4006_1000 <sub>H</sub> | 0x4006_1FFF <sub>H</sub> | AHB   | Reserved                               |

| 0x4006_2000 <sub>H</sub> | 0x4006_2FFF <sub>H</sub> |       | Reserved                               |

| 0x4006_3000 <sub>H</sub> | 0x4006_3FFF <sub>H</sub> |       | Reserved                               |

| 0x4006_4000 <sub>H</sub> | 0x41FF_FFFF <sub>H</sub> |       | Reserved                               |

|                |                                                                  | Power-on reset                 |                                               |                           | Run mode or                   |                               |                                            |

|----------------|------------------------------------------------------------------|--------------------------------|-----------------------------------------------|---------------------------|-------------------------------|-------------------------------|--------------------------------------------|

| Pin            |                                                                  | or low voltage detection state | INITX input state Device internal reset state |                           | sleep mode<br>state           | Timer mode o                  | r STOP mode<br>ate                         |

| status<br>type | Function group                                                   | Power supply unstable          | Power s                                       | upply stable              | Power supply stable           | Power sup                     | oply stable                                |

|                |                                                                  | -                              | INITX=0                                       | INITX=1                   | INITX=1                       | INIT                          | X=1                                        |

|                |                                                                  | -                              | -                                             | -                         | -                             | SPL=0                         | SPL=1                                      |

| G              | Trace selected                                                   | Setting disabled               | Setting disabled                              | Setting<br>disabled       | Maintain previous             | Maintain previous             | Trace output                               |

|                | GPIO<br>selected, or<br>resource other<br>than above<br>selected | Hi-Z                           | Hi-Z/<br>Input<br>enabled                     | Hi-Z/<br>Input<br>enabled | state                         | state                         | Hi-Z/<br>Internal<br>input fixed<br>at "0" |

| Н              | External interrupt enabled selected                              | Setting<br>disabled            | Setting<br>disabled                           | Setting<br>disabled       | Maintain<br>previous<br>state | Maintain<br>previous<br>state | Maintain<br>previous<br>state              |

|                | GPIO<br>selected, or<br>resource other<br>than above<br>selected | Hi-Z                           | Hi-Z/<br>Input<br>enabled                     | Hi-Z/<br>Input<br>enabled |                               |                               | Hi-Z/<br>Internal<br>input fixed<br>at "0" |

| I              | GPIO selected,<br>resource selected                              | Hi-Z                           | Hi-Z/<br>Input<br>enabled                     | Hi-Z/<br>Input<br>enabled | Maintain<br>previous<br>state | Maintain<br>previous<br>state | Hi-Z/<br>Internal<br>input fixed<br>at "0" |

| J              | NMIX selected                                                    | Setting<br>disabled            | Setting<br>disabled                           | Setting<br>disabled       | Maintain<br>previous<br>state | Maintain<br>previous<br>state | Maintain<br>previous<br>state              |

|                | GPIO<br>selected, or<br>resource other<br>than above<br>selected | Hi-Z                           | Hi-Z/<br>Input<br>enabled                     | Hi-Z/<br>Input<br>enabled |                               |                               | Hi-Z/<br>Internal<br>input fixed<br>at "0" |

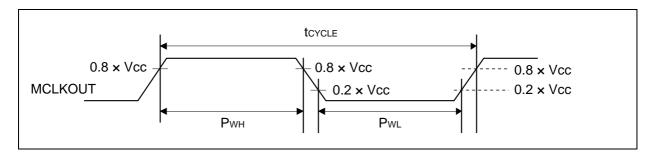

### (7) External Bus Timing

· External bus clock output Characteristics

$(Vcc = 2.7V \text{ to } 5.5V, Vss = 0V, Ta = -40^{\circ}C \text{ to } + 105^{\circ}C)$

| Doromotor           | Symbol             | Pin name     | Conditions              | Va    | Unit |       |  |

|---------------------|--------------------|--------------|-------------------------|-------|------|-------|--|

| Parameter           | Symbol             | Fill flatfie | Conditions              | Min   | Max  | Offic |  |

| Output fraguency    | +                  |              | $Vcc \ge 4.5 \text{ V}$ | ı     | 40   | MHz   |  |

| Output frequency    | $t_{\text{CYCLE}}$ | MOLKOUT      | Vcc < 4.5 V             | -     | 32   | MHz   |  |

| Minimum clock cycle |                    | MCLKOUT      | $Vcc \ge 4.5 \text{ V}$ | 25    | -    | ns    |  |

| time                | -                  |              | Vcc < 4.5 V             | 31.25 | -    | ns    |  |

Note: The external bus clock output is a divided clock of HCLK. For more information about setting of clock divider, see "Chapter: External Bus Interface" in "FM3 Family PERIPHERAL MANUAL" When external bus clock is not output, this characteristics does not give any effect on external bus operation.

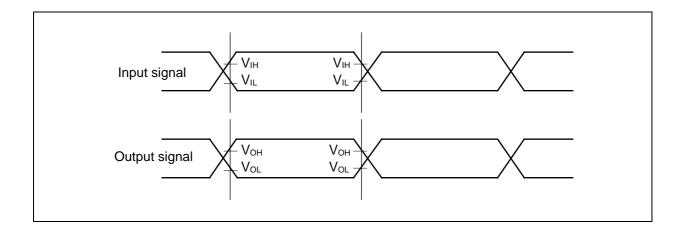

· External bus signal input/output Characteristics

$(Vcc = 2.7V \text{ to } 5.5V, Vss = 0V, Ta = -40^{\circ}C \text{ to } + 105^{\circ}C)$

| Parameter                      | Symbol       | Conditions | Conditions Value |   | Remarks |

|--------------------------------|--------------|------------|------------------|---|---------|

| Signal input abaroataristics   | $V_{IH}$     |            | $0.8 \times VCC$ | V |         |

| Signal input characteristics   | $V_{\rm IL}$ |            | $0.2 \times VCC$ | V |         |

| Cional autout abare atoristics | $V_{OH}$     | -          | $0.8 \times VCC$ | V |         |

| Signal output characteristics  | $V_{OL}$     |            | $0.2 \times VCC$ | V |         |

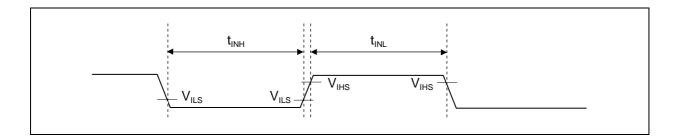

## (10) External input timing

$(Vcc = 2.7V \text{ to } 5.5V, Vss = 0V, Ta = -40^{\circ}C \text{ to } +105^{\circ}C)$

| Parameter         | Symbol           | Pin name        | Conditions                                 | Value                   | Value   |      | Remarks                     |

|-------------------|------------------|-----------------|--------------------------------------------|-------------------------|---------|------|-----------------------------|

| Parameter         | Symbol           | Finname         | Conditions                                 | Min                     | Max     | Unit | Remarks                     |

|                   |                  | ADTG            |                                            |                         |         |      | A/D converter trigger input |

|                   |                  | FRCKx           | -                                          | 2t <sub>CYCP</sub> *1 - | -       | ns   | Free-run timer input clock  |

| Input pulse width | t <sub>INH</sub> | ICxx            |                                            |                         |         |      | Input capture               |

|                   | $t_{ m INL}$     | $DTTI_{v}V$     | DTTIxX - 2t <sub>CYCP</sub> * <sup>1</sup> |                         |         | ns   | Wave form                   |

|                   | DITIX            | DITIXA          |                                            |                         | ZICYCP. |      | generator                   |

|                   |                  | INT00 to INT15, |                                            | $2t_{CYCP} + 100*^{1}$  | -       | ns   | External interrupt          |

|                   |                  | NMIX            | _                                          | 500* <sup>2</sup>       | -       | ns   | NMI                         |

<sup>\*1:</sup> t<sub>CYCP</sub> indicates the APB bus clock cycle time except stop when in stop mode, in timer mode. About the APB bus number which the A/D converter, Multi-function Timer, External interrupt are connected to, see "■BLOCK DIAGRAM" in this data sheet.

<sup>\*2:</sup> When in stop mode, in timer mode.

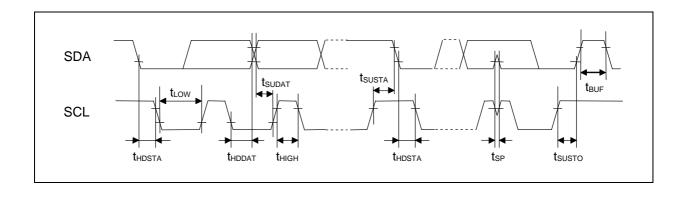

## (12) I<sup>2</sup>C timing

$(Vcc = 2.7V \text{ to } 5.5V, Vss = 0V, Ta = -40^{\circ}C \text{ to } + 105^{\circ}C)$

|                                                      |                    |                  | Турі              | ical               | High-s            | peed       |      |         |

|------------------------------------------------------|--------------------|------------------|-------------------|--------------------|-------------------|------------|------|---------|

| Parameter                                            | Symbol             | Conditions       | mo                | de                 | mo                | de         | Unit | Remarks |

|                                                      |                    |                  | Min               | Max                | Min               | Max        |      |         |

| SCL clock frequency                                  | $F_{SCL}$          |                  | 0                 | 100                | 0                 | 400        | kHz  |         |

| (Repeated) START condition                           |                    |                  |                   |                    |                   |            |      |         |

| hold time                                            | $t_{HDSTA}$        |                  | 4.0               | -                  | 0.6               | -          | μs   |         |

| $SDA \downarrow \rightarrow SCL \downarrow$          |                    |                  |                   |                    |                   |            |      |         |

| SCLclock "L" width                                   | $t_{LOW}$          |                  | 4.7               | -                  | 1.3               | -          | μs   |         |

| SCLclock "H" width                                   | $t_{ m HIGH}$      |                  | 4.0               | -                  | 0.6               | -          | μs   |         |

| (Repeated) START condition                           |                    |                  |                   |                    |                   |            |      |         |

| setup time                                           | $t_{SUSTA}$        | $C_L = 30 pF$ ,  | 4.7               | -                  | 0.6               | -          | μs   |         |

| $SCL \uparrow \rightarrow SDA \downarrow$            |                    | R =              |                   |                    |                   |            |      |         |

| Data hold time                                       | t                  | $(Vp/I_{OL})*^1$ | 0                 | 3.45* <sup>2</sup> | 0                 | $0.9*^{3}$ | μs   |         |

| $SCL \downarrow \rightarrow SDA \downarrow \uparrow$ | $t_{HDDAT}$        | ( • p/10L)       | U                 | 3.43               | U                 | 0.9        | μs   |         |

| Data setup time                                      | $t_{SUDAT}$        |                  | 250               | _                  | 100               | -          | ns   |         |

| $SDA \downarrow \uparrow \rightarrow SCL \uparrow$   | SUDAT              |                  | 230               | _                  | 100               |            | 113  |         |

| STOP condition setup time                            | tarrama            |                  | 4.0               | _                  | 0.6               | -          | μs   |         |

| $SCL \uparrow \rightarrow SDA \uparrow$              | $t_{SUSTO}$        |                  | 7.0               | _                  | 0.0               |            | μδ   |         |

| Bus free time between                                |                    |                  |                   |                    |                   |            |      |         |

| "STOP condition" and                                 | $t_{\mathrm{BUF}}$ |                  | 4.7               | -                  | 1.3               | -          | μs   |         |

| "START condition"                                    |                    |                  |                   |                    |                   |            |      |         |

| Noise filter                                         | $t_{SP}$           | -                | $2 t_{CYCP}^{*4}$ | -                  | $2 t_{CYCP}^{*4}$ | -          | ns   |         |

<sup>\*1 :</sup> R and C represent the pull-up resistor and load capacitance of the SCL and SDA lines, respectively. Vp indicates the power supply voltage of the pull-up resistor and  $I_{OL}$  indicates  $V_{OL}$  guaranteed current.

<sup>\*4 :</sup> t<sub>CYCP</sub> is the APB bus clock cycle time.

About the APB bus number that I<sup>2</sup>C is connected to, see "■BLOCK DIAGRAM" in this data sheet.

To use I<sup>2</sup>C, set the APB bus clock at 8 MHz or more.

<sup>\*2 :</sup> The maximum  $t_{HDDAT}$  must satisfy that it does not extend at least "L" period  $(t_{LOW})$  of device's SCL signal.

<sup>\*3 :</sup> A high-speed mode  $I^2C$  bus device can be used on a standard mode  $I^2C$  bus system as long as the device satisfies the requirement of " $t_{SUDAT} \ge 250$  ns".

### 5. 12-bit A/D Converter

· Electrical Characteristics for the A/D Converter

$(Vcc = AVcc = 2.7V \text{ to } 5.5V, Vss = AVss = 0V, Ta = -40^{\circ}C \text{ to } + 105^{\circ}C)$

| Davasatas                                     | Pin            |         | Value | 10 0.0 1, 1 55 |      | Damanta                            |

|-----------------------------------------------|----------------|---------|-------|----------------|------|------------------------------------|

| Parameter                                     | name           | Min     | Тур   | Max            | Unit | Remarks                            |

| Resolution                                    | -              | -       | -     | 12             | bit  |                                    |

| Non-linearity error                           | -              | - 4.5   | -     | + 4.5          | LSB  |                                    |

| Differential linearity error                  | -              | - 2.5   | -     | + 2.5          | LSB  |                                    |

| Zero transition voltage                       | AN0 to<br>AN15 | - 20    | -     | + 20           | mV   | AVRH = 2.7V  to  5.5V              |

| Full-scale transition voltage                 | AN0 to<br>AN15 | AVRH-20 | -     | AVRH+20        | mV   |                                    |

| Conversion time                               | -              | 1.0*1   | -     | -              | μs   | $AVcc \ge 4.5V$                    |

| Sampling time                                 | Ts             | *2      | =     | -              | ns   | $AVcc \ge 4.5V$                    |

| Sampling time                                 | 15             | *2      | -     | -              | 115  | AVcc < 4.5V                        |

| Compare clock cycle*3                         | Teck           | 50      | -     | 2000           | ns   |                                    |

| State transition time to operation permission | Tstt           | 1.0     | -     | -              | μs   |                                    |

| Power supply current                          | AVCC           | -       | 0.57  | 0.72           | mA   | A/D 1unit operation                |

| (analog + digital)                            | AVCC           | -       | 0.06  | 20             | μΑ   | When A/D stops                     |

| Reference power supply current                | AVRH           | -       | 1.1   | 1.96           | mA   | A/D 1unit operation<br>AVRH = 5.5V |

| (between AVRH and AVSS)                       | 717101         | -       | 0.06  | 4              | μΑ   | When A/D stops                     |

| Analog input capacity                         | Cin            | -       | -     | 12.9           | pF   |                                    |

| Analog input resistor                         | Rin            | -       | -     | 3.8            | kΩ   | $AVcc \ge 4.5V$ $AVcc < 4.5V$      |

| Interchannel disparity                        | -              | -       | -     | 4              | LSB  |                                    |

| Analog port input current                     | AN0 to<br>AN15 | -       | -     | 5              | μΑ   |                                    |

| Analog input voltage                          | AN0 to<br>AN15 | AVSS    |       | AVRH           | V    |                                    |

| Reference voltage                             | AVRH           | 2.7     | -     | AVCC           | V    |                                    |

<sup>\*1:</sup> The conversion time is the value of sampling time (Ts) + compare time (Tc).

The condition of the minimum conversion time is when the value of sampling time: 300ns, the value of compare time: 700ns ( $AVcc \ge 4.5V$ ).

Ensure that it satisfies the value of the sampling time (Ts) and compare clock cycle (Tcck).

For setting of the sampling time and compare clock cycle, see "Chapter: A/D Converter" in "FM3 Family PERIPHERAL MANUAL Analog Macro Part".

The A/D Converter register is set at APB bus clock timing. The sampling clock and compare clock are set at Base clock (HCLK).

Ensure that it set the sampling time to satisfy (Equation 1)

<sup>\*2:</sup> A necessary sampling time changes by external impedance.

<sup>\*3:</sup> The compare time (Tc) is the value of (Equation 2)

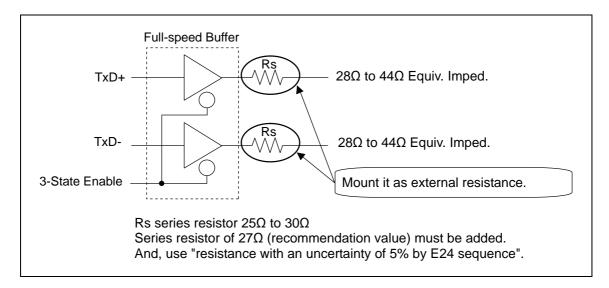

\*6 : USB Full-speed connection is performed via twist pair cable shield with  $90\Omega \pm 15\%$  characteristic impedance(Differential Mode).

USB standard defines that output impedance of USB driver must be in range from  $28\Omega$ to  $44\Omega$ . So, discrete series resistor (Rs) addition is defined in order to satisfy the above definition and keep balance. When using this USB FLS I/O, use it with  $25\Omega$  to  $30\Omega$  (recommendation value  $27\Omega$ ) series resistor Rs.

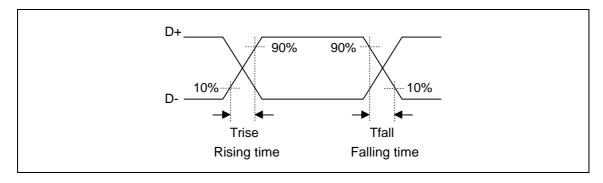

\*7: They indicate rising time (Trise) and falling time (Tfall) of the low-speed differential data signal. They are defined by the time between 10% and 90% of the output signal voltage.

See "· Low-Speed Load (Compliance Load)" for conditions of external load.

Please check the latest package dimension at the following URL. http://edevice.fujitsu.com/package/en-search/

Please check the latest package dimension at the following URL. http://edevice.fujitsu.com/package/en-search/