Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2010.00                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | AVR                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 512 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega164pv-10au |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.5.1 SPH and SPL – Stack Pointer High and Stack pointer Low

| Bit           | 15  | 14  | 13  | 12                   | 11                   | 10                   | 9   | 8   |     |

|---------------|-----|-----|-----|----------------------|----------------------|----------------------|-----|-----|-----|

| 0x3E (0x5E)   | -   | -   | -   | SP12                 | SP11                 | SP10                 | SP9 | SP8 | SPH |

| 0x3D (0x5D)   | SP7 | SP6 | SP5 | SP4                  | SP3                  | SP2                  | SP1 | SP0 | SPL |

|               | 7   | 6   | 5   | 4                    | 3                    | 2                    | 1   | 0   |     |

| Read/Write    | R   | R   | R   | R/W                  | R/W                  | R/W                  | R/W | R/W |     |

|               | R/W | R/W | R/W | R/W                  | R/W                  | R/W                  | R/W | R/W |     |

| Initial Value | 0   | 0   | 0   | 0/0/1 <sup>(1)</sup> | 0/1/0 <sup>(1)</sup> | 1/0/0 <sup>(1)</sup> | 0   | 0   |     |

|               | 1   | 1   | 1   | 1                    | 1                    | 1                    | 1   | 1   |     |

Note: 1. Initial values respectively for the ATmega164P/324P/644P.

#### Table 4-2. Stack Pointer size

| Device     | Stack Pointer size |

|------------|--------------------|

| ATmega164P | SP[10:0]           |

| ATmega324P | SP[11:0]           |

| ATmega644P | SP[12:0]           |

#### 4.5.2 RAMPZ – Extended Z-pointer Register for ELPM/SPM

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

| 0x3B (0x5B)   | RAMPZ7 | RAMPZ6 | RAMPZ5 | RAMPZ4 | RAMPZ3 | RAMPZ2 | RAMPZ1 | RAMPZ0 | RAMPZ |

| Read/Write    | R/W    |       |

| Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

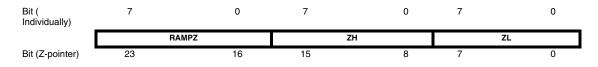

For ELPM/SPM instructions, the Z-pointer is a concatenation of RAMPZ, ZH, and ZL, as shown in Figure 4-4. Note that LPM is not affected by the RAMPZ setting.

Figure 4-4. The Z-pointer used by ELPM and SPM

The actual number of bits is implementation dependent. Unused bits in an implementation will always read as zero. For compatibility with future devices, be sure to write these bits to zero.

### 4.6 Instruction Execution Timing

This section describes the general access timing concepts for instruction execution. The AVR CPU is driven by the CPU clock  $clk_{CPU}$ , directly generated from the selected clock source for the chip. No internal clock division is used.

Figure 4-5 on page 15 shows the parallel instruction fetches and instruction executions enabled by the Harvard architecture and the fast-access Register File concept. This is the basic pipelining concept to obtain up to 1 MIPS per MHz with the corresponding unique results for functions per cost, functions per clocks, and functions per power-unit.

The following code examples show one assembly and one C function for writing to the EEPROM. The examples assume that interrupts are controlled (e.g. by disabling interrupts globally) so that no interrupts will occur during execution of these functions. The examples also assume that no Flash Boot Loader is present in the software. If such code is present, the EEPROM write function must also wait for any ongoing SPM command to finish.

```

Assembly Code Example<sup>()</sup>

EEPROM_write:

; Wait for completion of previous write

sbic EECR, EEPE

rjmp EEPROM_write

; Set up address (r18:r17) in address register

out EEARH, r18

out EEARL, r17

; Write data (r16) to Data Register

out EEDR, r16

; Write logical one to EEMPE

sbi EECR, EEMPE

; Start eeprom write by setting EEPE

sbi EECR, EEPE

ret

C Code Example<sup>(1)</sup>

void EEPROM_write(unsigned int uiAddress, unsigned char ucData)

{

/* Wait for completion of previous write */

while(EECR & (1<<EEPE))

;

/* Set up address and Data Registers */

EEAR = uiAddress;

EEDR = ucData;

/* Write logical one to EEMPE */

EECR | = (1 < < EEMPE);

/* Start eeprom write by setting EEPE */

EECR \mid = (1<<EPE);

}

```

```

Note: 1. See "About Code Examples" on page 8.

```

```

Assembly Code Example

Move_interrupts:

; Get MCUCR

in r16, MCUCR

mov r17, r16

; Enable change of Interrupt Vectors

ori r16, (1<<IVCE)

out MCUCR, r16

; Move interrupts to Boot Flash section

ori r17, (1<<IVSEL)

out MCUCR, r17

ret

C Code Example

void Move_interrupts(void)

{

uchar temp;

/* GET MCUCR*/

temp = MCUCR;

/* Enable change of Interrupt Vectors */

MCUCR = temp | (1<<IVCE);

/* Move interrupts to Boot Flash section */

MCUCR = temp | (1<<IVSEL);

}

```

# **10. External Interrupts**

# 10.1 Overview

The External Interrupts are triggered by the INT2:0 pin or any of the PCINT31:0 pins. Observe that, if enabled, the interrupts will trigger even if the INT2:0 or PCINT31:0 pins are configured as outputs. This feature provides a way of generating a software interrupt.

The Pin change interrupt PCI3 will trigger if any enabled PCINT31:24 pin toggle, Pin change interrupt PCI2 will trigger if any enabled PCINT23:16 pin toggles, Pin change interrupt PCI1 if any enabled PCINT15:8 toggles and Pin change interrupts PCI0 will trigger if any enabled PCINT7:0 pin toggles. PCMSK3, PCMSK2, PCMSK1 and PCMSK0 Registers control which pins contribute to the pin change interrupts. Pin change interrupts on PCINT31:0 are detected asynchronously. This implies that these interrupts can be used for waking the part also from sleep modes other than Idle mode.

The External Interrupts can be triggered by a falling or rising edge or a low level. This is set up as indicated in the specification for the External Interrupt Control Registers – EICRA (INT2:0). When the external interrupt is enabled and is configured as level triggered, the interrupt will trigger as long as the pin is held low. Low level interrupts and the edge interrupt on INT2:0 are detected asynchronously. This implies that these interrupts can be used for waking the part also from sleep modes other than Idle mode. The I/O clock is halted in all sleep modes except Idle mode.

Note that if a level triggered interrupt is used for wake-up from Power-down, the required level must be held long enough for the MCU to complete the wake-up to trigger the level interrupt. If the level disappears before the end of the Start-up Time, the MCU will still wake up, but no interrupt will be generated. The start-up time is defined by the SUT and CKSEL Fuses as described in "System Clock and Clock Options" on page 29.

# 10.2 Register Description

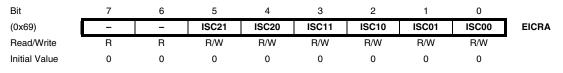

# 10.2.1 EICRA – External Interrupt Control Register A

The External Interrupt Control Register A contains control bits for interrupt sense control.

### • Bits 7:6 - Reserved

These bits are reserved in the ATmega164P/324P/644P, and will always read as zero.

### • Bits 5:0 – ISC21, ISC20 – ISC00, ISC00: External Interrupt 2 - 0 Sense Control Bits

The External Interrupts 2 - 0 are activated by the external pins INT2:0 if the SREG I-flag and the corresponding interrupt mask in the EIMSK is set. The level and edges on the external pins that activate the interrupts are defined in Table 10-1. Edges on INT2..INT0 are registered asynchronously. Pulses on INT2:0 pins wider than the minimum pulse width given in "External Interrupts Characteristics" on page 331 will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low level interrupt is selected, the low level must be held until the com-

Note that enabling the alternate function of some of the port pins does not affect the use of the other pins in the port as general digital I/O.

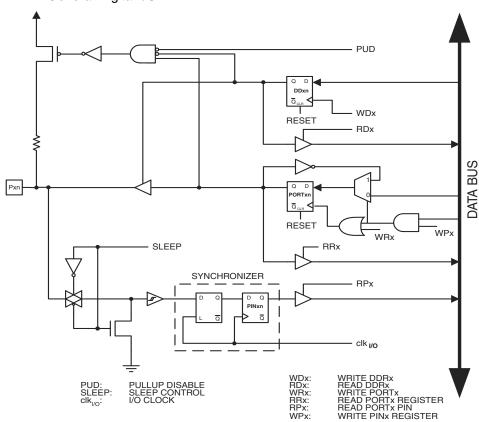

## 11.2 Ports as General Digital I/O

The ports are bi-directional I/O ports with optional internal pull-ups. Figure 11-2 shows a functional description of one I/O-port pin, here generically called Pxn.

Note: 1. WRx, WPx, WDx, RRx, RPx, and RDx are common to all pins within the same port. clk<sub>I/O</sub>, SLEEP, and PUD are common to all ports.

# 11.2.1 Configuring the Pin

Each port pin consists of three register bits: DDxn, PORTxn, and PINxn. As shown in "Register Description" on page 91, the DDxn bits are accessed at the DDRx I/O address, the PORTxn bits at the PORTx I/O address, and the PINxn bits at the PINx I/O address.

The DDxn bit in the DDRx Register selects the direction of this pin. If DDxn is written logic one, Pxn is configured as an output pin. If DDxn is written logic zero, Pxn is configured as an input pin.

If PORTxn is written logic one when the pin is configured as an input pin, the pull-up resistor is activated. To switch the pull-up resistor off, PORTxn has to be written logic zero or the pin has to be configured as an output pin. The port pins are tri-stated when reset condition becomes active, even if no clocks are running.

Table 11-4 on page 81 and Table 11-5 on page 81 relates the alternate functions of Port A to the overriding signals shown in Figure 11-5 on page 78.

| Signal<br>Name | PA7/ADC7/<br>PCINT7       |                           |                           | PA4/ADC4/<br>PCINT4       |

|----------------|---------------------------|---------------------------|---------------------------|---------------------------|

| PUOE           | 0                         | 0                         | 0                         | 0                         |

| PUOV           | 0                         | 0                         | 0                         | 0                         |

| DDOE           | 0                         | 0                         | 0                         | 0                         |

| DDOV           | 0                         | 0                         | 0                         | 0                         |

| PVOE           | 0                         | 0                         | 0                         | 0                         |

| PVOV           | 0                         | 0                         | 0                         | 0                         |

| DIEOE          | PCINT7 • PCIE0 +<br>ADC7D | PCINT6 • PCIE0 +<br>ADC6D | PCINT5 • PCIE0 +<br>ADC5D | PCINT4 • PCIE0 +<br>ADC4D |

| DIEOV          | PCINT7 • PCIE0            | PCINT6 • PCIE0            | PCINT5 • PCIE0            | PCINT4 • PCIE0            |

| DI             | PCINT7 INPUT              | PCINT6 INPUT              | PCINT5 INPUT              | PCINT4 INPUT              |

| AIO            | ADC7 INPUT                | ADC6 INPUT                | ADC5 INPUT                | ADC4 INPUT                |

Table 11-4.

Overriding Signals for Alternate Functions in PA7:PA4

Table 11-5.

Overriding Signals for Alternate Functions in PA3:PA0

| Signal<br>Name | PA3/ADC3/<br>PCINT3       | PA2/ADC2/<br>PCINT2       | PA1/ADC1/<br>PCINT1       | PA0/ADC0/<br>PCINT0       |

|----------------|---------------------------|---------------------------|---------------------------|---------------------------|

| PUOE           | 0                         | 0                         | 0                         | 0                         |

| PUOV           | 0                         | 0                         | 0                         | 0                         |

| DDOE           | 0                         | 0                         | 0                         | 0                         |

| DDOV           | 0                         | 0                         | 0                         | 0                         |

| PVOE           | 0                         | 0                         | 0                         | 0                         |

| PVOV           | 0                         | 0                         | 0                         | 0                         |

| DIEOE          | PCINT3 • PCIE0 +<br>ADC3D | PCINT2 • PCIE0 +<br>ADC2D | PCINT1 • PCIE0 +<br>ADC1D | PCINT0 • PCIE0 +<br>ADC0D |

| DIEOV          | PCINT3 • PCIE0            | PCINT2 • PCIE0            | PCINT1 • PCIE0            | PCINT0 • PCIE0            |

| DI             | PCINT3 INPUT              | PCINT2 INPUT              | PCINT1 INPUT              | PCINT0 INPUT              |

| AIO            | ADC3 INPUT                | ADC2 INPUT                | ADC1 INPUT                | ADC0 INPUT                |

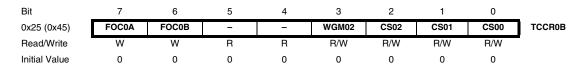

### 12.9.2 TCCR0B – Timer/Counter Control Register B

### • Bit 7 – FOC0A: Force Output Compare A

The FOC0A bit is only active when the WGM bits specify a non-PWM mode.

However, for ensuring compatibility with future devices, this bit must be set to zero when TCCR0B is written when operating in PWM mode. When writing a logical one to the FOC0A bit, an immediate Compare Match is forced on the Waveform Generation unit. The OC0A output is changed according to its COM0A1:0 bits setting. Note that the FOC0A bit is implemented as a strobe. Therefore it is the value present in the COM0A1:0 bits that determines the effect of the forced compare.

A FOC0A strobe will not generate any interrupt, nor will it clear the timer in CTC mode using OCR0A as TOP.

The FOC0A bit is always read as zero.

#### • Bit 6 – FOC0B: Force Output Compare B

The FOC0B bit is only active when the WGM bits specify a non-PWM mode.

However, for ensuring compatibility with future devices, this bit must be set to zero when TCCR0B is written when operating in PWM mode. When writing a logical one to the FOC0B bit, an immediate Compare Match is forced on the Waveform Generation unit. The OC0B output is changed according to its COM0B1:0 bits setting. Note that the FOC0B bit is implemented as a strobe. Therefore it is the value present in the COM0B1:0 bits that determines the effect of the forced compare.

A FOC0B strobe will not generate any interrupt, nor will it clear the timer in CTC mode using OCR0B as TOP.

The FOC0B bit is always read as zero.

#### • Bits 5:4 - Res: Reserved Bits

These bits are reserved bits and will always read as zero.

#### • Bit 3 – WGM02: Waveform Generation Mode

See the description in the "TCCR0A – Timer/Counter Control Register A" on page 104.

```

Assembly Code Examples<sup>(1)</sup>

...

; Set TCNTN to 0x01FF

Idi r17,0x01

Idi r16,0xFF

out TCNTNH,r17

out TCNTNL,r16

; Read TCNTN into r17:r16

in r16,TCNTNL

in r17,TCNTNH

...

C Code Examples<sup>(1)</sup>

unsigned int i;

```

```

...

/* Set TCNTn to 0x01FF */

TCNTn = 0x1FF;

/* Read TCNTn into i */

i = TCNTn;

....

```

Note: 1. The example code assumes that the part specific header file is included. For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

The assembly code example returns the TCNTn value in the r17:r16 register pair.

It is important to notice that accessing 16-bit registers are atomic operations. If an interrupt occurs between the two instructions accessing the 16-bit register, and the interrupt code updates the temporary register by accessing the same or any other of the 16-bit Timer Registers, then the result of the access outside the interrupt will be corrupted. Therefore, when both the main code and the interrupt code update the temporary register, the main code must disable the interrupts during the 16-bit access.

prevents the occurrence of odd-length, non-symmetrical PWM pulses, thereby making the output glitch-free.

The OCRnx Register access may seem complex, but this is not case. When the double buffering is enabled, the CPU has access to the OCRnx Buffer Register, and if double buffering is disabled the CPU will access the OCRnx directly. The content of the OCR1x (Buffer or Compare) Register is only changed by a write operation (the Timer/Counter does not update this register automatically as the TCNT1 and ICR1 Register). Therefore OCR1x is not read via the high byte temporary register (TEMP). However, it is a good practice to read the low byte first as when accessing other 16-bit registers. Writing the OCRnx Registers must be done via the TEMP Register since the compare of all 16 bits is done continuously. The high byte (OCRnxH) has to be written first. When the high byte I/O location is written by the CPU, the TEMP Register will be updated by the value written. Then when the low byte (OCRnxL) is written to the lower eight bits, the high byte will be copied into the upper 8-bits of either the OCRnx buffer or OCRnx Compare Register in the same system clock cycle.

For more information of how to access the 16-bit registers refer to "Accessing 16-bit Registers" on page 113.

#### 13.7.1 Force Output Compare

In non-PWM Waveform Generation modes, the match output of the comparator can be forced by writing a one to the *Force Output Compare* (FOCnx) bit. Forcing compare match will not set the OCFnx Flag or reload/clear the timer, but the OCnx pin will be updated as if a real compare match had occurred (the COMn1:0 bits settings define whether the OCnx pin is set, cleared or toggled).

#### 13.7.2 Compare Match Blocking by TCNTn Write

All CPU writes to the TCNTn Register will block any compare match that occurs in the next timer clock cycle, even when the timer is stopped. This feature allows OCRnx to be initialized to the same value as TCNTn without triggering an interrupt when the Timer/Counter clock is enabled.

### 13.7.3 Using the Output Compare Unit

Since writing TCNTn in any mode of operation will block all compare matches for one timer clock cycle, there are risks involved when changing TCNTn when using any of the Output Compare channels, independent of whether the Timer/Counter is running or not. If the value written to TCNTn equals the OCRnx value, the compare match will be missed, resulting in incorrect waveform generation. Do not write the TCNTn equal to TOP in PWM modes with variable TOP values. The compare match for the TOP will be ignored and the counter will continue to 0xFFFF. Similarly, do not write the TCNTn value equal to BOTTOM when the counter is downcounting.

The setup of the OCnx should be performed before setting the Data Direction Register for the port pin to output. The easiest way of setting the OCnx value is to use the Force Output Compare (FOCnx) strobe bits in Normal mode. The OCnx Register keeps its value even when changing between Waveform Generation modes.

Be aware that the COMnx1:0 bits are not double buffered together with the compare value. Changing the COMnx1:0 bits will take effect immediately.

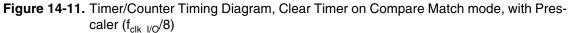

Figure 14-11 on page 150 shows the setting of OCF2A and the clearing of TCNT2 in CTC mode.

### 14.9 Asynchronous Operation of Timer/Counter2

When Timer/Counter2 operates asynchronously, some considerations must be taken.

- Warning: When switching between asynchronous and synchronous clocking of Timer/Counter2, the Timer Registers TCNT2, OCR2x, and TCCR2x might be corrupted. A safe procedure for switching clock source is:

- a. Disable the Timer/Counter2 interrupts by clearing OCIE2x and TOIE2.

- b. Select clock source by setting AS2 as appropriate.

- c. Write new values to TCNT2, OCR2x, and TCCR2x.

- d. To switch to asynchronous operation: Wait for TCN2UB, OCR2xUB, and TCR2xUB.

- e. Clear the Timer/Counter2 Interrupt Flags.

- f. Enable interrupts, if needed.

- The CPU main clock frequency must be more than four times the Oscillator frequency.

- When writing to one of the registers TCNT2, OCR2x, or TCCR2x, the value is transferred to a

temporary register, and latched after two positive edges on TOSC1. The user should not write

a new value before the contents of the temporary register have been transferred to its

destination. Each of the five mentioned registers have their individual temporary register, which

means that e.g. writing to TCNT2 does not disturb an OCR2x write in progress. To detect that a

transfer to the destination register has taken place, the Asynchronous Status Register ASSR

has been implemented.

- When entering Power-save or ADC Noise Reduction mode after having written to TCNT2, OCR2x, or TCCR2x, the user must wait until the written register has been updated if Timer/Counter2 is used to wake up the device. Otherwise, the MCU will enter sleep mode before the changes are effective. This is particularly important if any of the Output Compare2 interrupt is used to wake up the device, since the Output Compare function is disabled during writing to OCR2x or TCNT2. If the write cycle is not finished, and the MCU enters sleep mode

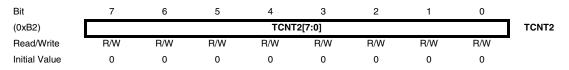

#### Bit 6 – FOC2B: Force Output Compare B

The FOC2B bit is only active when the WGM bits specify a non-PWM mode.

However, for ensuring compatibility with future devices, this bit must be set to zero when TCCR2B is written when operating in PWM mode. When writing a logical one to the FOC2B bit, an immediate Compare Match is forced on the Waveform Generation unit. The OC2B output is changed according to its COM2B1:0 bits setting. Note that the FOC2B bit is implemented as a strobe. Therefore it is the value present in the COM2B1:0 bits that determines the effect of the forced compare.

A FOC2B strobe will not generate any interrupt, nor will it clear the timer in CTC mode using OCR2B as TOP.

The FOC2B bit is always read as zero.

#### • Bits 5:4 - Res: Reserved Bits

These bits are reserved bits in the ATmega164P/324P/644P and will always read as zero.

#### Bit 3 – WGM22: Waveform Generation Mode

See the description in the "TCCR2A – Timer/Counter Control Register A" on page 152.

#### Bit 2:0 – CS22:0: Clock Select

The three Clock Select bits select the clock source to be used by the Timer/Counter, see Table 14-9 on page 156.

| CS22 | CS21 | CS20 | Description                               |  |  |

|------|------|------|-------------------------------------------|--|--|

| 0    | 0    | 0    | No clock source (Timer/Counter stopped).  |  |  |

| 0    | 0    | 1    | clk <sub>T2S</sub> /(No prescaling)       |  |  |

| 0    | 1    | 0    | clk <sub>T2S</sub> /8 (From prescaler)    |  |  |

| 0    | 1    | 1    | clk <sub>T2S</sub> /32 (From prescaler)   |  |  |

| 1    | 0    | 0    | 0 clk <sub>T2S</sub> /64 (From prescaler) |  |  |

| 1    | 0    | 1    | clk <sub>T2S</sub> /128 (From prescaler)  |  |  |

| 1    | 1    | 0    | clk <sub>T2S</sub> /256 (From prescaler)  |  |  |

| 1    | 1    | 1    | clk <sub>T2S</sub> /1024 (From prescaler) |  |  |

Table 14-9. Clock Select Bit Description

If external pin modes are used for the Timer/Counter0, transitions on the T0 pin will clock the counter even if the pin is configured as an output. This feature allows software control of the counting.

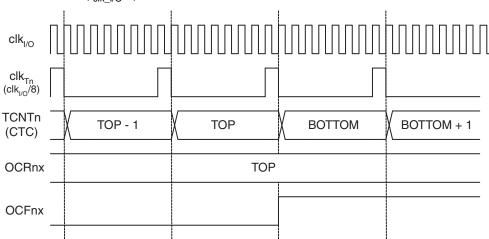

#### 14.11.3 TCNT2 – Timer/Counter Register

The Timer/Counter Register gives direct access, both for read and write operations, to the Timer/Counter unit 8-bit counter. Writing to the TCNT2 Register blocks (removes) the Compare

| Bit Number | Signal Name | Module |

|------------|-------------|--------|

| 39         | PD0.Data    |        |

| 38         | PD0.Control |        |

| 37         | PD1.Data    |        |

| 36         | PD1.Control |        |

| 35         | PD2.Data    |        |

| 34         | PD2.Control | Dert D |

| 33         | PD3.Data    | Port D |

| 32         | PD3.Control |        |

| 31         | PD4.Data    |        |

| 30         | PD4.Control |        |

| 29         | PD5.Data    |        |

| 28         | PD5.Control |        |

| 27         | PD6.Data    |        |

| 26         | PD6.Control |        |

| 25         | PD7.Data    |        |

| 24         | PD7.Control |        |

| 23         | PC0.Data    |        |

| 22         | PC0.Control |        |

| 21         | PC1.Data    |        |

| 20         | PC1.Control |        |

| 19         | PC6.Data    | Port C |

| 18         | PC6.Control |        |

| 17         | PC7.Data    |        |

| 16         | PC7.Control |        |

| 15         | PA7.Data    |        |

| Table 22-1. | ATmega164P/324P/644P           | Boundary-sca | an Order | (Continued)   |  |

|-------------|--------------------------------|--------------|----------|---------------|--|

|             | , thingaile in , e in , e i in | Doundary ood |          | (00111111000) |  |

# 24. Memory Programming

# 24.1 Program And Data Memory Lock Bits

The ATmega164P/324P/644P provides six Lock bits which can be left unprogrammed ("1") or can be programmed ("0") to obtain the additional features listed in Table 24-2. The Lock bits can only be erased to "1" with the Chip Erase command.

| Lock Bit Byte | Bit No | Description   | Default Value    |

|---------------|--------|---------------|------------------|

|               | 7      | -             | 1 (unprogrammed) |

|               | 6      | -             | 1 (unprogrammed) |

| BLB12         | 5      | Boot Lock bit | 1 (unprogrammed) |

| BLB11         | 4      | Boot Lock bit | 1 (unprogrammed) |

| BLB02         | 3      | Boot Lock bit | 1 (unprogrammed) |

| BLB01         | 2      | Boot Lock bit | 1 (unprogrammed) |

| LB2           | 1      | Lock bit      | 1 (unprogrammed) |

| LB1           | 0      | Lock bit      | 1 (unprogrammed) |

Note: 1. "1" means unprogrammed, "0" means programmed

| Memory Lock Bits |       |       | Protection Type                                                                                                                                                                                                                                                                                              |  |  |

|------------------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LB Mode          | LB2   | LB1   |                                                                                                                                                                                                                                                                                                              |  |  |

| 1                | 1     | 1     | No memory lock features enabled.                                                                                                                                                                                                                                                                             |  |  |

| 2                | 1     | 0     | Further programming of the Flash and EEPROM is disabled in Parallel and Serial Programming mode. The Fuse bits are locked in both Serial and Parallel Programming mode. <sup>(1)</sup>                                                                                                                       |  |  |

| 3                | 0     | 0     | Further programming and verification of the Flash and EEPROM is disabled in Parallel and Serial Programming mode. The Boot Lock bits and Fuse bits are locked in both Serial and Parallel Programming mode. <sup>(1)</sup>                                                                                   |  |  |

| BLB0 Mode        | BLB02 | BLB01 |                                                                                                                                                                                                                                                                                                              |  |  |

| 1                | 1     | 1     | No restrictions for SPM or (E)LPM accessing the Application section.                                                                                                                                                                                                                                         |  |  |

| 2                | 1     | 0     | SPM is not allowed to write to the Application section.                                                                                                                                                                                                                                                      |  |  |

| 3                | 0     | 0     | SPM is not allowed to write to the Application section, and<br>(E)LPM executing from the Boot Loader section is not allowed to<br>read from the Application section. If Interrupt Vectors are placed<br>in the Boot Loader section, interrupts are disabled while<br>executing from the Application section. |  |  |

| 4                | 0     | 1     | (E)LPM executing from the Boot Loader section is not allowed to<br>read from the Application section. If Interrupt Vectors are placed<br>in the Boot Loader section, interrupts are disabled while<br>executing from the Application section.                                                                |  |  |

# ATmega164P/324P/644P

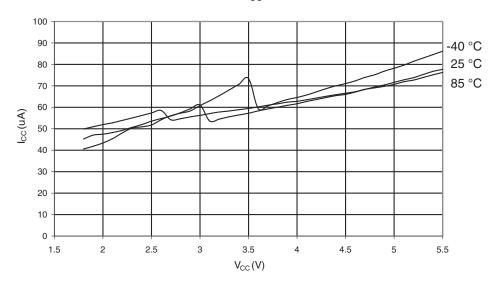

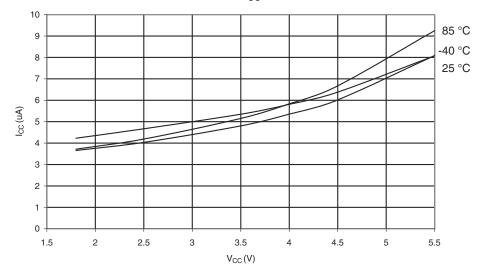

#### 26.2.12 Current Consumption of Peripheral Units

Figure 26-86. ADC Current vs.  $V_{CC}$  (AREF = AV<sub>CC</sub>)

Figure 26-87. Analog Comparator Current vs.  $V_{CC}$

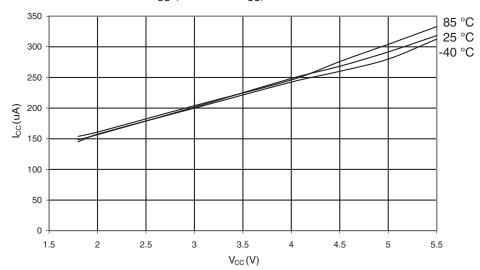

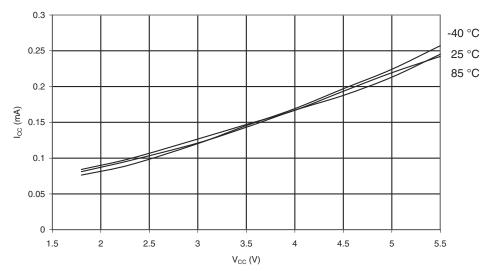

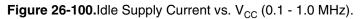

#### 26.3.2 Idle Supply Current

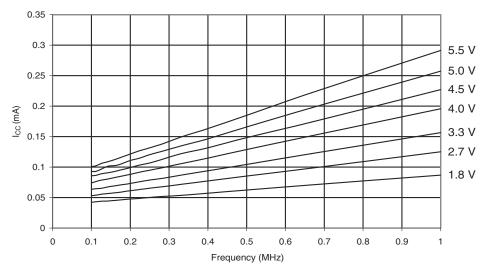

### 26.3.4 Power-down Supply Current

Figure 26-105. Power-down Supply Current vs.  $V_{CC}$  (Watchdog Timer Disabled).

Figure 26-106. Power-down Supply Current vs.  $V_{CC}$  (Watchdog Timer Enabled).

Figure 26-135.AREF External Reference Current vs. V<sub>CC</sub>

Figure 26-136. Brownout Detector Current vs.  $\mathrm{V}_{\mathrm{CC}}$

| E |  |  |  |  |

|---|--|--|--|--|

|   |  |  |  |  |

|   |  |  |  |  |

|   |  |  |  |  |

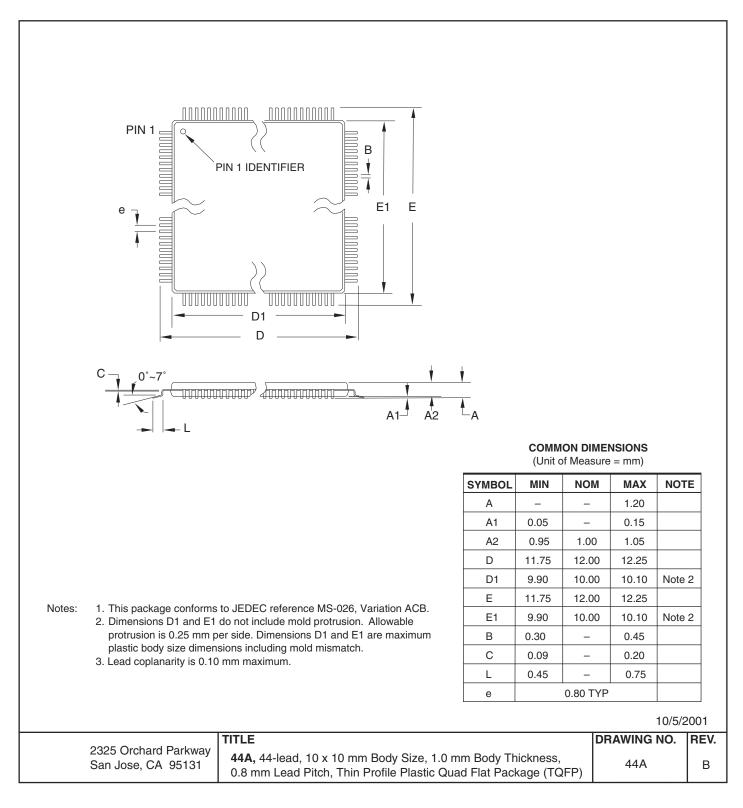

# 30. Packaging Information

# 30.1 44A

# ATmega164P/324P/644P

|   | 6.5 Low Frequency Crystal Oscillator          | 34 |

|---|-----------------------------------------------|----|

|   | 6.6 Calibrated Internal RC Oscillator         | 36 |

|   | 6.7 128 kHz Internal Oscillator               | 37 |

|   | 6.8 External Clock                            | 37 |

|   | 6.9 Timer/Counter Oscillator                  | 38 |

|   | 6.10 Clock Output Buffer                      |    |

|   | 6.11 System Clock Prescaler                   | 38 |

|   | 6.12 Register Description                     | 40 |

| 7 | Power Management and Sleep Modes              | 42 |

|   | 7.1 Overview                                  | 42 |

|   | 7.2 Sleep Modes                               | 42 |

|   | 7.3 BOD Disable                               | 43 |

|   | 7.4 Idle Mode                                 | 43 |

|   | 7.5 ADC Noise Reduction Mode                  | 43 |

|   | 7.6 Power-down Mode                           | 44 |

|   | 7.7 Power-save Mode                           | 44 |

|   | 7.8 Standby Mode                              | 44 |

|   | 7.9 Extended Standby Mode                     | 44 |

|   | 7.10 Power Reduction Register                 | 45 |

|   | 7.11 Minimizing Power Consumption             | 45 |

|   | 7.12 Register Description                     | 47 |

| 8 | System Control and Reset                      | 50 |

|   | 8.1 Resetting the AVR                         | 50 |

|   | 8.2 Reset Sources                             | 50 |

|   | 8.3 Power-on Reset                            | 51 |

|   | 8.4 External Reset                            | 52 |

|   | 8.5 Brown-out Detection                       | 53 |

|   | 8.6 Watchdog Reset                            | 53 |

|   | 8.7 Internal Voltage Reference                | 54 |

|   | 8.8 Watchdog Timer                            | 55 |

|   | 8.9 Register Description                      | 58 |

| 9 | Interrupts                                    | 61 |

|   | 9.1 Overview                                  | 61 |

|   | 9.2 Interrupt Vectors in ATmega164P/324P/644P | 61 |

|   | 9.3 Register Description                      | 65 |