Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega324p-20aqr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4. AVR CPU Core

## 4.1 Overview

This section discusses the AVR core architecture in general. The main function of the CPU core is to ensure correct program execution. The CPU must therefore be able to access memories, perform calculations, control peripherals, and handle interrupts.

In order to maximize performance and parallelism, the AVR uses a Harvard architecture – with separate memories and buses for program and data. Instructions in the program memory are executed with a single level pipelining. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This concept enables instructions to be executed in every clock cycle. The program memory is In-System Reprogrammable Flash memory.

The fast-access Register File contains 32 x 8-bit general purpose working registers with a single clock cycle access time. This allows single-cycle Arithmetic Logic Unit (ALU) operation. In a typ-

| Vector<br>No. | Program<br>Address <sup>(2)</sup> | Source      | Interrupt Definition       |

|---------------|-----------------------------------|-------------|----------------------------|

| 28            | \$0036                            | SPM_READY   | Store Program Memory Ready |

| 29            | \$0038                            | USART1_RX   | USART1 Rx Complete         |

| 30            | \$003A                            | USART1_UDRE | USART1 Data Register Empty |

| 31            | \$003C                            | USART1_TX   | USART1 Tx Complete         |

Table 9-1.

Reset and Interrupt Vectors (Continued)

Notes: 1. When the BOOTRST Fuse is programmed, the device will jump to the Boot Loader address at reset, see "Memory Programming" on page 293.

2. When the IVSEL bit in MCUCR is set, Interrupt Vectors will be moved to the start of the Boot Flash Section. The address of each Interrupt Vector will then be the address in this table added to the start address of the Boot Flash Section.

Table 9-2 shows reset and Interrupt Vectors placement for the various combinations of BOOTRST and IVSEL settings. If the program never enables an interrupt source, the Interrupt Vectors are not used, and regular program code can be placed at these locations. This is also the case if the Reset Vector is in the Application section while the Interrupt Vectors are in the Boot section or vice versa.

| BOOTRST | IVSEL | Reset Address      | Interrupt Vectors Start Address |

|---------|-------|--------------------|---------------------------------|

| 1       | 0     | 0x0000             | 0x0002                          |

| 1       | 1     | 0x0000             | Boot Reset Address + 0x0002     |

| 0       | 0     | Boot Reset Address | 0x0002                          |

| 0       | 1     | Boot Reset Address | Boot Reset Address + 0x0002     |

Table 9-2.

Reset and Interrupt Vectors Placement<sup>(1)</sup>

Note: 1. The Boot Reset Address is shown in Table 23-7 on page 288. For the BOOTRST Fuse "1" means unprogrammed while "0" means programmed.

The most typical and general program setup for the Reset and Interrupt Vector Addresses in ATmega164P/324P/644P is:

| Address | Labels | Code |            | Сс | omments          |

|---------|--------|------|------------|----|------------------|

| 0x0000  |        | jmp  | RESET      | ;  | Reset            |

| 0x0002  |        | jmp  | INT0       | ;  | IRQ0             |

| 0x0004  |        | jmp  | INT1       | ;  | IRQ1             |

| 0x0006  |        | jmp  | INT2       | ;  | IRQ2             |

| 0x0008  |        | jmp  | PCINT0     | ;  | PCINT0           |

| 0x000A  |        | jmp  | PCINT1     | ;  | PCINT1           |

| 0x000C  |        | jmp  | PCINT2     | ;  | PCINT2           |

| 0x000E  |        | jmp  | PCINT3     | ;  | PCINT3           |

| 0x0010  |        | jmp  | WDT        | ;  | Watchdog Timeout |

| 0x0012  |        | jmp  | TIM2_COMPA | ;  | Timer2 CompareA  |

| 0x0014  |        | jmp  | TIM2_COMPB | ;  | Timer2 CompareB  |

| 0x0016  |        | jmp  | TIM2_OVF   | ;  | Timer2 Overflow  |

| 0x0018  |        | jmp  | TIM1_CAPT  | ;  | Timer1 Capture   |

| 0x001A  |        | jmp  | TIM1_COMPA | ;  | Timer1 CompareA  |

| 0x001C  |        | jmp  | TIM1_COMPB | ;  | Timer1 CompareB  |

| 0x001E  |        | jmp  | TIM1_OVF   | ;  | Timer1 Overflow  |

| 0x0020  |        | jmp  | TIM0_COMPA | ;  | Timer0 CompareA  |

|         |        |      |            |    |                  |

#### Bit 2 – OCF0B: Timer/Counter 0 Output Compare B Match Flag

The OCF0B bit is set when a Compare Match occurs between the Timer/Counter and the data in OCR0B – Output Compare Register0 B. OCF0B is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF0B is cleared by writing a logic one to the flag. When the I-bit in SREG, OCIE0B (Timer/Counter Compare B Match Interrupt Enable), and OCF0B are set, the Timer/Counter Compare Match Interrupt is executed.

#### Bit 1 – OCF0A: Timer/Counter 0 Output Compare A Match Flag

The OCF0A bit is set when a Compare Match occurs between the Timer/Counter0 and the data in OCR0A – Output Compare Register0. OCF0A is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF0A is cleared by writing a logic one to the flag. When the I-bit in SREG, OCIE0A (Timer/Counter0 Compare Match Interrupt Enable), and OCF0A are set, the Timer/Counter0 Compare Match Interrupt is executed.

#### Bit 0 – TOV0: Timer/Counter0 Overflow Flag

The bit TOV0 is set when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV0 is cleared by writing a logic one to the flag. When the SREG I-bit, TOIE0 (Timer/Counter0 Overflow Interrupt Enable), and TOV0 are set, the Timer/Counter0 Overflow interrupt is executed.

The setting of this flag is dependent of the WGM02:0 bit setting. Refer to Table 12-8, "Waveform Generation Mode Bit Description" on page 106.

```

Assembly Code Examples<sup>(1)</sup>

...

; Set TCNTN to 0x01FF

Idi r17,0x01

Idi r16,0xFF

out TCNTNH,r17

out TCNTNL,r16

; Read TCNTN into r17:r16

in r16,TCNTNL

in r17,TCNTNH

...

C Code Examples<sup>(1)</sup>

unsigned int i;

```

```

...

/* Set TCNTn to 0x01FF */

TCNTn = 0x1FF;

/* Read TCNTn into i */

i = TCNTn;

....

```

Note: 1. The example code assumes that the part specific header file is included. For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

The assembly code example returns the TCNTn value in the r17:r16 register pair.

It is important to notice that accessing 16-bit registers are atomic operations. If an interrupt occurs between the two instructions accessing the 16-bit register, and the interrupt code updates the temporary register by accessing the same or any other of the 16-bit Timer Registers, then the result of the access outside the interrupt will be corrupted. Therefore, when both the main code and the interrupt code update the temporary register, the main code must disable the interrupts during the 16-bit access.

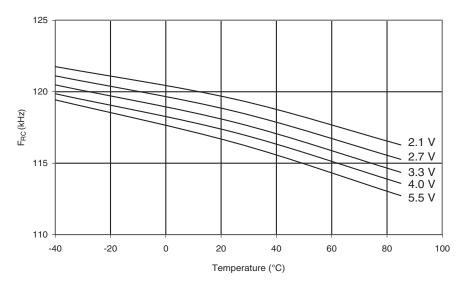

## 13.5 Counter Unit

The main part of the 16-bit Timer/Counter is the programmable 16-bit bi-directional counter unit. Figure 13-2 shows a block diagram of the counter and its surroundings.

Figure 13-2. Counter Unit Block Diagram

Signal description (internal signals):

| Count             | Increment or decrement TCNTn by 1.                     |

|-------------------|--------------------------------------------------------|

| Direction         | Select between increment and decrement.                |

| Clear             | Clear TCNTn (set all bits to zero).                    |

| clk <sub>Tn</sub> | Timer/Counter clock.                                   |

| ТОР               | Signalize that TCNTn has reached maximum value.        |

| воттом            | Signalize that TCNTn has reached minimum value (zero). |

The 16-bit counter is mapped into two 8-bit I/O memory locations: *Counter High* (TCNTnH) containing the upper eight bits of the counter, and *Counter Low* (TCNTnL) containing the lower eight bits. The TCNTnH Register can only be indirectly accessed by the CPU. When the CPU does an access to the TCNTnH I/O location, the CPU accesses the high byte temporary register (TEMP). The temporary register is updated with the TCNTnH value when the TCNTnL is read, and TCNTnH is updated with the temporary register value when TCNTnL is written. This allows the CPU to read or write the entire 16-bit counter value within one clock cycle via the 8-bit data bus. It is important to notice that there are special cases of writing to the TCNTn Register when the counter is counting that will give unpredictable results. The special cases are described in the sections where they are of importance.

Depending on the mode of operation used, the counter is cleared, incremented, or decremented at each *timer clock* ( $clk_{Tn}$ ). The  $clk_{Tn}$  can be generated from an external or internal clock source, selected by the *Clock Select* bits (CSn2:0). When no clock source is selected (CSn2:0 = 0) the timer is stopped. However, the TCNTn value can be accessed by the CPU, independent of whether  $clk_{Tn}$  is present or not. A CPU write overrides (has priority over) all counter clear or count operations.

The counting sequence is determined by the setting of the *Waveform Generation mode* bits (WGMn3:0) located in the *Timer/Counter Control Registers* A and B (TCCRnA and TCCRnB). There are close connections between how the counter behaves (counts) and how waveforms are generated on the Output Compare outputs OCnx. For more details about advanced counting sequences and waveform generation, see "Modes of Operation" on page 123.

## 13.8 Compare Match Output Unit

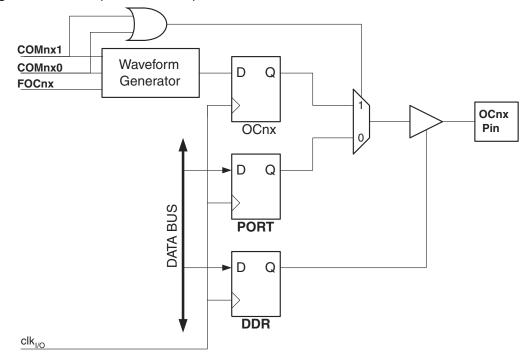

The *Compare Output mode* (COMnx1:0) bits have two functions. The Waveform Generator uses the COMnx1:0 bits for defining the Output Compare (OCnx) state at the next compare match. Secondly the COMnx1:0 bits control the OCnx pin output source. Figure 13-5 shows a simplified schematic of the logic affected by the COMnx1:0 bit setting. The I/O Registers, I/O bits, and I/O pins in the figure are shown in bold. Only the parts of the general I/O Port Control Registers (DDR and PORT) that are affected by the COMnx1:0 bits are shown. When referring to the OCnx state, the reference is for the internal OCnx Register, not the OCnx pin. If a system reset occur, the OCnx Register is reset to "0".

Figure 13-5. Compare Match Output Unit, Schematic

The general I/O port function is overridden by the Output Compare (OCnx) from the Waveform Generator if either of the COMnx1:0 bits are set. However, the OCnx pin direction (input or output) is still controlled by the *Data Direction Register* (DDR) for the port pin. The Data Direction Register bit for the OCnx pin (DDR\_OCnx) must be set as output before the OCnx value is visible on the pin. The port override function is generally independent of the Waveform Generation mode, but there are some exceptions. Refer to Table 13-2, Table 13-3 and Table 13-4 for details.

The design of the Output Compare pin logic allows initialization of the OCnx state before the output is enabled. Note that some COMnx1:0 bit settings are reserved for certain modes of operation. See Section "13.11" on page 132.

The COMnx1:0 bits have no effect on the Input Capture unit.

for power regulation, rectification, and DAC applications. High frequency allows physically small sized external components (coils, capacitors), and therefore reduces total system cost.

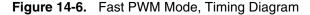

In fast PWM mode, the counter is incremented until the counter value matches the TOP value. The counter is then cleared at the following timer clock cycle. The timing diagram for the fast PWM mode is shown in Figure 14-6 on page 146. The TCNT2 value is in the timing diagram shown as a histogram for illustrating the single-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT2 slopes represent compare matches between OCR2x and TCNT2.

The Timer/Counter Overflow Flag (TOV2) is set each time the counter reaches TOP. If the interrupt is enabled, the interrupt handler routine can be used for updating the compare value.

In fast PWM mode, the compare unit allows generation of PWM waveforms on the OC2x pin. Setting the COM2x1:0 bits to two will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COM2x1:0 to three. TOP is defined as 0xFF when WGM2:0 = 3, and OCR2A when WGM2:0 = 7 (See Table 14-3 on page 153). The actual OC2x value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by setting (or clearing) the OC2x Register at the compare match between OCR2x and TCNT2, and clearing (or setting) the OC2x Register at the timer clock cycle the counter is cleared (changes from TOP to BOTTOM).

The PWM frequency for the output can be calculated by the following equation:

$$f_{OCnxPWM} = \frac{f_{\mathsf{Clk\_I/O}}}{N \cdot 256}$$

The *N* variable represents the prescale factor (1, 8, 32, 64, 128, 256, or 1024).

The extreme values for the OCR2A Register represent special cases when generating a PWM waveform output in the fast PWM mode. If the OCR2A is set equal to BOTTOM, the output will be a narrow spike for each MAX+1 timer clock cycle. Setting the OCR2A equal to MAX will result in a constantly high or low output (depending on the polarity of the output set by the COM2A1:0 bits.)

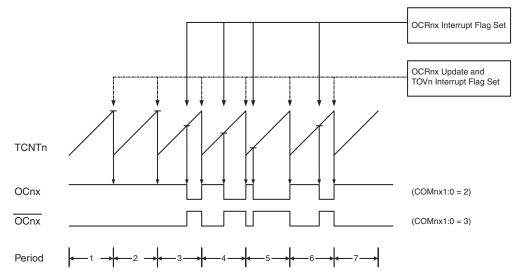

UCSRnA Register. When using synchronous mode (UMSELn = 1), the Data Direction Register for the XCKn pin (DDR\_XCKn) controls whether the clock source is internal (Master mode) or external (Slave mode). The XCKn pin is only active when using synchronous mode.

Figure 16-2 shows a block diagram of the clock generation logic.

Figure 16-2. Clock Generation Logic, Block Diagram

Signal description:

| txclk                     | Transmitter clock (Internal Signal).                                              |

|---------------------------|-----------------------------------------------------------------------------------|

| rxclk                     | Receiver base clock (Internal Signal).                                            |

| <b>xcki</b><br>operation. | Input from XCK pin (internal Signal). Used for synchronous slave                  |

| xcko                      | Clock output to XCK pin (Internal Signal). Used for synchronous master operation. |

| f <sub>osc</sub>          | XTAL pin frequency (System Clock).                                                |

#### 16.4.1 Internal Clock Generation – The Baud Rate Generator

Internal clock generation is used for the asynchronous and the synchronous master modes of operation. The description in this section refers to Figure 16-2 on page 173.

The USART Baud Rate Register (UBRRn) and the down-counter connected to it function as a programmable prescaler or baud rate generator. The down-counter, running at system clock ( $f_{osc}$ ), is loaded with the UBRRn value each time the counter has counted down to zero or when the UBRRLn Register is written. A clock is generated each time the counter reaches zero. This clock is the baud rate generator clock output (=  $f_{osc}/(UBRRn+1)$ ). The Transmitter divides the baud rate generator clock output by 2, 8 or 16 depending on mode. The baud rate generator output is used directly by the Receiver's clock and data recovery units. However, the recovery units use a state machine that uses 2, 8 or 16 states depending on mode set by the state of the UMSELn, U2Xn and DDR\_XCKn bits.

Table 16-1 on page 174 contains equations for calculating the baud rate (in bits per second) and for calculating the UBRRn value for each mode of operation using an internally generated clock source.

Note: 1. The baud rate is defined to be the transfer rate in bit per second (bps)

**BAUD** Baud rate (in bits per second, bps)

```

Assembly Code Example<sup>(1)(2)</sup>

```

```

USART_Transmit:

```

; Wait for empty transmit buffer **sbis** UCSRnA,UDREn

```

rjmp USART_Transmit

; Copy 9th bit from r17 to TXB8

```

```

cbi UCSRnB, TXB8

```

sbrc r17,0

sbi UCSRnB,TXB8

; Put LSB data (r16) into buffer, sends the data

```

out UDRn,r16

```

C Code Example<sup>(1)(2)</sup>

```

void USART_Transmit( unsigned int data )

{

/* Wait for empty transmit buffer */

while ( !( UCSRnA & (1<<UDREn))) )

;

/* Copy 9th bit to TXB8 */

UCSRnB &= ~(1<<TXB8);

if ( data & 0x0100 )

UCSRnB |= (1<<TXB8);

/* Put data into buffer, sends the data */

UDRn = data;

}</pre>

```

- Notes: 1. These transmit functions are written to be general functions. They can be optimized if the contents of the UCSRnB is static. For example, only the TXB8 bit of the UCSRnB Register is used after initialization.

- 2. See "About Code Examples" on page 8.

The ninth bit can be used for indicating an address frame when using multi processor communication mode or for other protocol handling as for example synchronization.

## 16.7.3 Transmitter Flags and Interrupts

The USART Transmitter has two flags that indicate its state: USART Data Register Empty (UDREn) and Transmit Complete (TXCn). Both flags can be used for generating interrupts.

The Data Register Empty (UDREn) Flag indicates whether the transmit buffer is ready to receive new data. This bit is set when the transmit buffer is empty, and cleared when the transmit buffer contains data to be transmitted that has not yet been moved into the Shift Register. For compatibility with future devices, always write this bit to zero when writing the UCSRnA Register.

When the Data Register Empty Interrupt Enable (UDRIEn) bit in UCSRnB is written to one, the USART Data Register Empty Interrupt will be executed as long as UDREn is set (provided that global interrupts are enabled). UDREn is cleared by writing UDRn. When interrupt-driven data

Data Register Empty interrupt (see description of the UDRIEn bit).UDREn is set after a reset to indicate that the Transmitter is ready.

#### • Bit 4 – FEn: Frame Error

This bit is set if the next character in the receive buffer had a Frame Error when received. I.e., when the first stop bit of the next character in the receive buffer is zero. This bit is valid until the receive buffer (UDRn) is read. The FEn bit is zero when the stop bit of received data is one. Always set this bit to zero when writing to UCSRnA.

#### Bit 3 – DORn: Data OverRun

This bit is set if a Data OverRun condition is detected. A Data OverRun occurs when the receive buffer is full (two characters), it is a new character waiting in the Receive Shift Register, and a new start bit is detected. This bit is valid until the receive buffer (UDRn) is read. Always set this bit to zero when writing to UCSRnA.

#### • Bit 2 – UPEn: USART Parity Error

This bit is set if the next character in the receive buffer had a Parity Error when received and the Parity Checking was enabled at that point (UPMn1 = 1). This bit is valid until the receive buffer (UDRn) is read. Always set this bit to zero when writing to UCSRnA.

#### • Bit 1 – U2Xn: Double the USART Transmission Speed

This bit only has effect for the asynchronous operation. Write this bit to zero when using synchronous operation.

Writing this bit to one will reduce the divisor of the baud rate divider from 16 to 8 effectively doubling the transfer rate for asynchronous communication.

#### • Bit 0 – MPCMn: Multi-processor Communication Mode

This bit enables the Multi-processor Communication mode. When the MPCMn bit is written to one, all the incoming frames received by the USART Receiver that do not contain address information will be ignored. The Transmitter is unaffected by the MPCMn setting. For more detailed information see "Multi-processor Communication Mode" on page 187.

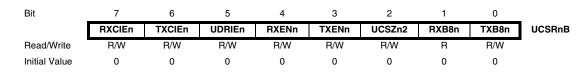

#### 16.11.3 UCSRnB – USART Control and Status Register n B

#### Bit 7 – RXCIEn: RX Complete Interrupt Enable n

Writing this bit to one enables interrupt on the RXCn Flag. A USART Receive Complete interrupt will be generated only if the RXCIEn bit is written to one, the Global Interrupt Flag in SREG is written to one and the RXCn bit in UCSRnA is set.

#### Bit 6 – TXCIEn: TX Complete Interrupt Enable n

Writing this bit to one enables interrupt on the TXCn Flag. A USART Transmit Complete interrupt will be generated only if the TXCIEn bit is written to one, the Global Interrupt Flag in SREG is written to one and the TXCn bit in UCSRnA is set.

This scheme is repeated until the last byte has been sent and the transfer is ended by generating a STOP condition or a repeated START condition. A STOP condition is generated by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | _ | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| value | 1     | Х    | 0     | 1     | Х    | 1    | 0 | Х    |

A REPEATED START condition is generated by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| value | 1     | Х    | 1     | 0     | Х    | 1    | 0 | Х    |

After a repeated START condition (state 0x10) the 2-wire Serial Interface can access the same Slave again, or a new Slave without transmitting a STOP condition. Repeated START enables the Master to switch between Slaves, Master Transmitter mode and Master Receiver mode without losing control of the bus.

Table 18-2. Status codes for Master Transmitter Mode

| Status Code              |                                                                      | Applica           | tion Softv | are Resp | onse  |      |                                                                                                  |

|--------------------------|----------------------------------------------------------------------|-------------------|------------|----------|-------|------|--------------------------------------------------------------------------------------------------|

| (TWSR)<br>Prescaler Bits | Status of the 2-wire Serial Bus<br>and 2-wire Serial Interface Hard- | To/from TWDR      |            | To       | TWCR  |      |                                                                                                  |

| are 0                    | ware                                                                 |                   | STA        | STO      | TWINT | TWEA | Next Action Taken by TWI Hardware                                                                |

| 0x08                     | A START condition has been transmitted                               | Load SLA+W        | 0          | 0        | 1     | х    | SLA+W will be transmitted;<br>ACK or NOT ACK will be received                                    |

| 0x10                     | A repeated START condition has been transmitted                      | Load SLA+W or     | 0          | 0        | 1     | х    | SLA+W will be transmitted;<br>ACK or NOT ACK will be received                                    |

|                          |                                                                      | Load SLA+R        | 0          | 0        | 1     | Х    | SLA+R will be transmitted;<br>Logic will switch to Master Receiver mode                          |

| 0x18                     | SLA+W has been transmitted;<br>ACK has been received                 | Load data byte or | 0          | 0        | 1     | х    | Data byte will be transmitted and ACK or NOT ACK will be received                                |

|                          |                                                                      | No TWDR action or | 1          | 0        | 1     | Х    | Repeated START will be transmitted                                                               |

|                          |                                                                      | No TWDR action or | 0          | 1        | 1     | х    | STOP condition will be transmitted and TWSTO Flag will be reset                                  |

|                          |                                                                      | No TWDR action    | 1          | 1        | 1     | х    | STOP condition followed by a START condition will be transmitted and TWSTO Flag will be reset    |

| 0x20                     | SLA+W has been transmitted;<br>NOT ACK has been received             | Load data byte or | 0          | 0        | 1     | х    | Data byte will be transmitted and ACK or NOT ACK will be received                                |

|                          |                                                                      | No TWDR action or | 1          | 0        | 1     | Х    | Repeated START will be transmitted                                                               |

|                          |                                                                      | No TWDR action or | 0          | 1        | 1     | Х    | STOP condition will be transmitted and TWSTO Flag will be reset                                  |

|                          |                                                                      | No TWDR action    | 1          | 1        | 1     | х    | STOP condition followed by a START condition will be transmitted and TWSTO Flag will be reset    |

| 0x28                     | Data byte has been transmitted;<br>ACK has been received             | Load data byte or | 0          | 0        | 1     | х    | Data byte will be transmitted and ACK or NOT ACK will be received                                |

|                          |                                                                      | No TWDR action or | 1          | 0        | 1     | Х    | Repeated START will be transmitted                                                               |

|                          |                                                                      | No TWDR action or | 0          | 1        | 1     | Х    | STOP condition will be transmitted and TWSTO Flag will be reset                                  |

|                          |                                                                      | No TWDR action    | 1          | 1        | 1     | Х    | STOP condition followed by a START condition will be transmitted and TWSTO Flag will be reset    |

| 0x30                     | Data byte has been transmitted;<br>NOT ACK has been received         | Load data byte or | 0          | 0        | 1     | х    | Data byte will be transmitted and ACK or NOT ACK will be received                                |

|                          |                                                                      | No TWDR action or | 1          | 0        | 1     | Х    | Repeated START will be transmitted                                                               |

|                          |                                                                      | No TWDR action or | 0          | 1        | 1     | X    | STOP condition will be transmitted and TWSTO Flag will be reset                                  |

|                          |                                                                      | No TWDR action    | 1          | 1        | 1     | х    | STOP condition followed by a START condition will be<br>transmitted and TWSTO Flag will be reset |

| 0x38                     | Arbitration lost in SLA+W or data bytes                              | No TWDR action or | 0          | 0        | 1     | х    | 2-wire Serial Bus will be released and not addressed Slave mode entered                          |

|                          |                                                                      | No TWDR action    | 1          | 0        | 1     | Х    | A START condition will be transmitted when the bus be-<br>comes free                             |

|       |       | · · · |                 |

|-------|-------|-------|-----------------|

| ADPS2 | ADPS1 | ADPS0 | Division Factor |

| 1     | 0     | 0     | 16              |

| 1     | 0     | 1     | 32              |

| 1     | 1     | 0     | 64              |

| 1     | 1     | 1     | 128             |

Table 20-5.

ADC Prescaler Selections (Continued)

#### 20.9.3 ADCL and ADCH – The ADC Data Register

ADLAR = 0

| Bit           | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |      |

|---------------|------|------|------|------|------|------|------|------|------|

| (0x79)        | -    | -    | -    | -    | -    | -    | ADC9 | ADC8 | ADCH |

| (0x78)        | ADC7 | ADC6 | ADC5 | ADC4 | ADC3 | ADC2 | ADC1 | ADC0 | ADCL |

|               | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |      |

| Read/Write    | R    | R    | R    | R    | R    | R    | R    | R    |      |

|               | R    | R    | R    | R    | R    | R    | R    | R    |      |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

|               | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

|               |      |      |      |      |      |      |      |      |      |

|               |      |      |      |      |      |      | _    | _    |      |

| Bit           | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |      |

ADLAR = 1

| Bit           | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |

|---------------|------|------|------|------|------|------|------|------|

| (0x79)        | ADC9 | ADC8 | ADC7 | ADC6 | ADC5 | ADC4 | ADC3 | ADC2 |

| (0x78)        | ADC1 | ADC0 | -    | -    | -    | -    | -    | -    |

|               | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| Read/Write    | R    | R    | R    | R    | R    | R    | R    | R    |

|               | R    | R    | R    | R    | R    | R    | R    | R    |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

|               | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

When an ADC conversion is complete, the result is found in these two registers. If differential channels are used, the result is presented in two's complement form.

When ADCL is read, the ADC Data Register is not updated until ADCH is read. Consequently, if the result is left adjusted and no more than 8-bit precision is required, it is sufficient to read ADCH. Otherwise, ADCL must be read first, then ADCH.

The ADLAR bit in ADMUX, and the MUXn bits in ADMUX affect the way the result is read from the registers. If ADLAR is set, the result is left adjusted. If ADLAR is cleared (default), the result is right adjusted.

#### • ADC9:0: ADC Conversion Result

These bits represent the result from the conversion, as detailed in "ADC Conversion Result" on page 253.

#### 20.9.4 ADCSRB – ADC Control and Status Register B

| Bit Number | Signal Name | Module |

|------------|-------------|--------|

| 39         | PD0.Data    |        |

| 38         | PD0.Control |        |

| 37         | PD1.Data    |        |

| 36         | PD1.Control |        |

| 35         | PD2.Data    |        |

| 34         | PD2.Control |        |

| 33         | PD3.Data    | Port D |

| 32         | PD3.Control |        |

| 31         | PD4.Data    |        |

| 30         | PD4.Control |        |

| 29         | PD5.Data    |        |

| 28         | PD5.Control |        |

| 27         | PD6.Data    |        |

| 26         | PD6.Control |        |

| 25         | PD7.Data    |        |

| 24         | PD7.Control |        |

| 23         | PC0.Data    |        |

| 22         | PC0.Control |        |

| 21         | PC1.Data    |        |

| 20         | PC1.Control |        |

| 19         | PC6.Data    | Port C |

| 18         | PC6.Control |        |

| 17         | PC7.Data    |        |

| 16         | PC7.Control |        |

| 15         | PA7.Data    |        |

| Table 22-1. | ATmega164P/324P/644P           | Boundary-sca | an Order | (Continued)  |  |

|-------------|--------------------------------|--------------|----------|--------------|--|

|             | , thingaile in , e in , e i in | Doundary ood |          | (0011111000) |  |

# 23. Boot Loader Support – Read-While-Write Self-Programming

## 23.1 Features

- Read-While-Write Self-Programming

- Flexible Boot Memory Size

- High Security (Separate Boot Lock Bits for a Flexible Protection)

- Separate Fuse to Select Reset Vector

- Optimized Page<sup>(1)</sup> Size

- Code Efficient Algorithm

- Efficient Read-Modify-Write Support

- Note: 1. A page is a section in the Flash consisting of several bytes (see Table 24-7 on page 296) used during programming. The page organization does not affect normal operation.

## 23.2 Overview

The Boot Loader Support provides a real Read-While-Write Self-Programming mechanism for downloading and uploading program code by the MCU itself. This feature allows flexible application software updates controlled by the MCU using a Flash-resident Boot Loader program. The Boot Loader program can use any available data interface and associated protocol to read code and write (program) that code into the Flash memory, or read the code from the program memory. The program code within the Boot Loader section has the capability to write into the entire Flash, including the Boot Loader memory. The Boot Loader can thus even modify itself, and it can also erase itself from the code if the feature is not needed anymore. The size of the Boot Loader memory is configurable with fuses and the Boot Loader has two separate sets of Boot Lock bits which can be set independently. This gives the user a unique flexibility to select different levels of protection.

## 23.3 Application and Boot Loader Flash Sections

The Flash memory is organized in two main sections, the Application section and the Boot Loader section (see Figure 23-2 on page 279). The size of the different sections is configured by the BOOTSZ Fuses as shown in Table 23-7 on page 288 and Figure 23-2. These two sections can have different level of protection since they have different sets of Lock bits.

#### 23.3.1 Application Section

The Application section is the section of the Flash that is used for storing the application code. The protection level for the Application section can be selected by the application Boot Lock bits (Boot Lock bits 0), see Table 23-2 on page 280. The Application section can never store any Boot Loader code since the SPM instruction is disabled when executed from the Application section.

#### 23.3.2 BLS – Boot Loader Section

While the Application section is used for storing the application code, the The Boot Loader software must be located in the BLS since the SPM instruction can initiate a programming when executing from the BLS only. The SPM instruction can access the entire Flash, including the BLS itself. The protection level for the Boot Loader section can be selected by the Boot Loader Lock bits (Boot Lock bits 1), see Table 23-3 on page 280.

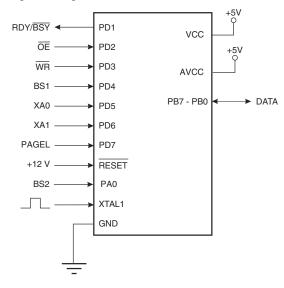

## 24.6 Parallel Programming Parameters, Pin Mapping, and Commands

This section describes how to parallel program and verify Flash Program memory, EEPROM Data memory, Memory Lock bits, and Fuse bits in the ATmega164P/324P/644P. Pulses are assumed to be at least 250 ns unless otherwise noted.

#### 24.6.1 Signal Names

In this section, some pins of the ATmega164P/324P/644P are referenced by signal names describing their functionality during parallel programming, see Figure 24-1 on page 297 and Figure 24-9 on page 297. Pins not described in the following table are referenced by pin names.

The XA1/XA0 pins determine the action executed when the XTAL1 pin is given a positive pulse. The bit coding is shown in Table 24-12 on page 298.

When pulsing  $\overline{WR}$  or  $\overline{OE}$ , the command loaded determines the action executed. The different commands are shown in Table 24-13 on page 298.

#### Figure 24-1. Parallel Programming<sup>(1)</sup>

Note: 1. Unused Pins should be left floating.

| Signal Name in<br>Programming Mode | Pin Name | I/O | Function                                                           |

|------------------------------------|----------|-----|--------------------------------------------------------------------|

| RDY/BSY                            | PD1      | ο   | 0: Device is busy programming, 1: Device is ready for new command. |

| ŌĒ                                 | PD2      | I   | Output Enable (Active low).                                        |

| WR                                 | PD3      | Ι   | Write Pulse (Active low).                                          |

| BS1                                | PD4      | I   | Byte Select 1.                                                     |

| XA0                                | PD5      | Ι   | XTAL Action Bit 0                                                  |

| XA1                                | PD6      | Ι   | XTAL Action Bit 1                                                  |

## 25.8 ADC Characteristics

| Table 25-11. | ADC Characteristics, Single Ended Channel |

|--------------|-------------------------------------------|

|              | ABC Characteristics, Single Ended Charner |

| Symbol            | Parameter                                                                               | Condition                                                                                              | Min <sup>(1)</sup>    | <b>Typ</b> <sup>(1)</sup> | Max <sup>(1)</sup>    | Units |  |

|-------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------|---------------------------|-----------------------|-------|--|

|                   | Resolution                                                                              | Single Ended Conversion                                                                                |                       | 10                        |                       | Bits  |  |

|                   | Absolute accuracy (Including<br>INL, DNL, quantization error,<br>gain and offset error) | Single Ended Conversion<br>$V_{REF} = 4V, V_{CC} = 4V,$<br>ADC clock = 200 kHz                         |                       | 3                         |                       |       |  |

|                   |                                                                                         | Single Ended Conversion<br>$V_{REF} = 4V, V_{CC} = 4V,$<br>ADC clock = 1 MHz                           |                       | 3.5                       |                       |       |  |

|                   |                                                                                         | Single Ended Conversion<br>$V_{REF} = 4V, V_{CC} = 4V,$<br>ADC clock = 200 kHz<br>Noise Reduction Mode |                       | 2.75                      |                       |       |  |

|                   |                                                                                         | Single Ended Conversion<br>$V_{REF} = 4V, V_{CC} = 4V,$<br>ADC clock = 1 MHz<br>Noise Reduction Mode   |                       | 3.5                       |                       | LSB   |  |

|                   | Integral Non-Linearity (INL)                                                            | Single Ended Conversion<br>$V_{REF} = 4V, V_{CC} = 4V,$<br>ADC clock = 200 kHz                         |                       | 1.5                       |                       |       |  |

|                   | Differential Non-Linearity (DNL)                                                        | Single Ended Conversion<br>$V_{REF} = 4V, V_{CC} = 4V,$<br>ADC clock = 200 kHz                         |                       | 0.3                       |                       |       |  |

|                   | Gain Error                                                                              | Single Ended Conversion<br>$V_{REF} = 4V, V_{CC} = 4V,$<br>ADC clock = 200 kHz                         |                       | 2.5                       |                       |       |  |

|                   | Offset Error                                                                            | Single Ended Conversion<br>$V_{REF} = 4V$ , $V_{CC} = 4V$ ,<br>ADC clock = 200 kHz                     |                       | 2.5                       |                       |       |  |

|                   | Conversion Time                                                                         | Free Running Conversion                                                                                | 13                    |                           | 260                   | μs    |  |

|                   | Clock Frequency                                                                         | Single Ended Conversion                                                                                | 50                    |                           | 1000                  | kHz   |  |

| AVCC              | Analog Supply Voltage                                                                   |                                                                                                        | V <sub>CC</sub> - 0.3 |                           | V <sub>CC</sub> + 0.3 | V     |  |

| $V_{REF}$         | Reference Voltage                                                                       |                                                                                                        | 1.0                   |                           | AVCC                  | V     |  |

| V <sub>IN</sub>   | Input Voltage                                                                           |                                                                                                        | GND                   |                           | V <sub>REF</sub>      | V     |  |

|                   | Input Bandwidth                                                                         |                                                                                                        |                       | 38.5                      |                       | kHz   |  |

| V <sub>INT1</sub> | Internal Voltage Reference                                                              | 1.1V                                                                                                   | 1.0                   | 1.1                       | 1.2                   | V     |  |

| V <sub>INT2</sub> | Internal Voltage Reference                                                              | 2.56V, V <sub>CC</sub> > 2.7V                                                                          | 2.33                  | 2.56                      | 2.79                  | V     |  |

| R <sub>REF</sub>  | Reference Input Resistance                                                              |                                                                                                        |                       | 32                        |                       | kΩ    |  |

| R <sub>AIN</sub>  | Analog Input Resistance                                                                 |                                                                                                        |                       | 100                       |                       | MΩ    |  |

Notes: 1. Values are guidelines only.

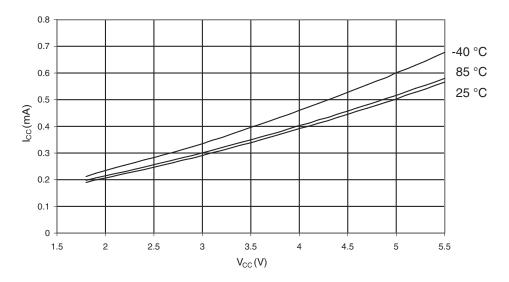

Figure 26-52. Active Supply Current vs.  $V_{CC}$  (Internal RC Oscillator, 128 kHz).

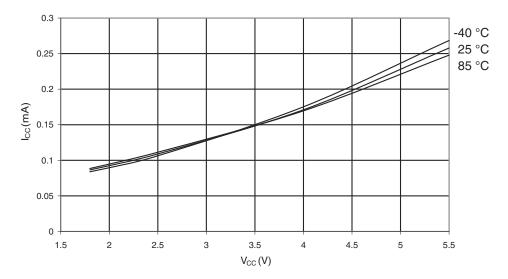

#### 26.2.2 Idle Supply Current

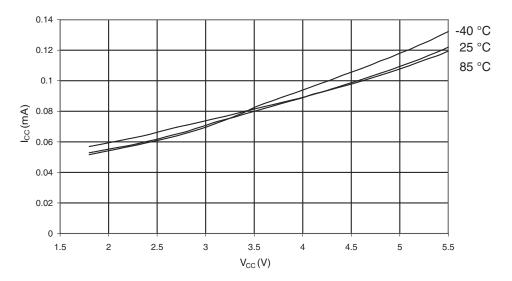

Figure 26-56. Idle Supply Current vs.  $V_{CC}$  (Internal RC Oscillator, 1 MHz).

Figure 26-57. Idle Supply Current vs.  $V_{CC}$  (Internal RC Oscillator, 128 kHz).

Figure 26-88. AREF External Reference Current vs.  $V_{\text{CC}}$

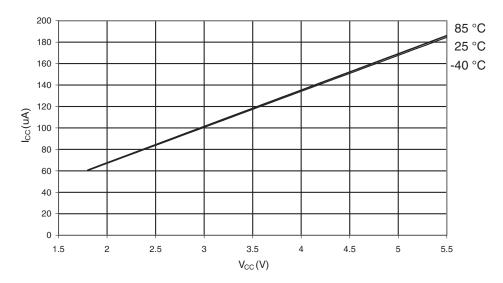

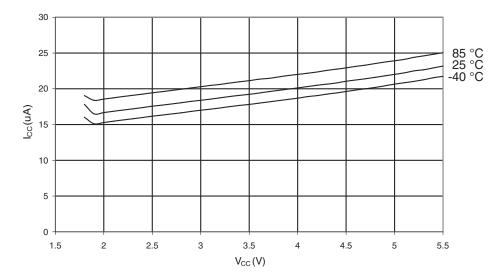

Figure 26-89. Brownout Detector Current vs.  $\mathrm{V}_{\mathrm{CC}}$

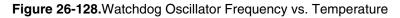

#### 26.3.11 Internal Oscillator Speed