Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | AVR                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 32KB (16K × 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-VQFN (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega324p-20mqr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.5.1 SPH and SPL – Stack Pointer High and Stack pointer Low

| Bit           | 15  | 14  | 13  | 12                   | 11                   | 10                   | 9   | 8   |     |

|---------------|-----|-----|-----|----------------------|----------------------|----------------------|-----|-----|-----|

| 0x3E (0x5E)   | -   | -   | -   | SP12                 | SP11                 | SP10                 | SP9 | SP8 | SPH |

| 0x3D (0x5D)   | SP7 | SP6 | SP5 | SP4                  | SP3                  | SP2                  | SP1 | SP0 | SPL |

|               | 7   | 6   | 5   | 4                    | 3                    | 2                    | 1   | 0   |     |

| Read/Write    | R   | R   | R   | R/W                  | R/W                  | R/W                  | R/W | R/W |     |

|               | R/W | R/W | R/W | R/W                  | R/W                  | R/W                  | R/W | R/W |     |

| Initial Value | 0   | 0   | 0   | 0/0/1 <sup>(1)</sup> | 0/1/0 <sup>(1)</sup> | 1/0/0 <sup>(1)</sup> | 0   | 0   |     |

|               | 1   | 1   | 1   | 1                    | 1                    | 1                    | 1   | 1   |     |

Note: 1. Initial values respectively for the ATmega164P/324P/644P.

#### Table 4-2. Stack Pointer size

| Device     | Stack Pointer size |

|------------|--------------------|

| ATmega164P | SP[10:0]           |

| ATmega324P | SP[11:0]           |

| ATmega644P | SP[12:0]           |

#### 4.5.2 RAMPZ – Extended Z-pointer Register for ELPM/SPM

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

| 0x3B (0x5B)   | RAMPZ7 | RAMPZ6 | RAMPZ5 | RAMPZ4 | RAMPZ3 | RAMPZ2 | RAMPZ1 | RAMPZ0 | RAMPZ |

| Read/Write    | R/W    |       |

| Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

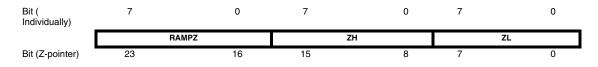

For ELPM/SPM instructions, the Z-pointer is a concatenation of RAMPZ, ZH, and ZL, as shown in Figure 4-4. Note that LPM is not affected by the RAMPZ setting.

Figure 4-4. The Z-pointer used by ELPM and SPM

The actual number of bits is implementation dependent. Unused bits in an implementation will always read as zero. For compatibility with future devices, be sure to write these bits to zero.

#### 4.6 Instruction Execution Timing

This section describes the general access timing concepts for instruction execution. The AVR CPU is driven by the CPU clock  $clk_{CPU}$ , directly generated from the selected clock source for the chip. No internal clock division is used.

Figure 4-5 on page 15 shows the parallel instruction fetches and instruction executions enabled by the Harvard architecture and the fast-access Register File concept. This is the basic pipelining concept to obtain up to 1 MIPS per MHz with the corresponding unique results for functions per cost, functions per clocks, and functions per power-unit.

The following code examples show one assembly and one C function for writing to the EEPROM. The examples assume that interrupts are controlled (e.g. by disabling interrupts globally) so that no interrupts will occur during execution of these functions. The examples also assume that no Flash Boot Loader is present in the software. If such code is present, the EEPROM write function must also wait for any ongoing SPM command to finish.

```

Assembly Code Example<sup>()</sup>

EEPROM_write:

; Wait for completion of previous write

sbic EECR, EEPE

rjmp EEPROM_write

; Set up address (r18:r17) in address register

out EEARH, r18

out EEARL, r17

; Write data (r16) to Data Register

out EEDR, r16

; Write logical one to EEMPE

sbi EECR, EEMPE

; Start eeprom write by setting EEPE

sbi EECR, EEPE

ret

C Code Example<sup>(1)</sup>

void EEPROM_write(unsigned int uiAddress, unsigned char ucData)

{

/* Wait for completion of previous write */

while(EECR & (1<<EEPE))

;

/* Set up address and Data Registers */

EEAR = uiAddress;

EEDR = ucData;

/* Write logical one to EEMPE */

EECR | = (1 < < EEMPE);

/* Start eeprom write by setting EEPE */

EECR \mid = (1<<EPE);

}

```

```

Note: 1. See "About Code Examples" on page 8.

```

# 8.7 Internal Voltage Reference

ATmega164P/324P/644P features an internal bandgap reference. This reference is used for Brown-out Detection, and it can be used as an input to the Analog Comparator or the ADC.

#### 8.7.1 Voltage Reference Enable Signals and Start-up Time

The voltage reference has a start-up time that may influence the way it should be used. The start-up time is given in "System and Reset Characteristics" on page 331. To save power, the reference is not always turned on. The reference is on during the following situations:

- 1. When the BOD is enabled (by programming the BODLEVEL [2:0] Fuse).

- 2. When the bandgap reference is connected to the Analog Comparator (by setting the ACBG bit in ACSR).

- 3. When the ADC is enabled.

Thus, when the BOD is not enabled, after setting the ACBG bit or enabling the ADC, the user must always allow the reference to start up before the output from the Analog Comparator or ADC is used. To reduce power consumption in Power-down mode, the user can avoid the three conditions above to ensure that the reference is turned off before entering Power-down mode.

```

Assembly Code Example

Move_interrupts:

; Get MCUCR

in r16, MCUCR

mov r17, r16

; Enable change of Interrupt Vectors

ori r16, (1<<IVCE)

out MCUCR, r16

; Move interrupts to Boot Flash section

ori r17, (1<<IVSEL)

out MCUCR, r17

ret

C Code Example

void Move_interrupts(void)

{

uchar temp;

/* GET MCUCR*/

temp = MCUCR;

/* Enable change of Interrupt Vectors */

MCUCR = temp | (1<<IVCE);

/* Move interrupts to Boot Flash section */

MCUCR = temp | (1<<IVSEL);

}

```

#### • MOSI/PCINT13 - Port B, Bit 5

MOSI: SPI Master Data output, Slave Data input for SPI channel. When the SPI is enabled as a slave, this pin is configured as an input regardless of the setting of DDB5. When the SPI is enabled as a master, the data direction of this pin is controlled by DDB5. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB5 bit.

PCINT13, Pin Change Interrupt source 13: The PB5 pin can serve as an external interrupt source.

### • SS/OC0B/PCINT12 – Port B, Bit 4

$\overline{SS}$ : Slave Port Select input. When the SPI is enabled as a slave, this pin is configured as an input regardless of the setting of DDB4. As a slave, the SPI is activated when this pin is driven low. When the SPI is enabled as a master, the data direction of this pin is controlled by DDB4. When the pin is forced to be an input, the pull-up can still be controlled by the PORTB4 bit.

OC0B, Output Compare Match B output: The PB4 pin can serve as an external output for the Timer/Counter0 Output Compare. The pin has to be configured as an output (DDB4 set "one") to serve this function. The OC0B pin is also the output pin for the PWM mode timer function.

PCINT12, Pin Change Interrupt source 12: The PB4 pin can serve as an external interrupt source.

#### • AIN1/OC0A/PCINT11, Bit 3

AIN1, Analog Comparator Negative input. This pin is directly connected to the negative input of the Analog Comparator.

OC0A, Output Compare Match A output: The PB3 pin can serve as an external output for the Timer/Counter0 Output Compare. The pin has to be configured as an output (DDB3 set "one") to serve this function. The OC0A pin is also the output pin for the PWM mode timer function.

PCINT11, Pin Change Interrupt source 11: The PB3 pin can serve as an external interrupt source.

#### • AIN0/INT2/PCINT10, Bit 2

AINO, Analog Comparator Positive input. This pin is directly connected to the positive input of the Analog Comparator.

INT2, External Interrupt source 2. The PB2 pin can serve as an External Interrupt source to the MCU.

PCINT10, Pin Change Interrupt source 10: The PB2 pin can serve as an external interrupt source.

#### • T1/CLKO/PCINT9, Bit 1

T1, Timer/Counter1 counter source.

CLKO, Divided System Clock: The divided system clock can be output on the PB1 pin. The divided system clock will be output if the CKOUT Fuse is programmed, regardless of the PORTB1 and DDB1 settings. It will also be output during reset.

PCINT9, Pin Change Interrupt source 9: The PB1 pin can serve as an external interrupt source.

| COM0A1 | COM0A0                                                                                        | Description                                                                                      |

|--------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| 0      | 0                                                                                             | Normal port operation, OC0A disconnected.                                                        |

| 0      | 1                                                                                             | WGM02 = 0: Normal Port Operation, OC0A Disconnected.<br>WGM02 = 1: Toggle OC0A on Compare Match. |

| 1      | 0 Clear OC0A on Compare Match when up-counting. Set OC0A on Compare Match when down-counting. |                                                                                                  |

| 1      | 1                                                                                             | Set OC0A on Compare Match when up-counting. Clear OC0A on Compare Match when down-counting.      |

Table 12-4.

Compare Output Mode, Phase Correct PWM Mode<sup>(1)</sup>

Note: 1. A special case occurs when OCR0A equals TOP and COM0A1 is set. In this case, the Compare Match is ignored, but the set or clear is done at TOP. See "Phase Correct PWM Mode" on page 101 for more details.

#### • Bits 5:4 – COM0B1:0: Compare Match Output B Mode

These bits control the Output Compare pin (OC0B) behavior. If one or both of the COM0B1:0 bits are set, the OC0B output overrides the normal port functionality of the I/O pin it is connected to. However, note that the Data Direction Register (DDR) bit corresponding to the OC0B pin must be set in order to enable the output driver.

When OC0B is connected to the pin, the function of the COM0B1:0 bits depends on the WGM02:0 bit setting. Table 12-2 on page 104 shows the COM0A1:0 bit functionality when the WGM02:0 bits are set to a normal or CTC mode (non-PWM).

| COM0B1 | COM0B0 | Description                               |

|--------|--------|-------------------------------------------|

| 0      | 0      | Normal port operation, OC0B disconnected. |

| 0      | 1      | Toggle OC0B on Compare Match              |

| 1      | 0      | Clear OC0B on Compare Match               |

| 1      | 1      | Set OC0B on Compare Match                 |

Table 12-5. Compare Output Mode, non-PWM Mode

Table 12-6 shows the COM0B1:0 bit functionality when the WGM02:0 bits are set to fast PWM mode.

Table 12-6.

Compare Output Mode, Fast PWM Mode<sup>(1)</sup>

|        | -      | -                                                                      |

|--------|--------|------------------------------------------------------------------------|

| COM0B1 | COM0B0 | Description                                                            |

| 0      | 0      | Normal port operation, OC0B disconnected.                              |

| 0      | 1      | Reserved                                                               |

| 1      | 0      | Clear OC0B on Compare Match, set OC0B at BOTTOM, (non-inverting mode). |

| 1      | 1      | Set OC0B on Compare Match, clear OC0B at BOTTOM, (inverting mode).     |

Note: 1. A special case occurs when OCR0B equals TOP and COM0B1 is set. In this case, the Compare Match is ignored, but the set or clear is done atBOTTOM. See "Fast PWM Mode" on page 99 for more details.

#### • Bits 2:0 - CS02:0: Clock Select

The three Clock Select bits select the clock source to be used by the Timer/Counter.

| CS02 | CS01 | CS00 | Description                                             |

|------|------|------|---------------------------------------------------------|

| 0    | 0    | 0    | No clock source (Timer/Counter stopped)                 |

| 0    | 0    | 1    | clk <sub>I/O</sub> /(No prescaling)                     |

| 0    | 1    | 0    | clk <sub>I/O</sub> /8 (From prescaler)                  |

| 0    | 1    | 1    | clk <sub>I/O</sub> /64 (From prescaler)                 |

| 1    | 0    | 0    | clk <sub>I/O</sub> /256 (From prescaler)                |

| 1    | 0    | 1    | clk <sub>I/O</sub> /1024 (From prescaler)               |

| 1    | 1    | 0    | External clock source on T0 pin. Clock on falling edge. |

| 1    | 1    | 1    | External clock source on T0 pin. Clock on rising edge.  |

Table 12-9. Clock Select Bit Description

If external pin modes are used for the Timer/Counter0, transitions on the T0 pin will clock the counter even if the pin is configured as an output. This feature allows software control of the counting.

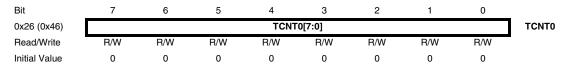

#### 12.9.3 TCNT0 – Timer/Counter Register

The Timer/Counter Register gives direct access, both for read and write operations, to the Timer/Counter unit 8-bit counter. Writing to the TCNT0 Register blocks (removes) the Compare Match on the following timer clock. Modifying the counter (TCNT0) while the counter is running, introduces a risk of missing a Compare Match between TCNT0 and the OCR0x Registers.

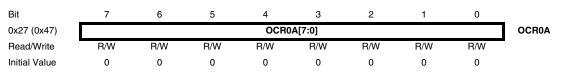

### 12.9.4 OCR0A – Output Compare Register A

The Output Compare Register A contains an 8-bit value that is continuously compared with the counter value (TCNT0). A match can be used to generate an Output Compare interrupt, or to generate a waveform output on the OC0A pin.

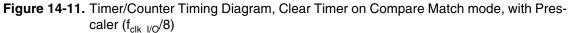

Figure 14-11 on page 150 shows the setting of OCF2A and the clearing of TCNT2 in CTC mode.

### 14.9 Asynchronous Operation of Timer/Counter2

When Timer/Counter2 operates asynchronously, some considerations must be taken.

- Warning: When switching between asynchronous and synchronous clocking of Timer/Counter2, the Timer Registers TCNT2, OCR2x, and TCCR2x might be corrupted. A safe procedure for switching clock source is:

- a. Disable the Timer/Counter2 interrupts by clearing OCIE2x and TOIE2.

- b. Select clock source by setting AS2 as appropriate.

- c. Write new values to TCNT2, OCR2x, and TCCR2x.

- d. To switch to asynchronous operation: Wait for TCN2UB, OCR2xUB, and TCR2xUB.

- e. Clear the Timer/Counter2 Interrupt Flags.

- f. Enable interrupts, if needed.

- The CPU main clock frequency must be more than four times the Oscillator frequency.

- When writing to one of the registers TCNT2, OCR2x, or TCCR2x, the value is transferred to a

temporary register, and latched after two positive edges on TOSC1. The user should not write

a new value before the contents of the temporary register have been transferred to its

destination. Each of the five mentioned registers have their individual temporary register, which

means that e.g. writing to TCNT2 does not disturb an OCR2x write in progress. To detect that a

transfer to the destination register has taken place, the Asynchronous Status Register ASSR

has been implemented.

- When entering Power-save or ADC Noise Reduction mode after having written to TCNT2, OCR2x, or TCCR2x, the user must wait until the written register has been updated if Timer/Counter2 is used to wake up the device. Otherwise, the MCU will enter sleep mode before the changes are effective. This is particularly important if any of the Output Compare2 interrupt is used to wake up the device, since the Output Compare function is disabled during writing to OCR2x or TCNT2. If the write cycle is not finished, and the MCU enters sleep mode

Match on the following timer clock. Modifying the counter (TCNT2) while the counter is running, introduces a risk of missing a Compare Match between TCNT2 and the OCR2x Registers.

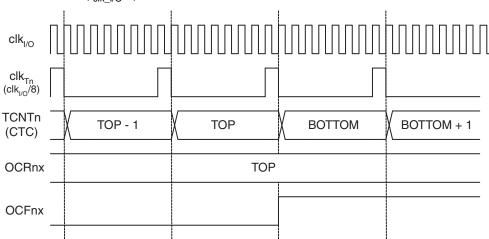

#### 14.11.4 OCR2A – Output Compare Register A

The Output Compare Register A contains an 8-bit value that is continuously compared with the counter value (TCNT2). A match can be used to generate an Output Compare interrupt, or to generate a waveform output on the OC2A pin.

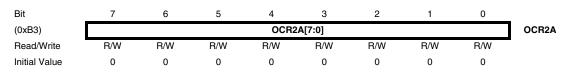

#### 14.11.5 OCR2B – Output Compare Register B

The Output Compare Register B contains an 8-bit value that is continuously compared with the counter value (TCNT2). A match can be used to generate an Output Compare interrupt, or to generate a waveform output on the OC2B pin.

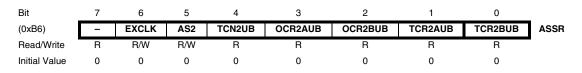

#### 14.11.6 ASSR – Asynchronous Status Register

#### Bit 6 – EXCLK: Enable External Clock Input

When EXCLK is written to one, and asynchronous clock is selected, the external clock input buffer is enabled and an external clock can be input on Timer Oscillator 1 (TOSC1) pin instead of a 32 kHz crystal. Writing to EXCLK should be done before asynchronous operation is selected. Note that the crystal Oscillator will only run when this bit is zero.

#### Bit 5 – AS2: Asynchronous Timer/Counter2

When AS2 is written to zero, Timer/Counter2 is clocked from the I/O clock, clk<sub>I/O</sub>. When AS2 is written to one, Timer/Counter2 is clocked from a crystal Oscillator connected to the Timer Oscillator 1 (TOSC1) pin. When the value of AS2 is changed, the contents of TCNT2, OCR2A, OCR2B, TCCR2A and TCCR2B might be corrupted.

#### • Bit 4 – TCN2UB: Timer/Counter2 Update Busy

When Timer/Counter2 operates asynchronously and TCNT2 is written, this bit becomes set. When TCNT2 has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that TCNT2 is ready to be updated with a new value.

#### Bit 3 – OCR2AUB: Output Compare Register2 Update Busy

When Timer/Counter2 operates asynchronously and OCR2A is written, this bit becomes set. When OCR2A has been updated from the temporary storage register, this bit is cleared by hardware. A logical zero in this bit indicates that OCR2A is ready to be updated with a new value.

```

Assembly Code Example<sup>(1)</sup>

SPI_MasterInit:

; Set MOSI and SCK output, all others input

ldi r17, (1<<DD_MOSI) | (1<<DD_SCK)

out DDR_SPI,r17

; Enable SPI, Master, set clock rate fck/16

ldi r17,(1<<SPE) | (1<<MSTR) | (1<<SPR0)

out SPCR, r17

ret

SPI_MasterTransmit:

; Start transmission of data (r16)

out SPDR, r16

Wait_Transmit:

; Wait for transmission complete

sbis SPSR, SPIF

rjmp Wait_Transmit

ret

C Code Example<sup>(1)</sup>

void SPI_MasterInit(void)

{

/* Set MOSI and SCK output, all others input */

DDR_SPI = (1<<DD_MOSI) | (1<<DD_SCK);

/* Enable SPI, Master, set clock rate fck/16 */

SPCR = (1<<SPE) | (1<<MSTR) | (1<<SPR0);

}

void SPI_MasterTransmit(char cData)

{

/* Start transmission */

SPDR = cData;

/* Wait for transmission complete */

while(!(SPSR & (1<<SPIF)))</pre>

;

```

}

the Master to switch between Slaves, Master Transmitter mode and Master Receiver mode without losing control over the bus.

Table 18-3. Status codes for Master Receiver Mode

| Status Code              |                                                                      | Applica           | tion Softv | vare Resp | onse  |      |                                                                                               |

|--------------------------|----------------------------------------------------------------------|-------------------|------------|-----------|-------|------|-----------------------------------------------------------------------------------------------|

| (TWSR)<br>Prescaler Bits | Status of the 2-wire Serial Bus<br>and 2-wire Serial Interface Hard- |                   |            | To        | TWCR  |      |                                                                                               |

| are 0                    | ware                                                                 | To/from TWDR      | STA        | STO       | TWINT | TWEA | Next Action Taken by TWI Hardware                                                             |

| 0x08                     | A START condition has been transmitted                               | Load SLA+R        | 0          | 0         | 1     | х    | SLA+R will be transmitted<br>ACK or NOT ACK will be received                                  |

| 0x10                     | A repeated START condition has been transmitted                      | Load SLA+R or     | 0          | 0         | 1     | х    | SLA+R will be transmitted<br>ACK or NOT ACK will be received                                  |

|                          |                                                                      | Load SLA+W        | 0          | 0         | 1     | х    | SLA+W will be transmitted<br>Logic will switch to Master Transmitter mode                     |

| 0x38                     | Arbitration lost in SLA+R or NOT ACK bit                             | No TWDR action or | 0          | 0         | 1     | х    | 2-wire Serial Bus will be released and not addressed<br>Slave mode will be entered            |

|                          |                                                                      | No TWDR action    | 1          | 0         | 1     | х    | A START condition will be transmitted when the bus becomes free                               |

| 0x40                     | SLA+R has been transmitted;<br>ACK has been received                 | No TWDR action or | 0          | 0         | 1     | 0    | Data byte will be received and NOT ACK will be<br>returned                                    |

|                          |                                                                      | No TWDR action    | 0          | 0         | 1     | 1    | Data byte will be received and ACK will be returned                                           |

| 0x48                     | SLA+R has been transmitted;                                          | No TWDR action or | 1          | 0         | 1     | Х    | Repeated START will be transmitted                                                            |

|                          | NOT ACK has been received                                            | No TWDR action or | 0          | 1         | 1     | Х    | STOP condition will be transmitted and TWSTO Flag will be reset                               |

|                          |                                                                      | No TWDR action    | 1          | 1         | 1     | х    | STOP condition followed by a START condition will be transmitted and TWSTO Flag will be reset |

| 0x50                     | Data byte has been received;<br>ACK has been returned                | Read data byte or | 0          | 0         | 1     | 0    | Data byte will be received and NOT ACK will be<br>returned                                    |

|                          |                                                                      | Read data byte    | 0          | 0         | 1     | 1    | Data byte will be received and ACK will be returned                                           |

| 0x58                     | Data byte has been received;                                         | Read data byte or | 1          | 0         | 1     | х    | Repeated START will be transmitted                                                            |

|                          | NOT ACK has been returned                                            | Read data byte or | 0          | 1         | 1     | Х    | STOP condition will be transmitted and TWSTO Flag will be reset                               |

|                          |                                                                      | Read data byte    | 1          | 1         | 1     | х    | STOP condition followed by a START condition will be transmitted and TWSTO Flag will be reset |

bus are written to the TWDR. It also indicates a write collision if data is attempted written to TWDR while the register is inaccessible.

#### • Bit 7 – TWINT: TWI Interrupt Flag

This bit is set by hardware when the TWI has finished its current job and expects application software response. If the I-bit in SREG and TWIE in TWCR are set, the MCU will jump to the TWI Interrupt Vector. While the TWINT Flag is set, the SCL low period is stretched. The TWINT Flag must be cleared by software by writing a logic one to it. Note that this flag is not automatically cleared by hardware when executing the interrupt routine. Also note that clearing this flag starts the operation of the TWI, so all accesses to the TWI Address Register (TWAR), TWI Status Register (TWSR), and TWI Data Register (TWDR) must be complete before clearing this flag.

#### Bit 6 – TWEA: TWI Enable Acknowledge Bit

The TWEA bit controls the generation of the acknowledge pulse. If the TWEA bit is written to one, the ACK pulse is generated on the TWI bus if the following conditions are met:

- 1. The device's own slave address has been received.

- 2. A general call has been received, while the TWGCE bit in the TWAR is set.

- 3. A data byte has been received in Master Receiver or Slave Receiver mode.

By writing the TWEA bit to zero, the device can be virtually disconnected from the 2-wire Serial Bus temporarily. Address recognition can then be resumed by writing the TWEA bit to one again.

#### • Bit 5 – TWSTA: TWI START Condition Bit

The application writes the TWSTA bit to one when it desires to become a Master on the 2-wire Serial Bus. The TWI hardware checks if the bus is available, and generates a START condition on the bus if it is free. However, if the bus is not free, the TWI waits until a STOP condition is detected, and then generates a new START condition to claim the bus Master status. TWSTA must be cleared by software when the START condition has been transmitted.

#### • Bit 4 – TWSTO: TWI STOP Condition Bit

Writing the TWSTO bit to one in Master mode will generate a STOP condition on the 2-wire Serial Bus. When the STOP condition is executed on the bus, the TWSTO bit is cleared automatically. In Slave mode, setting the TWSTO bit can be used to recover from an error condition. This will not generate a STOP condition, but the TWI returns to a well-defined unaddressed Slave mode and releases the SCL and SDA lines to a high impedance state.

#### Bit 3 – TWWC: TWI Write Collision Flag

The TWWC bit is set when attempting to write to the TWI Data Register – TWDR when TWINT is low. This flag is cleared by writing the TWDR Register when TWINT is high.

#### • Bit 2 – TWEN: TWI Enable Bit

The TWEN bit enables TWI operation and activates the TWI interface. When TWEN is written to one, the TWI takes control over the I/O pins connected to the SCL and SDA pins, enabling the slew-rate limiters and spike filters. If this bit is written to zero, the TWI is switched off and all TWI transmissions are terminated, regardless of any ongoing operation.

#### • Bit 1 – Res: Reserved Bit

This bit is a reserved bit and will always read as zero.

| Table 20-1. ADC Conversion Time  |                                                    |                          |  |  |  |  |  |  |  |

|----------------------------------|----------------------------------------------------|--------------------------|--|--|--|--|--|--|--|

| Condition                        | Sample & Hold (Cycles<br>from Start of Conversion) | Conversion Time (Cycles) |  |  |  |  |  |  |  |

| First conversion                 | 14.5                                               | 25                       |  |  |  |  |  |  |  |

| Normal conversions, single ended | 1.5                                                | 13                       |  |  |  |  |  |  |  |

| Auto Triggered conversions       | 2                                                  | 13.5                     |  |  |  |  |  |  |  |

| Normal conversions, differential | 1.5/2.5                                            | 13/14                    |  |  |  |  |  |  |  |

Table 20-1. ADC Conversion Time

#### 20.5.1 Differential Gain Channels

When using differential gain channels, certain aspects of the conversion need to be taken into consideration. Note that the differential channels should not be used with an AREF < 2V.

Differential conversions are synchronized to the internal clock  $CK_{ADC2}$  equal to half the ADC clock. This synchronization is done automatically by the ADC interface in such a way that the sample-and-hold occurs at a specific phase of  $CK_{ADC2}$ . A conversion initiated by the user (i.e., all single conversions, and the first free running conversion) when  $CK_{ADC2}$  is low will take the same amount of time as a single ended conversion (13 ADC clock cycles from the next prescaled clock cycle). A conversion initiated by the user when  $CK_{ADC2}$  is high will take 14 ADC clock cycles due to the synchronization mechanism. In Free Running mode, a new conversion is initiated immediately after the previous conversion completes, and since  $CK_{ADC2}$  is high at this time, all automatically started (i.e., all but the first) free running conversions will take 14 ADC clock cycles.

The gain stage is optimized for a bandwidth of 4 kHz at all gain settings. Higher frequencies may be subjected to non-linear amplification. An external low-pass filter should be used if the input signal contains higher frequency components than the gain stage bandwidth. Note that the ADC clock frequency is independent of the gain stage bandwidth limitation. For example, the ADC clock period may be 6  $\mu$ s, allowing a channel to be sampled at 12 kSPS, regardless of the bandwidth of this channel.

If differential gain channels are used and conversions are started by Auto Triggering, the ADC must be switched off between conversions. When Auto Triggering is used, the ADC prescaler is reset before the conversion is started. Since the gain stage is dependent of a stable ADC clock prior to the conversion, this conversion will not be valid. By disabling and then re-enabling the ADC between each conversion (writing ADEN in ADCSRA to "0" then to "1"), only extended conversions are performed. The result from the extended conversions will be valid. See "Prescaling and Conversion Timing" on page 243 for timing details.

## 20.6 Changing Channel or Reference Selection

The MUXn and REFS1:0 bits in the ADMUX Register are single buffered through a temporary register to which the CPU has random access. This ensures that the channels and reference selection only takes place at a safe point during the conversion. The channel and reference selection is continuously updated until a conversion is started. Once the conversion starts, the channel and reference selection is locked to ensure a sufficient sampling time for the ADC. Continuous updating resumes in the last ADC clock cycle before the conversion completes (ADIF in ADCSRA is set). Note that the conversion starts on the following rising ADC clock edge after ADSC is written. The user is thus advised not to write new channel or reference selection values to ADMUX until one ADC clock cycle after ADSC is written.

# ATmega164P/324P/644P

Example:

ADMUX = 0xED (ADC3 - ADC2, 10x gain, 2.56V reference, left adjusted result)

Voltage on ADC3 is 300 mV, voltage on ADC2 is 500 mV.

ADCR = 512 \* 10 \* (300 - 500) / 2560 = -400 = 0x270

ADCL will thus read 0x00, and ADCH will read 0x9C. Writing zero to ADLAR right adjusts the result: ADCL = 0x70, ADCH = 0x02.

#### 20.9 Register Description

#### 20.9.1 ADMUX – ADC Multiplexer Selection Register

| Bit           | 7     | 6     | 5     | 4    | 3    | 2    | 1    | 0    |       |

|---------------|-------|-------|-------|------|------|------|------|------|-------|

| (0x7C)        | REFS1 | REFS0 | ADLAR | MUX4 | MUX3 | MUX2 | MUX1 | MUX0 | ADMUX |

| Read/Write    | R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | -     |

| Initial Value | 0     | 0     | 0     | 0    | 0    | 0    | 0    | 0    |       |

#### Bit 7:6 – REFS1:0: Reference Selection Bits

These bits select the voltage reference for the ADC, as shown in Table 20-3. If these bits are changed during a conversion, the change will not go in effect until this conversion is complete (ADIF in ADCSRA is set). The internal voltage reference options may not be used if an external reference voltage is being applied to the AREF pin.

Table 20-3. Voltage Reference Selections for ADC

| REFS1 | REFS0 | Voltage Reference Selection                                          |

|-------|-------|----------------------------------------------------------------------|

| 0     | 0     | AREF, Internal Vref turned off                                       |

| 0     | 1     | AVCC with external capacitor at AREF pin                             |

| 1     | 0     | Internal 1.1V Voltage Reference with external capacitor at AREF pin  |

| 1     | 1     | Internal 2.56V Voltage Reference with external capacitor at AREF pin |

Note: If 10x og 200x gain is selected, only 2.56V should be used as Internal Voltage Reference.

#### Bit 5 – ADLAR: ADC Left Adjust Result

The ADLAR bit affects the presentation of the ADC conversion result in the ADC Data Register. Write one to ADLAR to left adjust the result. Otherwise, the result is right adjusted. Changing the ADLAR bit will affect the ADC Data Register immediately, regardless of any ongoing conversions. For a complete description of this bit, see "ADCL and ADCH – The ADC Data Register" on page 258.

#### • Bits 4:0 – MUX4:0: Analog Channel and Gain Selection Bits

The value of these bits selects which combination of analog inputs are connected to the ADC. These bits also select the gain for the differential channels. See Table 20-4 on page 256 for details. If these bits are changed during a conversion, the change will not go in effect until this conversion is complete (ADIF in ADCSRA is set).

# ATmega164P/324P/644P

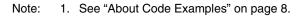

Note: 1. The parameters in the figure above are given in Table 23-7 on page 288.

## 23.5 Boot Loader Lock Bits

If no Boot Loader capability is needed, the entire Flash is available for application code. The Boot Loader has two separate sets of Boot Lock bits which can be set independently. This gives the user a unique flexibility to select different levels of protection.

The user can select:

- To protect the entire Flash from a software update by the MCU.

- To protect only the Boot Loader Flash section from a software update by the MCU.

- To protect only the Application Flash section from a software update by the MCU.

• Allow software update in the entire Flash.

See Table 23-2 on page 280 and Table 23-3 on page 280 for further details. The Boot Lock bits can be set in software and in Serial or Parallel Programming mode, but they can be cleared by a Chip Erase command only. The general Write Lock (Lock Bit mode 2) does not control the programming of the Flash memory by SPM instruction. Similarly, the general Read/Write Lock (Lock Bit mode 1) does not control reading nor writing by (E)LPM/SPM, if it is attempted.

# 24. Memory Programming

# 24.1 Program And Data Memory Lock Bits

The ATmega164P/324P/644P provides six Lock bits which can be left unprogrammed ("1") or can be programmed ("0") to obtain the additional features listed in Table 24-2. The Lock bits can only be erased to "1" with the Chip Erase command.

| Lock Bit Byte | Bit No | Description   | Default Value    |  |

|---------------|--------|---------------|------------------|--|

|               | 7      | -             | 1 (unprogrammed) |  |

|               | 6      | -             | 1 (unprogrammed) |  |

| BLB12         | 5      | Boot Lock bit | 1 (unprogrammed) |  |

| BLB11         | 4      | Boot Lock bit | 1 (unprogrammed) |  |

| BLB02         | 3      | Boot Lock bit | 1 (unprogrammed) |  |

| BLB01         | 2      | Boot Lock bit | 1 (unprogrammed) |  |

| LB2           | 1      | Lock bit      | 1 (unprogrammed) |  |

| LB1           | 0      | Lock bit      | 1 (unprogrammed) |  |

Note: 1. "1" means unprogrammed, "0" means programmed

| Memory Lock Bits |       |       | Protection Type                                                                                                                                                                                                                                                                                              |

|------------------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LB Mode          | LB2   | LB1   |                                                                                                                                                                                                                                                                                                              |

| 1                | 1     | 1     | No memory lock features enabled.                                                                                                                                                                                                                                                                             |

| 2                | 1     | 0     | Further programming of the Flash and EEPROM is disabled in Parallel and Serial Programming mode. The Fuse bits are locked in both Serial and Parallel Programming mode. <sup>(1)</sup>                                                                                                                       |

| 3                | 0     | 0     | Further programming and verification of the Flash and EEPROM is disabled in Parallel and Serial Programming mode. The Boot Lock bits and Fuse bits are locked in both Serial and Parallel Programming mode. <sup>(1)</sup>                                                                                   |

| BLB0 Mode        | BLB02 | BLB01 |                                                                                                                                                                                                                                                                                                              |

| 1                | 1     | 1     | No restrictions for SPM or (E)LPM accessing the Application section.                                                                                                                                                                                                                                         |

| 2                | 1     | 0     | SPM is not allowed to write to the Application section.                                                                                                                                                                                                                                                      |

| 3                | 0     | 0     | SPM is not allowed to write to the Application section, and<br>(E)LPM executing from the Boot Loader section is not allowed to<br>read from the Application section. If Interrupt Vectors are placed<br>in the Boot Loader section, interrupts are disabled while<br>executing from the Application section. |

| 4                | 0     | 1     | (E)LPM executing from the Boot Loader section is not allowed to<br>read from the Application section. If Interrupt Vectors are placed<br>in the Boot Loader section, interrupts are disabled while<br>executing from the Application section.                                                                |

# ATmega164P/324P/644P

# 25.3 Clock Characteristics

|                        | Frequency     | V <sub>cc</sub>                                          | Temperature  | Calibration Accuracy |  |

|------------------------|---------------|----------------------------------------------------------|--------------|----------------------|--|

| Factory<br>Calibration | 8.0 MHz       | з٧                                                       | 25°C         | ±10%                 |  |

| User<br>Calibration    | 7.3 - 8.1 MHz | 1.8V - 5.5V <sup>(1)</sup><br>2.7V - 5.5V <sup>(2)</sup> | -40°C - 85°C | ±1%                  |  |

Table 25-4. Calibration Accuracy of Internal RC Oscillator

Notes: 1. Voltage range for ATmega164PV/324PV/644PV.

2. Voltage range for ATmega164P/324P/644P.

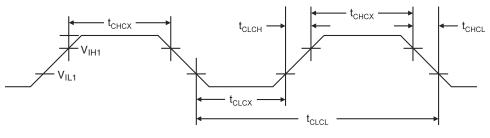

#### 25.3.1 External Clock Drive Waveforms

#### 25.3.2 External Clock Drive

#### Table 25-5. External Clock Drive

|                     |                                                         |      | V <sub>CC</sub> =1.8-5.5V |      | V <sub>CC</sub> =2.7-5.5V |      | V <sub>CC</sub> =4.5-5.5V |       |

|---------------------|---------------------------------------------------------|------|---------------------------|------|---------------------------|------|---------------------------|-------|

| Symbol              | Parameter                                               | Min. | Max.                      | Min. | Max.                      | Min. | Max.                      | Units |

| 1/t <sub>CLCL</sub> | Oscillator Frequency                                    | 0    | 4                         | 0    | 10                        | 0    | 20                        | MHz   |

| t <sub>CLCL</sub>   | Clock Period                                            | 250  |                           | 100  |                           | 50   |                           | ns    |

| t <sub>CHCX</sub>   | High Time                                               | 100  |                           | 40   |                           | 20   |                           | ns    |

| t <sub>CLCX</sub>   | Low Time                                                | 100  |                           | 40   |                           | 20   |                           | ns    |

| t <sub>CLCH</sub>   | Rise Time                                               |      | 2.0                       |      | 1.6                       |      | 0.5                       | μS    |

| t <sub>CHCL</sub>   | Fall Time                                               |      | 2.0                       |      | 1.6                       |      | 0.5                       | μS    |

| $\Delta t_{CLCL}$   | Change in period from<br>one clock cycle to the<br>next |      | 2                         |      | 2                         |      | 2                         | %     |

# 26.1.2 Idle Supply Current

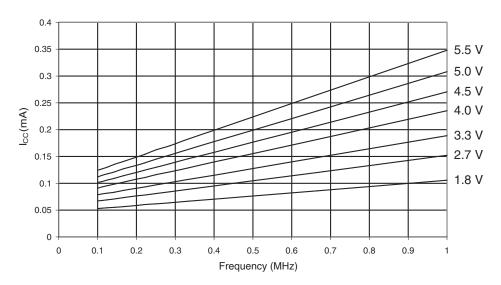

Figure 26-6. Idle Supply Current vs.Low Frequency (0.1 - 1.0 MHz).

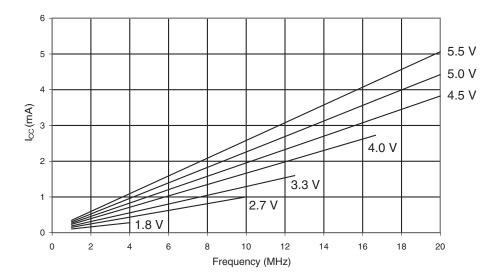

Figure 26-7. Idle Supply Current vs. Frequency (1 - 20 MHz).

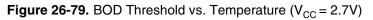

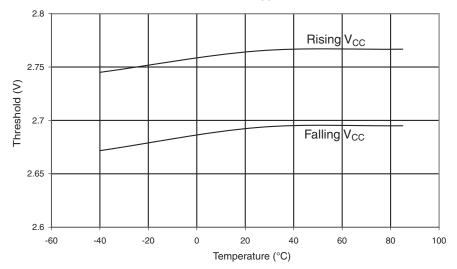

#### 26.2.10 BOD Threshold

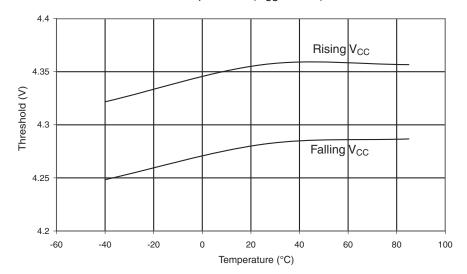

Figure 26-78. BOD Threshold vs. Temperature ( $V_{CC} = 4.3V$ )

| 7 | Table of Contents        | i   |

|---|--------------------------|-----|

|   | 32.14 Rev. 8011A - 08/06 | 430 |

|   | 32.13 Rev. 8011B - 09/06 | 430 |

|   | 32.12 Rev. 8011C - 10/06 | 429 |