Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

|                            |                                                                           |

| Core Processor             | AVR                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 32                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 2K x 8                                                                    |

| /oltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega324p-20pu |

The following code examples show one assembly and one C function for writing to the EEPROM. The examples assume that interrupts are controlled (e.g. by disabling interrupts globally) so that no interrupts will occur during execution of these functions. The examples also assume that no Flash Boot Loader is present in the software. If such code is present, the EEPROM write function must also wait for any ongoing SPM command to finish.

```

Assembly Code Example()

EEPROM_write:

; Wait for completion of previous write

sbic EECR, EEPE

rjmp EEPROM_write

; Set up address (r18:r17) in address register

out EEARH, r18

out EEARL, r17

; Write data (r16) to Data Register

out EEDR, r16

; Write logical one to EEMPE

sbi EECR, EEMPE

; Start eeprom write by setting EEPE

sbi EECR, EEPE

C Code Example<sup>(1)</sup>

void EEPROM_write(unsigned int uiAddress, unsigned char ucData)

/* Wait for completion of previous write */

while (EECR & (1<<EEPE))

/* Set up address and Data Registers */

EEAR = uiAddress;

EEDR = ucData;

/* Write logical one to EEMPE */

EECR \mid = (1 << EEMPE);

/* Start eeprom write by setting EEPE */

EECR \mid = (1 << EEPE);

```

Note: 1. See "About Code Examples" on page 8.

# ATmega164P/324P/644P

neither the clock frequency corresponding to the previous setting, nor the clock frequency corresponding to the new setting.

The ripple counter that implements the prescaler runs at the frequency of the undivided clock, which may be faster than the CPU's clock frequency. Hence, it is not possible to determine the state of the prescaler - even if it were readable, and the exact time it takes to switch from one clock division to the other cannot be exactly predicted. From the time the CLKPS values are written, it takes between T1 + T2 and T1 + 2 \* T2 before the new clock frequency is active. In this interval, 2 active clock edges are produced. Here, T1 is the previous clock period, and T2 is the period corresponding to the new prescaler setting.

To avoid unintentional changes of clock frequency, a special write procedure must be followed to change the CLKPS bits:

- 1. Write the Clock Prescaler Change Enable (CLKPCE) bit to one and all other bits in CLKPR to zero.

- 2. Within four cycles, write the desired value to CLKPS while writing a zero to CLKPCE. Interrupts must be disabled when changing prescaler setting to make sure the write procedure is not interrupted.

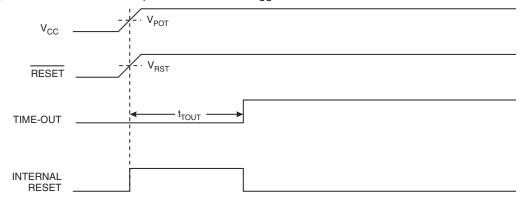

Figure 8-2. MCU Start-up, RESET Tied to V<sub>CC</sub>

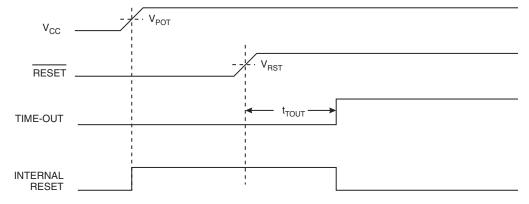

Figure 8-3. MCU Start-up, RESET Extended Externally

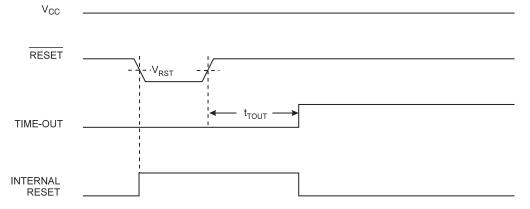

# 8.4 External Reset

An External Reset is generated by a low level on the  $\overline{\text{RESET}}$  pin. Reset pulses longer than the minimum pulse width (see "System and Reset Characteristics" on page 331) will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset. When the applied signal reaches the Reset Threshold Voltage –  $V_{RST}$  – on its positive edge, the delay counter starts the MCU after the Time-out period –  $t_{TOUT}$  – has expired.

Figure 8-4. External Reset During Operation

- In the same operation, write a logic one to the Watchdog change enable bit (WDCE) and WDE. A logic one must be written to WDE regardless of the previous value of the WDE bit.

- 2. Within the next four clock cycles, write the WDE and Watchdog prescaler bits (WDP) as desired, but with the WDCE bit cleared. This must be done in one operation.

The following code example shows one assembly and one C function for turning off the Watchdog Timer. The example assumes that interrupts are controlled (e.g. by disabling interrupts globally) so that no interrupts will occur during the execution of these functions.

```

Assembly Code Example<sup>(1)</sup>

WDT off:

; Turn off global interrupt

cli

; Reset Watchdog Timer

wdr

; Clear WDRF in MCUSR

r16, MCUSR

andi r16, (0xff & (0<<WDRF))</pre>

MCUSR, r16

out

; Write logical one to WDCE and WDE

; Keep old prescaler setting to prevent unintentional time-out

r16, WDTCSR

in

r16, (1<<WDCE) | (1<<WDE)

ori

WDTCSR, r16

out

; Turn off WDT

ldi

r16, (0<<WDE)

WDTCSR, r16

; Turn on global interrupt

sei

ret

```

## C Code Example<sup>(1)</sup>

```

void WDT_off(void)

{

__disable_interrupt();

__watchdog_reset();

/* Clear WDRF in MCUSR */

MCUSR &= ~(1<<WDRF);

/* Write logical one to WDCE and WDE */

/* Keep old prescaler setting to prevent unintentional time-out */

WDTCSR |= (1<<WDCE) | (1<<WDE);

/* Turn off WDT */

WDTCSR = 0x00;

__enable_interrupt();

}</pre>

```

Note: 1. The example code assumes that the part specific header file is included.

# 10. External Interrupts

#### 10.1 Overview

The External Interrupts are triggered by the INT2:0 pin or any of the PCINT31:0 pins. Observe that, if enabled, the interrupts will trigger even if the INT2:0 or PCINT31:0 pins are configured as outputs. This feature provides a way of generating a software interrupt.

The Pin change interrupt PCI3 will trigger if any enabled PCINT31:24 pin toggle, Pin change interrupt PCI2 will trigger if any enabled PCINT23:16 pin toggles, Pin change interrupt PCI1 if any enabled PCINT15:8 toggles and Pin change interrupts PCI0 will trigger if any enabled PCINT7:0 pin toggles. PCMSK3, PCMSK2, PCMSK1 and PCMSK0 Registers control which pins contribute to the pin change interrupts. Pin change interrupts on PCINT31:0 are detected asynchronously. This implies that these interrupts can be used for waking the part also from sleep modes other than Idle mode.

The External Interrupts can be triggered by a falling or rising edge or a low level. This is set up as indicated in the specification for the External Interrupt Control Registers – EICRA (INT2:0). When the external interrupt is enabled and is configured as level triggered, the interrupt will trigger as long as the pin is held low. Low level interrupts and the edge interrupt on INT2:0 are detected asynchronously. This implies that these interrupts can be used for waking the part also from sleep modes other than Idle mode. The I/O clock is halted in all sleep modes except Idle mode.

Note that if a level triggered interrupt is used for wake-up from Power-down, the required level must be held long enough for the MCU to complete the wake-up to trigger the level interrupt. If the level disappears before the end of the Start-up Time, the MCU will still wake up, but no interrupt will be generated. The start-up time is defined by the SUT and CKSEL Fuses as described in "System Clock and Clock Options" on page 29.

# 10.2 Register Description

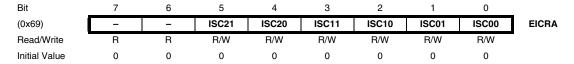

### 10.2.1 EICRA – External Interrupt Control Register A

The External Interrupt Control Register A contains control bits for interrupt sense control.

#### • Bits 7:6 - Reserved

These bits are reserved in the ATmega164P/324P/644P, and will always read as zero.

## • Bits 5:0 – ISC21, ISC20 – ISC00, ISC00: External Interrupt 2 - 0 Sense Control Bits

The External Interrupts 2 - 0 are activated by the external pins INT2:0 if the SREG I-flag and the corresponding interrupt mask in the EIMSK is set. The level and edges on the external pins that activate the interrupts are defined in Table 10-1. Edges on INT2..INT0 are registered asynchronously. Pulses on INT2:0 pins wider than the minimum pulse width given in "External Interrupts Characteristics" on page 331 will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt. If low level interrupt is selected, the low level must be held until the com-

If PORTxn is written logic one when the pin is configured as an output pin, the port pin is driven high (one). If PORTxn is written logic zero when the pin is configured as an output pin, the port pin is driven low (zero).

## 11.2.2 Toggling the Pin

Writing a logic one to PINxn toggles the value of PORTxn, independent on the value of DDRxn. Note that the SBI instruction can be used to toggle one single bit in a port.

#### 11.2.3 Switching Between Input and Output

When switching between tri-state ({DDxn, PORTxn} = 0b00) and output high ({DDxn, PORTxn} = 0b11), an intermediate state with either pull-up enabled {DDxn, PORTxn} = 0b01) or output low ({DDxn, PORTxn} = 0b10) must occur. Normally, the pull-up enabled state is fully acceptable, as a high-impedant environment will not notice the difference between a strong high driver and a pull-up. If this is not the case, the PUD bit in the MCUCR Register can be set to disable all pull-ups in all ports.

Switching between input with pull-up and output low generates the same problem. The user must use either the tri-state ({DDxn, PORTxn} = 0b00) or the output high state ({DDxn, PORTxn} = 0b11) as an intermediate step.

Table 11-1 summarizes the control signals for the pin value.

**Table 11-1.** Port Pin Configurations

| DDxn | PORTxn | PUD<br>(in MCUCR) | I/O    | Pull-up                 | Comment                                     |  |  |

|------|--------|-------------------|--------|-------------------------|---------------------------------------------|--|--|

| 0    | 0      | X                 | Input  | No                      | Tri-state (Hi-Z)                            |  |  |

| U    | U      | ^                 | IIIput | INO                     | III-State (III-Z)                           |  |  |

| 0    | 1      | 0                 | Input  | Yes                     | Pxn will source current if ext. pulled low. |  |  |

| 0    | 1      | 1                 | Input  | No Tri-state (Hi-Z)     |                                             |  |  |

| 1    | 0      | X                 | Output | No Output Low (Sink)    |                                             |  |  |

| 1    | 1      | X                 | Output | No Output High (Source) |                                             |  |  |

## 11.2.4 Reading the Pin Value

Independent of the setting of Data Direction bit DDxn, the port pin can be read through the PINxn Register bit. As shown in Figure 11-2, the PINxn Register bit and the preceding latch constitute a synchronizer. This is needed to avoid metastability if the physical pin changes value near the edge of the internal clock, but it also introduces a delay. Figure 11-3 shows a timing diagram of the synchronization when reading an externally applied pin value. The maximum and minimum propagation delays are denoted  $t_{\rm pd,max}$  and  $t_{\rm pd,min}$  respectively.

# ATmega164P/324P/644P

Table 11-2 summarizes the function of the overriding signals. The pin and port indexes from Figure 11-5 are not shown in the succeeding tables. The overriding signals are generated internally in the modules having the alternate function.

Table 11-2. Generic Description of Overriding Signals for Alternate Functions

| Signal Name            | Full Name                                                                                                                                                                 | Description                                                                                                                                                                                                                                                                          |  |  |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PUOE                   | Pull-up Override<br>Enable                                                                                                                                                | If this signal is set, the pull-up enable is controlled by the PUOV signal. If this signal is cleared, the pull-up is enabled when {DDxn, PORTxn, PUD} = 0b010.                                                                                                                      |  |  |  |  |

| PUOV                   | Pull-up Override Value  If PUOE is set, the pull-up is enabled/disabled whe set/cleared, regardless of the setting of the DDxn, and PUD Register bits.                    |                                                                                                                                                                                                                                                                                      |  |  |  |  |

| DDOE                   | Data Direction<br>Override Enable                                                                                                                                         | If this signal is set, the Output Driver Enable is controlled by the DDOV signal. If this signal is cleared, the Output driver is enabled by the DDxn Register bit.                                                                                                                  |  |  |  |  |

| DDOV                   | DDOV  Data Direction Override Value  Double If DDOE is set, the Output Driver is enabled/disabled v DDOV is set/cleared, regardless of the setting of the D Register bit. |                                                                                                                                                                                                                                                                                      |  |  |  |  |

| PVOE                   | Port Value<br>Override Enable                                                                                                                                             | If this signal is set and the Output Driver is enabled, the port value is controlled by the PVOV signal. If PVOE is cleared, and the Output Driver is enabled, the port Value is controlled by the PORTxn Register bit.                                                              |  |  |  |  |

| PVOV                   | Port Value<br>Override Value                                                                                                                                              | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                              |  |  |  |  |

| PTOE                   | Port Toggle<br>Override Enable                                                                                                                                            | If PTOE is set, the PORTxn Register bit is inverted.                                                                                                                                                                                                                                 |  |  |  |  |

| DIEOE                  | Digital Input<br>Enable Override<br>Enable                                                                                                                                | If this bit is set, the Digital Input Enable is controlled by the DIEOV signal. If this signal is cleared, the Digital Input Enable is determined by MCU state (Normal mode, sleep mode).                                                                                            |  |  |  |  |

| DIEOV                  | Digital Input<br>Enable Override<br>Value                                                                                                                                 | If DIEOE is set, the Digital Input is enabled/disabled when DIEOV is set/cleared, regardless of the MCU state (Normal mode, sleep mode).                                                                                                                                             |  |  |  |  |

| DI                     | Digital Input                                                                                                                                                             | This is the Digital Input to alternate functions. In the figure, the signal is connected to the output of the schmitt trigger but before the synchronizer. Unless the Digital Input is used as a clock source, the module with the alternate function will use its own synchronizer. |  |  |  |  |

| AlO Analog signal is c |                                                                                                                                                                           | nis is the Analog Input/output to/from alternate functions. The gnal is connected directly to the pad, and can be used birectionally.                                                                                                                                                |  |  |  |  |

The following subsections shortly describe the alternate functions for each port, and relate the overriding signals to the alternate function. Refer to the alternate function description for further details.

**OCnx**

according to operating mode set by the WGM22:0 bits and Compare Output mode (COM2x1:0) bits. The max and bottom signals are used by the Waveform Generator for handling the special cases of the extreme values in some modes of operation ("Modes of Operation" on page 144).

Figure 13-10 on page 130 shows a block diagram of the Output Compare unit.

OCRnx

TCNTn

= (8-bit Comparator )

OCFnx (Int.Req.)

Waveform Generator

WGMn1:0

Figure 14-3. Output Compare Unit, Block Diagram

top bottom

**FOCn**

The OCR2x Register is double buffered when using any of the Pulse Width Modulation (PWM) modes. For the Normal and Clear Timer on Compare (CTC) modes of operation, the double buffering is disabled. The double buffering synchronizes the update of the OCR2x Compare Register to either top or bottom of the counting sequence. The synchronization prevents the occurrence of odd-length, non-symmetrical PWM pulses, thereby making the output glitch-free.

COMnX1:0

The OCR2x Register access may seem complex, but this is not case. When the double buffering is enabled, the CPU has access to the OCR2x Buffer Register, and if double buffering is disabled the CPU will access the OCR2x directly.

#### 14.5.1 Force Output Compare

In non-PWM waveform generation modes, the match output of the comparator can be forced by writing a one to the Force Output Compare (FOC2x) bit. Forcing compare match will not set the OCF2x Flag or reload/clear the timer, but the OC2x pin will be updated as if a real compare match had occurred (the COM2x1:0 bits settings define whether the OC2x pin is set, cleared or toggled).

#### 14.5.2 Compare Match Blocking by TCNT2 Write

All CPU write operations to the TCNT2 Register will block any compare match that occurs in the next timer clock cycle, even when the timer is stopped. This feature allows OCR2x to be initialized to the same value as TCNT2 without triggering an interrupt when the Timer/Counter clock is enabled.

for power regulation, rectification, and DAC applications. High frequency allows physically small sized external components (coils, capacitors), and therefore reduces total system cost.

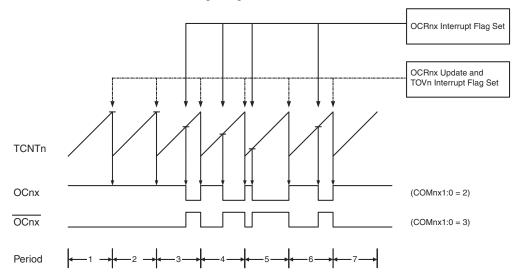

In fast PWM mode, the counter is incremented until the counter value matches the TOP value. The counter is then cleared at the following timer clock cycle. The timing diagram for the fast PWM mode is shown in Figure 14-6 on page 146. The TCNT2 value is in the timing diagram shown as a histogram for illustrating the single-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT2 slopes represent compare matches between OCR2x and TCNT2.

Figure 14-6. Fast PWM Mode, Timing Diagram

The Timer/Counter Overflow Flag (TOV2) is set each time the counter reaches TOP. If the interrupt is enabled, the interrupt handler routine can be used for updating the compare value.

In fast PWM mode, the compare unit allows generation of PWM waveforms on the OC2x pin. Setting the COM2x1:0 bits to two will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COM2x1:0 to three. TOP is defined as 0xFF when WGM2:0 = 3, and OCR2A when WGM2:0 = 7 (See Table 14-3 on page 153). The actual OC2x value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by setting (or clearing) the OC2x Register at the compare match between OCR2x and TCNT2, and clearing (or setting) the OC2x Register at the timer clock cycle the counter is cleared (changes from TOP to BOTTOM).

The PWM frequency for the output can be calculated by the following equation:

$$f_{OCnxPWM} = \frac{f_{\text{clk\_I/O}}}{N \cdot 256}$$

The N variable represents the prescale factor (1, 8, 32, 64, 128, 256, or 1024).

The extreme values for the OCR2A Register represent special cases when generating a PWM waveform output in the fast PWM mode. If the OCR2A is set equal to BOTTOM, the output will be a narrow spike for each MAX+1 timer clock cycle. Setting the OCR2A equal to MAX will result in a constantly high or low output (depending on the polarity of the output set by the COM2A1:0 bits.)

The interconnection between Master and Slave CPUs with SPI is shown in Figure 15-2. The system consists of two shift Registers, and a Master clock generator. The SPI Master initiates the communication cycle when pulling low the Slave Select  $\overline{SS}$  pin of the desired Slave. Master and Slave prepare the data to be sent in their respective shift Registers, and the Master generates the required clock pulses on the SCK line to interchange data. Data is always shifted from Master to Slave on the Master Out – Slave In, MOSI, line, and from Slave to Master on the Master In – Slave Out, MISO, line. After each data packet, the Master will synchronize the Slave by pulling high the Slave Select,  $\overline{SS}$ , line.

When configured as a Master, the SPI interface has no automatic control of the  $\overline{SS}$  line. This must be handled by user software before communication can start. When this is done, writing a byte to the SPI Data Register starts the SPI clock generator, and the hardware shifts the eight bits into the Slave. After shifting one byte, the SPI clock generator stops, setting the end of Transmission Flag (SPIF). If the SPI Interrupt Enable bit (SPIE) in the SPCR Register is set, an interrupt is requested. The Master may continue to shift the next byte by writing it into SPDR, or signal the end of packet by pulling high the Slave Select,  $\overline{SS}$  line. The last incoming byte will be kept in the Buffer Register for later use.

When configured as a Slave, the SPI interface will remain sleeping with MISO tri-stated as long as the  $\overline{SS}$  pin is driven high. In this state, software may update the contents of the SPI Data Register, SPDR, but the data will not be shifted out by incoming clock pulses on the SCK pin until the  $\overline{SS}$  pin is driven low. As one byte has been completely shifted, the end of Transmission Flag, SPIF is set. If the SPI Interrupt Enable bit, SPIE, in the SPCR Register is set, an interrupt is requested. The Slave may continue to place new data to be sent into SPDR before reading the incoming data. The last incoming byte will be kept in the Buffer Register for later use.

**MSB MASTER** MSB SI AVE LSB MISO MISO 8 BIT SHIFT REGISTER 8 BIT SHIFT REGISTER MOSI MOSI SHIFT **ENABLE** SPI SCK SCK CLOCK GENERATOR SS SS

**Figure 15-2.** SPI Master-slave Interconnection

The system is single buffered in the transmit direction and double buffered in the receive direction. This means that bytes to be transmitted cannot be written to the SPI Data Register before the entire shift cycle is completed. When receiving data, however, a received character must be read from the SPI Data Register before the next character has been completely shifted in. Otherwise, the first byte is lost.

In SPI Slave mode, the control logic will sample the incoming signal of the SCK pin. To ensure correct sampling of the clock signal, the minimum low and high periods should be:

Low period: longer than 2 CPU clock cycles.

High period: longer than 2 CPU clock cycles.

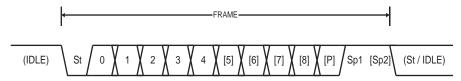

Figure 16-4. Frame Formats

St Start bit, always low.

(n) Data bits (0 to 8).

Parity bit. Can be odd or even.

**Sp** Stop bit, always high.

**IDLE** No transfers on the communication line (RxDn or TxDn). An IDLE line

must be high.

The frame format used by the USART is set by the UCSZn2:0, UPMn1:0 and USBSn bits in UCSRnB and UCSRnC. The Receiver and Transmitter use the same setting. Note that changing the setting of any of these bits will corrupt all ongoing communication for both the Receiver and Transmitter.

The USART Character SiZe (UCSZn2:0) bits select the number of data bits in the frame. The USART Parity mode (UPMn1:0) bits enable and set the type of parity bit. The selection between one or two stop bits is done by the USART Stop Bit Select (USBSn) bit. The Receiver ignores the second stop bit. An FE (Frame Error) will therefore only be detected in the cases where the first stop bit is zero.

## 16.5.1 Parity Bit Calculation

The parity bit is calculated by doing an exclusive-or of all the data bits. If odd parity is used, the result of the exclusive or is inverted. The relation between the parity bit and data bits is as follows::

$$\begin{array}{l} P_{even} = \, d_{n-1} \oplus \ldots \oplus d_3 \oplus d_2 \oplus d_1 \oplus d_0 \oplus 0 \\ P_{odd} = \, d_{n-1} \oplus \ldots \oplus d_3 \oplus d_2 \oplus d_1 \oplus d_0 \oplus 1 \end{array}$$

Peven Parity bit using even parity

Podd Parity bit using odd parity

Data bit n of the character

If used, the parity bit is located between the last data bit and first stop bit of a serial frame.

#### 16.6 USART Initialization

The USART has to be initialized before any communication can take place. The initialization process normally consists of setting the baud rate, setting frame format and enabling the Transmitter or the Receiver depending on the usage. For interrupt driven USART operation, the Global Interrupt Flag should be cleared and the USART interrupts should be disabled.

Before doing a re-initialization with changed baud rate or frame format, be sure that there are no ongoing transmissions during the period the registers are changed. The TXCn Flag can be used to check that the Transmitter has completed all transfers, and the RXC Flag can be used to

### • Bits 5:4 - UPMn1:0: Parity Mode

These bits enable and set type of parity generation and check. If enabled, the Transmitter will automatically generate and send the parity of the transmitted data bits within each frame. The Receiver will generate a parity value for the incoming data and compare it to the UPMn setting. If a mismatch is detected, the UPEn Flag in UCSRnA will be set.

Table 16-5. UPMn Bits Settings

| UPMn1 | UPMn0 | Parity Mode          |  |  |

|-------|-------|----------------------|--|--|

| 0     | 0     | Disabled             |  |  |

| 0     | 1     | Reserved             |  |  |

| 1     | 0     | Enabled, Even Parity |  |  |

| 1     | 1     | Enabled, Odd Parity  |  |  |

## • Bit 3 – USBSn: Stop Bit Select

This bit selects the number of stop bits to be inserted by the Transmitter. The Receiver ignores this setting.

Table 16-6. USBS Bit Settings

| USBSn | Stop Bit(s) |

|-------|-------------|

| 0     | 1-bit       |

| 1     | 2-bit       |

## • Bit 2:1 - UCSZn1:0: Character Size

The UCSZn1:0 bits combined with the UCSZn2 bit in UCSRnB sets the number of data bits (Character SiZe) in a frame the Receiver and Transmitter use.

Table 16-7. UCSZn Bits Settings

| UCSZn2 | UCSZn1 | UCSZn0  | Character Size |  |

|--------|--------|---------|----------------|--|

| 0      | 0      | 0       | 5-bit          |  |

| 0      | 0      | 1 6-bit |                |  |

| 0      | 1      | 0       | 7-bit          |  |

| 0      | 1      | 1       | 8-bit          |  |

| 1      | 0      | 0       | Reserved       |  |

| 1      | 0      | 1       | Reserved       |  |

| 1      | 1      | 0       | Reserved       |  |

| 1      | 1      | 1       | 9-bit          |  |

Table 16-10. Examples of UBRRn Settings for Commonly Used Oscillator Frequencies (Continued)

|              | f <sub>osc</sub> = 3.6864 MHz  |       |          | f <sub>osc</sub> = 4.0000 MHz |            |       |            | f <sub>osc</sub> = 7.3728 MHz |          |       |          |       |

|--------------|--------------------------------|-------|----------|-------------------------------|------------|-------|------------|-------------------------------|----------|-------|----------|-------|

| Baud<br>Rate | U2Xn = 0                       |       | U2Xn = 1 |                               | U2Xn = 0   |       | U2Xn = 1   |                               | U2Xn = 0 |       | U2Xn = 1 |       |

| (bps)        | UBRR                           | Error | UBRR     | Error                         | UBRR       | Error | UBRR       | Error                         | UBRR     | Error | UBRR     | Error |

| 2400         | 95                             | 0.0%  | 191      | 0.0%                          | 103        | 0.2%  | 207        | 0.2%                          | 191      | 0.0%  | 383      | 0.0%  |

| 4800         | 47                             | 0.0%  | 95       | 0.0%                          | 51         | 0.2%  | 103        | 0.2%                          | 95       | 0.0%  | 191      | 0.0%  |

| 9600         | 23                             | 0.0%  | 47       | 0.0%                          | 25         | 0.2%  | 51         | 0.2%                          | 47       | 0.0%  | 95       | 0.0%  |

| 14.4k        | 15                             | 0.0%  | 31       | 0.0%                          | 16         | 2.1%  | 34         | -0.8%                         | 31       | 0.0%  | 63       | 0.0%  |

| 19.2k        | 11                             | 0.0%  | 23       | 0.0%                          | 12         | 0.2%  | 25         | 0.2%                          | 23       | 0.0%  | 47       | 0.0%  |

| 28.8k        | 7                              | 0.0%  | 15       | 0.0%                          | 8          | -3.5% | 16         | 2.1%                          | 15       | 0.0%  | 31       | 0.0%  |

| 38.4k        | 5                              | 0.0%  | 11       | 0.0%                          | 6          | -7.0% | 12         | 0.2%                          | 11       | 0.0%  | 23       | 0.0%  |

| 57.6k        | 3                              | 0.0%  | 7        | 0.0%                          | 3          | 8.5%  | 8          | -3.5%                         | 7        | 0.0%  | 15       | 0.0%  |

| 76.8k        | 2                              | 0.0%  | 5        | 0.0%                          | 2          | 8.5%  | 6          | -7.0%                         | 5        | 0.0%  | 11       | 0.0%  |

| 115.2k       | 1                              | 0.0%  | 3        | 0.0%                          | 1          | 8.5%  | 3          | 8.5%                          | 3        | 0.0%  | 7        | 0.0%  |

| 230.4k       | 0                              | 0.0%  | 1        | 0.0%                          | 0          | 8.5%  | 1          | 8.5%                          | 1        | 0.0%  | 3        | 0.0%  |

| 250k         | 0                              | -7.8% | 1        | -7.8%                         | 0          | 0.0%  | 1          | 0.0%                          | 1        | -7.8% | 3        | -7.8% |

| 0.5M         | _                              | _     | 0        | -7.8%                         | _          | _     | 0          | 0.0%                          | 0        | -7.8% | 1        | -7.8% |

| 1M           | _                              | _     | _        | _                             | _          | _     | _          | _                             | _        | _     | 0        | -7.8% |

| Max. (1)     | 230.4 kbps 460.8 kbps 250 kbps |       | 0.5 Mbps |                               | 460.8 kbps |       | 921.6 kbps |                               |          |       |          |       |

<sup>1.</sup> UBRR = 0, Error = 0.0%

|   | Assembly Code Example                                                                                                                                                                                       | C Example                                                                                            | Comments                                                                                                           |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| 6 | wait3: in r16,TWCR sbrs r16,TWINT rjmp wait3                                                                                                                                                                | <pre>while (!(TWCR &amp; (1&lt;<twint))) ;<="" pre=""></twint)))></pre>                              | Wait for TWINT Flag set. This indicates that the DATA has been transmitted, and ACK/NACK has been received.        |

| 7 | <pre>in r16,TWSR andi r16, 0xF8 cpi r16, MT_DATA_ACK brne ERROR</pre>                                                                                                                                       | <pre>if ((TWSR &amp; 0xF8) != MT_DATA_ACK) ERROR();</pre>                                            | Check value of TWI Status<br>Register. Mask prescaler bits. If<br>status different from<br>MT_DATA_ACK go to ERROR |

|   | ldi r16, (1< <twint) (1<<twen)="" (1<<twsto)="" out="" r16<="" th="" twcr,=""  =""><th>TWCR = (1&lt;<twint) (1<<twen)="" (1<<twsto);<="" th=""  =""><th>Transmit STOP condition</th></twint)></th></twint)> | TWCR = (1< <twint) (1<<twen)="" (1<<twsto);<="" th=""  =""><th>Transmit STOP condition</th></twint)> | Transmit STOP condition                                                                                            |

### 18.7 Transmission Modes

The TWI can operate in one of four major modes. These are named Master Transmitter (MT), Master Receiver (MR), Slave Transmitter (ST) and Slave Receiver (SR). Several of these modes can be used in the same application. As an example, the TWI can use MT mode to write data into a TWI EEPROM, MR mode to read the data back from the EEPROM. If other masters are present in the system, some of these might transmit data to the TWI, and then SR mode would be used. It is the application software that decides which modes are legal.

The following sections describe each of these modes. Possible status codes are described along with figures detailing data transmission in each of the modes. These figures contain the following abbreviations:

S: START condition

Rs: REPEATED START condition

R: Read bit (high level at SDA)

W: Write bit (low level at SDA)

A: Acknowledge bit (low level at SDA)

A: Not acknowledge bit (high level at SDA)

Data: 8-bit data byte P: STOP condition

SLA: Slave Address

In Figure 18-12 on page 221 to Figure 18-18 on page 230, circles are used to indicate that the TWINT Flag is set. The numbers in the circles show the status code held in TWSR, with the prescaler bits masked to zero. At these points, actions must be taken by the application to continue or complete the TWI transfer. The TWI transfer is suspended until the TWINT Flag is cleared by software.

When the TWINT Flag is set, the status code in TWSR is used to determine the appropriate software action. For each status code, the required software action and details of the following serial transfer are given in Table 18-2 on page 220 to Table 18-5 on page 229. Note that the prescaler bits are masked to zero in these tables.

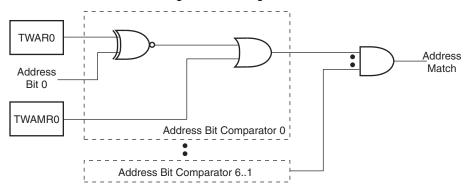

Figure 18-22. TWI Address Match Logic, Block Diagram

#### • Bit 0 - Res: Reserved Bit

This bit is reserved and will always read as zero.

#### 24.7.12 Reading the Fuse and Lock Bits

The algorithm for reading the Fuse and Lock bits is as follows (refer to "Programming the Flash" on page 300 for details on Command loading):

- 1. A: Load Command "0000 0100".

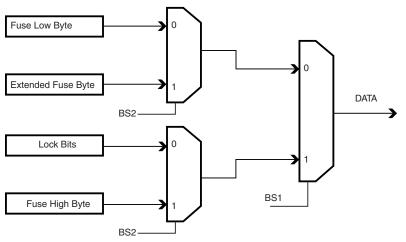

- 2. Set  $\overline{\text{OE}}$  to "0", and BS2, BS1 to "00". The status of the Fuse Low bits can now be read at DATA ("0" means programmed).

- 3. Set  $\overline{\text{OE}}$  to "0", and BS2, BS1 to "11". The status of the Fuse High bits can now be read at DATA ("0" means programmed).

- 4. Set OE to "0", and BS2, BS1 to "10". The status of the Extended Fuse bits can now be read at DATA ("0" means programmed).

- 5. Set  $\overline{\text{OE}}$  to "0", and BS2, BS1 to "01". The status of the Lock bits can now be read at DATA ("0" means programmed).

- 6. Set OE to "1".

Figure 24-6. Mapping Between BS1, BS2 and the Fuse and Lock Bits During Read

#### 24.7.13 Reading the Signature Bytes

The algorithm for reading the Signature bytes is as follows (refer to "Programming the Flash" on page 300 for details on Command and Address loading):

- 1. A: Load Command "0000 1000".

- 2. B: Load Address Low Byte (0x00 0x02).

- Set OE to "0", and BS to "0". The selected Signature byte can now be read at DATA.

- 4. Set  $\overline{OE}$  to "1".

## 24.7.14 Reading the Calibration Byte

The algorithm for reading the Calibration byte is as follows (refer to "Programming the Flash" on page 300 for details on Command and Address loading):

- 1. A: Load Command "0000 1000".

- 2. B: Load Address Low Byte, 0x00.

- 3. Set  $\overline{OE}$  to "0", and BS1 to "1". The Calibration byte can now be read at DATA.

- 4. Set  $\overline{OE}$  to "1".

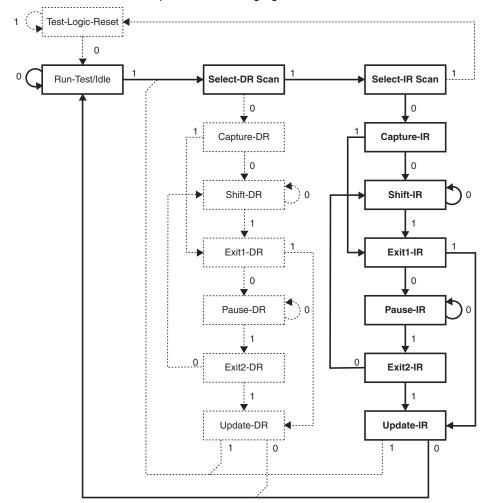

Figure 24-13. State Machine Sequence for Changing the Instruction Word

## 24.10.2 AVR\_RESET (0xC)

The AVR specific public JTAG instruction for setting the AVR device in the Reset mode or taking the device out from the Reset mode. The TAP controller is not reset by this instruction. The one bit Reset Register is selected as Data Register. Note that the reset will be active as long as there is a logic "one" in the Reset Chain. The output from this chain is not latched.

The active states are:

• Shift-DR: The Reset Register is shifted by the TCK input.

#### 24.10.3 PROG ENABLE (0x4)

The AVR specific public JTAG instruction for enabling programming via the JTAG port. The 16-bit Programming Enable Register is selected as Data Register. The active states are the following:

- Shift-DR: The programming enable signature is shifted into the Data Register.

- Update-DR: The programming enable signature is compared to the correct value, and Programming mode is entered if the signature is valid.

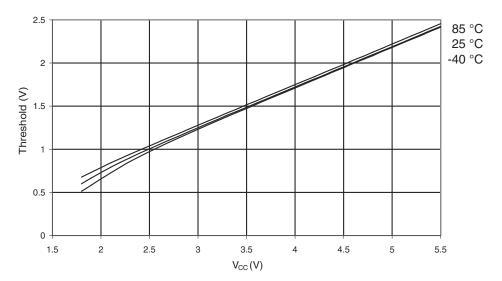

Figure 26-26. I/O Pin Input Threshold Voltage vs.  $V_{CC}$  ( $V_{IL}$ , I/O Pin Read as '0').

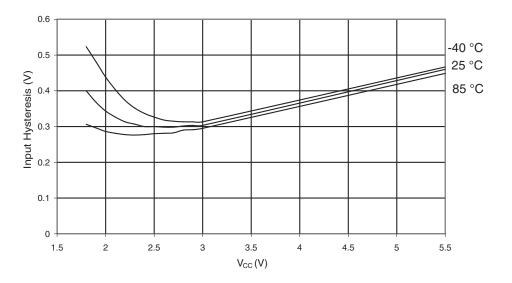

Figure 26-27. I/O Pin Input Hysteresis vs.  $V_{CC}$ .

# 26.3.7 Pin Pull-up

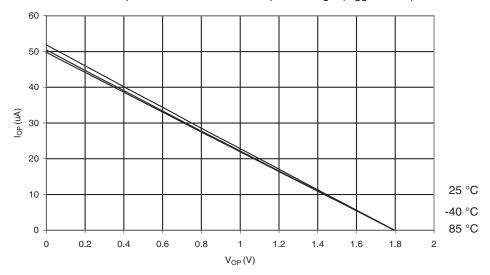

Figure 26-109.I/O Pin Pull-up Resistor Current vs. Input Voltage ( $V_{CC} = 1.8V$ ).

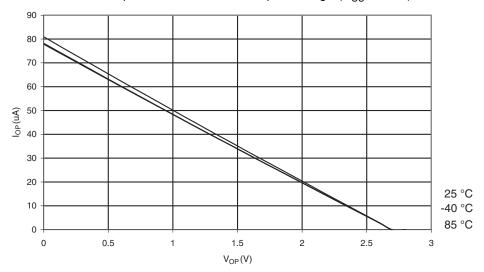

Figure 26-110.I/O Pin Pull-up Resistor Current vs. Input Voltage ( $V_{CC} = 2.7V$ ).

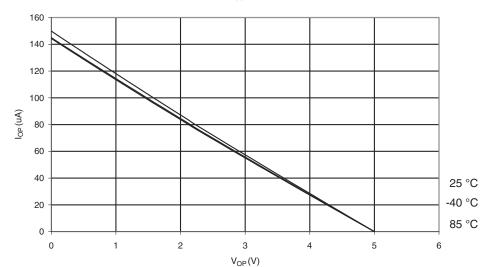

Figure 26-111.I/O Pin Pull-up Resistor Current vs. Input Voltage ( $V_{CC} = 5V$ ).

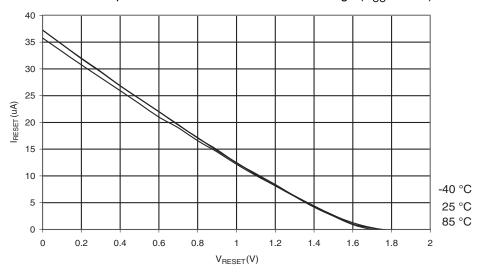

**Figure 26-112.**Reset Pull-up Resistor Current vs. Reset Pin Voltage ( $V_{CC} = 1.8V$ ).