Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega644p-20aur |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 5.6 Register Description

# 5.6.1 EEARH and EEARL – The EEPROM Address Register

| Bit           | 15    | 14    | 13    | 12    | 11     | 10     | 9     | 8     | _     |

|---------------|-------|-------|-------|-------|--------|--------|-------|-------|-------|

| 0x22 (0x42)   | -     | -     | -     | -     | EEAR11 | EEAR10 | EEAR9 | EEAR8 | EEARH |

| 0x21 (0x41)   | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3  | EEAR2  | EEAR1 | EEAR0 | EEARL |

|               | 7     | 6     | 5     | 4     | 3      | 2      | 1     | 0     |       |

| Read/Write    | R     | R     | R     | R     | R/W    | R/W    | R/W   | R/W   |       |

|               | R/W   | R/W   | R/W   | R/W   | R/W    | R/W    | R/W   | R/W   |       |

| Initial Value | 0     | 0     | 0     | 0     | Х      | Х      | Х     | Х     |       |

|               | Х     | Х     | Х     | х     | Х      | Х      | Х     | Х     |       |

### • Bits 15:12 - Res: Reserved Bits

These bits are reserved bits in the ATmega164P/324P/644P and will always read as zero.

### • Bits 11:0 – EEAR8:0: EEPROM Address

The EEPROM Address Registers – EEARH and EEARL specify the EEPROM address in the 4K bytes EEPROM space. The EEPROM data bytes are addressed linearly between 0 and 4096. The initial value of EEAR is undefined. A proper value must be written before the EEPROM may be accessed.

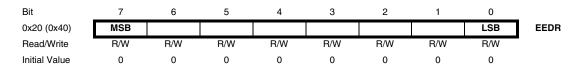

# 5.6.2 EEDR – The EEPROM Data Register

# Bits 7:0 – EEDR7:0: EEPROM Data

For the EEPROM write operation, the EEDR Register contains the data to be written to the EEPROM in the address given by the EEAR Register. For the EEPROM read operation, the EEDR contains the data read out from the EEPROM at the address given by EEAR.

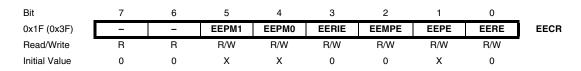

# 5.6.3 EECR – The EEPROM Control Register

### Bits 7:6 – Res: Reserved Bits

These bits are reserved bits in the ATmega164P/324P/644P and will always read as zero.

### • Bits 5:4 – EEPM1 and EEPM0: EEPROM Programming Mode Bits

The EEPROM Programming mode bit setting defines which programming action that will be triggered when writing EEPE. It is possible to program data in one atomic operation (erase the old value and program the new value) or to split the Erase and Write operations in two different operations. The Programming times for the different modes are shown in Table 5-1 on page 24.

# 6.1.3 Flash Clock – clk<sub>FLASH</sub>

The Flash clock controls operation of the Flash interface. The Flash clock is usually active simultaneously with the CPU clock.

# 6.1.4 Asynchronous Timer Clock – clk<sub>ASY</sub>

The Asynchronous Timer clock allows the Asynchronous Timer/Counter to be clocked directly from an external clock or an external 32 kHz clock crystal. The dedicated clock domain allows using this Timer/Counter as a real-time counter even when the device is in sleep mode.

# 6.1.5 ADC Clock – clk<sub>ADC</sub>

The ADC is provided with a dedicated clock domain. This allows halting the CPU and I/O clocks in order to reduce noise generated by digital circuitry. This gives more accurate ADC conversion results.

# 6.2 Clock Sources

The device has the following clock source options, selectable by Flash Fuse bits as shown below. The clock from the selected source is input to the AVR clock generator, and routed to the appropriate modules.

| Device Clocking Option            | CKSEL30     |

|-----------------------------------|-------------|

| Low Power Crystal Oscillator      | 1111 - 1000 |

| Full Swing Crystal Oscillator     | 0111 - 0110 |

| Low Frequency Crystal Oscillator  | 0101 - 0100 |

| Internal 128 kHz RC Oscillator    | 0011        |

| Calibrated Internal RC Oscillator | 0010        |

| External Clock                    | 0000        |

| Reserved                          | 0001        |

Table 6-1.

Device Clocking Options Select<sup>(1)</sup>

Note: 1. For all fuses "1" means unprogrammed while "0" means programmed.

### 6.2.1 Default Clock Source

The device is shipped with internal RC oscillator at 8.0MHz and with the fuse CKDIV8 programmed, resulting in 1.0MHz system clock. The startup time is set to maximum and time-out period enabled. (CKSEL = "0010", SUT = "10", CKDIV8 = "0"). The default setting ensures that all users can make their desired clock source setting using any available programming interface.

### 6.2.2 Clock Startup Sequence

Any clock source needs a sufficient  $V_{CC}$  to start oscillating and a minimum number of oscillating cycles before it can be considered stable.

To ensure sufficient  $V_{CC}$ , the device issues an internal reset with a time-out delay ( $t_{TOUT}$ ) after the device reset is released by all other reset sources. "On-chip Debug System" on page 46 describes the start conditions for the internal reset. The delay ( $t_{TOUT}$ ) is timed from the Watchdog Oscillator and the number of cycles in the delay is set by the SUTx and CKSELx fuse bits. The

# 6.3 Low Power Crystal Oscillator

This Crystal Oscillator is a low power oscillator, with reduced voltage swing on the XTAL2 output. It gives the lowest power consumption, but is not capable of driving other clock inputs, and may be more susceptible to noise in noisy environments. In these cases, refer to the "Full Swing Crystal Oscillator" on page 33.

Some initial guidelines for choosing capacitors for use with crystals are given in Table 6-3. The crystal should be connected as described in "Clock Source Connections" on page 31.

The Low Power Oscillator can operate in three different modes, each optimized for a specific frequency range. The operating mode is selected by the fuses CKSEL3..1 as shown in Table 6-3.

| Frequency Range (MHz) | CKSEL31 <sup>(2)</sup> | Recommended Range for Capacitors C1<br>and C2 (pF) |

|-----------------------|------------------------|----------------------------------------------------|

| 0.4 - 0.9             | 100 <sup>(3)</sup>     | _                                                  |

| 0.9 - 3.0             | 101                    | 12 - 22                                            |

| 3.0 - 8.0             | 110                    | 12 - 22                                            |

| 8.0 - 16.0            | 111                    | 12 - 22                                            |

Table 6-3.

Low Power Crystal Oscillator Operating Modes<sup>(1)</sup>

Notes: 1. If 8 MHz frequency exceeds the specification of the device (depends on V<sub>CC</sub>), the CKDIV8 Fuse can be programmed in order to divide the internal frequency by 8. It must be ensured that the resulting divided clock meets the frequency specification of the device.

- 2. This is the recommended CKSEL settings for the different frequency ranges.

- 3. This option should not be used with crystals, only with ceramic resonators.

The CKSEL0 Fuse together with the SUT1..0 Fuses select the start-up times as shown in Table 6-4.

Table 6-4.

Start-up Times for the Low Power Crystal Oscillator Clock Selection

Start-up Time from

Additional Delay

| Oscillator Source /<br>Power Conditions | Start-up Time from<br>Power-down and<br>Power-save | Additional Delay<br>from Reset<br>(V <sub>CC</sub> = 5.0V) | CKSEL0 | SUT10 |

|-----------------------------------------|----------------------------------------------------|------------------------------------------------------------|--------|-------|

| Ceramic resonator, fast rising power    | 258 CK                                             | 14CK + 4.1 ms <sup>(1)</sup>                               | 0      | 00    |

| Ceramic resonator, slowly rising power  | 258 CK                                             | 14CK + 65 ms <sup>(1)</sup>                                | 0      | 01    |

| Ceramic resonator, BOD enabled          | 1K CK                                              | 14CK <sup>(2)</sup>                                        | 0      | 10    |

| Ceramic resonator, fast rising power    | 1K CK                                              | 14CK + 4.1 ms <sup>(2)</sup>                               | 0      | 11    |

| Ceramic resonator, slowly rising power  | 1K CK                                              | 14CK + 65 ms <sup>(2)</sup>                                | 1      | 00    |

# 12.6.1 Compare Output Mode and Waveform Generation

The Waveform Generator uses the COM0x1:0 bits differently in Normal, CTC, and PWM modes. For all modes, setting the COM0x1:0 = 0 tells the Waveform Generator that no action on the OC0x Register is to be performed on the next Compare Match. For compare output actions in the non-PWM modes refer to Table 12-2 on page 104. For fast PWM mode, refer to Table 12-3 on page 104, and for phase correct PWM refer to Table 12-4 on page 105.

A change of the COM0x1:0 bits state will have effect at the first Compare Match after the bits are written. For non-PWM modes, the action can be forced to have immediate effect by using the FOC0x strobe bits.

# 12.7 Modes of Operation

The mode of operation, i.e., the behavior of the Timer/Counter and the Output Compare pins, is defined by the combination of the Waveform Generation mode (WGM02:0) and Compare Output mode (COM0x1:0) bits. The Compare Output mode bits do not affect the counting sequence, while the Waveform Generation mode bits do. The COM0x1:0 bits control whether the PWM output generated should be inverted or not (inverted or non-inverted PWM). For non-PWM modes the COM0x1:0 bits control whether the output should be set, cleared, or toggled at a Compare Match (See Section "13.8" on page 122.).

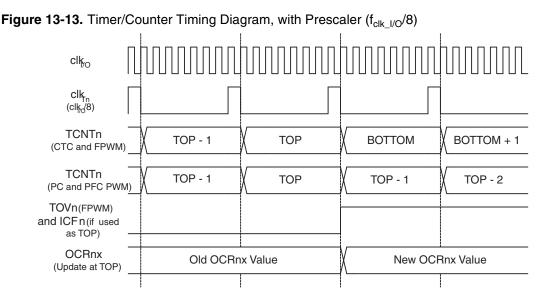

For detailed timing information see "Timer/Counter Timing Diagrams" on page 102.

# 12.7.1 Normal Mode

The simplest mode of operation is the Normal mode (WGM02:0 = 0). In this mode the counting direction is always up (incrementing), and no counter clear is performed. The counter simply overruns when it passes its maximum 8-bit value (TOP = 0xFF) and then restarts from the bottom (0x00). In normal operation the Timer/Counter Overflow Flag (TOV0) will be set in the same timer clock cycle as the TCNT0 becomes zero. The TOV0 Flag in this case behaves like a ninth bit, except that it is only set, not cleared. However, combined with the timer overflow interrupt that automatically clears the TOV0 Flag, the timer resolution can be increased by software. There are no special cases to consider in the Normal mode, a new counter value can be written anytime.

The Output Compare Unit can be used to generate interrupts at some given time. Using the Output Compare to generate waveforms in Normal mode is not recommended, since this will occupy too much of the CPU time.

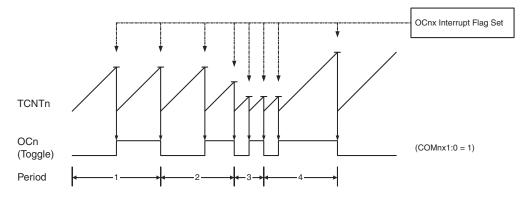

# 12.7.2 Clear Timer on Compare Match (CTC) Mode

In Clear Timer on Compare or CTC mode (WGM02:0 = 2), the OCR0A Register is used to manipulate the counter resolution. In CTC mode the counter is cleared to zero when the counter value (TCNT0) matches the OCR0A. The OCR0A defines the top value for the counter, hence also its resolution. This mode allows greater control of the Compare Match output frequency. It also simplifies the operation of counting external events.

The timing diagram for the CTC mode is shown in Figure 12-5. The counter value (TCNT0) increases until a Compare Match occurs between TCNT0 and OCR0A, and then counter (TCNT0) is cleared.

Figure 12-5. CTC Mode, Timing Diagram

An interrupt can be generated each time the counter value reaches the TOP value by using the OCF0A Flag. If the interrupt is enabled, the interrupt handler routine can be used for updating the TOP value. However, changing TOP to a value close to BOTTOM when the counter is running with none or a low prescaler value must be done with care since the CTC mode does not have the double buffering feature. If the new value written to OCR0A is lower than the current value of TCNT0, the counter will miss the Compare Match. The counter will then have to count to its maximum value (0xFF) and wrap around starting at 0x00 before the Compare Match can occur.

For generating a waveform output in CTC mode, the OC0A output can be set to toggle its logical level on each Compare Match by setting the Compare Output mode bits to toggle mode (COM0A1:0 = 1). The OC0A value will not be visible on the port pin unless the data direction for the pin is set to output. The waveform generated will have a maximum frequency of  $f_{OC0} = f_{clk\_l/O}/2$  when OCR0A is set to zero (0x00). The waveform frequency is defined by the following equation:

$$f_{OCnx} = \frac{f_{\mathsf{clk\_I/O}}}{2 \cdot N \cdot (1 + OCRnx)}$$

The N variable represents the prescale factor (1, 8, 64, 256, or 1024).

As for the Normal mode of operation, the TOV0 Flag is set in the same timer clock cycle that the counter counts from MAX to 0x00.

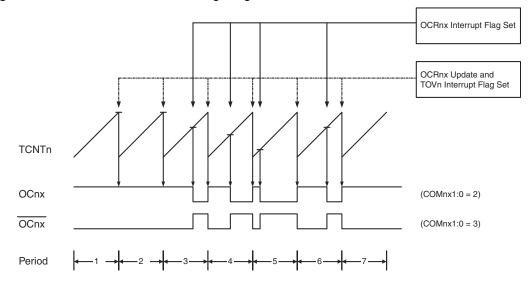

# 12.7.3 Fast PWM Mode

The fast Pulse Width Modulation or fast PWM mode (WGM02:0 = 3 or 7) provides a high frequency PWM waveform generation option. The fast PWM differs from the other PWM option by its single-slope operation. The counter counts from BOTTOM to TOP then restarts from BOT-TOM. TOP is defined as 0xFF when WGM2:0 = 3, and OCR0A when WGM2:0 = 7. In noninverting Compare Output mode, the Output Compare (OC0x) is cleared on the Compare Match between TCNT0 and OCR0x, and set at BOTTOM. In inverting Compare Output mode, the output is set on Compare Match and cleared at BOTTOM. Due to the single-slope operation, the operating frequency of the fast PWM mode can be twice as high as the phase correct PWM mode that use dual-slope operation. This high frequency makes the fast PWM mode well suited for power regulation, rectification, and DAC applications. High frequency allows physically small sized external components (coils, capacitors), and therefore reduces total system cost.

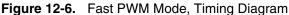

In fast PWM mode, the counter is incremented until the counter value matches the TOP value. The counter is then cleared at the following timer clock cycle. The timing diagram for the fast

PWM mode is shown in Figure 12-6. The TCNT0 value is in the timing diagram shown as a histogram for illustrating the single-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT0 slopes represent Compare Matches between OCR0x and TCNT0.

The Timer/Counter Overflow Flag (TOV0) is set each time the counter reaches TOP. If the interrupt is enabled, the interrupt handler routine can be used for updating the compare value.

In fast PWM mode, the compare unit allows generation of PWM waveforms on the OC0x pins. Setting the COM0x1:0 bits to two will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COM0x1:0 to three: Setting the COM0A1:0 bits to one allows the OC0A pin to toggle on Compare Matches if the WGM02 bit is set. This option is not available for the OC0B pin (See Table 12-3 on page 104). The actual OC0x value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by setting (or clearing) the OC0x Register at the Compare Match between OCR0x and TCNT0, and clearing (or setting) the OC0x Register at the timer clock cycle the counter is cleared (changes from TOP to BOTTOM).

The PWM frequency for the output can be calculated by the following equation:

$$f_{OCnxPWM} = \frac{f_{clk\_l/O}}{N \cdot 256}$$

The *N* variable represents the prescale factor (1, 8, 64, 256, or 1024).

The extreme values for the OCR0A Register represents special cases when generating a PWM waveform output in the fast PWM mode. If the OCR0A is set equal to BOTTOM, the output will be a narrow spike for each MAX+1 timer clock cycle. Setting the OCR0A equal to MAX will result in a constantly high or low output (depending on the polarity of the output set by the COM0A1:0 bits.)

A frequency (with 50% duty cycle) waveform output in fast PWM mode can be achieved by setting OC0x to toggle its logical level on each Compare Match (COM0x1:0 = 1). The waveform generated will have a maximum frequency of  $f_{OC0} = f_{clk}$  <sub>1/O</sub>/2 when OCR0A is set to zero. This

OCRnx Registers are written. As the third period shown in Figure 13-8 illustrates, changing the TOP actively while the Timer/Counter is running in the phase correct mode can result in an unsymmetrical output. The reason for this can be found in the time of update of the OCRnx Register. Since the OCRnx update occurs at TOP, the PWM period starts and ends at TOP. This implies that the length of the falling slope is determined by the previous TOP value, while the length of the rising slope is determined by the new TOP value. When these two values differ the two slopes of the period will differ in length. The difference in length gives the unsymmetrical result on the output.

It is recommended to use the phase and frequency correct mode instead of the phase correct mode when changing the TOP value while the Timer/Counter is running. When using a static TOP value there are practically no differences between the two modes of operation.

In phase correct PWM mode, the compare units allow generation of PWM waveforms on the OCnx pins. Setting the COMnx1:0 bits to two will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COMnx1:0 to three (See Table on page 133). The actual OCnx value will only be visible on the port pin if the data direction for the port pin is set as output (DDR\_OCnx). The PWM waveform is generated by setting (or clearing) the OCnx Register at the compare match between OCRnx and TCNTn when the counter increments, and clearing (or setting) the OCnx Register at compare match between OCRnx and TCNTn when the counter decrements. The PWM frequency for the output when using phase correct PWM can be calculated by the following equation:

$$f_{OCnxPCPWM} = \frac{f_{\mathsf{clk\_l/O}}}{2 \cdot N \cdot TOP}$$

The N variable represents the prescaler divider (1, 8, 64, 256, or 1024).

The extreme values for the OCRnx Register represent special cases when generating a PWM waveform output in the phase correct PWM mode. If the OCRnx is set equal to BOTTOM the output will be continuously low and if set equal to TOP the output will be continuously high for non-inverted PWM mode. For inverted PWM the output will have the opposite logic values. If OCR1A is used to define the TOP value (WGM13:0 = 11) and COM1A1:0 = 1, the OC1A output will toggle with a 50% duty cycle.

# 13.9.5 Phase and Frequency Correct PWM Mode

The *phase and frequency correct Pulse Width Modulation*, or phase and frequency correct PWM mode (WGMn3:0 = 8 or 9) provides a high resolution phase and frequency correct PWM waveform generation option. The phase and frequency correct PWM mode is, like the phase correct PWM mode, based on a dual-slope operation. The counter counts repeatedly from BOTTOM (0x0000) to TOP and then from TOP to BOTTOM. In non-inverting Compare Output mode, the Output Compare (OCnx) is cleared on the compare match between TCNTn and OCRnx while upcounting, and set on the compare match while downcounting. In inverting Compare Output mode, the operation is inverted. The dual-slope operation gives a lower maximum operation frequency compared to the single-slope operation. However, due to the symmetric feature of the dual-slope PWM modes, these modes are preferred for motor control applications.

The main difference between the phase correct, and the phase and frequency correct PWM mode is the time the OCRnx Register is updated by the OCRnx Buffer Register, (see Figure 13-8 and Figure 13-9).

The PWM resolution for the phase and frequency correct PWM mode can be defined by either ICRn or OCRnA. The minimum resolution allowed is 2-bit (ICRn or OCRnA set to 0x0003), and

# ATmega164P/324P/644P

13.11 Register Description

# 13.11.1 TCCR1A – Timer/Counter1 Control Register A

| Bit           | 7      | 6      | 5      | 4      | 3 | 2 | 1     | 0     | _      |

|---------------|--------|--------|--------|--------|---|---|-------|-------|--------|

| (0x80)        | COM1A1 | COM1A0 | COM1B1 | COM1B0 | - | - | WGM11 | WGM10 | TCCR1A |

| Read/Write    | R/W    | R/W    | R/W    | R/W    | R | R | R/W   | R/W   | •      |

| Initial Value | 0      | 0      | 0      | 0      | 0 | 0 | 0     | 0     |        |

# • Bit 7:6 – COMnA1:0: Compare Output Mode for Channel A

# • Bit 5:4 – COMnB1:0: Compare Output Mode for Channel B

The COMnA1:0 and COMnB1:0 control the Output Compare pins (OCnA and OCnB respectively) behavior. If one or both of the COMnA1:0 bits are written to one, the OCnA output overrides the normal port functionality of the I/O pin it is connected to. If one or both of the COMnB1:0 bit are written to one, the OCnB output overrides the normal port functionality of the I/O pin it is connected to. However, note that the *Data Direction Register* (DDR) bit corresponding to the OCnA or OCnB pin must be set in order to enable the output driver.

When the OCnA or OCnB is connected to the pin, the function of the COMnx1:0 bits is dependent of the WGMn3:0 bits setting. Table 13-2 on page 132 shows the COMnx1:0 bit functionality when the WGMn3:0 bits are set to a Normal or a CTC mode (non-PWM).

| COMnA1/COMnB1 | COMnA0/COMnB0 | Description                                                 |

|---------------|---------------|-------------------------------------------------------------|

| 0             | 0             | Normal port operation, OCnA/OCnB disconnected.              |

| 0             | 1             | Toggle OCnA/OCnB on Compare Match.                          |

| 1             | 0             | Clear OCnA/OCnB on Compare Match (Set output to low level). |

| 1             | 1             | Set OCnA/OCnB on Compare Match (Set output to high level).  |

Table 13-2.

Compare Output Mode, non-PWM

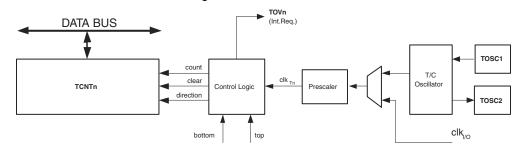

# 14.4 Counter Unit

The main part of the 8-bit Timer/Counter is the programmable bi-directional counter unit. Figure 14-2 shows a block diagram of the counter and its surrounding environment.

Figure 14-2. Counter Unit Block Diagram

Signal description (internal signals):

| count             | Increment or decrement TCNT2 by 1.                               |

|-------------------|------------------------------------------------------------------|

| direction         | Selects between increment and decrement.                         |

| clear             | Clear TCNT2 (set all bits to zero).                              |

| clk <sub>Tn</sub> | Timer/Counter clock, referred to as $clk_{T2}$ in the following. |

| top               | Signalizes that TCNT2 has reached maximum value.                 |

| bottom            | Signalizes that TCNT2 has reached minimum value (zero).          |

Depending on the mode of operation used, the counter is cleared, incremented, or decremented at each timer clock ( $clk_{T2}$ ).  $clk_{T2}$  can be generated from an external or internal clock source, selected by the Clock Select bits (CS22:0). When no clock source is selected (CS22:0 = 0) the timer is stopped. However, the TCNT2 value can be accessed by the CPU, regardless of whether  $clk_{T2}$  is present or not. A CPU write overrides (has priority over) all counter clear or count operations.

The counting sequence is determined by the setting of the WGM21 and WGM20 bits located in the Timer/Counter Control Register (TCCR2A) and the WGM22 located in the Timer/Counter Control Register B (TCCR2B). There are close connections between how the counter behaves (counts) and how waveforms are generated on the Output Compare outputs OC2A and OC2B. For more details about advanced counting sequences and waveform generation, see "Modes of Operation" on page 144.

The Timer/Counter Overflow Flag (TOV2) is set according to the mode of operation selected by the WGM22:0 bits. TOV2 can be used for generating a CPU interrupt.

# 14.5 Output Compare Unit

The 8-bit comparator continuously compares TCNT2 with the Output Compare Register (OCR2A and OCR2B). Whenever TCNT2 equals OCR2A or OCR2B, the comparator signals a match. A match will set the Output Compare Flag (OCF2A or OCF2B) at the next timer clock cycle. If the corresponding interrupt is enabled, the Output Compare Flag generates an Output Compare interrupt. The Output Compare Flag is automatically cleared when the interrupt is executed. Alternatively, the Output Compare Flag can be cleared by software by writing a logical one to its I/O bit location. The Waveform Generator uses the match signal to generate an output

# 15.3 **SS** Pin Functionality

# 15.3.1 Slave Mode

When the SPI is configured as a Slave, the Slave Select ( $\overline{SS}$ ) pin is always input. When  $\overline{SS}$  is held low, the SPI is activated, and MISO becomes an output if configured so by the user. All other pins are inputs. When  $\overline{SS}$  is driven high, all pins are inputs, and the SPI is passive, which means that it will not receive incoming data. Note that the SPI logic will be reset once the  $\overline{SS}$  pin is driven high.

The  $\overline{SS}$  pin is useful for packet/byte synchronization to keep the slave bit counter synchronous with the master clock generator. When the  $\overline{SS}$  pin is driven high, the SPI slave will immediately reset the send and receive logic, and drop any partially received data in the Shift Register.

# 15.3.2 Master Mode

When the SPI is configured as a Master (MSTR in SPCR is set), the user can determine the direction of the  $\overline{SS}$  pin.

If  $\overline{SS}$  is configured as an output, the pin is a general output pin which does not affect the SPI system. Typically, the pin will be driving the  $\overline{SS}$  pin of the SPI Slave.

If  $\overline{SS}$  is configured as an input, it must be held high to ensure Master SPI operation. If the  $\overline{SS}$  pin is driven low by peripheral circuitry when the SPI is configured as a Master with the  $\overline{SS}$  pin defined as an input, the SPI system interprets this as another master selecting the SPI as a slave and starting to send data to it. To avoid bus contention, the SPI system takes the following actions:

- 1. The MSTR bit in SPCR is cleared and the SPI system becomes a Slave. As a result of the SPI becoming a Slave, the MOSI and SCK pins become inputs.

- 2. The SPIF Flag in SPSR is set, and if the SPI interrupt is enabled, and the I-bit in SREG is set, the interrupt routine will be executed.

Thus, when interrupt-driven SPI transmission is used in Master mode, and there exists a possibility that  $\overline{SS}$  is driven low, the interrupt should always check that the MSTR bit is still set. If the MSTR bit has been cleared by a slave select, it must be set by the user to re-enable SPI Master mode.

# 15.4 Data Modes

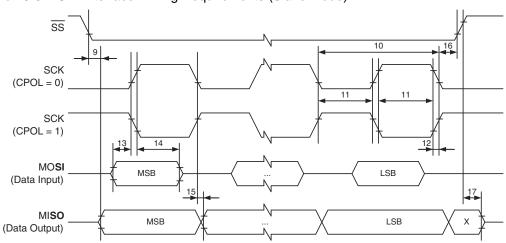

There are four combinations of SCK phase and polarity with respect to serial data, which are determined by control bits CPHA and CPOL. The SPI data transfer formats are shown in Figure 15-3 on page 167 and Figure 15-4 on page 167. Data bits are shifted out and latched in on opposite edges of the SCK signal, ensuring sufficient time for data signals to stabilize. This is clearly seen by summarizing Table 15-3 on page 168 and Table 15-4 on page 168, as done in Table 15-2 on page 167

The UDORDn bit in UCSRnC sets the frame format used by the USART in MSPIM mode. The Receiver and Transmitter use the same setting. Note that changing the setting of any of these bits will corrupt all ongoing communication for both the Receiver and Transmitter.

16-bit data transfer can be achieved by writing two data bytes to UDRn. A UART transmit complete interrupt will then signal that the 16-bit value has been shifted out.

# 17.5.1 USART MSPIM Initialization

The USART in MSPIM mode has to be initialized before any communication can take place. The initialization process normally consists of setting the baud rate, setting master mode of operation (by setting DDR\_XCKn to one), setting frame format and enabling the Transmitter and the Receiver. Only the transmitter can operate independently. For interrupt driven USART operation, the Global Interrupt Flag should be cleared (and thus interrupts globally disabled) when doing the initialization.

Note: To ensure immediate initialization of the XCKn output the baud-rate register (UBRRn) must be zero at the time the transmitter is enabled. Contrary to the normal mode USART operation the UBRRn must then be written to the desired value after the transmitter is enabled, but before the first transmission is started. Setting UBRRn to zero before enabling the transmitter is not necessary if the initialization is done immediately after a reset since UBRRn is reset to zero.

Before doing a re-initialization with changed baud rate, data mode, or frame format, be sure that there is no ongoing transmissions during the period the registers are changed. The TXCn Flag can be used to check that the Transmitter has completed all transfers, and the RXCn Flag can be used to check that there are no unread data in the receive buffer. Note that the TXCn Flag must be cleared before each transmission (before UDRn is written) if it is used for this purpose.

The following simple USART initialization code examples show one assembly and one C function that are equal in functionality. The examples assume polling (no interrupts enabled). The baud rate is given as a function parameter. For the assembly code, the baud rate parameter is assumed to be stored in the r17:r16 registers.

# 24. Memory Programming

# 24.1 Program And Data Memory Lock Bits

The ATmega164P/324P/644P provides six Lock bits which can be left unprogrammed ("1") or can be programmed ("0") to obtain the additional features listed in Table 24-2. The Lock bits can only be erased to "1" with the Chip Erase command.

| Lock Bit Byte | Bit No | Description   | Default Value    |

|---------------|--------|---------------|------------------|

|               | 7      | -             | 1 (unprogrammed) |

|               | 6      | -             | 1 (unprogrammed) |

| BLB12         | 5      | Boot Lock bit | 1 (unprogrammed) |

| BLB11         | 4      | Boot Lock bit | 1 (unprogrammed) |

| BLB02         | 3      | Boot Lock bit | 1 (unprogrammed) |

| BLB01         | 2      | Boot Lock bit | 1 (unprogrammed) |

| LB2           | 1      | Lock bit      | 1 (unprogrammed) |

| LB1           | 0      | Lock bit      | 1 (unprogrammed) |

Note: 1. "1" means unprogrammed, "0" means programmed

| Memory Lock Bits |       | S     | Protection Type                                                                                                                                                                                                                                                                                              |

|------------------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LB Mode          | LB2   | LB1   |                                                                                                                                                                                                                                                                                                              |

| 1                | 1     | 1     | No memory lock features enabled.                                                                                                                                                                                                                                                                             |

| 2                | 1     | 0     | Further programming of the Flash and EEPROM is disabled in Parallel and Serial Programming mode. The Fuse bits are locked in both Serial and Parallel Programming mode. <sup>(1)</sup>                                                                                                                       |

| 3                | 0     | 0     | Further programming and verification of the Flash and EEPROM is disabled in Parallel and Serial Programming mode. The Boot Lock bits and Fuse bits are locked in both Serial and Parallel Programming mode. <sup>(1)</sup>                                                                                   |

| BLB0 Mode        | BLB02 | BLB01 |                                                                                                                                                                                                                                                                                                              |

| 1                | 1     | 1     | No restrictions for SPM or (E)LPM accessing the Application section.                                                                                                                                                                                                                                         |

| 2                | 1     | 0     | SPM is not allowed to write to the Application section.                                                                                                                                                                                                                                                      |

| 3                | 0     | 0     | SPM is not allowed to write to the Application section, and<br>(E)LPM executing from the Boot Loader section is not allowed to<br>read from the Application section. If Interrupt Vectors are placed<br>in the Boot Loader section, interrupts are disabled while<br>executing from the Application section. |

| 4                | 0     | 1     | (E)LPM executing from the Boot Loader section is not allowed to<br>read from the Application section. If Interrupt Vectors are placed<br>in the Boot Loader section, interrupts are disabled while<br>executing from the Application section.                                                                |

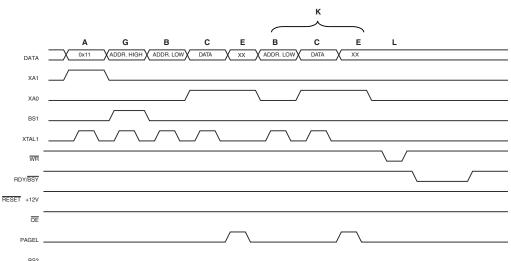

Figure 24-4. Programming the EEPROM Waveforms

# 24.7.6 Reading the Flash

The algorithm for reading the Flash memory is as follows (refer to "Programming the Flash" on page 300 for details on Command and Address loading):

- 1. A: Load Command "0000 0010".

- 2. H: Load Address Extended Byte (0x00- 0xFF).

- 3. G: Load Address High Byte (0x00 0xFF).

- 4. B: Load Address Low Byte (0x00 0xFF).

- 5. Set OE to "0", and BS1 to "0". The Flash word low byte can now be read at DATA.

- 6. Set BS to "1". The Flash word high byte can now be read at DATA.

- 7. Set OE to "1".

# 24.7.7 Reading the EEPROM

The algorithm for reading the EEPROM memory is as follows (refer to "Programming the Flash" on page 300 for details on Command and Address loading):

- 1. A: Load Command "0000 0011".

- 2. G: Load Address High Byte (0x00 0xFF).

- 3. B: Load Address Low Byte (0x00 0xFF).

- 4. Set  $\overline{OE}$  to "0", and BS1 to "0". The EEPROM Data byte can now be read at DATA.

- 5. Set OE to "1".

# 24.7.8 Programming the Fuse Low Bits

The algorithm for programming the Fuse Low bits is as follows (refer to "Programming the Flash" on page 300 for details on Command and Data loading):

- 1. A: Load Command "0100 0000".

- 2. C: Load Data Low Byte. Bit  $n = 0^{\circ}$  programs and bit  $n = 1^{\circ}$  erases the Fuse bit.

- 3. Give  $\overline{WR}$  a negative pulse and wait for RDY/ $\overline{BSY}$  to go high.

Figure 25-5. SPI Interface Timing Requirements (Slave Mode)

# 25.7 2-wire Serial Interface Characteristics

Table 25-10 describes the requirements for devices connected to the 2-wire Serial Bus. The ATmega164P/324P/644P 2-wire Serial Interface meets or exceeds these requirements under the noted conditions.

Timing symbols refer to Figure 25-6.

| Table 25-10. | 2-wire Serial Bus | Requirements |

|--------------|-------------------|--------------|

|--------------|-------------------|--------------|

| Symbol                         | Parameter                                        | Condition                                     | Min                                      | Max                          | Units |

|--------------------------------|--------------------------------------------------|-----------------------------------------------|------------------------------------------|------------------------------|-------|

| V <sub>IL</sub>                | Input Low-voltage                                |                                               | -0.5                                     | 0.3 V <sub>CC</sub>          | V     |

| V <sub>IH</sub>                | Input High-voltage                               |                                               | 0.7 V <sub>CC</sub>                      | V <sub>CC</sub> + 0.5        | V     |

| $V_{hys}^{(1)}$                | Hysteresis of Schmitt Trigger Inputs             |                                               | 0.05 V <sub>CC</sub> <sup>(2)</sup>      | _                            | V     |

| $V_{OL}^{(1)}$                 | Output Low-voltage                               | 3 mA sink current                             | 0                                        | 0.4                          | V     |

| t <sub>r</sub> <sup>(1)</sup>  | Rise Time for both SDA and SCL                   |                                               | 20 + 0.1C <sub>b</sub> <sup>(2)(3)</sup> | 300                          | ns    |

| t <sub>of</sub> <sup>(1)</sup> | Output Fall Time from $V_{IHmin}$ to $V_{ILmax}$ | 10 pF < $C_{b}$ < 400 pF <sup>(3)</sup>       | 20 + 0.1C <sub>b</sub> <sup>(2)(3)</sup> | 250                          | ns    |

| t <sub>SP</sub> <sup>(1)</sup> | Spikes Suppressed by Input Filter                |                                               | 0                                        | 50 <sup>(2)</sup>            | ns    |

| I <sub>i</sub>                 | Input Current each I/O Pin                       | $0.1V_{CC} < V_i < 0.9V_{CC}$                 | -10                                      | 10                           | μA    |

| C <sub>i</sub> <sup>(1)</sup>  | Capacitance for each I/O Pin                     |                                               | _                                        | 10                           | pF    |

| f <sub>SCL</sub>               | SCL Clock Frequency                              | $f_{CK}^{(4)} > max(16f_{SCL}, 250kHz)^{(5)}$ | 0                                        | 400                          | kHz   |

| Rp Value of Pull-up resistor   |                                                  | $f_{SCL} \leq 100 \text{ kHz}$                | $\frac{V_{CC} - 0.4V}{3\text{mA}}$       | $\frac{1000 \text{ns}}{C_b}$ | Ω     |

|                                | value of Pull-up resistor                        | f <sub>SCL</sub> > 100 kHz                    | $\frac{V_{CC} - 0.4V}{3\text{mA}}$       | $\frac{300 \text{ns}}{C_b}$  | Ω     |

| t <sub>HD;STA</sub> Ho         | Hold Time (repeated) START Condition             | $f_{SCL} \le 100 \text{ kHz}$                 | 4.0                                      | _                            | μs    |

|                                |                                                  | f <sub>SCL</sub> > 100 kHz                    | 0.6                                      | _                            | μs    |

| t <sub>LOW</sub>               |                                                  | $f_{SCL} \le 100 \text{ kHz}^{(6)}$           | 4.7                                      | _                            | μs    |

|                                | Low Period of the SCL Clock                      | f <sub>SCL</sub> > 100 kHz <sup>(7)</sup>     | 1.3                                      | _                            | μs    |

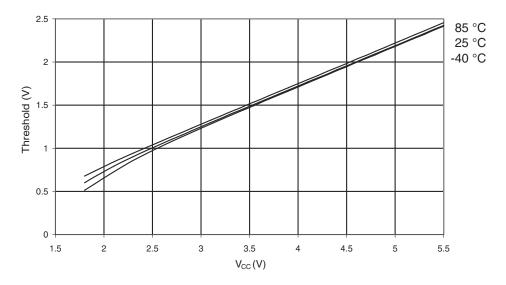

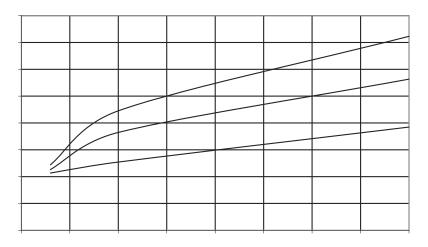

Figure 26-26. I/O Pin Input Threshold Voltage vs.  $V_{CC}$  ( $V_{IL}$ , I/O Pin Read as '0').

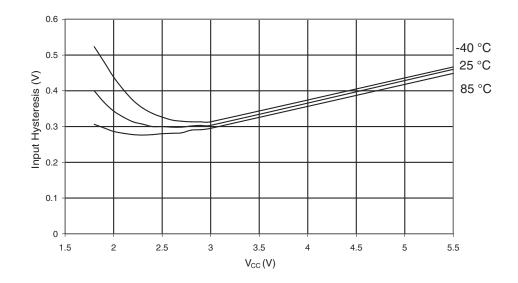

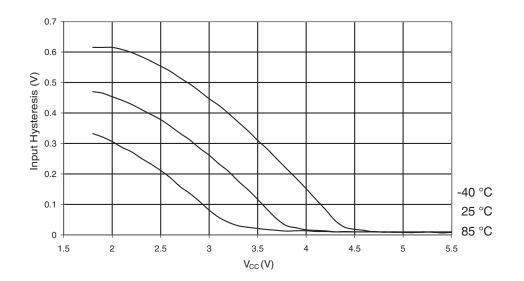

Figure 26-27. I/O Pin Input Hysteresis vs. V<sub>CC</sub>.

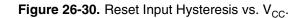

# 26.1.10 BOD Threshold

# 26.2.13 Current Consumption in Reset and Reset Pulsewidth

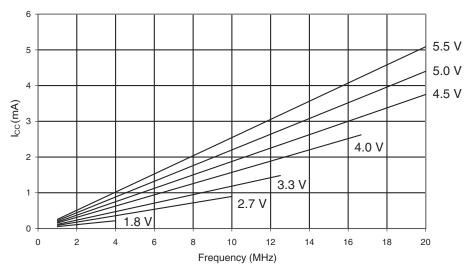

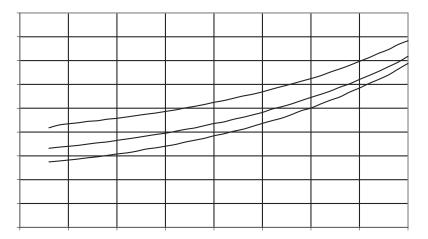

Figure 26-92. Reset Supply Current vs. Low Frequency

Figure 26-93. Reset Supply Current vs. Frequency

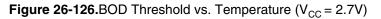

# 26.3.10 BOD Threshold

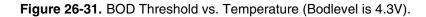

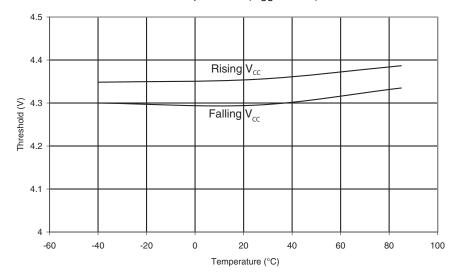

**Figure 26-125.**BOD Threshold vs. Temperature ( $V_{CC} = 4.3V$ )

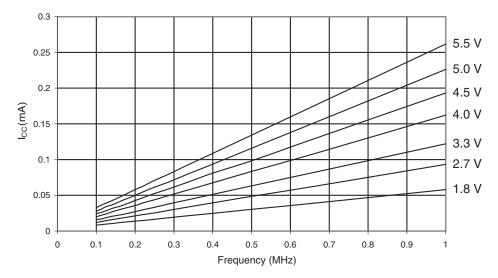

Figure 26-137. Programming Current vs.  $V_{CC}$

Figure 26-138. Watchdog Timer Current vs.  $V_{\text{CC}}$

# 29. Ordering Information

# 29.1 ATmega164P

| Speed (MHz) <sup>(3)</sup> | Power Supply | Ordering Code                   | Package <sup>(1)</sup> | Operational Range |

|----------------------------|--------------|---------------------------------|------------------------|-------------------|

| 10                         | 1.8 - 5.5V   | ATmega164PV-10AU <sup>(2)</sup> | 44A                    |                   |

|                            |              | ATmega164PV-10PU <sup>(2)</sup> | 40P6                   |                   |

|                            |              | ATmega164PV-10MU <sup>(2)</sup> | 44M1                   | Industrial        |

| 20                         | 2.7 - 5.5V   | ATmega164P-20AU <sup>(2)</sup>  | 44A                    | (-40°C to 85°C)   |

|                            |              | ATmega164P-20PU <sup>(2)</sup>  | 40P6                   |                   |

|                            |              | ATmega164P-20MU <sup>(2)</sup>  | 44M1                   |                   |

Notes: 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information and minimum quantities.

- 2. Pb-free packaging, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

- 3. For Speed vs. V<sub>CC</sub> see "Speed Grades" on page 329.

| Package Type |                                                                                                                |  |

|--------------|----------------------------------------------------------------------------------------------------------------|--|

| 44A          | 44-lead, Thin (1.0 mm) Plastic Gull Wing Quad Flat Package (TQFP)                                              |  |

| 40P6         | 40-pin, 0.600" Wide, Plastic Dual Inline Package (PDIP)                                                        |  |

| 44M1         | 44-pad, 7 x 7 x 1.0 mm body, lead pitch 0.50 mm, Thermally Enhanced Plastic Very Thin Quad Flat No-Lead (VQFN) |  |