Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 10MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega644pv-10au |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.5.1 SPH and SPL – Stack Pointer High and Stack pointer Low

| Bit           | 15  | 14  | 13  | 12                   | 11                   | 10                   | 9   | 8   |     |

|---------------|-----|-----|-----|----------------------|----------------------|----------------------|-----|-----|-----|

| 0x3E (0x5E)   | -   | -   | -   | SP12                 | SP11                 | SP10                 | SP9 | SP8 | SPH |

| 0x3D (0x5D)   | SP7 | SP6 | SP5 | SP4                  | SP3                  | SP2                  | SP1 | SP0 | SPL |

|               | 7   | 6   | 5   | 4                    | 3                    | 2                    | 1   | 0   |     |

| Read/Write    | R   | R   | R   | R/W                  | R/W                  | R/W                  | R/W | R/W |     |

|               | R/W | R/W | R/W | R/W                  | R/W                  | R/W                  | R/W | R/W |     |

| Initial Value | 0   | 0   | 0   | 0/0/1 <sup>(1)</sup> | 0/1/0 <sup>(1)</sup> | 1/0/0 <sup>(1)</sup> | 0   | 0   |     |

|               | 1   | 1   | 1   | 1                    | 1                    | 1                    | 1   | 1   |     |

Note: 1. Initial values respectively for the ATmega164P/324P/644P.

#### Table 4-2. Stack Pointer size

| Device     | Stack Pointer size |

|------------|--------------------|

| ATmega164P | SP[10:0]           |

| ATmega324P | SP[11:0]           |

| ATmega644P | SP[12:0]           |

#### 4.5.2 RAMPZ – Extended Z-pointer Register for ELPM/SPM

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

| 0x3B (0x5B)   | RAMPZ7 | RAMPZ6 | RAMPZ5 | RAMPZ4 | RAMPZ3 | RAMPZ2 | RAMPZ1 | RAMPZ0 | RAMPZ |

| Read/Write    | R/W    |       |

| Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

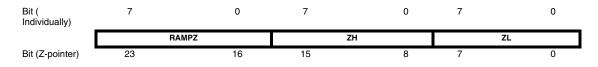

For ELPM/SPM instructions, the Z-pointer is a concatenation of RAMPZ, ZH, and ZL, as shown in Figure 4-4. Note that LPM is not affected by the RAMPZ setting.

Figure 4-4. The Z-pointer used by ELPM and SPM

The actual number of bits is implementation dependent. Unused bits in an implementation will always read as zero. For compatibility with future devices, be sure to write these bits to zero.

## 4.6 Instruction Execution Timing

This section describes the general access timing concepts for instruction execution. The AVR CPU is driven by the CPU clock  $clk_{CPU}$ , directly generated from the selected clock source for the chip. No internal clock division is used.

Figure 4-5 on page 15 shows the parallel instruction fetches and instruction executions enabled by the Harvard architecture and the fast-access Register File concept. This is the basic pipelining concept to obtain up to 1 MIPS per MHz with the corresponding unique results for functions per cost, functions per clocks, and functions per power-unit.

| Power Conditions    | Start-up Time from Power-<br>down and Power-save | Additional Delay from<br>Reset (V <sub>CC</sub> = 5.0V) | SUT10 |

|---------------------|--------------------------------------------------|---------------------------------------------------------|-------|

| BOD enabled         | 6 CK                                             | 14CK                                                    | 00    |

| Fast rising power   | 6 CK                                             | 14CK + 4.1 ms                                           | 01    |

| Slowly rising power | 6 CK                                             | 14CK + 65 ms                                            | 10    |

|                     | Reserved                                         |                                                         | 11    |

| Table 6-15. | Start-un | Times for the | External | Clock Selection |

|-------------|----------|---------------|----------|-----------------|

|             | Start-up |               | LAIGINAI |                 |

When applying an external clock, it is required to avoid sudden changes in the applied clock frequency to ensure stable operation of the MCU. A variation in frequency of more than 2% from one clock cycle to the next can lead to unpredictable behavior. If changes of more than 2% is required, ensure that the MCU is kept in Reset during the changes.

Note that the System Clock Prescaler can be used to implement run-time changes of the internal clock frequency while still ensuring stable operation. Refer to "System Clock Prescaler" on page 38 for details.

## 6.9 Timer/Counter Oscillator

ATmega164P/324P/644P uses the same type of crystal oscillator for Low-frequency Crystal Oscillator and Timer/Counter Oscillator. See "Low Frequency Crystal Oscillator" on page 34 for details on the oscillator and crystal requirements.

The device can operate its Timer/Counter2 from an external 32.768 kHz watch crystal or a external clock source. See "Clock Source Connections" on page 31 for details.

Applying an external clock source to TOSC1 can be done if EXTCLK in the ASSR Register is written to logic one. See "The Output Compare Register B contains an 8-bit value that is continuously compared with the counter value (TCNT2). A match can be used to generate an Output Compare interrupt, or to generate a waveform output on the OC2B pin." on page 157 for further description on selecting external clock as input instead of a 32.768 kHz watch crystal.

## 6.10 Clock Output Buffer

The device can output the system clock on the CLKO pin. To enable the output, the CKOUT Fuse has to be programmed. This mode is suitable when the chip clock is used to drive other circuits on the system. The clock also will be output during reset, and the normal operation of I/O pin will be overridden when the fuse is programmed. Any clock source, including the internal RC Oscillator, can be selected when the clock is output on CLKO. If the System Clock Prescaler is used, it is the divided system clock that is output.

## 6.11 System Clock Prescaler

The ATmega164P/324P/644P has a system clock prescaler, and the system clock can be divided by setting the "CLKPR – Clock Prescale Register" on page 40. This feature can be used to decrease the system clock frequency and the power consumption when the requirement for processing power is low. This can be used with all clock source options, and it will affect the clock frequency of the CPU and all synchronous peripherals.  $clk_{I/O}$ ,  $clk_{ADC}$ ,  $clk_{CPU}$ , and  $clk_{FLASH}$  are divided by a factor as shown in Table 6-16 on page 41.

When switching between prescaler settings, the System Clock Prescaler ensures that no glitches occurs in the clock system. It also ensures that no intermediate frequency is higher than

The alternate pin configuration is as follows:

#### • OC2A/PCINT31 – Port D, Bit 7

OC2A, Output Compare Match A output: The PD7 pin can serve as an external output for the Timer/Counter2 Output Compare A. The pin has to be configured as an output (DDD7 set (one)) to serve this function. The OC2A pin is also the output pin for the PWM mode timer function.

PCINT31, Pin Change Interrupt Source 31:The PD7 pin can serve as an external interrupt source.

#### ICP1/OC2B/PCINT30 – Port D, Bit 6

ICP1, Input Capture Pin 1: The PD6 pin can act as an input capture pin for Timer/Counter1.

OC2B, Output Compare Match B output: The PD6 pin can serve as an external output for the Timer/Counter2 Output Compare B. The pin has to be configured as an output (DDD6 set (one)) to serve this function. The OC2B pin is also the output pin for the PWM mode timer function.

PCINT30, Pin Change Interrupt Source 30: The PD6 pin can serve as an external interrupt source.

#### • OC1A/PCINT29 – Port D, Bit 5

OC1A, Output Compare Match A output: The PD5 pin can serve as an external output for the Timer/Counter1 Output Compare A. The pin has to be configured as an output (DDD5 set (one)) to serve this function. The OC1A pin is also the output pin for the PWM mode timer function.

PCINT29, Pin Change Interrupt Source 29: The PD5 pin can serve as an external interrupt source.

#### • OC1B/XCK1/PCINT28 – Port D, Bit 4

OC1B, Output Compare Match B output: The PB4 pin can serve as an external output for the Timer/Counter1 Output Compare B. The pin has to be configured as an output (DDD4 set (one)) to serve this function. The OC1B pin is also the output pin for the PWM mode timer function.

XCK1, USART1 External clock. The Data Direction Register (DDB4) controls whether the clock is output (DDD4 set "one") or input (DDD4 cleared). The XCK4 pin is active only when the USART1 operates in Synchronous mode.

PCINT28, Pin Change Interrupt Source 28: The PD4 pin can serve as an external interrupt source.

#### INT1/TXD1/PCINT27 – Port D, Bit 3

INT1, External Interrupt source 1. The PD3 pin can serve as an external interrupt source to the MCU.

TXD1, Transmit Data (Data output pin for the USART1). When the USART1 Transmitter is enabled, this pin is configured as an output regardless of the value of DDD3.

PCINT27, Pin Change Interrupt Source 27: The PD3 pin can serve as an external interrupt source.

The Timer/Counter Overflow Flag (TOVn) is set according to the mode of operation selected by the WGMn3:0 bits. TOVn can be used for generating a CPU interrupt.

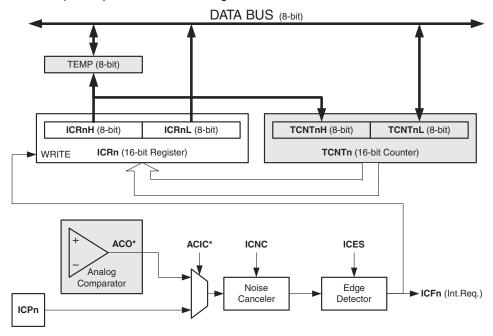

## 13.6 Input Capture Unit

The Timer/Counter incorporates an Input Capture unit that can capture external events and give them a time-stamp indicating time of occurrence. The external signal indicating an event, or multiple events, can be applied via the ICPn pin or alternatively, via the analog-comparator unit. The time-stamps can then be used to calculate frequency, duty-cycle, and other features of the signal applied. Alternatively the time-stamps can be used for creating a log of the events.

The Input Capture unit is illustrated by the block diagram shown in Figure 13-3. The elements of the block diagram that are not directly a part of the Input Capture unit are gray shaded. The small "n" in register and bit names indicates the Timer/Counter number.

Figure 13-3. Input Capture Unit Block Diagram

When a change of the logic level (an event) occurs on the *Input Capture pin* (ICPn), alternatively on the *Analog Comparator output* (ACO), and this change confirms to the setting of the edge detector, a capture will be triggered. When a capture is triggered, the 16-bit value of the counter (TCNTn) is written to the *Input Capture Register* (ICRn). The *Input Capture Flag* (ICFn) is set at the same system clock as the TCNTn value is copied into ICRn Register. If enabled (ICIEn = 1), the Input Capture Flag generates an Input Capture interrupt. The ICFn Flag is automatically cleared when the interrupt is executed. Alternatively the ICFn Flag can be cleared by software by writing a logical one to its I/O bit location.

Reading the 16-bit value in the *Input Capture Register* (ICRn) is done by first reading the low byte (ICRnL) and then the high byte (ICRnH). When the low byte is read the high byte is copied into the high byte temporary register (TEMP). When the CPU reads the ICRnH I/O location it will access the TEMP Register.

The ICRn Register can only be written when using a Waveform Generation mode that utilizes the ICRn Register for defining the counter's TOP value. In these cases the *Waveform Genera*-

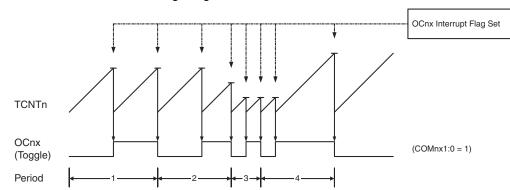

The timing diagram for the CTC mode is shown in Table 14-5 on page 145. The counter value (TCNT2) increases until a compare match occurs between TCNT2 and OCR2A, and then counter (TCNT2) is cleared.

An interrupt can be generated each time the counter value reaches the TOP value by using the OCF2A Flag. If the interrupt is enabled, the interrupt handler routine can be used for updating the TOP value. However, changing TOP to a value close to BOTTOM when the counter is running with none or a low prescaler value must be done with care since the CTC mode does not have the double buffering feature. If the new value written to OCR2A is lower than the current value of TCNT2, the counter will miss the compare match. The counter will then have to count to its maximum value (0xFF) and wrap around starting at 0x00 before the compare match can occur.

For generating a waveform output in CTC mode, the OC2A output can be set to toggle its logical level on each compare match by setting the Compare Output mode bits to toggle mode (COM2A1:0 = 1). The OC2A value will not be visible on the port pin unless the data direction for the pin is set to output. The waveform generated will have a maximum frequency of  $f_{OC2A} = f_{clk\_I/O}/2$  when OCR2A is set to zero (0x00). The waveform frequency is defined by the following equation:

$$f_{OCnx} = \frac{f_{\mathsf{clk\_l/O}}}{2 \cdot N \cdot (1 + OCRnx)}$$

The N variable represents the prescale factor (1, 8, 32, 64, 128, 256, or 1024).

As for the Normal mode of operation, the TOV2 Flag is set in the same timer clock cycle that the counter counts from MAX to 0x00.

## 14.7.3 Fast PWM Mode

The fast Pulse Width Modulation or fast PWM mode (WGM22:0 = 3 or 7) provides a high frequency PWM waveform generation option. The fast PWM differs from the other PWM option by its single-slope operation. The counter counts from BOTTOM to TOP then restarts from BOT-TOM. TOP is defined as 0xFF when WGM22:0 = 3, and OCR2A when MGM22:0 = 7. In noninverting Compare Output mode, the Output Compare (OC2x) is cleared on the compare match between TCNT2 and OCR2x, and set at BOTTOM. In inverting Compare Output mode, the output is set on compare match and cleared at BOTTOM. Due to the single-slope operation, the operating frequency of the fast PWM mode can be twice as high as the phase correct PWM mode that uses dual-slope operation. This high frequency makes the fast PWM mode well suited

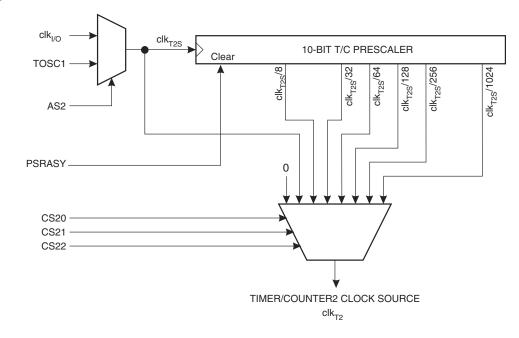

## 14.10 Timer/Counter Prescaler

Figure 14-12. Prescaler for Timer/Counter2

The clock source for Timer/Counter2 is named  $clk_{T2S}$ .  $clk_{T2S}$  is by default connected to the main system I/O clock  $clk_{IO}$ . By setting the AS2 bit in ASSR, Timer/Counter2 is asynchronously clocked from the TOSC1 pin. This enables use of Timer/Counter2 as a Real Time Counter (RTC). When AS2 is set, pins TOSC1 and TOSC2 are disconnected from Port C. A crystal can then be connected between the TOSC1 and TOSC2 pins to serve as an independent clock source for Timer/Counter2. The Oscillator is optimized for use with a 32.768 kHz crystal. By setting the EXCLK bit in the ASSR a 32 kHz external clock can be applied. See "ASSR – Asynchronous Status Register" on page 157 for details.

For Timer/Counter2, the possible prescaled selections are:  $clk_{T2S}/8$ ,  $clk_{T2S}/32$ ,  $clk_{T2S}/64$ ,  $clk_{T2S}/128$ ,  $clk_{T2S}/256$ , and  $clk_{T2S}/1024$ . Additionally,  $clk_{T2S}$  as well as 0 (stop) may be selected. Setting the PSRASY bit in GTCCR resets the prescaler. This allows the user to operate with a predictable prescaler.

## 14.11 Register Description

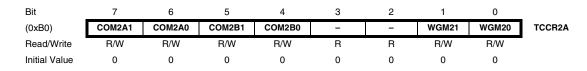

## 14.11.1 TCCR2A – Timer/Counter Control Register A

## Bits 7:6 – COM2A1:0: Compare Match Output A Mode

These bits control the Output Compare pin (OC2A) behavior. If one or both of the COM2A1:0 bits are set, the OC2A output overrides the normal port functionality of the I/O pin it is connected to. However, note that the Data Direction Register (DDR) bit corresponding to the OC2A pin must be set in order to enable the output driver.

check that there are no unread data in the receive buffer. Note that the TXCn Flag must be cleared before each transmission (before UDRn is written) if it is used for this purpose.

The following simple USART initialization code examples show one assembly and one C function that are equal in functionality. The examples assume asynchronous operation using polling (no interrupts enabled) and a fixed frame format. The baud rate is given as a function parameter. For the assembly code, the baud rate parameter is assumed to be stored in the r17:r16 Registers.

```

Assembly Code Example<sup>(1)</sup>

USART_Init:

; Set baud rate

out UBRRHn, r17

out UBRRLn, r16

; Enable receiver and transmitter

ldi r16, (1<<RXENn) | (1<<TXENn)

out UCSRnB,r16

; Set frame format: 8data, 2stop bit

ldi r16, (1<<USBSn) | (3<<UCSZn0)

out UCSRnC, r16

ret

C Code Example<sup>(1)</sup>

void USART_Init( unsigned int baud )

{

/* Set baud rate */

UBRRHn = (unsigned char) (baud>>8);

UBRRLn = (unsigned char) baud;

/* Enable receiver and transmitter */

UCSRnB = (1 << RXENn) | (1 << TXENn);

/* Set frame format: 8data, 2stop bit */

UCSRnC = (1<<USBSn) | (3<<UCSZn0);

}

```

Note: 1. See "About Code Examples" on page 8.

More advanced initialization routines can be made that include frame format as parameters, disable interrupts and so on. However, many applications use a fixed setting of the baud and control registers, and for these types of applications the initialization code can be placed directly in the main routine, or be combined with initialization code for other I/O modules.

## 16.7 Data Transmission – The USART Transmitter

The USART Transmitter is enabled by setting the *Transmit Enable* (TXEN) bit in the UCSRnB Register. When the Transmitter is enabled, the normal port operation of the TxDn pin is overridden by the USART and given the function as the Transmitter's serial output. The baud rate, mode of operation and frame format must be set up once before doing any transmissions. If synchronous operation is used, the clock on the XCKn pin will be overridden and used as transmission clock.

## 16.11 Register Description

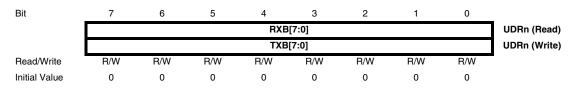

## 16.11.1 UDRn – USART I/O Data Register n

The USART Transmit Data Buffer Register and USART Receive Data Buffer Registers share the same I/O address referred to as USART Data Register or UDRn. The Transmit Data Buffer Register (TXB) will be the destination for data written to the UDRn Register location. Reading the UDRn Register location will return the contents of the Receive Data Buffer Register (RXB).

For 5-, 6-, or 7-bit characters the upper unused bits will be ignored by the Transmitter and set to zero by the Receiver.

The transmit buffer can only be written when the UDREn Flag in the UCSRnA Register is set. Data written to UDRn when the UDREn Flag is not set, will be ignored by the USART Transmitter. When data is written to the transmit buffer, and the Transmitter is enabled, the Transmitter will load the data into the Transmit Shift Register when the Shift Register is empty. Then the data will be serially transmitted on the TxDn pin.

The receive buffer consists of a two level FIFO. The FIFO will change its state whenever the receive buffer is accessed. Due to this behavior of the receive buffer, do not use Read-Modify-Write instructions (SBI and CBI) on this location. Be careful when using bit test instructions (SBIC and SBIS), since these also will change the state of the FIFO.

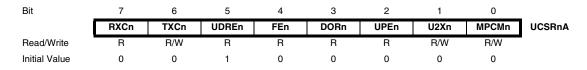

## 16.11.2 UCSRnA – USART Control and Status Register A

## • Bit 7 – RXCn: USART Receive Complete

This flag bit is set when there are unread data in the receive buffer and cleared when the receive buffer is empty (i.e., does not contain any unread data). If the Receiver is disabled, the receive buffer will be flushed and consequently the RXCn bit will become zero. The RXCn Flag can be used to generate a Receive Complete interrupt (see description of the RXCIEn bit).

#### Bit 6 – TXCn: USART Transmit Complete

This flag bit is set when the entire frame in the Transmit Shift Register has been shifted out and there are no new data currently present in the transmit buffer (UDRn). The TXCn Flag bit is automatically cleared when a transmit complete interrupt is executed, or it can be cleared by writing a one to its bit location. The TXCn Flag can generate a Transmit Complete interrupt (see description of the TXCIEn bit).

#### • Bit 5 – UDREn: USART Data Register Empty

The UDREn Flag indicates if the transmit buffer (UDRn) is ready to receive new data. If UDREn is one, the buffer is empty, and therefore ready to be written. The UDREn Flag can generate a

#### Bit 5 – UDRIEn: USART Data Register Empty Interrupt Enable n

Writing this bit to one enables interrupt on the UDREn Flag. A Data Register Empty interrupt will be generated only if the UDRIEn bit is written to one, the Global Interrupt Flag in SREG is written to one and the UDREn bit in UCSRnA is set.

#### Bit 4 – RXENn: Receiver Enable n

Writing this bit to one enables the USART Receiver. The Receiver will override normal port operation for the RxDn pin when enabled. Disabling the Receiver will flush the receive buffer invalidating the FEn, DORn, and UPEn Flags.

#### Bit 3 – TXENn: Transmitter Enable n

Writing this bit to one enables the USART Transmitter. The Transmitter will override normal port operation for the TxDn pin when enabled. The disabling of the Transmitter (writing TXENn to zero) will not become effective until ongoing and pending transmissions are completed, i.e., when the Transmit Shift Register and Transmit Buffer Register do not contain data to be transmitted. When disabled, the Transmitter will no longer override the TxDn port.

#### • Bit 2 – UCSZn2: Character Size n

The UCSZn2 bits combined with the UCSZn1:0 bit in UCSRnC sets the number of data bits (Character SiZe) in a frame the Receiver and Transmitter use.

#### Bit 1 – RXB8n: Receive Data Bit 8 n

RXB8n is the ninth data bit of the received character when operating with serial frames with nine data bits. Must be read before reading the low bits from UDRn.

#### Bit 0 – TXB8n: Transmit Data Bit 8 n

TXB8n is the ninth data bit in the character to be transmitted when operating with serial frames with nine data bits. Must be written before writing the low bits to UDRn.

#### 16.11.4 UCSRnC – USART Control and Status Register n C

| Bit           | 7       | 6       | 5     | 4     | 3     | 2      | 1      | 0      | _      |

|---------------|---------|---------|-------|-------|-------|--------|--------|--------|--------|

|               | UMSELn1 | UMSELn0 | UPMn1 | UPMn0 | USBSn | UCSZn1 | UCSZn0 | UCPOLn | UCSRnC |

| Read/Write    | R/W     | R/W     | R/W   | R/W   | R/W   | R/W    | R/W    | R/W    | •      |

| Initial Value | 0       | 0       | 0     | 0     | 0     | 1      | 1      | 0      |        |

#### Bits 7:6 – UMSELn1:0 USART Mode Select

These bits select the mode of operation of the USARTn as shown in Table 16-4...

#### Table 16-4. UMSELn Bits Settings

| UMSELn1 | UMSELn0 | Mode                              |

|---------|---------|-----------------------------------|

| 0       | 0       | Asynchronous USART                |

| 0       | 1       | Synchronous USART                 |

| 1       | 0       | (Reserved)                        |

| 1       | 1       | Master SPI (MSPIM) <sup>(1)</sup> |

Note: 1. See "USART in SPI Mode" on page 198 for full description of the Master SPI Mode (MSPIM) operation

- 1. The first step in a TWI transmission is to transmit a START condition. This is done by writing a specific value into TWCR, instructing the TWI hardware to transmit a START condition. Which value to write is described later on. However, it is important that the TWINT bit is set in the value written. Writing a one to TWINT clears the flag. The TWI will not start any operation as long as the TWINT bit in TWCR is set. Immediately after the application has cleared TWINT, the TWI will initiate transmission of the START condition.

- 2. When the START condition has been transmitted, the TWINT Flag in TWCR is set, and TWSR is updated with a status code indicating that the START condition has successfully been sent.

- 3. The application software should now examine the value of TWSR, to make sure that the START condition was successfully transmitted. If TWSR indicates otherwise, the application software might take some special action, like calling an error routine. Assuming that the status code is as expected, the application must load SLA+W into TWDR. Remember that TWDR is used both for address and data. After TWDR has been loaded with the desired SLA+W, a specific value must be written to TWCR, instructing the TWI hardware to transmit the SLA+W present in TWDR. Which value to write is described later on. However, it is important that the TWINT bit is set in the value written. Writing a one to TWINT clears the flag. The TWI will not start any operation as long as the TWINT bit in TWCR is set. Immediately after the application has cleared TWINT, the TWI will initiate transmission of the address packet.

- 4. When the address packet has been transmitted, the TWINT Flag in TWCR is set, and TWSR is updated with a status code indicating that the address packet has successfully been sent. The status code will also reflect whether a Slave acknowledged the packet or not.

- 5. The application software should now examine the value of TWSR, to make sure that the address packet was successfully transmitted, and that the value of the ACK bit was as expected. If TWSR indicates otherwise, the application software might take some special action, like calling an error routine. Assuming that the status code is as expected, the application must load a data packet into TWDR. Subsequently, a specific value must be written to TWCR, instructing the TWI hardware to transmit the data packet present in TWDR. Which value to write is described later on. However, it is important that the TWINT bit is set in the value written. Writing a one to TWINT clears the flag. The TWI will not start any operation as long as the TWINT bit in TWCR is set. Immediately after the application has cleared TWINT, the TWI will initiate transmission of the data packet.

- 6. When the data packet has been transmitted, the TWINT Flag in TWCR is set, and TWSR is updated with a status code indicating that the data packet has successfully been sent. The status code will also reflect whether a Slave acknowledged the packet or not.

- 7. The application software should now examine the value of TWSR, to make sure that the data packet was successfully transmitted, and that the value of the ACK bit was as expected. If TWSR indicates otherwise, the application software might take some special action, like calling an error routine. Assuming that the status code is as expected, the application must write a specific value to TWCR, instructing the TWI hardware to transmit a STOP condition. Which value to write is described later on. However, it is important that the TWINT bit is set in the value written. Writing a one to TWINT clears the flag. The TWI will not start any operation as long as the TWINT bit in TWCR is set. Immediately after the application has cleared TWINT, the TWI will initiate transmission of the STOP condition. Note that TWINT is NOT set after a STOP condition has been sent.

Even though this example is simple, it shows the principles involved in all TWI transmissions. These can be summarized as follows:

• When the TWI has finished an operation and expects application response, the TWINT Flag is set. The SCL line is pulled low until TWINT is cleared.

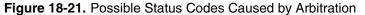

Two or more masters are accessing different slaves. In this case, arbitration will occur in the SLA bits. Masters trying to output a one on SDA while another Master outputs a zero will lose the arbitration. Masters losing arbitration in SLA will switch to Slave mode to check if they are being addressed by the winning Master. If addressed, they will switch to SR or ST mode, depending on the value of the READ/WRITE bit. If they are not being addressed, they will switch to not addressed Slave mode or wait until the bus is free and transmit a new START condition, depending on application software action.

This is summarized in Figure 18-21. Possible status values are given in circles.

## 18.9 Register Description

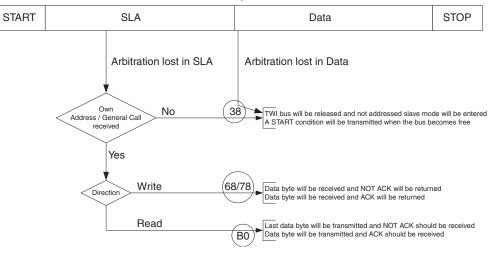

#### 18.9.1 TWBR – TWI Bit Rate Register

#### • Bits 7:0 - TWI Bit Rate Register

TWBR selects the division factor for the bit rate generator. The bit rate generator is a frequency divider which generates the SCL clock frequency in the Master modes. See "Bit Rate Generator Unit" on page 213 for calculating bit rates.

#### 18.9.2 TWCR – TWI Control Register

| Bit           | 7     | 6    | 5     | 4     | 3    | 2    | 1 | 0    | _    |

|---------------|-------|------|-------|-------|------|------|---|------|------|

| (0xBC)        | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE | TWCR |

| Read/Write    | R/W   | R/W  | R/W   | R/W   | R    | R/W  | R | R/W  | -    |

| Initial Value | 0     | 0    | 0     | 0     | 0    | 0    | 0 | 0    |      |

The TWCR is used to control the operation of the TWI. It is used to enable the TWI, to initiate a Master access by applying a START condition to the bus, to generate a Receiver acknowledge, to generate a stop condition, and to control halting of the bus while the data to be written to the

|       |       | · · · |                 |

|-------|-------|-------|-----------------|

| ADPS2 | ADPS1 | ADPS0 | Division Factor |

| 1     | 0     | 0     | 16              |

| 1     | 0     | 1     | 32              |

| 1     | 1     | 0     | 64              |

| 1     | 1     | 1     | 128             |

Table 20-5.

ADC Prescaler Selections (Continued)

#### 20.9.3 ADCL and ADCH – The ADC Data Register

ADLAR = 0

| Bit           | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |      |

|---------------|------|------|------|------|------|------|------|------|------|

| (0x79)        | -    | -    | -    | -    | -    | -    | ADC9 | ADC8 | ADCH |

| (0x78)        | ADC7 | ADC6 | ADC5 | ADC4 | ADC3 | ADC2 | ADC1 | ADC0 | ADCL |

|               | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |      |

| Read/Write    | R    | R    | R    | R    | R    | R    | R    | R    |      |

|               | R    | R    | R    | R    | R    | R    | R    | R    |      |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

|               | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

|               |      |      |      |      |      |      |      |      |      |

|               |      |      |      |      |      |      | _    | _    |      |

| Bit           | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |      |

ADLAR = 1

| Bit           | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |

|---------------|------|------|------|------|------|------|------|------|

| (0x79)        | ADC9 | ADC8 | ADC7 | ADC6 | ADC5 | ADC4 | ADC3 | ADC2 |

| (0x78)        | ADC1 | ADC0 | -    | -    | -    | -    | -    | -    |

|               | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| Read/Write    | R    | R    | R    | R    | R    | R    | R    | R    |

|               | R    | R    | R    | R    | R    | R    | R    | R    |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

|               | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

When an ADC conversion is complete, the result is found in these two registers. If differential channels are used, the result is presented in two's complement form.

When ADCL is read, the ADC Data Register is not updated until ADCH is read. Consequently, if the result is left adjusted and no more than 8-bit precision is required, it is sufficient to read ADCH. Otherwise, ADCL must be read first, then ADCH.

The ADLAR bit in ADMUX, and the MUXn bits in ADMUX affect the way the result is read from the registers. If ADLAR is set, the result is left adjusted. If ADLAR is cleared (default), the result is right adjusted.

#### • ADC9:0: ADC Conversion Result

These bits represent the result from the conversion, as detailed in "ADC Conversion Result" on page 253.

#### 20.9.4 ADCSRB – ADC Control and Status Register B

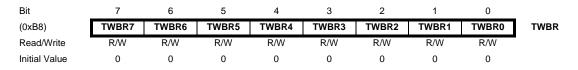

### Figure 22-4. General Port Pin Schematic Diagram

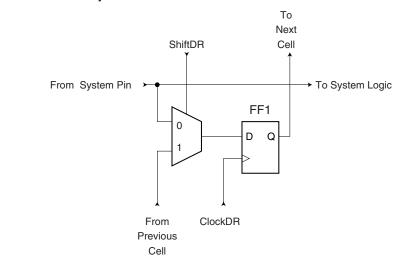

#### 22.5.2 Scanning the RESET Pin

The RESET pin accepts 5V active low logic for standard reset operation, and 12V active high logic for High Voltage Parallel programming. An observe-only cell as shown in Figure 22-5 is inserted for the 5V reset signal.

Figure 22-5. Observe-only Cell

## 25.4 System and Reset Characteristics

| Symbol                          | Parameter                                                 | Condition                                      | Min                | Тур | Max                | Units |

|---------------------------------|-----------------------------------------------------------|------------------------------------------------|--------------------|-----|--------------------|-------|

| v (1)                           | Power-on Reset Threshold Voltage (rising)                 |                                                | 0.7                | 1.0 | 1.4                | V     |

| V <sub>POT</sub> <sup>(1)</sup> | Power-on Reset Threshold Voltage (falling) <sup>(2)</sup> |                                                | 0.6                | 0.9 | 1.3                | V     |

| V <sub>RST</sub>                | RESET Pin Threshold Voltage                               |                                                | 0.2V <sub>CC</sub> |     | 0.9V <sub>CC</sub> | V     |

| t <sub>RST</sub>                | Minimum pulse width on RESET Pin                          |                                                |                    |     | 2.5                | μs    |

| V <sub>HYST</sub>               | Brown-out Detector Hysteresis                             |                                                |                    | 50  |                    | mV    |

| t <sub>BOD</sub>                | Min Pulse Width on Brown-out Reset                        |                                                |                    | 2   |                    | μs    |

| V <sub>BG</sub>                 | Bandgap reference voltage                                 | $V_{C C} = 2.7 V, T_{A} = 25^{\circ} C$        | 1.0                | 1.1 | 1.2                | V     |

| t <sub>BG</sub>                 | Bandgap reference start-up time                           | $V_{C C} = 2.7 V, T_{A} = 25^{\circ} C$        |                    | 40  | 70                 | μs    |

| I <sub>BG</sub>                 | Bandgap reference current consumption                     | V <sub>C C</sub> = 2.7V, T <sub>A</sub> = 25°C |                    | 10  |                    | μA    |

Table 25-6. Reset, Brown-out and Internal Voltage Reference Characteristics

Notes: 1. Values are guidelines only.

2. The Power-on Reset will not work unless the supply voltage has been below V<sub>POT</sub> (falling)

## Table 25-7.BODLEVEL Fuse Coding<sup>(1)</sup>

| BODLEVEL 2:0 Fuses | Min V <sub>BOT</sub> | Тур V <sub>вот</sub> | Max V <sub>BOT</sub> | Units |  |  |  |

|--------------------|----------------------|----------------------|----------------------|-------|--|--|--|

| 111                | BOD Disabled         |                      |                      |       |  |  |  |

| 110                | 1.7                  | 1.8                  | 2.0                  |       |  |  |  |

| 101                | 2.5                  | 2.7                  | 2.9                  | V     |  |  |  |

| 100                | 4.1                  | 4.3                  | 4.5                  |       |  |  |  |

| 011                |                      |                      |                      |       |  |  |  |

| 010                | Reserved             |                      |                      |       |  |  |  |

| 001                |                      |                      |                      |       |  |  |  |

| 000                |                      |                      |                      |       |  |  |  |

Note: 1. V<sub>BOT</sub> may be below nominal minimum operating voltage for some devices. For devices where this is the case, the device is tested down to V<sub>CC</sub> = V<sub>BOT</sub> during the production test. This guarantees that a Brown-Out Reset will occur before V<sub>CC</sub> drops to a voltage where correct operation of the microcontroller is no longer guaranteed. The test is performed using BODLEVEL = 101 for ATmega164P/324P/644P and BODLEVEL = 110 for ATmega164P/324P/644PV.

# 25.5 External Interrupts Characteristics

#### Table 25-8. Asynchronous External Interrupt Characteristics

| Symbol           | Parameter                                               | Condition | Min | Тур | Max | Units |

|------------------|---------------------------------------------------------|-----------|-----|-----|-----|-------|

| t <sub>INT</sub> | Minimum pulse width for asynchronous external interrupt |           |     | 50  |     | ns    |

| PRR bit  | Additional Current consumption<br>compared to Active with external<br>clock (see Figure 26-1 on page<br>338 and Figure 26-2 on page 339) | Additional Current consumption<br>compared to Idle with external<br>clock (see Figure 26-6 on page<br>341 and Figure 26-7 on page 341) |

|----------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| PRUSART1 | 1.8%                                                                                                                                     | 6.9%                                                                                                                                   |

| PRUSART0 | 2.4%                                                                                                                                     | 9.1%                                                                                                                                   |

| PRTWI    | 5.4%                                                                                                                                     | 21.2%                                                                                                                                  |

| PRTIM2   | 4.6%                                                                                                                                     | 17.4%                                                                                                                                  |

| PRTIM1   | 2.7%                                                                                                                                     | 10.5%                                                                                                                                  |

| PRTIM0   | 1.6%                                                                                                                                     | 6.0%                                                                                                                                   |

| PRADC    | 4.5%                                                                                                                                     | 16.8%                                                                                                                                  |

| PRSPI    | 3.3%                                                                                                                                     | 12.9%                                                                                                                                  |

It is possible to calculate the typical current consumption based on the numbers from Table 26-2 on page 344 for other  $V_{CC}$  and frequency settings than listed in Table 26-1 on page 343.

ExampleCalculate the expected current consumption in idle mode with TIMER1, ADC, and SPI enabled<br/>at  $V_{CC} = 2.0V$  and F = 1MHz. From Table 26-2 on page 344, third column, we see that we need<br/>to add 10.5% for the TIMER1, 16.8% for the ADC, and 12.9% for the SPI module. Reading<br/>from Figure 26-6 on page 341, we find that the idle current consumption is ~0.115 mA at  $V_{CC} =$ <br/>2.0V and F = 1MHz. The total current consumption in idle mode with TIMER1, ADC, and SPI<br/>enabled, gives:

$\text{ICC}_{\text{total}} \approx 0.115 \ \text{mA} \cdot (1 + 0.105 + 0.168 + 0.129) \approx 0.161 \ \text{mA}$

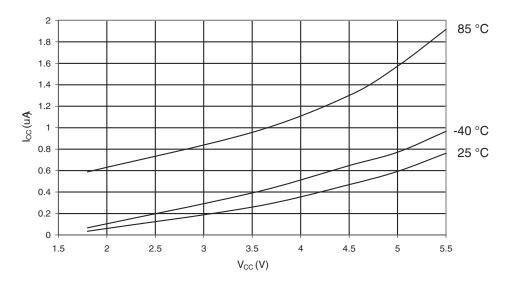

#### 26.1.4 Power-down Supply Current

Figure 26-11. Power-down Supply Current vs. V<sub>CC</sub> (Watchdog Timer Disabled).

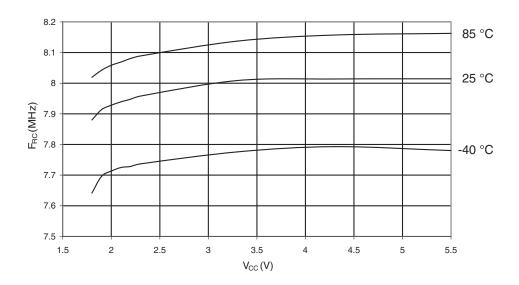

Figure 26-36. Calibrated 8 MHz RC Oscillator Frequency vs. V<sub>CC</sub>.

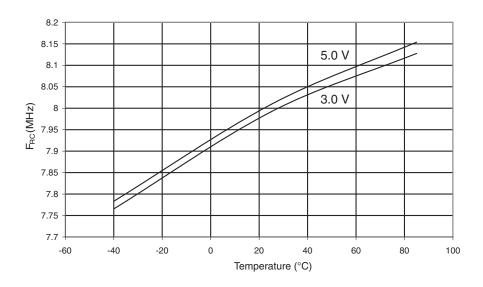

Figure 26-37. Calibrated 8 MHz RC Oscillator Frequency vs. Temperature.

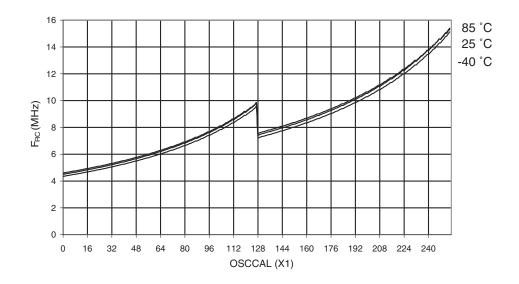

Figure 26-38. Calibrated 8 MHz RC Oscillator Frequency vs. OSCCAL Value.

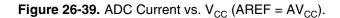

## 26.1.12 Current Consumption of Peripheral Units

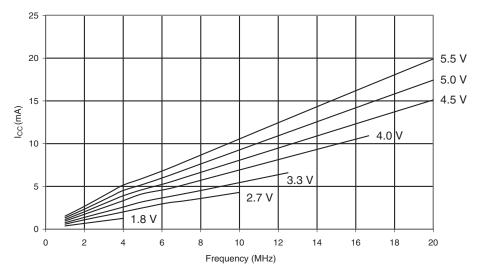

# 26.3 ATmega644P Typical Characteristic

## 26.3.1 Active Supply Current

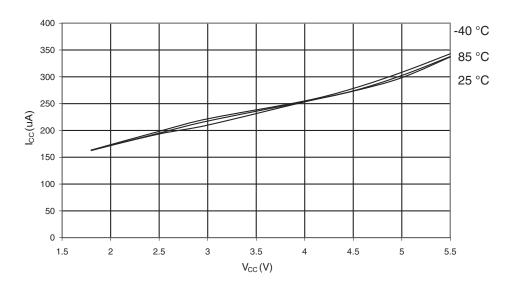

Figure 26-95. Active Supply Current vs. Low Frequency (0.1 - 1.0 MHz).

Figure 26-96. Active Supply Current vs. Frequency (1 - 20 MHz).

| Address     | Name     | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Page |

|-------------|----------|--------|--------|--------|--------|--------|--------|--------|--------|------|

| 0x1C (0x3C) | EIFR     | -      | -      | -      | -      | -      | INTF2  | INTF1  | INTF0  | 68   |

| 0x1B (0x3B) | PCIFR    | -      | -      | -      | -      | PCIF3  | PCIF2  | PCIF1  | PCIF0  | 69   |

| 0x1A (0x3A) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x19 (0x39) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x18 (0x38) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x17 (0x37) | TIFR2    | -      | -      | -      | -      | -      | OCF2B  | OCF2A  | TOV2   | 159  |

| 0x16 (0x36) | TIFR1    | -      | -      | ICF1   | -      | -      | OCF1B  | OCF1A  | TOV1   | 138  |

| 0x15 (0x35) | TIFR0    | -      | -      | -      | -      | -      | OCF0B  | OCF0A  | TOV0   | 109  |

| 0x14 (0x34) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x13 (0x33) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x12 (0x32) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x11 (0x31) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x10 (0x30) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x0F (0x2F) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x0E (0x2E) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x0D (0x2D) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x0C (0x2C) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x0B (0x2B) | PORTD    | PORTD7 | PORTD6 | PORTD5 | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 | 92   |

| 0x0A (0x2A) | DDRD     | DDD7   | DDD6   | DDD5   | DDD4   | DDD3   | DDD2   | DDD1   | DDD0   | 92   |

| 0x09 (0x29) | PIND     | PIND7  | PIND6  | PIND5  | PIND4  | PIND3  | PIND2  | PIND1  | PIND0  | 92   |

| 0x08 (0x28) | PORTC    | PORTC7 | PORTC6 | PORTC5 | PORTC4 | PORTC3 | PORTC2 | PORTC1 | PORTC0 | 92   |

| 0x07 (0x27) | DDRC     | DDC7   | DDC6   | DDC5   | DDC4   | DDC3   | DDC2   | DDC1   | DDC0   | 92   |

| 0x06 (0x26) | PINC     | PINC7  | PINC6  | PINC5  | PINC4  | PINC3  | PINC2  | PINC1  | PINC0  | 92   |

| 0x05 (0x25) | PORTB    | PORTB7 | PORTB6 | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 | 91   |

| 0x04 (0x24) | DDRB     | DDB7   | DDB6   | DDB5   | DDB4   | DDB3   | DDB2   | DDB1   | DDB0   | 91   |

| 0x03 (0x23) | PINB     | PINB7  | PINB6  | PINB5  | PINB4  | PINB3  | PINB2  | PINB1  | PINB0  | 91   |

| 0x02 (0x22) | PORTA    | PORTA7 | PORTA6 | PORTA5 | PORTA4 | PORTA3 | PORTA2 | PORTA1 | PORTA0 | 91   |

| 0x01 (0x21) | DDRA     | DDA7   | DDA6   | DDA5   | DDA4   | DDA3   | DDA2   | DDA1   | DDA0   | 91   |

| 0x00 (0x20) | PINA     | PINA7  | PINA6  | PINA5  | PINA4  | PINA3  | PINA2  | PINA1  | PINA0  | 91   |

Notes: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

2. I/O registers within the address range \$00 - \$1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions.

3. Some of the status flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate on all bits in the I/O register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

4. When using the I/O specific commands IN and OUT, the I/O addresses \$00 - \$3F must be used. When addressing I/O registers as data space using LD and ST instructions, \$20 must be added to these addresses. The ATmega164P/324P/644P is a complex microcontroller with more peripheral units than can be supported within the 64 location reserved in Opcode for the IN and OUT instructions. For the Extended I/O space from \$60 - \$FF, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

# ATmega164P/324P/644P

|   | 6.5 Low Frequency Crystal Oscillator          | 34 |

|---|-----------------------------------------------|----|

|   | 6.6 Calibrated Internal RC Oscillator         | 36 |

|   | 6.7 128 kHz Internal Oscillator               | 37 |

|   | 6.8 External Clock                            | 37 |

|   | 6.9 Timer/Counter Oscillator                  | 38 |

|   | 6.10 Clock Output Buffer                      | 38 |

|   | 6.11 System Clock Prescaler                   | 38 |

|   | 6.12 Register Description                     | 40 |

| 7 | Power Management and Sleep Modes              | 42 |

|   | 7.1 Overview                                  | 42 |

|   | 7.2 Sleep Modes                               | 42 |

|   | 7.3 BOD Disable                               | 43 |

|   | 7.4 Idle Mode                                 | 43 |

|   | 7.5 ADC Noise Reduction Mode                  | 43 |

|   | 7.6 Power-down Mode                           | 44 |

|   | 7.7 Power-save Mode                           | 44 |

|   | 7.8 Standby Mode                              | 44 |

|   | 7.9 Extended Standby Mode                     | 44 |

|   | 7.10 Power Reduction Register                 | 45 |

|   | 7.11 Minimizing Power Consumption             | 45 |

|   | 7.12 Register Description                     | 47 |

| 8 | System Control and Reset                      | 50 |

|   | 8.1 Resetting the AVR                         | 50 |

|   | 8.2 Reset Sources                             | 50 |

|   | 8.3 Power-on Reset                            | 51 |

|   | 8.4 External Reset                            | 52 |

|   | 8.5 Brown-out Detection                       | 53 |

|   | 8.6 Watchdog Reset                            | 53 |

|   | 8.7 Internal Voltage Reference                | 54 |

|   | 8.8 Watchdog Timer                            | 55 |

|   | 8.9 Register Description                      | 58 |

| 9 | Interrupts                                    | 61 |

|   | 9.1 Overview                                  | 61 |

|   | 9.2 Interrupt Vectors in ATmega164P/324P/644P | 61 |

|   | 9.3 Register Description                      | 65 |