Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                             |  |

|----------------------------|-------------------------------------------------------------|--|

| Product Status             | Active                                                      |  |

| Core Processor             | AVR                                                         |  |

| Core Size                  | 8-Bit                                                       |  |

| Speed                      | 10MHz                                                       |  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                           |  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                       |  |

| Number of I/O              | 32                                                          |  |

| Program Memory Size        | 64KB (32K x 16)                                             |  |

| Program Memory Type        | FLASH                                                       |  |

| EEPROM Size                | 2K x 8                                                      |  |

| RAM Size                   | 4K x 8                                                      |  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                 |  |

| Data Converters            | A/D 8x10b                                                   |  |

| Oscillator Type            | Internal                                                    |  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |  |

| Mounting Type              | Through Hole                                                |  |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                    |  |

| Supplier Device Package    | 40-PDIP                                                     |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/atmega644pv-10pu |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

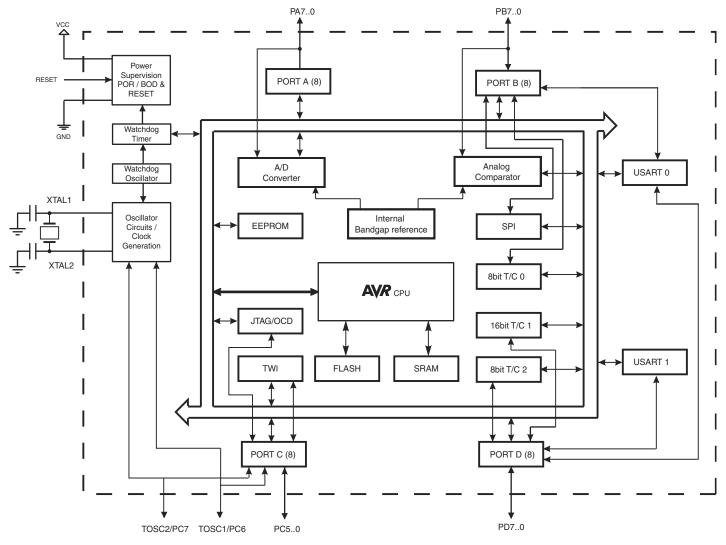

# 2. Overview

The ATmega164P/324P/644P is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega164P/324P/644P achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

## 2.1 Block Diagram

Figure 2-1. Block Diagram

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

Clk<sub>CPU</sub>

1st Instruction Fetch

1st Instruction Execute

2nd Instruction Fetch

2nd Instruction Execute

3rd Instruction Fetch

3rd Instruction Execute

4th Instruction Fetch

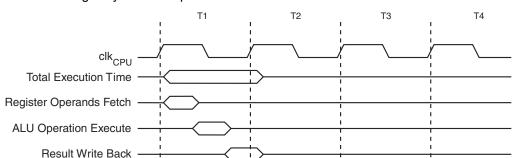

Figure 4-5. The Parallel Instruction Fetches and Instruction Executions

Figure 4-6 shows the internal timing concept for the Register File. In a single clock cycle an ALU operation using two register operands is executed, and the result is stored back to the destination register.

Figure 4-6. Single Cycle ALU Operation

### 4.7 Reset and Interrupt Handling

The AVR provides several different interrupt sources. These interrupts and the separate Reset Vector each have a separate program vector in the program memory space. All interrupts are assigned individual enable bits which must be written logic one together with the Global Interrupt Enable bit in the Status Register in order to enable the interrupt. Depending on the Program Counter value, interrupts may be automatically disabled when Boot Lock bits BLB02 or BLB12 are programmed. This feature improves software security. See the section "Memory Programming" on page 293 for details.

The lowest addresses in the program memory space are by default defined as the Reset and Interrupt Vectors. The complete list of vectors is shown in "Interrupts" on page 61. The list also determines the priority levels of the different interrupts. The lower the address the higher is the priority level. RESET has the highest priority, and next is INTO – the External Interrupt Request 0. The Interrupt Vectors can be moved to the start of the Boot Flash section by setting the IVSEL bit in the MCU Control Register (MCUCR). Refer to "Interrupts" on page 61 for more information. The Reset Vector can also be moved to the start of the Boot Flash section by programming the BOOTRST Fuse, see "Memory Programming" on page 293.

When an interrupt occurs, the Global Interrupt Enable I-bit is cleared and all interrupts are disabled. The user software can write logic one to the I-bit to enable nested interrupts. All enabled

## 12.6.1 Compare Output Mode and Waveform Generation

The Waveform Generator uses the COM0x1:0 bits differently in Normal, CTC, and PWM modes. For all modes, setting the COM0x1:0 = 0 tells the Waveform Generator that no action on the OC0x Register is to be performed on the next Compare Match. For compare output actions in the non-PWM modes refer to Table 12-2 on page 104. For fast PWM mode, refer to Table 12-3 on page 104, and for phase correct PWM refer to Table 12-4 on page 105.

A change of the COM0x1:0 bits state will have effect at the first Compare Match after the bits are written. For non-PWM modes, the action can be forced to have immediate effect by using the FOC0x strobe bits.

## 12.7 Modes of Operation

The mode of operation, i.e., the behavior of the Timer/Counter and the Output Compare pins, is defined by the combination of the Waveform Generation mode (WGM02:0) and Compare Output mode (COM0x1:0) bits. The Compare Output mode bits do not affect the counting sequence, while the Waveform Generation mode bits do. The COM0x1:0 bits control whether the PWM output generated should be inverted or not (inverted or non-inverted PWM). For non-PWM modes the COM0x1:0 bits control whether the output should be set, cleared, or toggled at a Compare Match (See Section "13.8" on page 122.).

For detailed timing information see "Timer/Counter Timing Diagrams" on page 102.

#### 12.7.1 Normal Mode

The simplest mode of operation is the Normal mode (WGM02:0 = 0). In this mode the counting direction is always up (incrementing), and no counter clear is performed. The counter simply overruns when it passes its maximum 8-bit value (TOP = 0xFF) and then restarts from the bottom (0x00). In normal operation the Timer/Counter Overflow Flag (TOV0) will be set in the same timer clock cycle as the TCNT0 becomes zero. The TOV0 Flag in this case behaves like a ninth bit, except that it is only set, not cleared. However, combined with the timer overflow interrupt that automatically clears the TOV0 Flag, the timer resolution can be increased by software. There are no special cases to consider in the Normal mode, a new counter value can be written anytime.

The Output Compare Unit can be used to generate interrupts at some given time. Using the Output Compare to generate waveforms in Normal mode is not recommended, since this will occupy too much of the CPU time.

## 12.7.2 Clear Timer on Compare Match (CTC) Mode

In Clear Timer on Compare or CTC mode (WGM02:0 = 2), the OCR0A Register is used to manipulate the counter resolution. In CTC mode the counter is cleared to zero when the counter value (TCNT0) matches the OCR0A. The OCR0A defines the top value for the counter, hence also its resolution. This mode allows greater control of the Compare Match output frequency. It also simplifies the operation of counting external events.

The timing diagram for the CTC mode is shown in Figure 12-5. The counter value (TCNT0) increases until a Compare Match occurs between TCNT0 and OCR0A, and then counter (TCNT0) is cleared.

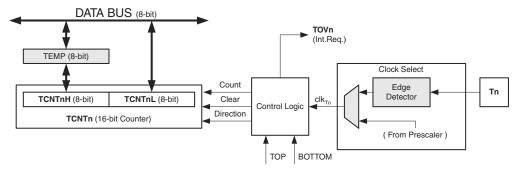

#### 13.5 Counter Unit

The main part of the 16-bit Timer/Counter is the programmable 16-bit bi-directional counter unit. Figure 13-2 shows a block diagram of the counter and its surroundings.

Figure 13-2. Counter Unit Block Diagram

Signal description (internal signals):

Count Increment or decrement TCNTn by 1.

**Direction** Select between increment and decrement.

Clear TCNTn (set all bits to zero).

**clk**<sub>Tn</sub> Timer/Counter clock.

**TOP** Signalize that TCNTn has reached maximum value.

**BOTTOM** Signalize that TCNTn has reached minimum value (zero).

The 16-bit counter is mapped into two 8-bit I/O memory locations: *Counter High* (TCNTnH) containing the upper eight bits of the counter, and *Counter Low* (TCNTnL) containing the lower eight bits. The TCNTnH Register can only be indirectly accessed by the CPU. When the CPU does an access to the TCNTnH I/O location, the CPU accesses the high byte temporary register (TEMP). The temporary register is updated with the TCNTnH value when the TCNTnL is read, and TCNTnH is updated with the temporary register value when TCNTnL is written. This allows the CPU to read or write the entire 16-bit counter value within one clock cycle via the 8-bit data bus. It is important to notice that there are special cases of writing to the TCNTn Register when the counter is counting that will give unpredictable results. The special cases are described in the sections where they are of importance.

Depending on the mode of operation used, the counter is cleared, incremented, or decremented at each *timer clock* ( $clk_{Tn}$ ). The  $clk_{Tn}$  can be generated from an external or internal clock source, selected by the *Clock Select* bits (CSn2:0). When no clock source is selected (CSn2:0 = 0) the timer is stopped. However, the TCNTn value can be accessed by the CPU, independent of whether  $clk_{Tn}$  is present or not. A CPU write overrides (has priority over) all counter clear or count operations.

The counting sequence is determined by the setting of the *Waveform Generation mode* bits (WGMn3:0) located in the *Timer/Counter Control Registers* A and B (TCCRnA and TCCRnB). There are close connections between how the counter behaves (counts) and how waveforms are generated on the Output Compare outputs OCnx. For more details about advanced counting sequences and waveform generation, see "Modes of Operation" on page 123.

```

Assembly Code Example<sup>(1)</sup>

SPI_MasterInit:

; Set MOSI and SCK output, all others input

ldi r17, (1<<DD_MOSI) | (1<<DD_SCK)

out DDR_SPI,r17

; Enable SPI, Master, set clock rate fck/16

ldi r17, (1<<SPE) | (1<<MSTR) | (1<<SPR0)

out SPCR, r17

ret

SPI_MasterTransmit:

; Start transmission of data (r16)

out SPDR, r16

Wait_Transmit:

; Wait for transmission complete

sbis SPSR, SPIF

rjmp Wait_Transmit

ret

C Code Example<sup>(1)</sup>

void SPI_MasterInit(void)

/* Set MOSI and SCK output, all others input */

DDR_SPI = (1<<DD_MOSI) | (1<<DD_SCK);</pre>

/* Enable SPI, Master, set clock rate fck/16 */

SPCR = (1<<SPE) | (1<<MSTR) | (1<<SPR0);

void SPI_MasterTransmit(char cData)

/* Start transmission */

SPDR = cData;

/* Wait for transmission complete */

while(!(SPSR & (1<<SPIF)))</pre>

```

Note: 1. See "About Code Examples" on page 8.

#### • Bit 0 - UCPOLn: Clock Polarity

This bit is used for synchronous mode only. Write this bit to zero when asynchronous mode is used. The UCPOLn bit sets the relationship between data output change and data input sample, and the synchronous clock (XCKn).

Table 16-8. UCPOLn Bit Settings

| UCPOLn | Transmitted Data Changed (Output of TxDn Pin) | Received Data Sampled (Input on RxDn Pin) |  |  |

|--------|-----------------------------------------------|-------------------------------------------|--|--|

| 0      | Rising XCKn Edge                              | Falling XCKn Edge                         |  |  |

| 1      | Falling XCKn Edge                             | Rising XCKn Edge                          |  |  |

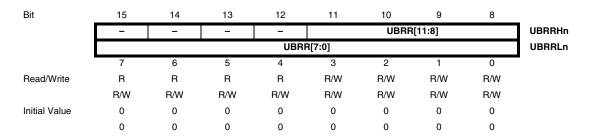

#### 16.11.5 UBRRnL and UBRRnH – USART Baud Rate Registers

#### Bit 15:12 – Reserved Bits

These bits are reserved for future use. For compatibility with future devices, these bit must be written to zero when UBRRH is written.

### • Bit 11:0 - UBRR11:0: USART Baud Rate Register

This is a 12-bit register which contains the USART baud rate. The UBRRH contains the four most significant bits, and the UBRRL contains the eight least significant bits of the USART baud rate. Ongoing transmissions by the Transmitter and Receiver will be corrupted if the baud rate is changed. Writing UBRRL will trigger an immediate update of the baud rate prescaler.

# ATmega164P/324P/644P

This scheme is repeated until the last byte has been sent and the transfer is ended by generating a STOP condition or a repeated START condition. A STOP condition is generated by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| value | 1     | Х    | 0     | 1     | Х    | 1    | 0 | Х    |

A REPEATED START condition is generated by writing the following value to TWCR:

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| value | 1     | Х    | 1     | 0     | Х    | 1    | 0 | Х    |

After a repeated START condition (state 0x10) the 2-wire Serial Interface can access the same Slave again, or a new Slave without transmitting a STOP condition. Repeated START enables the Master to switch between Slaves, Master Transmitter mode and Master Receiver mode without losing control of the bus.

Table 18-2. Status codes for Master Transmitter Mode

| Status Code              |                                                                   | Application Software Response |     |     | onse  |      |                                                                                                                        |

|--------------------------|-------------------------------------------------------------------|-------------------------------|-----|-----|-------|------|------------------------------------------------------------------------------------------------------------------------|

| (TWSR)<br>Prescaler Bits | Status of the 2-wire Serial Bus and 2-wire Serial Interface Hard- | - TO/HOILL TWOK               |     |     |       |      |                                                                                                                        |

| are 0                    | ware                                                              |                               | STA | STO | TWINT | TWEA | Next Action Taken by TWI Hardware                                                                                      |

| 0x08                     | A START condition has been transmitted                            | Load SLA+W                    | 0   | 0   | 1     | Х    | SLA+W will be transmitted;<br>ACK or NOT ACK will be received                                                          |

| 0x10                     | A repeated START condition has been transmitted                   | Load SLA+W or                 | 0   | 0   | 1     | X    | SLA+W will be transmitted;<br>ACK or NOT ACK will be received                                                          |

|                          |                                                                   | Load SLA+R                    | 0   | 0   | 1     | Х    | SLA+R will be transmitted;<br>Logic will switch to Master Receiver mode                                                |

| 0x18                     | SLA+W has been transmitted;<br>ACK has been received              | Load data byte or             | 0   | 0   | 1     | Х    | Data byte will be transmitted and ACK or NOT ACK will be received                                                      |

|                          |                                                                   | No TWDR action or             | 1   | 0   | 1     | Х    | Repeated START will be transmitted                                                                                     |

|                          |                                                                   | No TWDR action or             | 0   | 1   | 1     | X    | STOP condition will be transmitted and                                                                                 |

|                          |                                                                   | No TWDR action                | 1   | 1   | 1     | X    | TWSTO Flag will be reset STOP condition followed by a START condition will be transmitted and TWSTO Flag will be reset |

| 0x20                     | SLA+W has been transmitted;                                       | Load data byte or             | 0   | 0   | 1     | Х    | Data byte will be transmitted and ACK or NOT ACK will                                                                  |

|                          | NOT ACK has been received                                         |                               |     |     |       |      | be received                                                                                                            |

|                          |                                                                   | No TWDR action or             | 1   | 0   | 1     | Х    | Repeated START will be transmitted                                                                                     |

|                          |                                                                   | No TWDR action or             | 0   | 1   | 1     | Х    | STOP condition will be transmitted and                                                                                 |

|                          |                                                                   | No TWDR action                | 1   | 1   | 1     | х    | TWSTO Flag will be reset STOP condition followed by a START condition will be transmitted and TWSTO Flag will be reset |

| 0x28                     | Data byte has been transmitted; ACK has been received             | Load data byte or             | 0   | 0   | 1     | Х    | Data byte will be transmitted and ACK or NOT ACK will be received                                                      |

|                          |                                                                   | No TWDR action or             | 1   | 0   | 1     | Х    | Repeated START will be transmitted                                                                                     |

|                          |                                                                   | No TWDR action or             | 0   | 1   | 1     | Х    | STOP condition will be transmitted and TWSTO Flag will be reset                                                        |

|                          |                                                                   | No TWDR action                | 1   | 1   | 1     | Х    | STOP condition followed by a START condition will be transmitted and TWSTO Flag will be reset                          |

| 0x30                     | Data byte has been transmitted;<br>NOT ACK has been received      | Load data byte or             | 0   | 0   | 1     | Х    | Data byte will be transmitted and ACK or NOT ACK will be received                                                      |

|                          |                                                                   | No TWDR action or             | 1   | 0   | 1     | Х    | Repeated START will be transmitted                                                                                     |

|                          |                                                                   | No TWDR action or             | 0   | 1   | 1     | X    | STOP condition will be transmitted and                                                                                 |

|                          |                                                                   | No TWDR action                | 1   | 1   | 1     | Х    | TWSTO Flag will be reset STOP condition followed by a START condition will be transmitted and TWSTO Flag will be reset |

| 0x38                     | Arbitration lost in SLA+W or data bytes                           | No TWDR action or             | 0   | 0   | 1     | Х    | 2-wire Serial Bus will be released and not addressed Slave mode entered                                                |

|                          | .,                                                                | No TWDR action                | 1   | 0   | 1     | Х    | A START condition will be transmitted when the bus becomes free                                                        |

# ATmega164P/324P/644P

The upper 7 bits are the address to which the 2-wire Serial Interface will respond when addressed by a Master. If the LSB is set, the TWI will respond to the general call address (0x00), otherwise it will ignore the general call address.

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| value | 0     | 1    | 0     | 0     | 0    | 1    | 0 | Х    |

TWEN must be written to one to enable the TWI. The TWEA bit must be written to one to enable the acknowledgement of the device's own slave address or the general call address. TWSTA and TWSTO must be written to zero.

When TWAR and TWCR have been initialized, the TWI waits until it is addressed by its own slave address (or the general call address if enabled) followed by the data direction bit. If the direction bit is "0" (write), the TWI will operate in SR mode, otherwise ST mode is entered. After its own slave address and the write bit have been received, the TWINT Flag is set and a valid status code can be read from TWSR. The status code is used to determine the appropriate software action. The appropriate action to be taken for each status code is detailed in Table 18-4 on page 226. The Slave Receiver mode may also be entered if arbitration is lost while the TWI is in the Master mode (see states 0x68 and 0x78).

If the TWEA bit is reset during a transfer, the TWI will return a "Not Acknowledge" ("1") to SDA after the next received data byte. This can be used to indicate that the Slave is not able to receive any more bytes. While TWEA is zero, the TWI does not acknowledge its own slave address. However, the 2-wire Serial Bus is still monitored and address recognition may resume at any time by setting TWEA. This implies that the TWEA bit may be used to temporarily isolate the TWI from the 2-wire Serial Bus.

In all sleep modes other than Idle mode, the clock system to the TWI is turned off. If the TWEA bit is set, the interface can still acknowledge its own slave address or the general call address by using the 2-wire Serial Bus clock as a clock source. The part will then wake up from sleep and the TWI will hold the SCL clock low during the wake up and until the TWINT Flag is cleared (by writing it to one). Further data reception will be carried out as normal, with the AVR clocks running as normal. Observe that if the AVR is set up with a long start-up time, the SCL line may be held low for a long time, blocking other data transmissions.

Note that the 2-wire Serial Interface Data Register – TWDR does not reflect the last byte present on the bus when waking up from these Sleep modes.

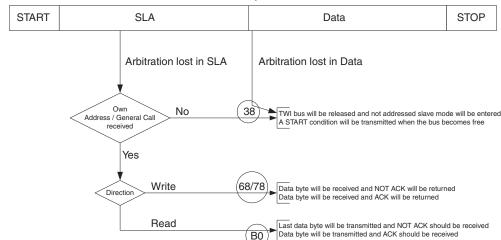

• Two or more masters are accessing different slaves. In this case, arbitration will occur in the SLA bits. Masters trying to output a one on SDA while another Master outputs a zero will lose the arbitration. Masters losing arbitration in SLA will switch to Slave mode to check if they are being addressed by the winning Master. If addressed, they will switch to SR or ST mode, depending on the value of the READ/WRITE bit. If they are not being addressed, they will switch to not addressed Slave mode or wait until the bus is free and transmit a new START condition, depending on application software action.

This is summarized in Figure 18-21. Possible status values are given in circles.

Figure 18-21. Possible Status Codes Caused by Arbitration

# 18.9 Register Description

#### 18.9.1 TWBR - TWI Bit Rate Register

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |      |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| (0xB8)        | TWBR7 | TWBR6 | TWBR5 | TWBR4 | TWBR3 | TWBR2 | TWBR1 | TWBR0 | TWBR |

| Read/Write    | R/W   | 1    |

| Initial Value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |      |

#### • Bits 7:0 - TWI Bit Rate Register

TWBR selects the division factor for the bit rate generator. The bit rate generator is a frequency divider which generates the SCL clock frequency in the Master modes. See "Bit Rate Generator Unit" on page 213 for calculating bit rates.

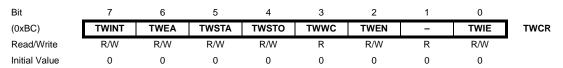

#### 18.9.2 TWCR – TWI Control Register

The TWCR is used to control the operation of the TWI. It is used to enable the TWI, to initiate a Master access by applying a START condition to the bus, to generate a Receiver acknowledge, to generate a stop condition, and to control halting of the bus while the data to be written to the

of a lost bus arbitration, no data is lost in the transition from Master to Slave. Handling of the ACK bit is controlled automatically by the TWI logic, the CPU cannot access the ACK bit directly.

#### Bits 7:0 – TWD: TWI Data Register

These eight bits constitute the next data byte to be transmitted, or the latest data byte received on the 2-wire Serial Bus.

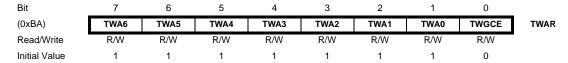

#### 18.9.5 TWAR - TWI (Slave) Address Register

The TWAR should be loaded with the 7-bit Slave address (in the seven most significant bits of TWAR) to which the TWI will respond when programmed as a Slave Transmitter or Receiver, and not needed in the Master modes. In multimaster systems, TWAR must be set in masters which can be addressed as Slaves by other Masters.

The LSB of TWAR is used to enable recognition of the general call address (0x00). There is an associated address comparator that looks for the slave address (or general call address if enabled) in the received serial address. If a match is found, an interrupt request is generated.

#### Bits 7:1 – TWA: TWI (Slave) Address Register

These seven bits constitute the slave address of the TWI unit.

#### Bit 0 – TWGCE: TWI General Call Recognition Enable Bit

If set, this bit enables the recognition of a General Call given over the 2-wire Serial Bus.

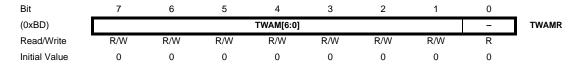

### 18.9.6 TWAMR – TWI (Slave) Address Mask Register

#### • Bits 7:1 - TWAM: TWI Address Mask

The TWAMR can be loaded with a 7-bit Slave Address mask. Each of the bits in TWAMR can mask (disable) the corresponding address bit in the TWI Address Register (TWAR). If the mask bit is set to one then the address match logic ignores the compare between the incoming address bit and the corresponding bit in TWAR. Figure 18-22 shows the address match logic in detail.

Table 20-4.

Input Channel and Gain Selections

| MUX40                | Single Ended<br>Input   | Positive Differential Input | Negative Differential Input | Gain |

|----------------------|-------------------------|-----------------------------|-----------------------------|------|

| 00000                | ADC0                    |                             |                             |      |

| 00001                | ADC1                    |                             |                             |      |

| 00010                | ADC2                    |                             |                             |      |

| 00011                | ADC3                    | N/A                         |                             |      |

| 00100                | ADC4                    |                             |                             |      |

| 00101                | ADC5                    |                             |                             |      |

| 00110                | ADC6                    |                             |                             |      |

| 00111                | ADC7                    |                             |                             |      |

| 01000                |                         | ADC0                        | ADC0                        | 10x  |

| 01001                |                         | ADC1                        | ADC0                        | 10x  |

| 01010 <sup>(1)</sup> |                         | ADC0                        | ADC0                        | 200x |

| 01011 <sup>(1)</sup> |                         | ADC1                        | ADC0                        | 200x |

| 01100                |                         | ADC2                        | ADC2                        | 10x  |

| 01101                |                         | ADC3                        | ADC2                        | 10x  |

| 01110 <sup>(1)</sup> |                         | ADC2                        | ADC2                        | 200x |

| 01111 <sup>(1)</sup> |                         | ADC3                        | ADC2                        | 200x |

| 10000                |                         | ADC0                        | ADC1                        | 1x   |

| 10001                |                         | ADC1                        | ADC1                        | 1x   |

| 10010                | N/A                     | ADC2                        | ADC1                        | 1x   |

| 10011                |                         | ADC3                        | ADC1                        | 1x   |

| 10100                |                         | ADC4                        | ADC1                        | 1x   |

| 10101                |                         | ADC5                        | ADC1                        | 1x   |

| 10110                |                         | ADC6                        | ADC1                        | 1x   |

| 10111                |                         | ADC7                        | ADC1                        | 1x   |

| 11000                |                         | ADC0                        | ADC2                        | 1x   |

| 11001                |                         | ADC1                        | ADC2                        | 1x   |

| 11010                |                         | ADC2                        | ADC2                        | 1x   |

| 11011                |                         | ADC3                        | ADC2                        | 1x   |

| 11100                |                         | ADC4                        | ADC2                        | 1x   |

| 11101                |                         | ADC5                        | ADC2                        | 1x   |

| 11110                | 1.1V (V <sub>BG</sub> ) | NI/A                        |                             |      |

| 11111                | 0 V (GND)               | N/A                         |                             |      |

Note: 1. The differential input channels are not tested for devices in PDIP Package. This feature is only guaranteed to work for devices in TQFP and VQFN/QFN/MLF Packages

#### 24.10.15 Performing Chip Erase

- 1. Enter JTAG instruction PROG\_COMMANDS.

- 2. Start Chip Erase using programming instruction 1a.

- Poll for Chip Erase complete using programming instruction 1b, or wait for t<sub>WLRH\_CE</sub> (refer to Table 24-14 on page 306).

#### 24.10.16 Programming the Flash

Before programming the Flash a Chip Erase must be performed, see "Performing Chip Erase" on page 322.

- 1. Enter JTAG instruction PROG\_COMMANDS.

- 2. Enable Flash write using programming instruction 2a.

- 3. Load address Extended High byte using programming instruction 2b.

- Load address High byte using programming instruction 2c.

- 5. Load address Low byte using programming instruction 2d.

- 6. Load data using programming instructions 2e, 2f and 2g.

- 7. Repeat steps 5 and 6 for all instruction words in the page.

- 8. Write the page using programming instruction 2h.

- Poll for Flash write complete using programming instruction 2i, or wait for t<sub>WLRH</sub> (refer to Table 24-14 on page 306).

- 10. Repeat steps 3 to 9 until all data have been programmed.

A more efficient data transfer can be achieved using the PROG\_PAGELOAD instruction:

- 1. Enter JTAG instruction PROG\_COMMANDS.

- 2. Enable Flash write using programming instruction 2a.

- Load the page address using programming instructions 2b, 2c and 2d. PCWORD (refer to Table 24-7 on page 296) is used to address within one page and must be written as 0.

- Enter JTAG instruction PROG\_PAGELOAD.

- 5. Load the entire page by shifting in all instruction words in the page byte-by-byte, starting with the LSB of the first instruction in the page and ending with the MSB of the last instruction in the page. Use Update-DR to copy the contents of the Flash Data Byte Register into the Flash page location and to auto-increment the Program Counter before each new word.

- 6. Enter JTAG instruction PROG COMMANDS.

- 7. Write the page using programming instruction 2h.

- 8. Poll for Flash write complete using programming instruction 2i, or wait for t<sub>WLRH</sub> (refer to Table 24-14 on page 306).

- 9. Repeat steps 3 to 8 until all data have been programmed.

#### 24.10.17 Reading the Flash

- Enter JTAG instruction PROG\_COMMANDS.

- 2. Enable Flash read using programming instruction 3a.

- 3. Load address using programming instructions 3b, 3c and 3d.

- 4. Read data using programming instruction 3e.

- 5. Repeat steps 3 and 4 until all data have been read.

A more efficient data transfer can be achieved using the PROG\_PAGEREAD instruction:

# ATmega164P/324P/644P

$T_A = -40$ °C to 85°C,  $V_{CC} = 1.8$ V to 5.5V (unless otherwise noted) (Continued)

| Symbol            | Parameter                                  | Condition                                        | Min. | Тур.       | Max. | Units |

|-------------------|--------------------------------------------|--------------------------------------------------|------|------------|------|-------|

| V <sub>ACIO</sub> | Analog Comparator<br>Input Offset Voltage  | $V_{CC} = 5V$ $V_{in} = V_{CC}/2$                |      | <10        | 40   | mV    |

| I <sub>ACLK</sub> | Analog Comparator<br>Input Leakage Current | $V_{CC} = 5V$ $V_{in} = V_{CC}/2$                | -50  |            | 50   | nA    |

| t <sub>ACID</sub> | Analog Comparator<br>Propagation Delay     | V <sub>CC</sub> = 2.7V<br>V <sub>CC</sub> = 4.0V |      | 750<br>500 |      | ns    |

- Notes: 1. "Max" means the highest value where the pin is guaranteed to be read as low

- 2. "Min" means the lowest value where the pin is guaranteed to be read as high

- 3. Although each I/O port can sink more than the test conditions (20 mA at VCC = 5V, 10 mA at VCC = 3V) under steady state conditions (non-transient), the following must be observed:

- 1.) The sum of all IOL, for ports PB0-PB7, XTAL2, PD0-PD7 should not exceed 100 mA.

- 2.) The sum of all IOL, for ports PA0-PA3, PC0-PC7 should not exceed 100 mA.

- If IOL exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test condition.

- 4. Although each I/O port can source more than the test conditions (20 mA at VCC = 5V, 10 mA at VCC = 3V) under steady state conditions (non-transient), the following must be observed:

- 1.) The sum of all IOH, for ports PB0-PB7, XTAL2, PD0-PD7 should not exceed 100 mA.

- 2.) The sum of all IOH, for ports PA0-PA3, PC0-PC7 should not exceed 100 mA.

- If IOH exceeds the test condition, VOH may exceed the related specification. Pins are not guaranteed to source current greater than the listed test condition.

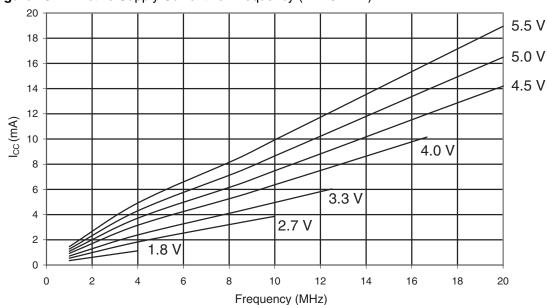

Figure 26-2. Active Supply Current vs. Frequency (1 - 20 MHz).

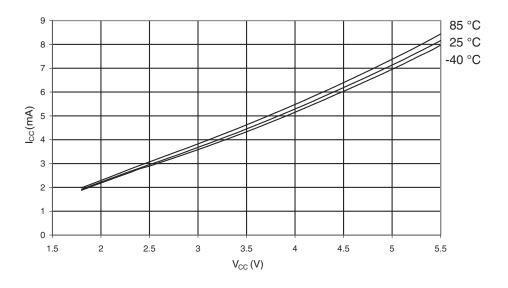

Figure 26-3. Active Supply Current vs.  $V_{CC}$  (Internal RC Oscillator, 8 MHz).

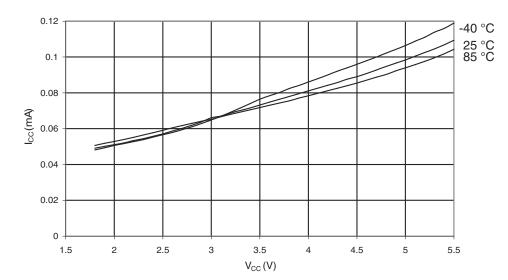

**Figure 26-10.** Idle Supply Current vs.  $V_{CC}$  (Internal RC Oscillator, 128 kHz).

## 26.1.3 Supply Current of IO modules

The tables and formulas below can be used to calculate the additional current consumption for the different I/O modules in Active and Idle mode. The enabling or disabling of the I/O modules are controlled by the Power Reduction Register. See "PRR – Power Reduction Register" on page 48 for details.

| PRR bit  | Typical numbers                |                                |                                |

|----------|--------------------------------|--------------------------------|--------------------------------|

|          | V <sub>CC</sub> = 2V, F = 1MHz | V <sub>CC</sub> = 3V, F = 4MHz | V <sub>CC</sub> = 5V, F = 8MHz |

| PRUSART1 | 6.0 uA                         | 38.5 uA                        | 150.0 uA                       |

| PRUSART0 | 7.9 uA                         | 50.3 uA                        | 197.0 uA                       |

| PRTWI    | 16.9 uA                        | 116.2 uA                       | 489.3 uA                       |

| PRTIM2   | 14.4 uA                        | 95.8 uA                        | 393.2 uA                       |

| PRTIM1   | 9.0 uA                         | 57.3 uA                        | 234.8 uA                       |

| PRTIM0   | 5.1uA                          | 33.3 uA                        | 132.5 uA                       |

| PRADC    | 18.1 uA                        | 86.3 uA                        | 335.3 uA                       |

| PRSPI    | 11.1 uA                        | 70.5 uA                        | 285.0 uA                       |

# 26.1.6 Standby Supply Current

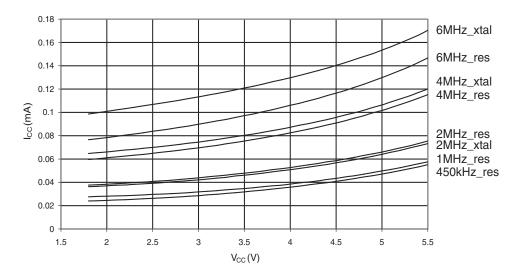

**Figure 26-14.** Standby Supply Current vs.  $V_{CC}$  (Watchdog Timer Disabled).

#### 26.1.7 Pin Pull-up

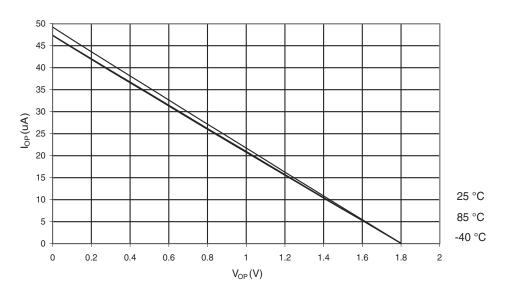

**Figure 26-15.** I/O Pin Pull-up Resistor Current vs. Input Voltage ( $V_{CC} = 1.8V$ ).

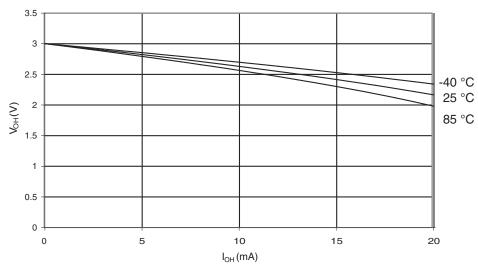

**Figure 26-70.** I/O Pin Output Voltage vs. Source Current ( $V_{CC} = 3V$ ).

Figure 26-71. I/O Pin Output Voltage vs. Source Current ( $V_{CC} = 5V$ ).

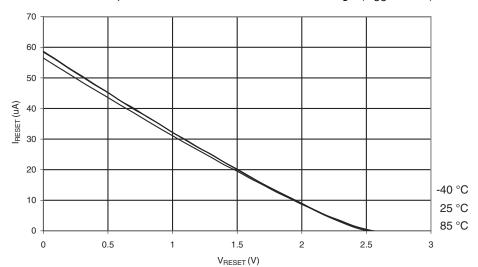

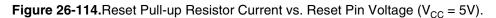

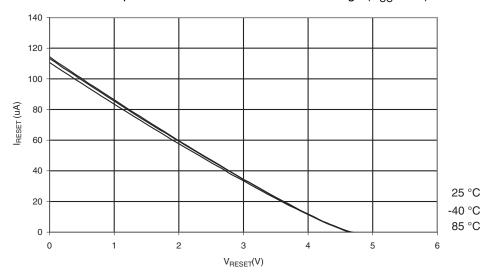

**Figure 26-113.**Reset Pull-up Resistor Current vs. Reset Pin Voltage ( $V_{CC} = 2.7V$ ).

## 32.13 Rev. 8011B - 09/06

1. Updated "DC Characteristics" on page 325.

## 32.14 Rev. 8011A - 08/06

1. Initial revision.

### Headquarters

Atmel Corporation

2325 Orchard Parkway San Jose, CA 95131 USA

Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

Atmel Asia

Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon Hong Kong

Tel: (852) 2245-6100 Fax: (852) 2722-1369 Atmel Europe

Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex

France

Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033

Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site

www.atmel.com

Technical Support

Enter Product Line E-mail

Sales Contact

www.atmel.com/contacts

Literature Requests

www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2009 Atmel Corporation. All rights reserved. Atmel logo and combinations thereof, AVR® and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.