#### Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XF

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 67MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                               |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                            |

| Number of I/O              | 38                                                                           |

| Program Memory Size        | 128KB (128K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 32K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                 |

| Data Converters            | A/D 1x12b; D/A 2x8b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 68-VFQFN Exposed Pad                                                         |

| Supplier Device Package    | 68-QFN (8x8)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c5467lti-lp003 |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1. Architectural Overview                           | 4  |

|-----------------------------------------------------|----|

| 2. Pinouts                                          | 6  |

| 3. Pin Descriptions                                 | 11 |

| 4. CPU                                              | 12 |

| 4.1 ARM Cortex-M3 CPU                               | 12 |

| 4.2 Cache Controller                                |    |

| 4.3 DMA and PHUB                                    |    |

| 4.4 Interrupt Controller                            |    |

| 5. Memory                                           | 19 |

| 5.1 Static RAM                                      |    |

| 5.2 Flash Program Memory                            | 19 |

| 5.3 Flash Security                                  |    |

| 5.4 EEPROM<br>5.5 Nonvolatile Latches (NVLs)        |    |

| 5.6 External Memory Interface                       |    |

| 5.7 Memory Map                                      |    |

|                                                     |    |

| 6. System Integration<br>6.1 Clocking System        |    |

| 6.2 Power System                                    |    |

| 6.3 Reset                                           |    |

| 6.4 I/O System and Routing                          |    |

| 7. Digital Subsystem                                |    |

| 7.1 Example Peripherals                             |    |

| 7.2 Universal Digital Block                         |    |

| 7.3 UDB Array Description                           |    |

| 7.4 DSI Routing Interface Description               | 45 |

| 7.5 USB                                             |    |

| 7.6 Timers, Counters, and PWMs                      |    |

| 7.7 l <sup>2</sup> C                                |    |

| 8. Analog Subsystem                                 |    |

| 8.1 Analog Routing                                  |    |

| 8.2 Delta-sigma ADC                                 |    |

| 8.3 Successive Approximation ADC<br>8.4 Comparators |    |

| 8.5 Opamps                                          |    |

| 8.6 Programmable SC/CT Blocks                       |    |

| 8.7 LCD Direct Drive                                |    |

| 8.8 CapSense                                        |    |

| 8.9 Temp Sensor                                     |    |

| 8.10 DAC                                            |    |

| 8.11 Up/Down Mixer                                  |    |

| 8.12 Sample and Hold                                | 60 |

| 9. Programming, Debug Interfaces, Resources | 60  |

|---------------------------------------------|-----|

| 9.1 JTAG Interface                          | 61  |

| 9.2 SWD Interface                           |     |

| 9.3 Debug Features                          | 63  |

| 9.4 Trace Features                          |     |

| 9.5 SWV and TRACEPORT Interfaces            |     |

| 9.6 Programming Features                    | 63  |

| 9.7 Device Security                         |     |

| 9.8 CSP Package Bootloader                  | 64  |

| 10. Development Support                     | 64  |

| 10.1 Documentation                          |     |

| 10.2 Online                                 |     |

| 10.3 Tools                                  | 64  |

| 11. Electrical Specifications               | 65  |

| 11.1 Absolute Maximum Ratings               |     |

| 11.2 Device Level Specifications            |     |

| 11.3 Power Regulators                       |     |

| 11.4 Inputs and Outputs                     |     |

| 11.5 Analog Peripherals                     |     |

| 11.6 Digital Peripherals                    |     |

| 11.7 Memory                                 |     |

| 11.8 PSoC System Resources                  | 109 |

| 11.9 Clocking                               | 112 |

| 12. Ordering Information                    | 116 |

| 12.1 Part Numbering Conventions             |     |

| 13. Packaging                               | 118 |

| 14. Acronyms                                |     |

| 15. Reference Documents                     |     |

| 16. Document Conventions                    | 123 |

| 16.1 Units of Measure                       |     |

| Document History Page                       |     |

| Sales, Solutions, and Legal Information     |     |

| Worldwide Sales and Design Support          |     |

| Products                                    |     |

| PSoC® Solutions                             |     |

| Cypress Developer Community                 |     |

| Technical Support                           | 120 |

|                                             |     |

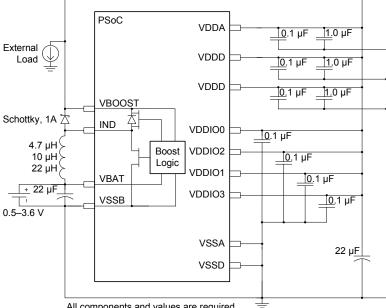

The CY8C54LP family supports a wide supply operating range from 1.71 to 5.5 V. This allows operation from regulated supplies such as  $1.8 \pm 5\%$ ,  $2.5 V \pm 10\%$ ,  $3.3 V \pm 10\%$ , or  $5.0 V \pm 10\%$ , or directly from a wide range of battery types. In addition, it provides an integrated high efficiency synchronous boost converter that can power the device from supply voltages as low as 0.5 V. This enables the device to be powered directly from a single battery. In addition, you can use the boost converter to generate other voltages required by the device, such as a 3.3 V supply for LCD glass drive. The boost's output is available on the V<sub>BOOST</sub> pin, allowing other devices in the application to be powered from the PSoC.

PSoC supports a wide range of low-power modes. These include a 300-nA hibernate mode with RAM retention and a  $2-\mu$ A sleep mode with RTC. In the second mode the optional 32.768-kHz watch crystal runs continuously and maintains an accurate RTC.

Power to all major functional blocks, including the programmable digital and analog peripherals, can be controlled independently by firmware. This allows low-power background processing when some peripherals are not in use. This, in turn, provides a total device current of only 3.1 mA when the CPU is running at 6 MHz.

The details of the PSoC power modes are covered in the "Power System" section on page 27 of this datasheet.

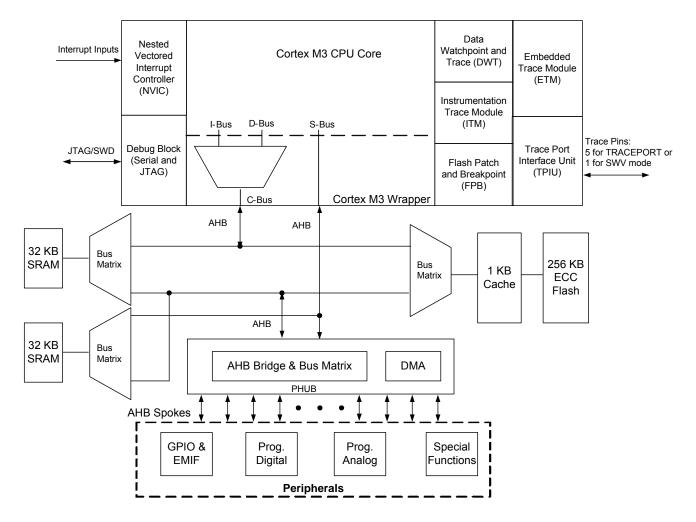

PSoC uses JTAG (4-wire) or SWD (2-wire) interfaces for programming, debug, and test. Using these standard interfaces you can debug or program the PSoC with a variety of hardware solutions from Cypress or third party vendors. The Cortex-M3 debug and trace modules include FPB, DWT, ETM, and ITM. These modules have many features to help solve difficult debug and trace problems. Details of the programming, test, and debugging interfaces are discussed in the "Programming, Debug Interfaces, Resources" section on page 60 of this datasheet.

# 2. Pinouts

Each VDDIO pin powers a specific set of I/O pins. (The USBIOs are powered from VDDD.) Using the VDDIO pins, a single PSoC can support multiple voltage levels, reducing the need for off-chip level shifters. The black lines drawn on the pinout diagrams in Figure 2-3 and Figure 2-4, as well as Table 2-1, show the pins that are powered by each VDDIO.

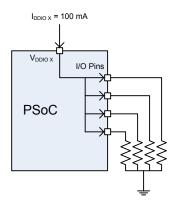

Each VDDIO may source up to 100 mA total to its associated I/O pins, as shown in Figure 2-1.

## Figure 2-1. VDDIO Current Limit

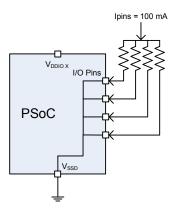

Conversely, for the 100-pin and 68-pin devices, the set of I/O pins associated with any VDDIO may sink up to 100 mA total, as shown in Figure 2-2.

## Figure 2-2. I/O Pins Current Limit

## Figure 6-6. Application of Boost Converter powering PSoC device

All components and values are required

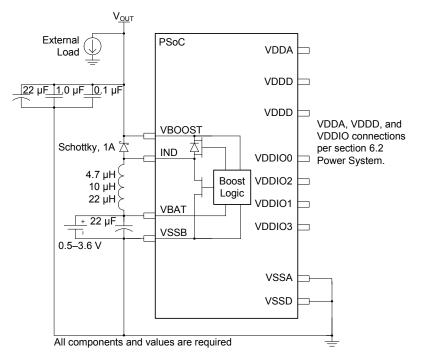

The boost converter may also generate a supply that is not used directly by the PSoC device. An example of this use case is boosting a 1.8 V supply to 4.0 V to drive a white LED. If the boost converter is not supplying the PSoC devices  $V_{DDA}$ ,  $V_{DDD}$ , and V<sub>DDIO</sub> it must comply with the same design rules as supplying the PSoC device, but with a change to the bulk capacitor requirements. A parallel arrangement 22 µF, 1.0 µF, and 0.1 µF capacitors are all required on the Vout supply and must be placed within 1 cm of the VBOOST pin to ensure regulator stability.

Figure 6-7. Application of Boost Converter not powering PSoC device

#### 6.4.13 SIO as Comparator

This section applies only to SIO pins. The adjustable input level feature of the SIOs as explained in the Adjustable Input Level section can be used to construct a comparator. The threshold for the comparator is provided by the SIO's reference generator. The reference generator has the option to set the analog signal routed through the analog global line as threshold for the comparator. Note that a pair of SIO pins share the same threshold.

The digital input path in Figure 6-10 on page 35 illustrates this functionality. In the figure, 'Reference level' is the analog signal routed through the analog global. The hysteresis feature can also be enabled for the input buffer of the SIO, which increases noise immunity for the comparator.

#### 6.4.14 Hot Swap

This section applies only to SIO pins. SIO pins support 'hot swap' capability to plug into an application without loading the signals that are connected to the SIO pins even when no power is applied to the PSoC device. This allows the unpowered PSoC to maintain a high impedance load to the external device while also preventing the PSoC from being powered through a SIO pin's protection diode.

Powering the device up or down while connected to an operational I2C bus may cause transient states on the SIO pins. The overall I2C bus design should take this into account.

#### 6.4.15 Over Voltage Tolerance

All I/O pins provide an over voltage tolerance feature at any operating VDD.

- There are no current limitations for the SIO pins as they present a high impedance load to the external circuit.

- The GPIO pins must be limited to 100 µA using a current limiting resistor. GPIO pins clamp the pin voltage to approximately one diode above the VDDIO supply.

- In case of a GPIO pin configured for analog input/output, the analog voltage on the pin must not exceed the VDDIO supply voltage to which the GPIO belongs.

A common application for this feature is connection to a bus such as I<sup>2</sup>C where different devices are running from different supply voltages. In the I<sup>2</sup>C case, the PSoC chip is configured into the Open Drain, Drives Low mode for the SIO pin. This allows an external pull-up to pull the I<sup>2</sup>C bus voltage above the PSoC pin supply. For example, the PSoC chip could operate at 1.8 V, and an external device could run from 5 V. Note that the SIO pin's V<sub>IH</sub> and V<sub>IL</sub> levels are determined by the associated VDDIO supply pin.

The SIO pin must be in one of the following modes: 0 (high impedance analog), 1 (high impedance digital), or 4 (open drain drives low). See Figure 6-12 for details. Absolute maximum ratings for the device must be observed for all I/O pins.

## 6.4.16 Reset Configuration

While reset is active all I/Os are reset to and held in the High Impedance Analog state. After reset is released, the state can be reprogrammed on a port-by-port basis to pull-down or pull-up. To ensure correct reset operation, the port reset configuration data is stored in special nonvolatile registers. The stored reset data is automatically transferred to the port reset configuration registers at reset release.

## 6.4.17 Low Power Functionality

In all low power modes the I/O pins retain their state until the part is awakened and changed or reset. To awaken the part, use a pin interrupt, because the port interrupt logic continues to function in all low power modes.

#### 6.4.18 Special Pin Functionality

Some pins on the device include additional special functionality in addition to their GPIO or SIO functionality. The specific special function pins are listed in "Pinouts" on page 6. The special features are:

- Digital

- □ 4- to 25-MHz crystal oscillator

- □ 32.768-kHz crystal oscillator

- Wake from sleep on I<sup>2</sup>C address match. Any pin can be used for I<sup>2</sup>C if wake from sleep is not required.

- JTAG interface pins

- □ SWD interface pins

- SWV interface pins

- TRACEPORT interface pins

- External reset

- Analog

- Opamp inputs and outputs

- High current IDAC outputs

- External reference inputs

#### 6.4.19 JTAG Boundary Scan

The device supports standard JTAG boundary scan chains on all pins for board level test.

Independent of the ALU operation, these functions are available:

- Shift left

- Shift right

- Nibble swap

- Bitwise OR mask

## 7.2.2.3 Conditionals

Each datapath has two compares, with bit masking options. Compare operands include the two accumulators and the two data registers in a variety of configurations. Other conditions include zero detect, all ones detect, and overflow. These conditions are the primary datapath outputs, a selection of which can be driven out to the UDB routing matrix. Conditional computation can use the built in chaining to neighboring UDBs to operate on wider data widths without the need to use routing resources.

## 7.2.2.4 Variable MSB

The most significant bit of an arithmetic and shift function can be programmatically specified. This supports variable width CRC and PRS functions, and in conjunction with ALU output masking, can implement arbitrary width timers, counters and shift blocks.

## 7.2.2.5 Built in CRC/PRS

The datapath has built in support for single cycle Cyclic Redundancy Check (CRC) computation and Pseudo Random Sequence (PRS) generation of arbitrary width and arbitrary polynomial. CRC/PRS functions longer than 8 bits may be implemented in conjunction with PLD logic, or built in chaining may be use to extend the function into neighboring UDBs.

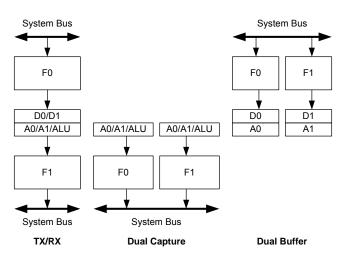

## 7.2.2.6 Input/Output FIFOs

Each datapath contains two four-byte deep FIFOs, which can be independently configured as an input buffer (system bus writes to the FIFO, datapath internal reads the FIFO), or an output buffer (datapath internal writes to the FIFO, the system bus reads from the FIFO). The FIFOs generate status that are selectable as datapath outputs and can therefore be driven to the routing, to interact with sequencers, interrupts, or DMA.

## Figure 7-5. Example FIFO Configurations

## 7.2.2.7 Chaining

The datapath can be configured to chain conditions and signals such as carries and shift data with neighboring datapaths to create higher precision arithmetic, shift, CRC/PRS functions.

## 7.2.2.8 Time Multiplexing

In applications that are over sampled, or do not need high clock rates, the single ALU block in the datapath can be efficiently shared with two sets of registers and condition generators. Carry and shift out data from the ALU are registered and can be selected as inputs in subsequent cycles. This provides support for 16-bit functions in one (8-bit) datapath.

## 7.2.2.9 Datapath I/O

There are six inputs and six outputs that connect the datapath to the routing matrix. Inputs from the routing provide the configuration for the datapath operation to perform in each cycle, and the serial data inputs. Inputs can be routed from other UDB blocks, other device peripherals, device I/O pins, and so on. The outputs to the routing can be selected from the generated conditions, and the serial data outputs. Outputs can be routed to other UDB blocks, device peripherals, interrupt and DMA controller, I/O pins, and so on.

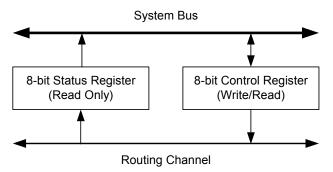

## 7.2.3 Status and Control Module

The primary purpose of this circuitry is to coordinate CPU firmware interaction with internal UDB operation.

## Figure 7-6. Status and Control Registers

The bits of the control register, which may be written to by the system bus, are used to drive into the routing matrix, and thus provide firmware with the opportunity to control the state of UDB processing. The status register is read-only and it allows internal UDB state to be read out onto the system bus directly from internal routing. This allows firmware to monitor the state of UDB processing. Each bit of these registers has programmable connections to the routing matrix and routing connections are made depending on the requirements of the application.

## 7.2.3.1 Usage Examples

As an example of control input, a bit in the control register can be allocated as a function enable bit. There are multiple ways to enable a function. In one method the control bit output would be routed to the clock control block in one or more UDBs and serve as a clock enable for the selected UDB blocks. A status example is a case where a PLD or datapath block generated a condition, such as a "compare true" condition that is captured and latched by the status register and then read (and cleared) by CPU firmware.

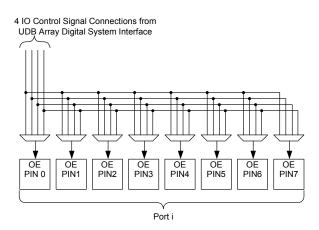

## Figure 7-13. I/O Pin Output Enable Connectivity

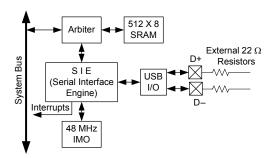

## 7.5 USB

PSoC includes a dedicated Full-Speed (12 Mbps) USB 2.0 transceiver supporting all four USB transfer types: control, interrupt, bulk, and isochronous. PSoC Creator provides full configuration support. USB interfaces to hosts through two dedicated USBIO pins, which are detailed in the "I/O System and Routing" section on page 33.

USB includes the following features:

- Eight unidirectional data endpoints

- One bidirectional control endpoint 0 (EP0)

- Shared 512-byte buffer for the eight data endpoints

- Dedicated 8-byte buffer for EP0

- Three memory modes

Access

- Manual Memory Management with No DMA Access

- Manual Memory Management with Manual DMA Access

Automatic Memory Management with Automatic DMA

- Internal 3.3 V regulator for transceiver

- Internal 48 MHz oscillator that auto locks to USB bus clock, requiring no external crystal for USB (USB equipped parts only)

- Interrupts on bus and each endpoint event, with device wakeup

- USB Reset, Suspend, and Resume operations

- Bus powered and self powered modes

## Figure 7-14. USB

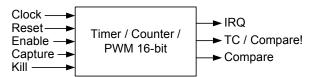

## 7.6 Timers, Counters, and PWMs

The Timer/Counter/PWM peripheral is a 16-bit dedicated peripheral providing three of the most common embedded peripheral features. As almost all embedded systems use some combination of timers, counters, and PWMs. Four of them have been included on this PSoC device family. Additional and more advanced functionality timers, counters, and PWMs can also be instantiated in Universal Digital Blocks (UDBs) as required. PSoC Creator allows you to choose the timer, counter, and PWM features that they require. The tool set utilizes the most optimal resources available.

The Timer/Counter/PWM peripheral can select from multiple clock sources, with input and output signals connected through the DSI routing. DSI routing allows input and output connections to any device pin and any internal digital signal accessible through the DSI. Each of the four instances has a compare output, terminal count output (optional complementary compare output), and programmable interrupt request line. The Timer/Counter/PWMs are configurable as free running, one shot, or Enable input controlled. The peripheral has timer reset and capture inputs, and a kill input for control of the comparator outputs. The peripheral supports full 16-bit capture.

Timer/Counter/PWM features include:

- 16-bit Timer/Counter/PWM (down count only)

- Selectable clock source

- PWM comparator (configurable for LT, LTE, EQ, GTE, GT)

- Period reload on start, reset, and terminal count

- Interrupt on terminal count, compare true, or capture

- Dynamic counter reads

- Timer capture mode

- Count while enable signal is asserted mode

- Free run mode

- One Shot mode (stop at end of period)

- Complementary PWM outputs with deadband

- PWM output kill

## Figure 7-15. Timer/Counter/PWM

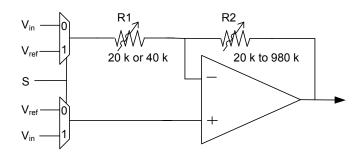

## 8.6.3 PGA

The PGA amplifies an external or internal signal. The PGA can be configured to operate in inverting mode or noninverting mode. The PGA function may be configured for both positive and negative gains as high as 50 and 49 respectively. The gain is adjusted by changing the values of R1 and R2 as illustrated in Figure 8-9. The schematic in Figure 8-9 shows the configuration and possible resistor settings for the PGA. The gain is switched from inverting and non inverting by changing the shared select value of the both the input muxes. The bandwidth for each gain case is listed in Table 8-3.

#### Table 8-3. Bandwidth

| Gain | Bandwidth |

|------|-----------|

| 1    | 6.0 MHz   |

| 24   | 340 kHz   |

| 48   | 220 kHz   |

| 50   | 215 kHz   |

## Figure 8-9. PGA Resistor Settings

The PGA is used in applications where the input signal may not be large enough to achieve the desired resolution in the ADC, or dynamic range of another SC/CT block such as a mixer. The gain is adjustable at runtime, including changing the gain of the PGA prior to each ADC sample.

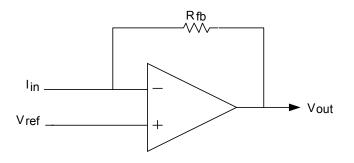

## 8.6.4 TIA

The Transimpedance Amplifier (TIA) converts an internal or external current to an output voltage. The TIA uses an internal feedback resistor in a continuous time configuration to convert input current to output voltage. For an input current I<sub>in</sub>, the output voltage is V<sub>REF</sub> - I<sub>in</sub> x R<sub>fb</sub>, where V<sub>REF</sub> is the value placed on the non inverting input. The feedback resistor Rfb is programmable between 20 K $\Omega$  and 1 M $\Omega$  through a configuration register. Table 8-4 shows the possible values of Rfb and associated configuration settings.

## Table 8-4. Feedback Resistor Settings

| Configuration Word | Nominal $R_{fb}$ (K $\Omega$ ) |

|--------------------|--------------------------------|

| 000b               | 20                             |

| 001b               | 30                             |

| 010b               | 40                             |

| 011b               | 60                             |

| 100b               | 120                            |

| 101b               | 250                            |

| 110b               | 500                            |

| 111b               | 1000                           |

## Figure 8-10. Continuous Time TIA Schematic

The TIA configuration is used for applications where an external sensor's output is current as a function of some type of stimulus such as temperature, light, magnetic flux etc. In a common application, the voltage DAC output can be connected to the V<sub>REF</sub> TIA input to allow calibration of the external sensor bias current by adjusting the voltage DAC output voltage.

## 8.7 LCD Direct Drive

The PSoC Liquid Crystal Display (LCD) driver system is a highly configurable peripheral designed to allow PSoC to directly drive a broad range of LCD glass. All voltages are generated on chip, eliminating the need for external components. With a high multiplex ratio of up to 1/16, the CY8C54LP family LCD driver system can drive a maximum of 736 segments. The PSoC LCD driver module was also designed with the conservative power budget of portable devices in mind, enabling different LCD drive modes and power down modes to conserve power.

PSoC Creator provides an LCD segment drive component. The component wizard provides easy and flexible configuration of LCD resources. You can specify pins for segments and commons along with other options. The software configures the device to meet the required specifications. This is possible because of the programmability inherent to PSoC devices.

## 11.2 Device Level Specifications

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C and T<sub>J</sub>  $\leq$  100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted. Unless otherwise specified, all charts and graphs show typical values.

11.2.1 Device Level Specifications

## Table 11-2. DC Specifications

| Parameter                         | Description                                                                     | Condition                                                                                | S          | Min       | Тур                                                                        | Max                                                                        | Units |

|-----------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------|-----------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|-------|

| V <sub>DDA</sub>                  | Analog supply voltage and input to analog core regulator                        | Analog core regulator                                                                    | r enabled  | 1.8       | -                                                                          | 5.5                                                                        | V     |

| V <sub>DDA</sub>                  | Analog supply voltage, analog regulator bypassed                                | Analog core regulator                                                                    | r disabled | 1.71      | 1.8                                                                        | 1.89                                                                       | V     |

| V <sub>DDD</sub>                  | Digital supply voltage relative to $V_{\text{SSD}}$                             | Digital core regulator                                                                   | 1.8<br>—   | -         | V <sub>DDA</sub> <sup>[15]</sup><br>V <sub>DDA</sub> + 0.1 <sup>[17]</sup> | V                                                                          |       |

| V <sub>DDD</sub>                  | Digital supply voltage, digital regulator bypassed                              | Digital core regulator                                                                   | disabled   | 1.71      | 1.8                                                                        | 1.89                                                                       | V     |

| V <sub>DDIO</sub> <sup>[16]</sup> | I/O supply voltage relative to V <sub>SSIO</sub>                                |                                                                                          |            | 1.71<br>_ | -                                                                          | V <sub>DDA</sub> <sup>[15]</sup><br>V <sub>DDA</sub> + 0.1 <sup>[17]</sup> | V     |

| V <sub>CCA</sub>                  | Direct analog core voltage input (Analog regulator bypass)                      | Analog core regulator                                                                    | r disabled | 1.71      | 1.8                                                                        | 1.89                                                                       | V     |

| V <sub>CCD</sub>                  | Direct digital core voltage input (Digital regulator bypass)                    | Digital core regulator                                                                   | disabled   | 1.71      | 1.8                                                                        | 1.89                                                                       | V     |

| Active Mode                       |                                                                                 |                                                                                          |            |           | •                                                                          |                                                                            | •     |

| I <sub>DD</sub> <sup>[18]</sup>   | Sum of digital and analog IDDD + IDDA.                                          | $V_{DDX} = 2.7 V \text{ to } 5.5 V;$<br>$F_{CPU} = 3 \text{ MHz}^{[19]}$                 | T = -40 °C | _         | 1.9                                                                        | 3.8                                                                        | mA    |

|                                   | IDDIOX for I/Os not included. IMO enabled, bus clock and CPU clock enabled. CPU | F <sub>CPU</sub> = 3 MHz <sup>[19]</sup>                                                 | T = 25 °C  | _         | 1.9                                                                        | 3.8                                                                        |       |

|                                   | executing complex program from flash                                            |                                                                                          | T = 85 °C  | _         | 2                                                                          | 3.8                                                                        |       |

|                                   |                                                                                 | V <sub>DDX</sub> = 2.7 V to 5.5 V;<br>F <sub>CPU</sub> = 6 MHz                           | T = -40 °C | _         | 3.1                                                                        | 5                                                                          |       |

|                                   |                                                                                 | $F_{CPU} = 6 \text{ MHz}$                                                                | T = 25 °C  | _         | 3.1                                                                        | 5                                                                          |       |

|                                   |                                                                                 |                                                                                          | T = 85 °C  | _         | 3.2                                                                        | 5                                                                          |       |

|                                   |                                                                                 | $V_{DDX} = 2.7 V \text{ to } 5.5 V;$                                                     | T = -40 °C | _         | 5.4                                                                        | 7                                                                          |       |

|                                   |                                                                                 |                                                                                          | T = 25 °C  | _         | 5.4                                                                        | 7                                                                          |       |

|                                   |                                                                                 |                                                                                          | T = 85 °C  | _         | 5.6                                                                        | 7                                                                          |       |

|                                   |                                                                                 | $V_{DDX} = 2.7 V \text{ to } 5.5 V;$                                                     | T = -40 °C | _         | 8.9                                                                        | 10.5                                                                       |       |

|                                   |                                                                                 | $V_{DDX} = 2.7 V \text{ to } 5.5 V;$<br>$F_{CPU} = 24 \text{ MHz}^{[19]}$                | T = 25 °C  | _         | 8.9                                                                        | 10.5                                                                       |       |

|                                   |                                                                                 |                                                                                          | T = 85 °C  | _         | 9.1                                                                        | 10.5                                                                       |       |

|                                   |                                                                                 | V <sub>DDX</sub> = 2.7 V to 5.5 V;<br>F <sub>CPU</sub> = 48 MHz <sup>[19]</sup>          | T = -40 °C | _         | 15.5                                                                       | 17                                                                         |       |

|                                   |                                                                                 | $F_{CPU} = 48 \text{ MHz}^{[19]}$                                                        | T = 25 °C  | _         | 15.4                                                                       | 17                                                                         |       |

|                                   |                                                                                 |                                                                                          | T = 85 °C  | _         | 15.7                                                                       | 17                                                                         |       |

|                                   |                                                                                 | V <sub>DDX</sub> = 2.7 V to 5.5 V;<br>F <sub>CPU</sub> = 62 MHz                          | T = -40 °C | _         | 18                                                                         | 19.5                                                                       |       |

|                                   |                                                                                 | $F_{CPU} = 62 \text{ MHz}$                                                               | T = 25 °C  | _         | 18                                                                         | 19.5                                                                       |       |

|                                   |                                                                                 |                                                                                          | T = 85 °C  | _         | 18.5                                                                       | 19.5                                                                       |       |

|                                   |                                                                                 | $V_{DDX}$ = 2.7 V to 5.5 V;                                                              | T = -40 °C | _         | 26.5                                                                       | 30                                                                         |       |

|                                   |                                                                                 | $F_{CPU}^{DDR} = 74 \text{ MHz}$                                                         | T = 25 °C  | _         | 26.5                                                                       | 30                                                                         |       |

|                                   |                                                                                 |                                                                                          | T = 85 °C  | _         | 27                                                                         | 30                                                                         |       |

|                                   |                                                                                 | V <sub>DDX</sub> = 2.7 V to 5.5 V;                                                       | T = -40 °C | _         | 22                                                                         | 25.5                                                                       |       |

|                                   |                                                                                 | V <sub>DDX</sub> = 2.7 V to 5.5 V;<br>F <sub>CPU</sub> = 80 MHz, IMO<br>= 3 MHz with PLL | T = 25 °C  | _         | 22                                                                         | 25.5                                                                       |       |

|                                   |                                                                                 |                                                                                          | T = 85 °C  | _         | 22.5                                                                       | 25.5                                                                       | 1     |

#### Notes

15. The power supplies can be brought up in any sequence however once stable  $V_{DDA}$  must be greater than or equal to all other supplies. 16. The  $V_{DDIO}$  supply voltage must be greater than the maximum voltage on the associated GPIO pins. Maximum voltage on GPIO pin  $\leq V_{DDIO} \leq V_{DDA}$ .

17. Guaranteed by design, not production tested.

18. The current consumption of additional peripherals that are implemented only in programmed logic blocks can be found in their respective datasheets, available in PSoC Creator, the integrated design environment. To estimate total current, find CPU current at frequency of interest and add peripheral currents for your particular system from the device datasheet and component datasheets.

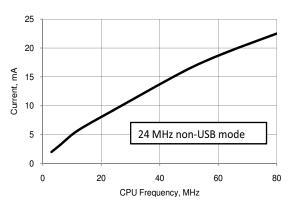

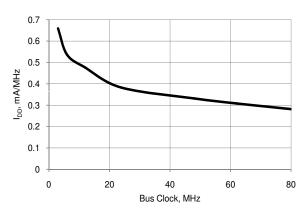

Figure 11-1. Active Mode Current vs  $F_{CPU},\,V_{DD}$  = 3.3 V, Temperature = 25  $^\circ\text{C}$

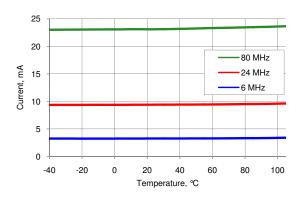

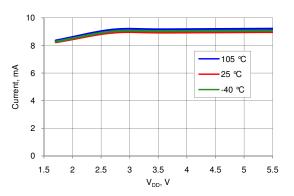

Figure 11-3. Active Mode Current vs Temperature and  $F_{CPU}, \ V_{DD}$  = 3.3 V

## Figure 11-2. I<sub>DD</sub> vs Frequency at 25 °C

Figure 11-4. Active Mode Current vs  $V_{\text{DD}}$  and Temperature,  $F_{\text{CPU}}$  = 24 MHz

## Table 11-3. AC Specifications

| Parameter                              | Description                                                                                                            | Conditions                                                                                                 | Min | Тур | Max   | Units |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----|-----|-------|-------|

| F <sub>CPU</sub>                       | CPU frequency                                                                                                          | $1.71 \text{ V} \leq \text{V}_{DDD} \leq 5.5 \text{ V}$                                                    | DC  | -   | 80.01 | MHz   |

| F <sub>BUSCLK</sub>                    | Bus frequency                                                                                                          | $1.71~V \leq V_{DDD} \leq 5.5~V$                                                                           | DC  | -   | 80.01 | MHz   |

| S <sub>VDD</sub> <sup>[24]</sup>       | V <sub>DD</sub> ramp rate                                                                                              |                                                                                                            | _   | -   | 0.066 | V/µs  |

| T <sub>IO_INIT</sub> <sup>[24]</sup>   | Time from $V_{DDD}/V_{DDA}/V_{CCD}/V_{CCA} \ge IPOR$ to I/O ports set to their reset states                            |                                                                                                            | -   | -   | 10    | μs    |

| T <sub>STARTUP</sub> <sup>[24]</sup>   | Time from $V_{DDD}/V_{DDA}/V_{CCD}/V_{CCA} \ge PRES$ to CPU executing code at reset vector                             | $V_{CCA}/V_{DDA}$ = regulated from<br>$V_{DDA}/V_{DDD}$ , no PLL used, fast IMO<br>boot mode (48 MHz typ.) | -   | -   | 33    | μs    |

|                                        |                                                                                                                        | $V_{CCA}/V_{CCD}$ = regulated from<br>$V_{DDA}/V_{DDD}$ , no PLL used, slow<br>IMO boot mode (12 MHz typ.) | -   | -   | 66    | μs    |

| T <sub>SLEEP</sub> <sup>[24]</sup>     | Wakeup from sleep mode –<br>Application of non-LVD interrupt to beginning<br>of execution of next CPU instruction      |                                                                                                            | _   | -   | 25    | μs    |

| T <sub>HIBERNATE</sub> <sup>[24]</sup> | Wakeup form hibernate mode – Application of<br>external interrupt to beginning of execution of<br>next CPU instruction |                                                                                                            | _   | -   | 150   | μs    |

Note

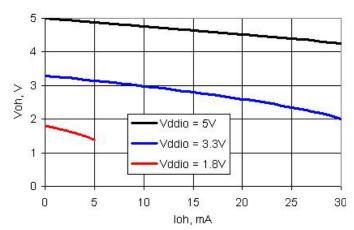

Figure 11-17. SIO Output High Voltage and Current, Unregulated Mode

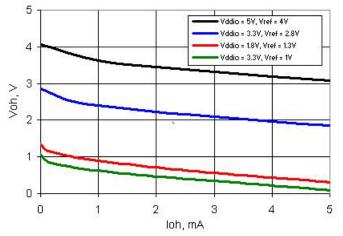

Figure 11-19. SIO Output High Voltage and Current, Regulated Mode

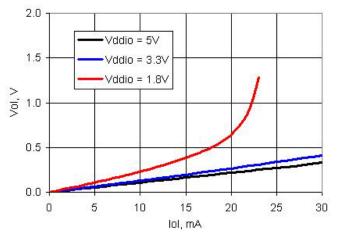

Figure 11-18. SIO Output Low Voltage and Current, Unregulated Mode

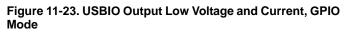

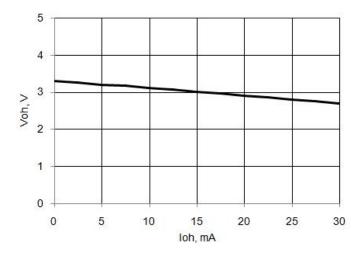

Figure 11-22. USBIO Output High Voltage and Current, GPIO Mode

# Table 11-14. USBIO AC Specifications<sup>[37]</sup>

| Parameter | Description                                                 | Conditions                                           | Min        | Тур | Max           | Units |

|-----------|-------------------------------------------------------------|------------------------------------------------------|------------|-----|---------------|-------|

| Tdrate    | Full-speed data rate average bit rate                       |                                                      | 12 – 0.25% | 12  | 12 +<br>0.25% | MHz   |

| Tjr1      | Receiver data jitter tolerance to next transition           |                                                      | -8         | _   | 8             | ns    |

| Tjr2      | Receiver data jitter tolerance to pair transition           |                                                      | -5         | _   | 5             | ns    |

| Tdj1      | Driver differential jitter to next transition               |                                                      | -3.5       | -   | 3.5           | ns    |

| Tdj2      | Driver differential jitter to pair transition               |                                                      | -4         | -   | 4             | ns    |

| Tfdeop    | Source jitter for differential transition to SE0 transition |                                                      | -2         | -   | 5             | ns    |

| Tfeopt    | Source SE0 interval of EOP                                  |                                                      | 160        | -   | 175           | ns    |

| Tfeopr    | Receiver SE0 interval of EOP                                |                                                      | 82         | I   | -             | ns    |

| Tfst      | Width of SE0 interval during differential transition        |                                                      | -          | -   | 14            | ns    |

| Fgpio_out | GPIO mode output operating frequency                        | $3 \text{ V} \leq \text{V}_{DDD} \leq 5.5 \text{ V}$ | -          | -   | 20            | MHz   |

|           |                                                             | V <sub>DDD</sub> = 1.71 V                            | -          | I   | 6             | MHz   |

| Tr_gpio   | Rise time, GPIO mode, 10%/90% V <sub>DDD</sub>              | V <sub>DDD</sub> > 3 V, 25 pF load                   | -          | 1   | 12            | ns    |

|           |                                                             | V <sub>DDD</sub> = 1.71 V, 25 pF load                | -          | -   | 40            | ns    |

| Tf_gpio   | Fall time, GPIO mode, 90%/10% V <sub>DDD</sub>              | V <sub>DDD</sub> > 3 V, 25 pF load                   | -          | -   | 12            | ns    |

|           |                                                             | V <sub>DDD</sub> = 1.71 V, 25 pF load                | -          | _   | 40            | ns    |

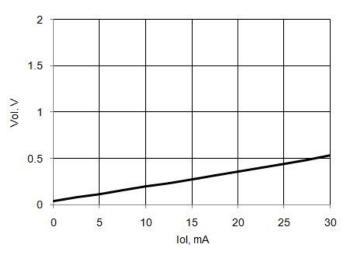

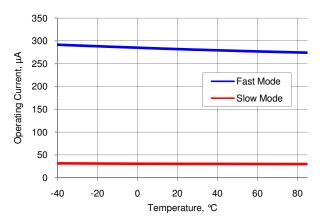

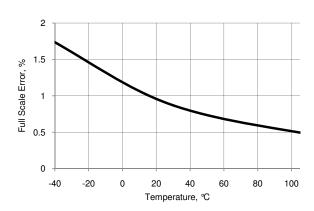

Figure 11-46. IDAC Full Scale Error vs Temperature, Range = 255 µA, Source Mode

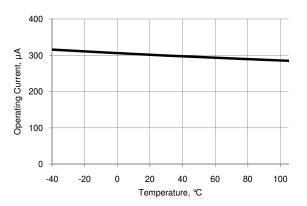

Figure 11-48. IDAC Operating Current vs Temperature, Range = 255  $\mu$ A, Code = 0, Source Mode

Table 11-31. IDAC AC Specifications<sup>[54]</sup>

-40 -20 0 20 40 60 80 Temperature, ℃

Figure 11-47. IDAC Full Scale Error vs Temperature,

Range = 255  $\mu$ A, Sink Mode

Figure 11-49. IDAC Operating Current vs Temperature, Range =  $255 \mu A$ , Code = 0, Sink Mode

| Parameter           | Description              | Conditions                                                                              | Min | Тур | Max | Units     |

|---------------------|--------------------------|-----------------------------------------------------------------------------------------|-----|-----|-----|-----------|

| F <sub>DAC</sub>    | Update rate              |                                                                                         | -   | -   | 8   | Msps      |

| T <sub>SETTLE</sub> | Settling time to 0.5 LSB | Range = 31.875 $\mu$ A, full scale<br>transition, fast mode, 600 $\Omega$ 15-pF<br>load | -   | -   | 125 | ns        |

|                     |                          | Range = 255 $\mu$ A, full scale<br>transition, fast mode, 600 $\Omega$ 15-pF<br>load    | -   | -   | 125 | ns        |

|                     | Current noise            | Range = 255 $\mu$ A, source mode, fast<br>mode, V <sub>DDA</sub> = 5 V, 10 kHz          | -   | 340 | -   | pA/sqrtHz |

Note 54. Based on device characterization (Not production tested).

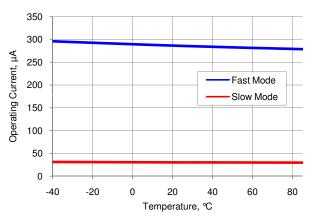

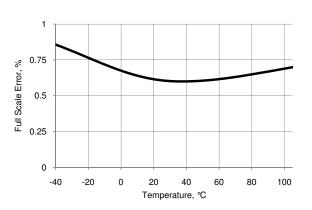

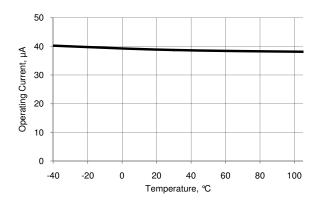

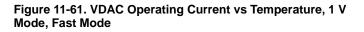

Figure 11-58. VDAC Full Scale Error vs Temperature, 1 V Mode

Figure 11-60. VDAC Operating Current vs Temperature, 1V Mode, Slow Mode

| Parameter        | Description                            | Conditions                                                | Min | Тур  | Max  | Units     |

|------------------|----------------------------------------|-----------------------------------------------------------|-----|------|------|-----------|

| F <sub>DAC</sub> | Update rate                            | 1 V scale                                                 | -   | -    | 1000 | ksps      |

|                  |                                        | 4 V scale                                                 | -   | -    | 250  | ksps      |

| TsettleP         | Settling time to 0.1%, step 25% to 75% | 1 V scale, Cload = 15 pF                                  | -   | 0.45 | 1    | μs        |

|                  |                                        | 4 V scale, Cload = 15 pF                                  | -   | 0.8  | 3.2  | μs        |

| TsettleN         | Settling time to 0.1%, step 75% to 25% | 1 V scale, Cload = 15 pF                                  | -   | 0.45 | 1    | μs        |

|                  |                                        | 4 V scale, Cload = 15 pF                                  | -   | 0.7  | 3    | μs        |

|                  | Voltage noise                          | Range = 1 V, fast mode,<br>V <sub>DDA</sub> = 5 V, 10 kHz | _   | 750  | Ι    | nV/sqrtHz |

## 11.6.4 <sup>2</sup>C

# Table 11-49. Fixed I<sup>2</sup>C DC Specifications<sup>[66]</sup>

| Parameter | Description               | Conditions                       | Min | Тур | Max | Units |

|-----------|---------------------------|----------------------------------|-----|-----|-----|-------|

|           | Block current consumption | Enabled, configured for 100 kbps | _   | _   | 250 | μA    |

|           |                           | Enabled, configured for 400 kbps | _   | _   | 260 | μA    |

# Table 11-50. Fixed I<sup>2</sup>C AC Specifications

| Parameter | Description | Conditions | Min | Тур | Max | Units |

|-----------|-------------|------------|-----|-----|-----|-------|

|           | Bit rate    |            | -   | -   | 1   | Mbps  |

## 11.6.5 USB

## Table 11-51. USB DC Specifications

| Parameter            | Description                                         | Conditions                                                                                          | Min  | Тур | Max  | Units |

|----------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|-----|------|-------|

| V <sub>USB_5</sub>   | Device supply (V <sub>DDD</sub> ) for USB operation | USB configured, USB regulator<br>enabled                                                            | 4.35 | _   | 5.25 | V     |

| V <sub>USB_3.3</sub> |                                                     | USB configured, USB regulator<br>bypassed                                                           | 3.15 | _   | 3.6  | V     |

| V <sub>USB_3</sub>   |                                                     | USB configured, USB regulator bypassed <sup>[67]</sup>                                              | 2.85 | -   | 3.6  | V     |

| IUSB_Configured      |                                                     | V <sub>DDD</sub> = 5 V, F <sub>CPU</sub> = 1.5 MHz                                                  | -    | 10  | -    | mA    |

| mode, b              | mode, bus clock and IMO = 24 MHz                    | V <sub>DDD</sub> = 3.3 V, F <sub>CPU</sub> = 1.5 MHz                                                | _    | 8 – | mA   |       |

| IUSB_Suspended       | Device supply current in device sleep mode          | V <sub>DDD</sub> = 5 V, connected to USB<br>host, PICU configured to wake on<br>USB resume signal   | -    | 0.5 | -    | mA    |

|                      |                                                     | V <sub>DDD</sub> = 5 V, disconnected from<br>USB host                                               | -    | 0.3 | -    | mA    |

|                      |                                                     | V <sub>DDD</sub> = 3.3 V, connected to USB<br>host, PICU configured to wake on<br>USB resume signal | -    | 0.5 | -    | mA    |

|                      |                                                     | V <sub>DDD</sub> = 3.3 V, disconnected from<br>USB host                                             | -    | 0.3 | -    | mA    |

Notes

66. Based on device characterization (Not production tested).67. Rise/fall time matching (TR) not guaranteed, see Table 11-15 on page 80.

## 11.7.3 Nonvolatile Latches (NVL)

## Table 11-57. NVL DC Specifications

| Parameter | Description               | Conditions           | Min  | Тур | Max | Units |

|-----------|---------------------------|----------------------|------|-----|-----|-------|

|           | Erase and program voltage | V <sub>DDD</sub> pin | 1.71 | -   | 5.5 | V     |

# Table 11-58. NVL AC Specifications

| Parameter | Description             | Conditions                                    | Min | Тур | Max | Units                       |

|-----------|-------------------------|-----------------------------------------------|-----|-----|-----|-----------------------------|

|           | NVL endurance           | Programmed at 25 °C                           | 1 K | -   | -   | Program/<br>erase<br>cycles |

|           |                         | Programmed at 0 °C to 70 °C                   | 100 | -   | -   | Program/<br>erase<br>cycles |

|           | NVL data retention time | Average ambient temp. $T_A \le 55 \text{ °C}$ | 20  | -   | -   | Years                       |

|           |                         | Average ambient temp. T <sub>A</sub> ≤ 85 °C  | 10  | _   | _   | Years                       |

## 11.7.4 SRAM

## Table 11-59. SRAM DC Specifications

| Parameter         |                                        | Conditions | Min | Тур | Max | Units |

|-------------------|----------------------------------------|------------|-----|-----|-----|-------|

| V <sub>SRAM</sub> | SRAM retention voltage <sup>[70]</sup> |            | 1.2 | -   | 1   | V     |

## Table 11-60. SRAM AC Specifications

| Parameter         | Description              | Conditions | Min | Тур | Max   | Units |

|-------------------|--------------------------|------------|-----|-----|-------|-------|

| F <sub>SRAM</sub> | SRAM operating frequency |            | DC  | 1   | 80.01 | MHz   |

## 11.7.5 External Memory Interface

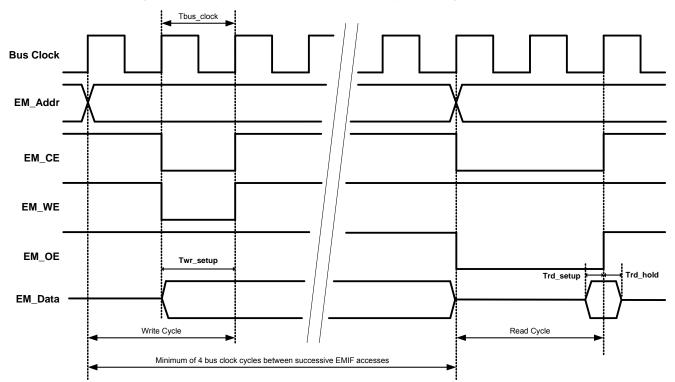

## Figure 11-70. Asynchronous Write and Read Cycle Timing, No Wait States

|  | Table 11-61. | Asynchronous Write and Read Timing Specifications <sup>[71]</sup> |

|--|--------------|-------------------------------------------------------------------|

|--|--------------|-------------------------------------------------------------------|

| Parameter  | Description                                                  | Conditions | Min             | Тур | Max | Units |

|------------|--------------------------------------------------------------|------------|-----------------|-----|-----|-------|

| Fbus_clock | Bus clock frequency <sup>[72]</sup>                          |            | -               | -   | 33  | MHz   |

| Tbus_clock | Bus clock period <sup>[73]</sup>                             |            | 30.3            | -   | -   | ns    |

| Twr_Setup  | Time from EM_data valid to rising edge of<br>EM_WE and EM_CE |            | Tbus_clock – 10 | _   | -   | ns    |

| Trd_setup  | Time that EM_data must be valid before rising edge of EM_OE  |            | 5               | -   | -   | ns    |

| Trd_hold   | Time that EM_data must be valid after rising edge of EM_OE   |            | 5               | _   | -   | ns    |

Notes

71. Based on device characterization (Not production tested).

72. EMIF signal timings are limited by GPIO frequency limitations. See "GPIO" section on page 73.

73. EMIF output signals are generally synchronized to bus clock, so EMIF signal timings are dependent on bus clock frequency.

## 11.9.2 Internal Low-Speed Oscillator

## Table 11-73. ILO DC Specifications

| Parameter       | Description                       | Conditions                 | Min | Тур | Max | Units |

|-----------------|-----------------------------------|----------------------------|-----|-----|-----|-------|

|                 | Operating current <sup>[87]</sup> | F <sub>OUT</sub> = 1 kHz   | _   | -   | 1.7 | μA    |

| I <sub>CC</sub> |                                   | F <sub>OUT</sub> = 33 kHz  | -   | -   | 2.6 | μA    |

|                 |                                   | F <sub>OUT</sub> = 100 kHz | _   | -   | 2.6 | μA    |

|                 | Leakage current <sup>[87]</sup>   | Power down mode            | -   | -   | 15  | nA    |

## Table 11-74. ILO AC Specifications<sup>[88]</sup>

| Parameter        | Description                   | Conditions | Min | Тур | Max | Units |

|------------------|-------------------------------|------------|-----|-----|-----|-------|

| Tstart_ilo       | Startup time, all frequencies | Turbo mode | -   | -   | 2   | ms    |

|                  | ILO frequencies               | ·          |     |     |     |       |

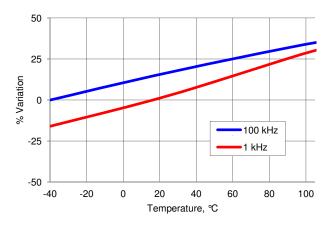

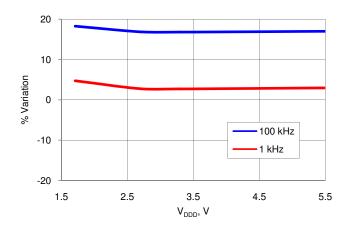

| F <sub>ILO</sub> | 100 kHz                       |            | 45  | 100 | 200 | kHz   |

|                  | 1 kHz                         |            | 0.5 | 1   | 2   | kHz   |

## Figure 11-77. ILO Frequency Variation vs. Temperature

Figure 11-78. ILO Frequency Variation vs. V<sub>DD</sub>

#### Notes

87. This value is calculated, not measured.

## 11.9.3 MHz External Crystal Oscillator

For more information on crystal or ceramic resonator selection for the MHzECO, refer to application note AN54439: PSoC 3 and PSoC 5 External Oscillators.

## Table 11-75. MHzECO DC Specifications

| Parameter       |                                   | Conditions        | Min | Тур | Max | Units |

|-----------------|-----------------------------------|-------------------|-----|-----|-----|-------|

| I <sub>CC</sub> | Operating current <sup>[89]</sup> | 13.56 MHz crystal | -   | 3.8 | _   | mA    |

#### Table 11-76. MHzECO AC Specifications

| Parameter | Description             | Conditions | Min | Тур | Max | Units |

|-----------|-------------------------|------------|-----|-----|-----|-------|

| F         | Crystal frequency range |            | 4   | -   | 25  | MHz   |

#### 11.9.4 kHz External Crystal Oscillator

## Table 11-77. kHzECO DC Specifications<sup>[89]</sup>

| Parameter       | Description       | Conditions                | Min | Тур  | Max | Units |

|-----------------|-------------------|---------------------------|-----|------|-----|-------|

| I <sub>CC</sub> | Operating current | Low power mode; CL = 6 pF | -   | 0.25 | 1.0 | μA    |

| DL              | Drive level       |                           | -   | -    | 1   | μW    |

## Table 11-78. kHzECO AC Specifications<sup>[89]</sup>

| Parameter       | Description  | Conditions      | Min | Тур    | Max | Units |

|-----------------|--------------|-----------------|-----|--------|-----|-------|

| F               | Frequency    |                 | -   | 32.768 | -   | kHz   |

| T <sub>ON</sub> | Startup time | High power mode | -   | 1      | -   | S     |

#### 11.9.5 External Clock Reference

#### Table 11-79. External Clock Reference AC Specifications<sup>[89]</sup>

| Parameter | Description              | Conditions                         | Min | Тур | Мах | Units |

|-----------|--------------------------|------------------------------------|-----|-----|-----|-------|

|           | External frequency range |                                    | 0   | _   | 33  | MHz   |

|           | Input duty cycle range   | Measured at V <sub>DDIO</sub> /2   | 30  | 50  | 70  | %     |

|           | Input edge rate          | V <sub>IL</sub> to V <sub>IH</sub> | 0.5 | -   | -   | V/ns  |

#### 11.9.6 Phase-Locked Loop

#### Table 11-80. PLL DC Specifications

| Parameter       | Description           | Conditions               | Min | Тур | Max | Units |

|-----------------|-----------------------|--------------------------|-----|-----|-----|-------|

| I <sub>DD</sub> | PLL operating current | In = 3 MHz, Out = 80 MHz | _   | 650 | -   | μA    |

|                 |                       | In = 3 MHz, Out = 67 MHz | _   | 400 | -   | μA    |

|                 |                       | In = 3 MHz, Out = 24 MHz | -   | 200 | -   | μA    |

#### Table 11-81. PLL AC Specifications

| Parameter   | Description                                | Conditions          | Min | Тур | Max | Units |

|-------------|--------------------------------------------|---------------------|-----|-----|-----|-------|

| Fpllin      | PLL input frequency <sup>[90]</sup>        |                     | 1   | _   | 48  | MHz   |

|             | PLL intermediate frequency <sup>[91]</sup> | Output of prescaler | 1   | -   | 3   | MHz   |

| Fpllout     | PLL output frequency <sup>[90]</sup>       |                     | 24  | _   | 80  | MHz   |

|             | Lock time at startup                       |                     | -   | -   | 250 | μs    |

| Jperiod-rms | Jitter (rms) <sup>[89]</sup>               |                     | _   | _   | 250 | ps    |

Notes

89. Based on device characterization (Not production tested).

91. PLL input divider, Q, must be set so that the input frequency is divided down to the intermediate frequency range. Value for Q ranges from 1 to 16.

<sup>90.</sup> This specification is guaranteed by testing the PLL across the specified range using the IMO as the source for the PLL.

# 13. Packaging

## Table 13-1. Package Characteristics

| Parameter       | Description                          | Conditions    | Min | Тур  | Max | Units   |

|-----------------|--------------------------------------|---------------|-----|------|-----|---------|

| T <sub>A</sub>  | Operating ambient temperature        |               | -40 | 25   | 85  | °C      |

| TJ              | Operating junction temperature       |               | -40 | _    | 100 | °C      |

| T <sub>JA</sub> | Package $\theta_{JA}$ (68-pin QFN)   |               | -   | 15   | _   | °C/Watt |

| T <sub>JA</sub> | Package $\theta_{JA}$ (100-pin TQFP) |               | -   | 34   | _   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (68-pin QFN)   |               | _   | 13   | _   | °C/Watt |

| T <sub>JC</sub> | Package $\theta_{JC}$ (100-pin TQFP) |               | -   | 10   | -   | °C/Watt |

| T <sub>A</sub>  | Operating ambient temperature        | For CSP parts | -40 | 25   | 85  | °C      |

| TJ              | Operating junction temperature       | For CSP parts | -40 | -    | 100 | °C      |

| T <sub>JA</sub> | Package $\theta_{JA}$ (99-ball CSP)  |               |     | 16.5 |     | °C/Watt |

| T <sub>Jc</sub> | Package $\theta_{JC}$ (99-ball CSP)  |               | _   | 0.1  | -   | °C/Watt |

## Table 13-2. Solder Reflow Peak Temperature

| Package      | Maximum Peak<br>Temperature | Maximum Time at<br>Peak Temperature |

|--------------|-----------------------------|-------------------------------------|

| 68-pin QFN   | 260 °C                      | 30 seconds                          |

| 100-pin TQFP | 260 °C                      | 30 seconds                          |

| 99-pin CSP   | 255 °C                      | 30 seconds                          |

## Table 13-3. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package      | MSL   |

|--------------|-------|

| 68-pin QFN   | MSL 3 |

| 100-pin TQFP | MSL 3 |

| 99-pin CSP   | MSL 1 |