#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 80MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                               |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                            |

| Number of I/O              | 62                                                                           |

| Program Memory Size        | 256КВ (256К х 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 64K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                 |

| Data Converters            | A/D 1x12b; D/A 2x8b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-LQFP                                                                     |

| Supplier Device Package    | 100-TQFP (14x14)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c5488axi-lp120 |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **More Information**

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the knowledge base article KBA86521, How to Design with PSoC 3, PSoC 4, and PSoC 5LP. Following is an abbreviated list for PSoC 5LP:

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, PSoC 5LP In addition, PSoC Creator includes a device selection tool.

- Application notes: Cypress offers a large number of PSoC application notes and code examples covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with PSoC 5LP are:

- AN77759: Getting Started With PSoC 5LP

- AN77835: PSoC 3 to PSoC 5LP Migration Guide

- AN61290: Hardware Design Considerations

- □ AN57821: Mixed Signal Circuit Board Layout

- AN58304: Pin Selection for Analog Designs

- □ AN81623: Digital Design Best Practices

- AN73854: Introduction To Bootloaders

- Development Kits:

- CY8CKIT-059 is a low-cost platform for prototyping, with a unique snap-away programmer and debugger on the USB connector.

- CY8CKIT-050 is designed for analog performance, for developing high-precision analog, low-power, and low-voltage applications.

- CY8CKIT-001 provides a common development platform for any one of the PSoC 1, PSoC 3, PSoC 4, or PSoC 5LP families of devices.

- The MiniProg3 device provides an interface for flash programming and debug.

- Technical Reference Manuals (TRM)

- Architecture TRM

- Registers TRM

- Programming Specification

# **PSoC Creator**

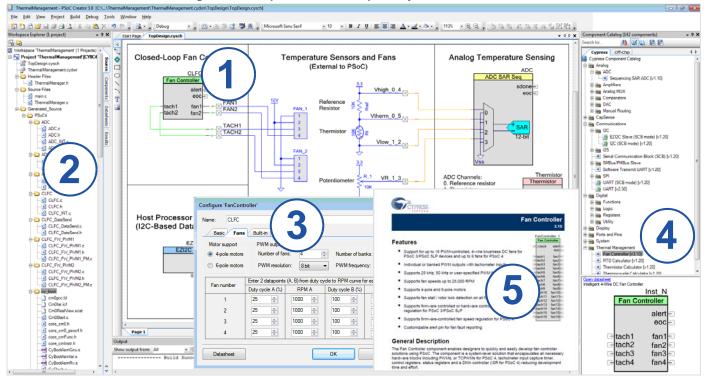

PSoC Creator is a free Windows-based Integrated Design Environment (IDE). It enables concurrent hardware and firmware design of PSoC 3, PSoC 4, and PSoC 5LP based systems. Create designs using classic, familiar schematic capture supported by over 100 pre-verified, production-ready PSoC Components; see the list of component datasheets. With PSoC Creator, you can:

- 1. Drag and drop component icons to build your hardware system design in the main design workspace

- 2. Codesign your application firmware with the PSoC hardware, using the PSoC Creator IDE C compiler

- 3. Configure components using the configuration tools

- 4. Explore the library of 100+ components

- 5. Review component datasheets

#### Figure 1. Multiple-Sensor Example Project in PSoC Creator

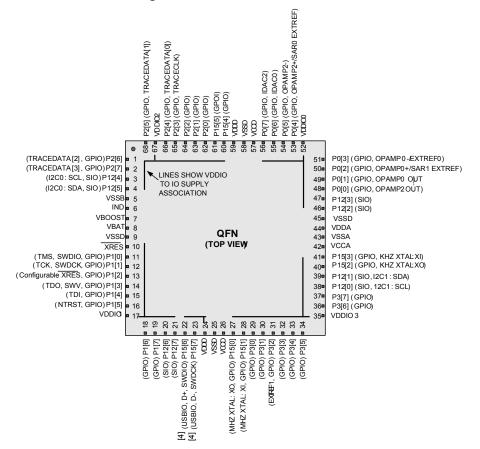

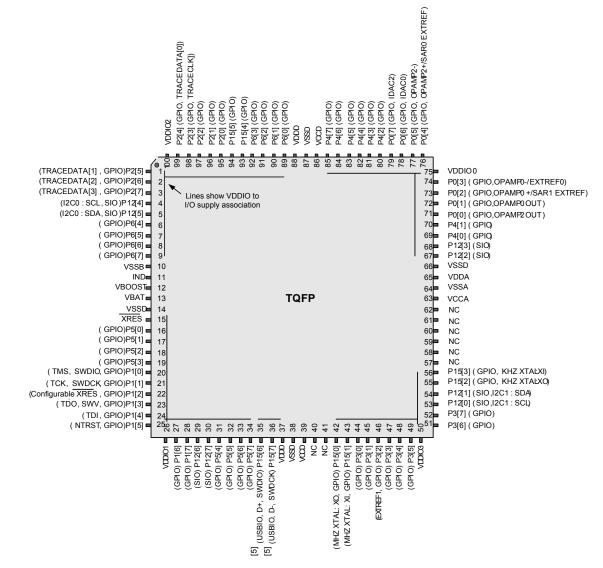

#### Figure 2-3. 68-Pin QFN Part Pinout<sup>[3]</sup>

Notes

3. The center pad on the QFN package should be connected to digital ground (VSSD) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floated and not connected to any other signal. For more information, see AN72845, Design Guidelines for QFN Devices.

4. Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

Table 2-1. V<sub>DDIO</sub> and Port Pin Associations

| VDDIO  | Port Pins                            |

|--------|--------------------------------------|

| VDDIO0 | P0[7:0], P4[7:0], P12[3:2]           |

| VDDIO1 | P1[7:0], P5[7:0], P12[7:6]           |

| VDDIO2 | P2[7:0], P6[7:0], P12[5:4], P15[5:4] |

| VDDIO3 | P3[7:0], P12[1:0], P15[3:0]          |

| VDDD   | P15[7:6] (USB D+, D-)                |

Note 5. Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

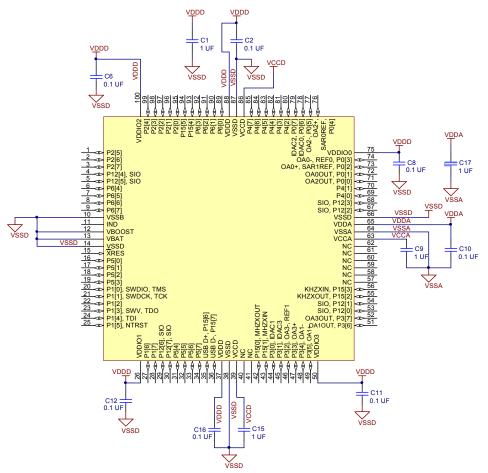

Figure 2-5 and Figure 2-6 show an example schematic and an example PCB layout, for the 100-pin TQFP part, for optimal analog performance on a 2-layer board.

- The two pins labeled VDDD must be connected together.

- The two pins labeled VCCD must be connected together, with capacitance added, as shown in Figure 2-5 and Power System

on page 27. The trace between the two VCCD pins should be as short as possible.

■ The two pins labeled VSSD must be connected together.

For information on circuit board layout issues for mixed signals, refer to the application note AN57821 - Mixed Signal Circuit Board Layout Considerations for PSoC® 3 and PSoC 5.

Figure 2-5. Example Schematic for 100-Pin TQFP Part with Power Connections

**Note** The two VCCD pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-6.

For more information on pad layout, refer to http://www.cypress.com/cad-resources/psoc-5lp-cad-libraries.

## Table 4-6. Interrupt Vector Table

| Interrupt # | Cortex-M3 Exception # | Fixed Function           | DMA               | UDB          |

|-------------|-----------------------|--------------------------|-------------------|--------------|

| 0           | 16                    | Low voltage detect (LVD) | phub_termout0[0]  | udb_intr[0]  |

| 1           | 17                    | Cache/ECC                | phub_termout0[1]  | udb_intr[1]  |

| 2           | 18                    | Reserved                 | phub_termout0[2]  | udb_intr[2]  |

| 3           | 19                    | Sleep (Pwr Mgr)          | phub_termout0[3]  | udb_intr[3]  |

| 4           | 20                    | PICU[0]                  | phub_termout0[4]  | udb_intr[4]  |

| 5           | 21                    | PICU[1]                  | phub_termout0[5]  | udb_intr[5]  |

| 6           | 22                    | PICU[2]                  | phub_termout0[6]  | udb_intr[6]  |

| 7           | 23                    | PICU[3]                  | phub_termout0[7]  | udb_intr[7]  |

| 8           | 24                    | PICU[4]                  | phub_termout0[8]  | udb_intr[8]  |

| 9           | 25                    | PICU[5]                  | phub_termout0[9]  | udb_intr[9]  |

| 10          | 26                    | PICU[6]                  | phub_termout0[10] | udb_intr[10] |

| 11          | 27                    | PICU[12]                 | phub_termout0[11] | udb_intr[11] |

| 12          | 28                    | PICU[15]                 | phub_termout0[12] | udb_intr[12] |

| 13          | 29                    | Comparators Combined     | phub_termout0[13] | udb_intr[13] |

| 14          | 30                    | Switched Caps Combined   | phub_termout0[14] | udb_intr[14] |

| 15          | 31                    | I <sup>2</sup> C         | phub_termout0[15] | udb_intr[15] |

| 16          | 32                    | Reserved                 | phub_termout1[0]  | udb_intr[16] |

| 17          | 33                    | Timer/Counter0           | phub_termout1[1]  | udb_intr[17] |

| 18          | 34                    | Timer/Counter1           | phub_termout1[2]  | udb_intr[18] |

| 19          | 35                    | Timer/Counter2           | phub_termout1[3]  | udb_intr[19] |

| 20          | 36                    | Timer/Counter3           | phub_termout1[4]  | udb_intr[20] |

| 21          | 37                    | USB SOF Int              | phub_termout1[5]  | udb_intr[21] |

| 22          | 38                    | USB Arb Int              | phub_termout1[6]  | udb_intr[22] |

| 23          | 39                    | USB Bus Int              | phub_termout1[7]  | udb_intr[23] |

| 24          | 40                    | USB Endpoint[0]          | phub_termout1[8]  | udb_intr[24] |

| 25          | 41                    | USB Endpoint Data        | phub_termout1[9]  | udb_intr[25] |

| 26          | 42                    | Reserved                 | phub_termout1[10] | udb_intr[26] |

| 27          | 43                    | LCD                      | phub_termout1[11] | udb_intr[27] |

| 28          | 44                    | Reserved                 | phub_termout1[12] | udb_intr[28] |

| 29          | 45                    | Decimator Int            | phub_termout1[13] | udb_intr[29] |

| 30          | 46                    | phub_err_int             | phub_termout1[14] | udb_intr[30] |

| 31          | 47                    | eeprom_fault_int         | phub_termout1[15] | udb_intr[31] |

## 5. Memory

## 5.1 Static RAM

CY8C54LP static RAM (SRAM) is used for temporary data storage. Code can be executed at full speed from the portion of SRAM that is located in the code space. This process is slower from SRAM above 0x20000000. The device provides up to 64 KB of SRAM. The CPU or the DMA controller can access all of SRAM. The SRAM can be accessed simultaneously by the Cortex-M3 CPU and the DMA controller if accessing different 32-KB blocks.

## 5.2 Flash Program Memory

Flash memory in PSoC devices provides nonvolatile storage for user firmware, user configuration data, bulk data storage, and optional ECC data. The main flash memory area contains up to 256 KB of user program space.

Up to an additional 32 KB of flash space is available for Error Correcting Codes (ECC). If ECC is not used this space can store device configuration data and bulk user data. User code may not be run out of the ECC flash memory section. ECC can correct one bit error and detect two bit errors per 8 bytes of firmware memory; an interrupt can be generated when an error is detected. The flash output is 9 bytes wide with 8 bytes of data and 1 byte of ECC data.

The CPU or DMA controller read both user code and bulk data located in flash through the cache controller. This provides higher CPU performance. If ECC is enabled, the cache controller also performs error checking and correction.

Flash programming is performed through a special interface and preempts code execution out of flash. Code execution may be done out of SRAM during flash programming.

The flash programming interface performs flash erasing, programming and setting code protection levels. Flash in-system serial programming (ISSP), typically used for production programming, is possible through both the SWD and JTAG interfaces. In-system programming, typically used for bootloaders, is also possible using serial interfaces such as I<sup>2</sup>C, USB, UART, and SPI, or any communications protocol.

#### 5.3 Flash Security

All PSoC devices include a flexible flash protection model that prevents access and visibility to on-chip flash memory. This prevents duplication or reverse engineering of proprietary code. Flash memory is organized in blocks, where each block contains 256 bytes of program or data and 32 bytes of ECC or configuration data.

The device offers the ability to assign one of four protection levels to each row of flash. Table 5-1 lists the protection modes available. Flash protection levels can only be changed by performing a complete flash erase. The Full Protection and Field Upgrade settings disable external access (through a debugging tool such as PSoC Creator, for example). If your application requires code update through a boot loader, then use the Field Upgrade setting. Use the Unprotected setting only when no security is needed in your application. The PSoC device also offers an advanced security feature called Device Security which permanently disables all test, programming, and debug ports, protecting your application from external access (see the "Device Security" section on page 63). For more information on how to take full advantage of the security features in PSoC, see the PSoC 5 TRM.

| Protection<br>Setting | Allowed                                              | Not Allowed                              |

|-----------------------|------------------------------------------------------|------------------------------------------|

| Unprotected           | External read and write<br>+ internal read and write | -                                        |

| Factory<br>Upgrade    | External write + internal read and write             | External read                            |

| Field Upgrade         | Internal read and write                              | External read and write                  |

| Full Protection       | Internal read                                        | External read and write + internal write |

#### Disclaimer

Note the following details of the flash code protection features on Cypress devices.

Cypress products meet the specifications contained in their particular Cypress datasheets. Cypress believes that its family of products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

#### 5.4 EEPROM

PSoC EEPROM memory is a byte addressable nonvolatile memory. The CY8C54LP has 2 KB of EEPROM memory to store user data. Reads from EEPROM are random access at the byte level. Reads are done directly; writes are done by sending write commands to an EEPROM programming interface. CPU code execution can continue from flash during EEPROM writes. EEPROM is erasable and writeable at the row level. The EEPROM is divided into 128 rows of 16 bytes each. The factory default values of all EEPROM bytes are 0.

Because the EEPROM is mapped to the Cortex-M3 Peripheral region, the CPU cannot execute out of EEPROM. There is no ECC hardware associated with EEPROM. If ECC is required it must be handled in firmware.

It can take as much as 20 milliseconds to write to EEPROM or flash. During this time the device should not be reset, or unexpected changes may be made to portions of EEPROM or flash. Reset sources (see *Section 6.3.1*) include XRES pin, software reset, and watchdog; care should be taken to make sure that these are not inadvertently activated. In addition, the low voltage detect circuits should be configured to generate an interrupt instead of a reset.

## 5.5 Nonvolatile Latches (NVLs)

PSoC has a 4-byte array of nonvolatile latches (NVLs) that are used to configure the device at reset. The NVL register map is shown in Table 5-3.

| Table 5-2. | <b>Device Configuration NVL Register M</b> | ар |

|------------|--------------------------------------------|----|

|------------|--------------------------------------------|----|

| Register Address | 7            | 6         | 5                         | 4 | 3               | 2         | 1            | 0    |          |

|------------------|--------------|-----------|---------------------------|---|-----------------|-----------|--------------|------|----------|

| 0x00             | PRT3RDM[1:0] |           | PRT2RDM[1:0] PRT1RDM[1:0] |   | )] PRT2RDM[1:0] |           | DM[1:0]      | PRT0 | RDM[1:0] |

| 0x01             | PRT12R       | DM[1:0]   | PRT6RDM[1:0]              |   | PRT5RDM[1:0]    |           | PRT4RDM[1:0] |      |          |

| 0x02             | XRESMEN      | DBGEN     |                           |   | PRT15           | 5RDM[1:0] |              |      |          |

| 0x03             |              | DIG_PHS_I | DLY[3:0] ECCEN            |   | DPS             | [1:0]     | CFGSPEED     |      |          |

The details for individual fields and their factory default settings are shown in Table 5-3:.

## Table 5-3. Fields and Factory Default Settings

| Field            | Description                                                                                                                            | Settings                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| PRTxRDM[1:0]     |                                                                                                                                        | 00b (default) - high impedance analog<br>01b - high impedance digital<br>10b - resistive pull up<br>11b - resistive pull down |

| XRESMEN          | Controls whether pin P1[2] is used as a GPIO or as an external reset. P1[2] is generally used as a GPIO, and not as an external reset. | 0 (default) - GPIO<br>1 - external reset                                                                                      |

| DBGEN            | Debug Enable allows access to the debug system, for third-party programmers.                                                           | 0 - access disabled<br>1 (default) - access enabled                                                                           |

| CFGSPEED         | Controls the speed of the IMO-based clock during the device boot process, for faster boot or low-power operation                       | 0 (default) - 12 MHz IMO<br>1 - 48 MHz IMO                                                                                    |

| DPS[1:0]         | Controls the usage of various P1 pins as a debug port.<br>See "Programming, Debug Interfaces, Resources" on<br>page 60.                | 00b - 5-wire JTAG<br>01b (default) - 4-wire JTAG<br>10b - SWD<br>11b - debug ports disabled                                   |

| ECCEN            | Controls whether ECC flash is used for ECC or for general configuration and data storage. See "Flash Program Memory" on page 19.       | 0 - ECC disabled<br>1 (default) - ECC enabled                                                                                 |

| DIG_PHS_DLY[3:0] | Selects the digital clock phase delay.                                                                                                 | See the TRM for details.                                                                                                      |

Although PSoC Creator provides support for modifying the device configuration NVLs, the number of NVL erase/write cycles is limited – see "Nonvolatile Latches (NVL)" on page 106.

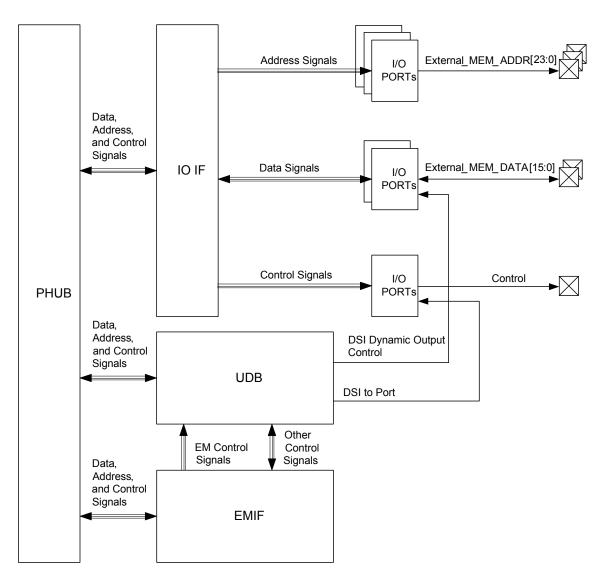

## 5.6 External Memory Interface

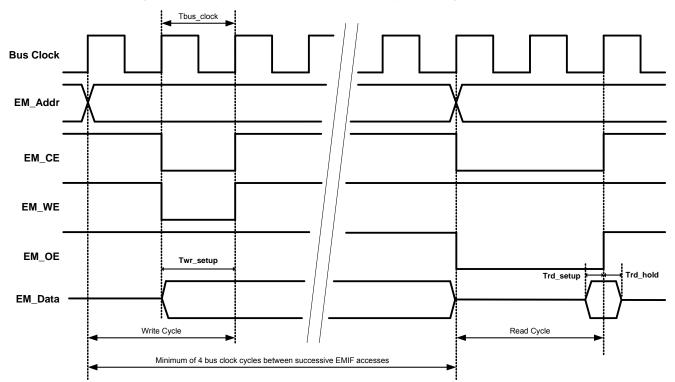

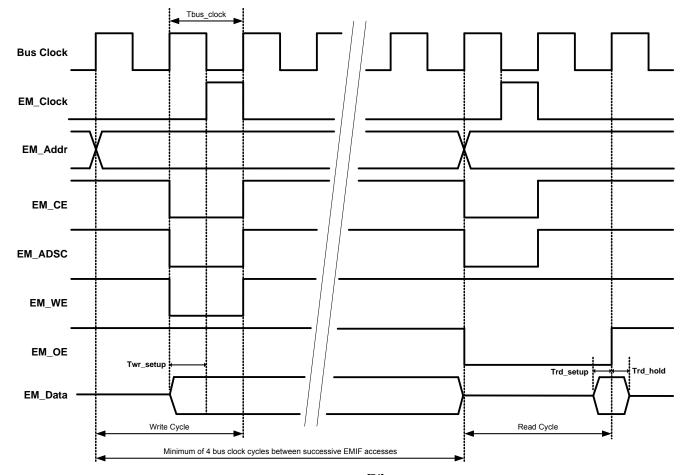

CY8C54LP provides an EMIF for connecting to external memory devices. The connection allows read and write accesses to external memories. The EMIF operates in conjunction with UDBs, I/O ports, and other hardware to generate external memory address and control signals. At 33 MHz, each memory access cycle takes four bus clock cycles.

Figure 5-1 is the EMIF block diagram. The EMIF supports synchronous and asynchronous memories. The CY8C54LP only supports one type of external memory device at a time.

External memory is located in the Cortex-M3 external RAM space; it can use up to 24 address bits. See Table 5-4 on page 22Memory Map on page 22. The memory can be 8 or 16 bits wide.

Cortex-M3 instructions can be fetched from external memory if it is 16-bit. Other limitations apply; for details, see application note AN89610, PSoC<sup>®</sup> 4 and PSoC 5LP ARM Cortex Code Optimization. There is no provision for code security in external memory. If code must be kept secure, then it should be placed in internal flash. See Flash Security on page 19 and Device Security on page 63.

Figure 5-1. EMIF Block Diagram

# 6. System Integration

## 6.1 Clocking System

The clocking system generates, divides, and distributes clocks throughout the PSoC system. For the majority of systems, no external crystal is required. The IMO and PLL together can generate up to a 80-MHz clock, accurate to ±2% over voltage and temperature. Additional internal and external clock sources allow each design to optimize accuracy, power, and cost. All of the system clock sources can be used to generate other clock frequencies in the 16-bit clock dividers and UDBs for anything the user wants, for example a UART baud rate generator.

Clock generation and distribution is automatically configured through the PSoC Creator IDE graphical interface. This is based on the complete system's requirements. It greatly speeds the design process. PSoC Creator allows designers to build clocking systems with minimal input. The designer can specify desired clock frequencies and accuracies, and the software locates or builds a clock that meets the required specifications. This is possible because of the programmability inherent in PSoC. Key features of the clocking system include:

- Seven general purpose clock sources

- □ 3- to 74-MHz IMO, ±2% at 3 MHz

- 4- to 25-MHz external crystal oscillator (MHzECO)

- Clock doubler provides a doubled clock frequency output for the USB block, see USB Clock Domain on page 26

- DSI signal from an external I/O pin or other logic

- 24- to 80-MHz fractional PLL sourced from IMO, MHzECO, or DSI

- □ 1-kHz, 33-kHz, 100-kHz ILO for watchdog timer (WDT) and sleep timer

- 32.768-kHz external crystal oscillator (kHzECO) for RTC

- IMO has a USB mode that auto locks to USB bus clock requiring no external crystal for USB. (USB equipped parts only)

- Independently sourced clock in all clock dividers

- Eight 16-bit clock dividers for the digital system

- Four 16-bit clock dividers for the analog system

- Dedicated 16-bit divider for the CPU bus and CPU clock

- Automatic clock configuration in PSoC Creator

| Source  | Fmin   | Tolerance at Fmin                | Fmax    | Tolerance at Fmax | Startup Time                          |

|---------|--------|----------------------------------|---------|-------------------|---------------------------------------|

| IMO     | 3 MHz  | ±2% over voltage and temperature | 74 MHz  | ±7%               | 13 µs max                             |

| MHzECO  | 4 MHz  | Crystal dependent                | 25 MHz  | Crystal dependent | 5 ms typ, max is<br>crystal dependent |

| DSI     | 0 MHz  | Input dependent                  | 33 MHz  | Input dependent   | Input dependent                       |

| PLL     | 24 MHz | Input dependent                  | 80 MHz  | Input dependent   | 250 µs max                            |

| Doubler | 48 MHz | Input dependent                  | 48 MHz  | Input dependent   | 1 µs max                              |

| ILO     | 1 kHz  | -50%, +100%                      | 100 kHz | -55%, +100%       | 15 ms max in lowest power mode        |

| kHzECO  | 32 kHz | Crystal dependent                | 32 kHz  | Crystal dependent | 500 ms typ, max is crystal dependent  |

#### Table 6-1. Oscillator Summary

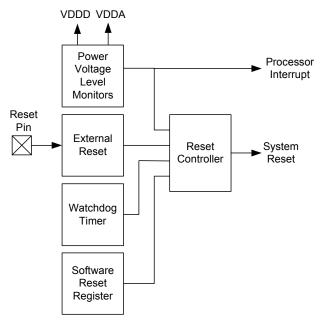

## Figure 6-8. Resets

The term **system reset** indicates that the processor as well as analog and digital peripherals and registers are reset.

A reset status register shows some of the resets or power voltage monitoring interrupts. The program may examine this register to detect and report certain exception conditions. This register is cleared after a power-on reset. For details see the Technical Reference Manual.

#### 6.3.1 Reset Sources

#### 6.3.1.1 Power Voltage Level Monitors

#### IPOR - Initial Power-on-Reset

At initial power on, IPOR monitors the power voltages  $V_{DDD}$ ,  $V_{DDA}$ ,  $V_{CCD}$  and  $V_{CCA}$ . The trip level is not precise. It is set to approximately 1 volt (0.75 V to 1.45 V). This is below the lowest specified operating voltage but high enough for the internal circuits to be reset and to hold their reset state. The monitor generates a reset pulse that is at least 150 ns wide. It may be much wider if one or more of the voltages ramps up slowly.

After boot, the IPOR circuit is disabled and voltage supervision is handed off to the precise low-voltage reset (PRES) circuit.

#### PRES - Precise Low-Voltage Reset

This circuit monitors the outputs of the analog and digital internal regulators after power up. The regulator outputs are compared to a precise reference voltage. The response to a PRES trip is identical to an IPOR reset.

In normal operating mode, the program cannot disable the digital PRES circuit. The analog regulator can be disabled, which also disables the analog portion of the PRES. The PRES circuit is disabled automatically during sleep and hibernate modes, with one exception: During sleep mode the regulators are periodically activated (buzzed) to provide supervisory services and to reduce wakeup time. At these times the PRES circuit is also buzzed to allow periodic voltage monitoring.

ALVI, DLVI, AHVI - Analog/Digital Low Voltage Interrupt, Analog High Voltage Interrupt

Interrupt circuits are available to detect when VDDA and VDDD go outside a voltage range. For AHVI, VDDA is compared to a fixed trip level. For ALVI and DLVI, VDDA and VDDD are compared to trip levels that are programmable, as listed in Table 6-5. ALVI and DLVI can also be configured to generate a device reset instead of an interrupt.

| Table 6-5. Analog/Digital Low Voltage Interrupt, Analog High |

|--------------------------------------------------------------|

| Voltage Interrupt                                            |

| Interrupt | Supply | Normal Voltage<br>Range | Available Trip Settings            |

|-----------|--------|-------------------------|------------------------------------|

| DLVI      | VDDD   | 1.71 V-5.5 V            | 1.70 V-5.45 V in 250 mV increments |

| ALVI      | VDDA   | 1.71 V-5.5 V            | 1.70 V-5.45 V in 250 mV increments |

| AHVI      | VDDA   | 1.71 V-5.5 V            | 5.75 V                             |

The monitors are disabled until after IPOR. During sleep mode these circuits are periodically activated (buzzed). If an interrupt occurs during buzzing then the system first enters its wakeup sequence. The interrupt is then recognized and may be serviced.

The buzz frequency is adjustable, and should be set to be less than the minimum time that any voltage is expected to be out of range. For details on how to adjust the buzz frequency, see the TRM.

#### 6.3.1.2 Other Reset Sources

XRES - External Reset

PSoC 5LP has a dedicated XRES pin, which holds the part in reset while held active (low). The response to an XRES is the same as to an IPOR reset.

The external reset is active low. It includes an internal pull-up resistor. XRES is active during sleep and hibernate modes.

After XRES has been deasserted, at least 10  $\mu s$  must elapse before it can be reasserted.

SRES - Software Reset

A reset can be commanded under program control by setting a bit in the software reset register. This is done either directly by the program or indirectly by DMA access. The response to a SRES is the same as after an IPOR reset.

Another register bit exists to disable this function.

WRES - Watchdog Timer Reset

The watchdog reset detects when the software program is no longer being executed correctly. To indicate to the watchdog timer that it is running correctly, the program must periodically reset the timer. If the timer is not reset before a user-specified amount of time, then a reset is generated.

**Note** IPOR disables the watchdog function. The program must enable the watchdog function at an appropriate point in the code by setting a register bit. When this bit is set, it cannot be cleared again except by an IPOR power on reset event.

## 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the VDDIO pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both General Purpose I/O (GPIO) and Special I/O (SIO) provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense<sup>[8]</sup>, and LCD segment drive, while SIO pins are used for voltages in excess of VDDA and for programmable output voltages.

- Features supported by both GPIO and SIO:

- User programmable port reset state

- Separate I/O supplies and voltages for up to four groups of I/O

- Digital peripherals use DSI to connect the pins

- Input or output or both for CPU and DMA

- Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

- LCD segment drive on LCD equipped devices

- CapSense<sup>[8]</sup>

- Analog input and output capability

- □ Continuous 100 µA clamp current capability

- Standard drive strength down to 1.71 V

- Additional features only provided on SIO pins:

- □ Higher drive strength than GPIO

- Hot swap capability (5 V tolerance at any operating VDD)

- Programmable and regulated high input and output drive levels down to 1.2 V

- No analog input, CapSense, or LCD capability

- Over voltage tolerance up to 5.5 V

- □ SIO can act as a general purpose analog comparator

- USBIO features:

- □ Full speed USB 2.0 compliant I/O

- Highest drive strength for general purpose use

- Input, output, or both for CPU and DMA

- Input, output, or both for digital peripherals

- Digital output (CMOS) drive mode

- Each pin can be an interrupt source configured as rising edge, falling edge, or both edges

Note

#### 7.1.3 Example System Function Components

The following is a sample of the system function components available in PSoC Creator for the CY8C54LP family. The exact amount of hardware resources (UDBs, SC/CT blocks, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- CapSense

- LCD Drive

- LCD Control

- Filters

7.1.4 Designing with PSoC Creator

#### 7.1.4.1 More Than a Typical IDE

A successful design tool allows for the rapid development and deployment of both simple and complex designs. It reduces or eliminates any learning curve. It makes the integration of a new design into the production stream straightforward.

PSoC Creator is that design tool.

PSoC Creator is a full featured Integrated Development Environment (IDE) for hardware and software design. It is optimized specifically for PSoC devices and combines a modern, powerful software development platform with a sophisticated graphical design tool. This unique combination of tools makes PSoC Creator the most flexible embedded design platform available.

Graphical design entry simplifies the task of configuring a particular part. You can select the required functionality from an extensive catalog of components and place it in your design. All components are parameterized and have an editor dialog that allows you to tailor functionality to your needs.

PSoC Creator automatically configures clocks and routes the I/O to the selected pins and then generates APIs to give the application complete control over the hardware. Changing the PSoC device configuration is as simple as adding a new component, setting its parameters, and rebuilding the project.

At any stage of development you are free to change the hardware configuration and even the target processor. To retarget your application (hardware and software) to new devices, even from 8- to 32-bit families, just select the new device and rebuild.

You also have the ability to change the C compiler and evaluate an alternative. Components are designed for portability and are validated against all devices, from all families, and against all supported tool chains. Switching compilers is as easy as editing the from the project options and rebuilding the application with no errors from the generated APIs or boot code.

#### 7.1.4.2 Component Catalog

The component catalog is a repository of reusable design elements that select device functionality and customize your PSoC device. It is populated with an impressive selection of content; from simple primitives such as logic gates and device registers, through the digital timers, counters and PWMs, plus analog components such as ADC, DACs, and filters, and communication protocols, such as I<sup>2</sup>C, and USB. See "Example Peripherals" section on page 40 for more details about available peripherals. All content is fully characterized and carefully documented in datasheets with code examples, AC/DC specifications, and user code ready APIs.

#### 7.1.4.3 Design Reuse

The symbol editor gives you the ability to develop reusable components that can significantly reduce future design time. Just draw a symbol and associate that symbol with your proven design. PSoC Creator allows for the placement of the new symbol anywhere in the component catalog along with the content provided by Cypress. You can then reuse your content as many times as you want, and in any number of projects, without ever having to revisit the details of the implementation.

#### 7.1.4.4 Software Development

Anchoring the tool is a modern, highly customizable user interface. It includes project management and integrated editors for C and assembler source code, as well the design entry tools.

Project build control leverages compiler technology from top commercial vendors such as ARM® Limited, Keil™, and CodeSourcery (GNU). Free versions of Keil C51 and GNU C Compiler (GCC) for ARM, with no restrictions on code size or end product distribution, are included with the tool distribution. Upgrading to more optimizing compilers is a snap with support for the professional Keil C51 product and ARM RealView™ compiler.

#### 7.1.4.5 Nonintrusive Debugging

With JTAG (4-wire) and SWD (2-wire) debug connectivity available on all devices, the PSoC Creator debugger offers full control over the target device with minimum intrusion. Breakpoints and code execution commands are all readily available from toolbar buttons and an impressive lineup of windows—register, locals, watch, call stack, memory and peripherals—make for an unparalleled level of visibility into the system.

PSoC Creator contains all the tools necessary to complete a design, and then to maintain and extend that design for years to come. All steps of the design flow are carefully integrated and optimized for ease-of-use and to maximize productivity.

Independent of the ALU operation, these functions are available:

- Shift left

- Shift right

- Nibble swap

- Bitwise OR mask

## 7.2.2.3 Conditionals

Each datapath has two compares, with bit masking options. Compare operands include the two accumulators and the two data registers in a variety of configurations. Other conditions include zero detect, all ones detect, and overflow. These conditions are the primary datapath outputs, a selection of which can be driven out to the UDB routing matrix. Conditional computation can use the built in chaining to neighboring UDBs to operate on wider data widths without the need to use routing resources.

#### 7.2.2.4 Variable MSB

The most significant bit of an arithmetic and shift function can be programmatically specified. This supports variable width CRC and PRS functions, and in conjunction with ALU output masking, can implement arbitrary width timers, counters and shift blocks.

## 7.2.2.5 Built in CRC/PRS

The datapath has built in support for single cycle Cyclic Redundancy Check (CRC) computation and Pseudo Random Sequence (PRS) generation of arbitrary width and arbitrary polynomial. CRC/PRS functions longer than 8 bits may be implemented in conjunction with PLD logic, or built in chaining may be use to extend the function into neighboring UDBs.

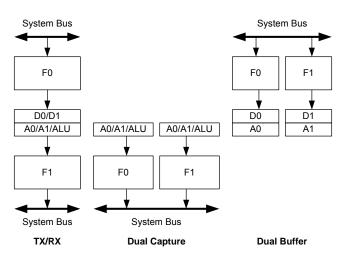

## 7.2.2.6 Input/Output FIFOs

Each datapath contains two four-byte deep FIFOs, which can be independently configured as an input buffer (system bus writes to the FIFO, datapath internal reads the FIFO), or an output buffer (datapath internal writes to the FIFO, the system bus reads from the FIFO). The FIFOs generate status that are selectable as datapath outputs and can therefore be driven to the routing, to interact with sequencers, interrupts, or DMA.

## Figure 7-5. Example FIFO Configurations

## 7.2.2.7 Chaining

The datapath can be configured to chain conditions and signals such as carries and shift data with neighboring datapaths to create higher precision arithmetic, shift, CRC/PRS functions.

## 7.2.2.8 Time Multiplexing

In applications that are over sampled, or do not need high clock rates, the single ALU block in the datapath can be efficiently shared with two sets of registers and condition generators. Carry and shift out data from the ALU are registered and can be selected as inputs in subsequent cycles. This provides support for 16-bit functions in one (8-bit) datapath.

## 7.2.2.9 Datapath I/O

There are six inputs and six outputs that connect the datapath to the routing matrix. Inputs from the routing provide the configuration for the datapath operation to perform in each cycle, and the serial data inputs. Inputs can be routed from other UDB blocks, other device peripherals, device I/O pins, and so on. The outputs to the routing can be selected from the generated conditions, and the serial data outputs. Outputs can be routed to other UDB blocks, device peripherals, interrupt and DMA controller, I/O pins, and so on.

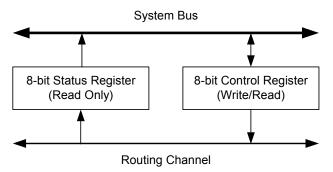

#### 7.2.3 Status and Control Module

The primary purpose of this circuitry is to coordinate CPU firmware interaction with internal UDB operation.

## Figure 7-6. Status and Control Registers

The bits of the control register, which may be written to by the system bus, are used to drive into the routing matrix, and thus provide firmware with the opportunity to control the state of UDB processing. The status register is read-only and it allows internal UDB state to be read out onto the system bus directly from internal routing. This allows firmware to monitor the state of UDB processing. Each bit of these registers has programmable connections to the routing matrix and routing connections are made depending on the requirements of the application.

#### 7.2.3.1 Usage Examples

As an example of control input, a bit in the control register can be allocated as a function enable bit. There are multiple ways to enable a function. In one method the control bit output would be routed to the clock control block in one or more UDBs and serve as a clock enable for the selected UDB blocks. A status example is a case where a PLD or datapath block generated a condition, such as a "compare true" condition that is captured and latched by the status register and then read (and cleared) by CPU firmware.

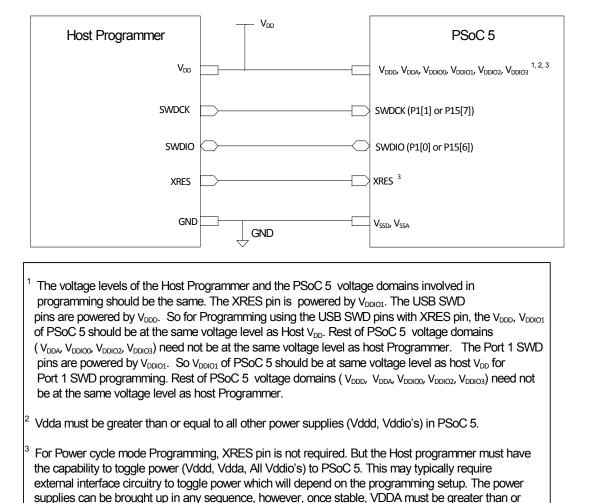

## 9.2 SWD Interface

The SWD interface is the preferred alternative to the JTAG interface. It requires only two pins instead of the four or five needed by JTAG. SWD provides all of the programming and debugging features of JTAG at the same speed. SWD does not provide access to scan chains or device chaining. The SWD clock frequency can be up to 1/3 of the CPU clock frequency.

SWD uses two pins, either two of the JTAG pins (TMS and TCK) or the USBIO D+ and D- pins. The USBIO pins are useful for in system programming of USB solutions that would otherwise require a separate programming connector. One pin is used for the data clock and the other is used for data input and output.

SWD can be enabled on only one of the pin pairs at a time. This only happens if, within 8 µs (key window) after reset, that pin pair

(JTAG or USB) receives a predetermined acquire sequence of 1s and 0s. If the NVL latches are set for SWD (see Section 5.5), this sequence need not be applied to the JTAG pin pair. The acquire sequence must always be applied to the USB pin pair.

SWD is used for debugging or for programming the flash memory.

The SWD interface can be enabled from the JTAG interface or disabled, allowing its pins to be used as GPIO. Unlike JTAG, the SWD interface can always be reacquired on any device during the key window. It can then be used to reenable the JTAG interface, if desired. When using SWD or JTAG pins as standard GPIO, make sure that the GPIO functionality and PCB circuits do not interfere with SWD or JTAG use.

equal to all other supplies.

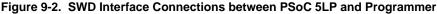

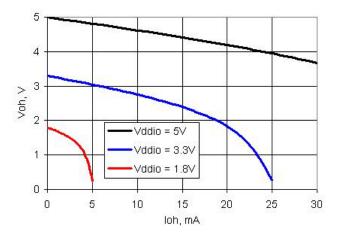

Figure 11-15. GPIO Output High Voltage and Current

Table 11-9. GPIO AC Specifications<sup>[32]</sup>

| Parameter | Description                                                                             | Conditions                            | Min | Тур | Max | Units |

|-----------|-----------------------------------------------------------------------------------------|---------------------------------------|-----|-----|-----|-------|

| TriseF    | Rise time in Fast Strong Mode                                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 6   | ns    |

| TfallF    | Fall time in Fast Strong Mode                                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 6   | ns    |

| TriseS    | Rise time in Slow Strong Mode                                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | -   | 60  | ns    |

| TfallS    | Fall time in Slow Strong Mode                                                           | 3.3 V V <sub>DDIO</sub> Cload = 25 pF | -   | _   | 60  | ns    |

|           | GPIO output operating frequency                                                         |                                       |     |     |     |       |

| Fgpioout  | $2.7 \text{ V} \leq \text{V}_{\text{DDIO}} \leq 5.5 \text{ V}$ , fast strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 33  | MHz   |

|           | $1.71 \text{ V} \leq \text{V}_{\text{DDIO}} < 2.7 \text{ V}$ , fast strong drive mode   | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 20  | MHz   |

|           | $3.3 \text{ V} \le \text{V}_{\text{DDIO}} \le 5.5 \text{ V}$ , slow strong drive mode   | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | _   | 7   | MHz   |

|           | $1.71 \text{ V} \le \text{V}_{\text{DDIO}} < 3.3 \text{ V}$ , slow strong drive mode    | 90/10% V <sub>DDIO</sub> into 25 pF   | -   | -   | 3.5 | MHz   |

| Fgpioin   | GPIO input operating frequency                                                          | 90/10% V <sub>DDIO</sub>              | _   | -   | 33  | MHz   |

## 11.5.6 Current Digital-to-analog Converter (IDAC)

All specifications are based on use of the low-resistance IDAC output pins (see Pin Descriptions on page 11 for details). See the IDAC component data sheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, all charts and graphs show typical values.

## Table 11-30. IDAC DC Specifications

| Parameter        | Description                     | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Min | Тур    | Max   | Units  |

|------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|-------|--------|

|                  | Resolution                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _   | -      | 8     | bits   |

| I <sub>OUT</sub> | Output current at code = 255    | $eq:rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_$ | _   | 2.04   | -     | mA     |

|                  |                                 | Range = 2.04 mA, High mode, code = 255, $V_{DDA} \le 2.7$ V, Rload = 300 $\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _   | 2.04   | _     | mA     |

|                  |                                 | Range = 255 $\mu$ A, code = 255, Rload<br>= 600 $\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -   | 255    | _     | μA     |

|                  |                                 | Range = 31.875 $\mu$ A, code = 255,<br>Rload = 600 $\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -   | 31.875 | -     | μA     |

|                  | Monotonicity                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -   | -      | Yes   |        |

| Ezs              | Zero scale error                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -   | 0      | ±1    | LSB    |

| Eg               | Gain error                      | Range = 2.04 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -   | -      | ±2.5  | %      |

|                  |                                 | Range = 255 µA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -   | -      | ±2.5  | %      |

|                  |                                 | Range = 31.875 µA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -   | -      | ±3.5  | %      |

| TC_Eg            | Temperature coefficient of gain | Range = 2.04 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -   | -      | 0.045 | % / °C |

|                  | error                           | Range = 255 µA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -   | -      | 0.045 | % / °C |