#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 800MHz                                                                 |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                                  |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                       |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers |                                                                        |

| Ethernet                        | 10/100/1000Mbps (4)                                                    |

| SATA                            | -                                                                      |

| USB                             |                                                                        |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | Cryptography, Random Number Generator                                  |

| Package / Case                  | 783-BBGA, FCBGA                                                        |

| Supplier Device Package         | 783-FCBGA (29x29)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8543evuang |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### NOTE

From a system standpoint, if any of the I/O power supplies ramp prior to the  $V_{DD}$  core supply, the I/Os associated with that I/O supply may drive a logic one or zero during power-up, and extra current may be drawn by the device.

# 4 Input Clocks

This section discusses the timing for the input clocks.

# 4.1 System Clock Timing

The following table provides the system clock (SYSCLK) AC timing specifications for the device.

### Table 5. SYSCLK AC Timing Specifications

At recommended operating conditions (see Table 2) with  $OV_{DD} = 3.3 \text{ V} \pm 165 \text{ mV}$ .

| Parameter/Condition       | Symbol                            | Min | Тур | Мах  | Unit | Notes      |

|---------------------------|-----------------------------------|-----|-----|------|------|------------|

| SYSCLK frequency          | f <sub>SYSCLK</sub>               | 16  | —   | 133  | MHz  | 1, 6, 7, 8 |

| SYSCLK cycle time         | t <sub>SYSCLK</sub>               | 7.5 | _   | 60   | ns   | 6, 7, 8    |

| SYSCLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub> | 0.6 | 1.0 | 1.2  | ns   | 2          |

| SYSCLK duty cycle         | t <sub>KHK</sub> ∕tsysclk         | 40  | —   | 60   | %    | 3          |

| SYSCLK jitter             | _                                 | _   | —   | ±150 | ps   | 4, 5       |

Notes:

- Caution: The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

- 2. Rise and fall times for SYSCLK are measured at 0.6 and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the total input jitter—short term and long term—and is guaranteed by design.

- 5. The SYSCLK driver's closed loop jitter bandwidth must be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track SYSCLK drivers with the specified jitter.

- 6. This parameter has been adjusted slower according to the workaround for device erratum GEN 13.

- 7. For spread spectrum clocking. Guidelines are + 0% to -1% down spread at modulation rate between 20 and 60 kHz on SYSCLK.

- 8. System with operating core frequency less than 1200 MHz must limit SYSCLK frequency to 100 MHz maximum.

# 4.2 Real Time Clock Timing

The RTC input is sampled by the platform clock (CCB clock). The output of the sampling latch is then used as an input to the counters of the PIC and the TimeBase unit of the e500. There is no jitter specification. The minimum pulse width of the RTC signal must be greater than 2x the period of the CCB clock. That is, minimum clock high time is  $2 \times t_{CCB}$ , and minimum clock low time is  $2 \times t_{CCB}$ . There is no minimum RTC frequency; RTC may be grounded if not needed.

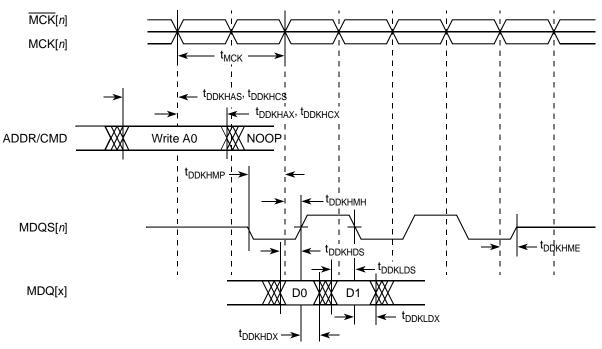

Figure 4 shows the DDR SDRAM output timing diagram.+

Figure 4. DDR SDRAM Output Timing Diagram

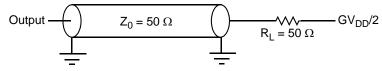

Figure 5 provides the AC test load for the DDR bus.

Figure 5. DDR AC Test Load

DUART

# 7 DUART

This section describes the DC and AC electrical specifications for the DUART interface of the device.

# 7.1 DUART DC Electrical Characteristics

This table provides the DC electrical characteristics for the DUART interface.

### Table 20. DUART DC Electrical Characteristics

| Parameter                                                                 | Symbol          | Min  | Мах                    | Unit |

|---------------------------------------------------------------------------|-----------------|------|------------------------|------|

| High-level input voltage                                                  | V <sub>IH</sub> | 2    | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                   | V <sub>IL</sub> | -0.3 | 0.8                    | V    |

| Input current $(V_{IN}^{1} = 0 V \text{ or } V_{IN} = V_{DD})$            | I <sub>IN</sub> | —    | ±5                     | μA   |

| High-level output voltage ( $OV_{DD} = min, I_{OH} = -2 mA$ )             | V <sub>OH</sub> | 2.4  | —                      | V    |

| Low-level output voltage (OV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA) | V <sub>OL</sub> | —    | 0.4                    | V    |

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

# 7.2 DUART AC Electrical Specifications

This table provides the AC timing parameters for the DUART interface.

### Table 21. DUART AC Timing Specifications

| Parameter         | Value                       | Unit | Notes   |

|-------------------|-----------------------------|------|---------|

| Minimum baud rate | f <sub>CCB</sub> /1,048,576 | baud | 1, 2    |

| Maximum baud rate | f <sub>CCB</sub> /16        | baud | 1, 2, 3 |

| Oversample rate   | 16                          |      | 1, 4    |

Notes:

1. Guaranteed by design.

2. f<sub>CCB</sub> refers to the internal platform clock.

3. Actual attainable baud rate is limited by the latency of interrupt processing.

4. The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

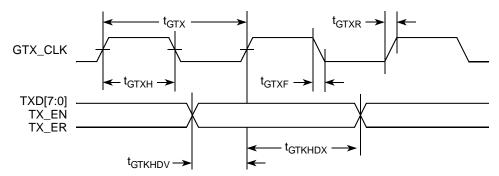

Figure 8 shows the GMII transmit AC timing diagram.

Figure 8. GMII Transmit AC Timing Diagram

### 8.2.2.2 GMII Receive AC Timing Specifications

This table provides the GMII receive AC timing specifications.

| Table 27. GMII Receive AC | Timing Specifications |

|---------------------------|-----------------------|

|---------------------------|-----------------------|

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|

| RX_CLK clock period                         | t <sub>GRX</sub>                    | —   | 8.0 | —   | ns   |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 35  | _   | 75  | ns   |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | _   | —   | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>GRDXKH</sub>                 | 0   | _   | —   | ns   |

| RX_CLK clock rise (20%-80%)                 | t <sub>GRXR</sub> 2                 | —   | _   | 1.0 | ns   |

| RX_CLK clock fall time (80%-20%)            | t <sub>GRXF</sub> 2                 |     |     | 1.0 | ns   |

#### Notes:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GRDVKH</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GRX</sub> represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

2. Guaranteed by design.

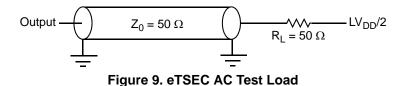

Figure 9 provides the AC test load for eTSEC.

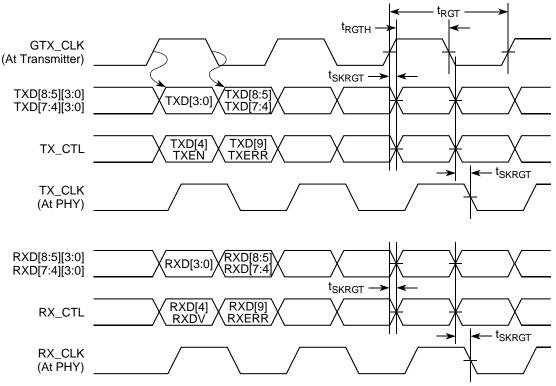

Figure 17. RGMII and RTBI AC Timing and Multiplexing Diagrams

# 8.2.7 RMII AC Timing Specifications

This section describes the RMII transmit and receive AC timing specifications.

## 8.2.7.1 RMII Transmit AC Timing Specifications

The RMII transmit AC timing specifications are in this table.

| Table 34. | RMII Transmit | AC Timing | Specifications |

|-----------|---------------|-----------|----------------|

|-----------|---------------|-----------|----------------|

| Parameter/Condition                       | Symbol <sup>1</sup> | Min  | Тур  | Max  | Unit |

|-------------------------------------------|---------------------|------|------|------|------|

| TSECn_TX_CLK clock period                 | t <sub>RMT</sub>    | 15.0 | 20.0 | 25.0 | ns   |

| TSECn_TX_CLK duty cycle                   | t <sub>RMTH</sub>   | 35   | 50   | 65   | %    |

| TSECn_TX_CLK peak-to-peak jitter          | t <sub>RMTJ</sub>   | _    | _    | 250  | ps   |

| Rise time TSEC <i>n</i> _TX_CLK (20%–80%) | t <sub>RMTR</sub>   | 1.0  | _    | 2.0  | ns   |

| Fall time TSEC <i>n</i> _TX_CLK (80%–20%) | t <sub>RMTF</sub>   | 1.0  | _    | 2.0  | ns   |

#### Local Bus

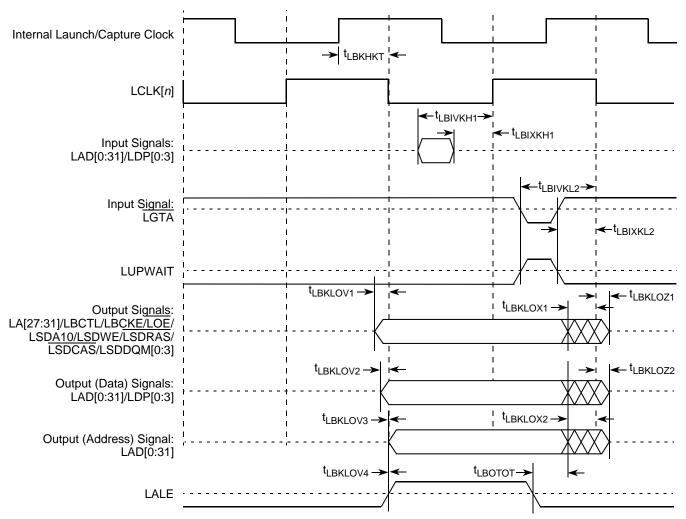

Figure 24. Local Bus Signals (PLL Bypass Mode)

### NOTE

In PLL bypass mode, LCLK[n] is the inverted version of the internal clock with the delay of  $t_{LBKHKT}$ . In this mode, signals are launched at the rising edge of the internal clock and are captured at falling edge of the internal clock with the exception of LGTA/LUPWAIT (which is captured on the rising edge of the internal clock).

#### Local Bus

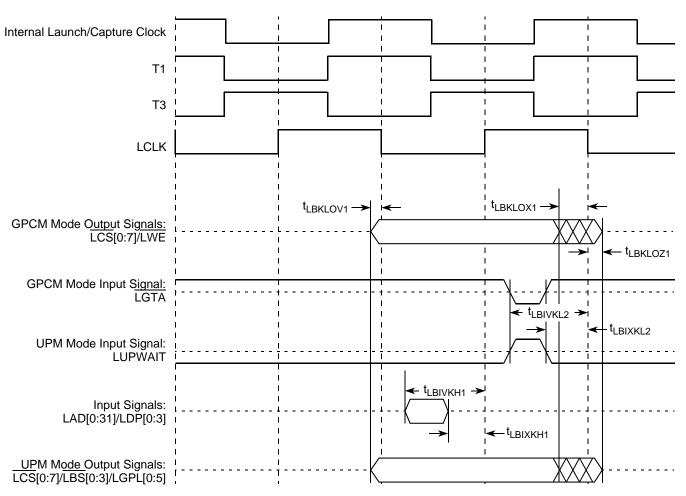

Figure 26. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 (PLL Bypass Mode)

JTAG

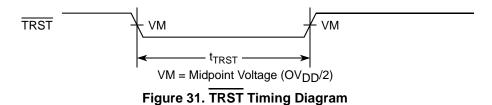

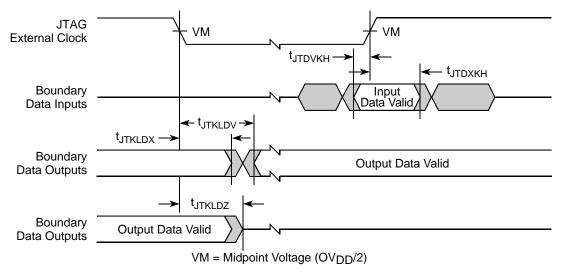

Figure 31 provides the  $\overline{\text{TRST}}$  timing diagram.

Figure 32. Boundary-Scan Timing Diagram

### l<sup>2</sup>C

# 13 I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the I<sup>2</sup>C interfaces of the device.

# **13.1** I<sup>2</sup>C DC Electrical Characteristics

This table provides the DC electrical characteristics for the  $I^2C$  interfaces.

### Table 45. I<sup>2</sup>C DC Electrical Characteristics

| Parameter                                                                                                | Symbol              | Min                  | Мах                                | Unit | Notes |

|----------------------------------------------------------------------------------------------------------|---------------------|----------------------|------------------------------------|------|-------|

| Input high voltage level                                                                                 | V <sub>IH</sub>     | $0.7 \times OV_{DD}$ | OV <sub>DD</sub> + 0.3             | V    | _     |

| Input low voltage level                                                                                  | V <sub>IL</sub>     | -0.3                 | $0.3 	imes OV_{DD}$                | V    | —     |

| Low level output voltage                                                                                 | V <sub>OL</sub>     | 0                    | $0.2 \times \text{OV}_{\text{DD}}$ | V    | 1     |

| Pulse width of spikes which must be suppressed by the input filter                                       | t <sub>I2KHKL</sub> | 0                    | 50                                 | ns   | 2     |

| Input current each I/O pin (input voltage is between $0.1 \times OV_{DD}$ and $0.9 \times OV_{DD}$ (max) | I                   | -10                  | 10                                 | μΑ   | 3     |

| Capacitance for each I/O pin                                                                             | Cl                  | —                    | 10                                 | pF   | —     |

### Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

- 2. See the MPC8548E PowerQUICC<sup>™</sup> III Integrated Processor Family Reference Manual, for information on the digital filter used.

- 3. I/O pins obstruct the SDA and SCL lines if  $\ensuremath{\mathsf{OV}_{\mathsf{DD}}}$  is switched off.

# **13.2** I<sup>2</sup>C AC Electrical Specifications

This table provides the AC timing parameters for the  $I^2C$  interfaces.

Table 46. I<sup>2</sup>C AC Electrical Specifications

| Parameter                                                                                    | Symbol <sup>1</sup> | Min | Max | Unit | Notes |

|----------------------------------------------------------------------------------------------|---------------------|-----|-----|------|-------|

| SCL clock frequency                                                                          | f <sub>I2C</sub>    | 0   | 400 | kHz  | —     |

| Low period of the SCL clock                                                                  | t <sub>I2CL</sub>   | 1.3 | —   | μS   | 4     |

| High period of the SCL clock                                                                 | t <sub>I2CH</sub>   | 0.6 | —   | μS   | 4     |

| Setup time for a repeated START condition                                                    | t <sub>I2SVKH</sub> | 0.6 | —   | μS   | 4     |

| Hold time (repeated) START condition (after this period, the first clock pulse is generated) | t <sub>I2SXKL</sub> | 0.6 | —   | μS   | 4     |

| Data setup time                                                                              | t <sub>I2DVKH</sub> | 100 | —   | ns   | 4     |

| Data input hold time:<br>CBUS compatible masters<br>I <sup>2</sup> C bus devices             | t <sub>I2DXKL</sub> | 0   |     | μs   | 2     |

| Data output delay time:                                                                      | t <sub>I2OVKL</sub> | —   | 0.9 | —    | 3     |

| Set-up time for STOP condition                                                               | t <sub>I2PVKH</sub> | 0.6 | —   | μS   | —     |

| Bus free time between a STOP and START condition                                             | t <sub>I2KHDX</sub> | 1.3 |     | μS   |       |

#### PCI/PCI-X

### Table 54. PCI-X AC Timing Specifications at 133 MHz (continued)

| Parameter                                        | Symbol              | Min | Max | Unit | Notes |

|--------------------------------------------------|---------------------|-----|-----|------|-------|

| HRESET to PCI-X initialization pattern hold time | t <sub>PCRHIX</sub> | 0   | 50  | ns   | 6, 12 |

Notes:

1. See the timing measurement conditions in the PCI-X 1.0a Specification.

- 2. Minimum times are measured at the package pin (not the test point). Maximum times are measured with the test point and load circuit.

- 3. Setup time for point-to-point signals applies to REQ and GNT only. All other signals are bused.

- 4. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 5. Setup time applies only when the device is not driving the pin. Devices cannot drive and receive signals at the same time.

- 6. Maximum value is also limited by delay to the first transaction (time for HRESET high to first configuration access, t<sub>PCRHFV</sub>). The PCI-X initialization pattern control signals after the rising edge of HRESET must be negated no later than two clocks before the first FRAME and must be floated no later than one clock before FRAME is asserted.

- 7. A PCI-X device is permitted to have the minimum values shown for t<sub>PCKHOV</sub> and t<sub>CYC</sub> only in PCI-X mode. In conventional mode, the device must meet the requirements specified in PCI 2.2 for the appropriate clock frequency.

8. Device must meet this specification independent of how many outputs switch simultaneously.

9. The timing parameter t<sub>PCIVKH</sub> is a minimum of 1.4 ns rather than the minimum of 1.2 ns in the PCI-X 1.0a Specification.

- 10. The timing parameter t<sub>PCRHFV</sub> is a minimum of 10 clocks rather than the minimum of 5 clocks in the *PCI-X 1.0a Specification.*

- 11. Guaranteed by characterization.

12. Guaranteed by design.

# 16 High-Speed Serial Interfaces (HSSI)

The device features one Serializer/Deserializer (SerDes) interface to be used for high-speed serial interconnect applications. The SerDes interface can be used for PCI Express and/or serial RapidIO data transfers.

This section describes the common portion of SerDes DC electrical specifications, which is the DC requirement for SerDes reference clocks. The SerDes data lane's transmitter and receiver reference circuits are also shown.

# 16.1 Signal Terms Definition

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

Figure 38 shows how the signals are defined. For illustration purpose, only one SerDes lane is used for the description. The figure shows a waveform for either a transmitter output (SD\_TX and  $\overline{SD}_TX$ ) or a receiver input (SD\_RX and  $\overline{SD}_RX$ ). Each signal swings between A volts and B volts where A > B.

Using this waveform, the definitions are as follows. To simplify the illustration, the following definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signaling environment.

• Single-ended swing

The transmitter output signals and the receiver input signals SD\_TX,  $\overline{SD}_TX$ ,  $\overline{SD}_RX$  and  $\overline{SD}_RX$  each have a peak-to-peak swing of A – B volts. This is also referred as each signal wire's single-ended swing.

- Differential output voltage,  $V_{OD}$  (or differential output swing): The differential output voltage (or swing) of the transmitter,  $V_{OD}$ , is defined as the difference of the two complimentary output voltages:  $V_{SD_TX} - V_{\overline{SD_TX}}$ . The  $V_{OD}$  value can be either positive or negative.

- Differential input voltage, V<sub>ID</sub> (or differential input swing): The differential input voltage (or swing) of the receiver, V<sub>ID</sub>, is defined as the difference of the two complimentary input voltages: V<sub>SD\_RX</sub> – V<sub>SD\_RX</sub>. The V<sub>ID</sub> value can be either positive or negative.

- Differential peak voltage,  $V_{DIFFp}$ The peak value of the differential transmitter output signal or the differential receiver input signal is defined as differential peak voltage,  $V_{DIFFp} = |A - B|$  volts.

- Differential peak-to-peak,  $V_{DIFFp-p}$ Because the differential output signal of the transmitter and the differential input signal of the receiver each range from A – B to –(A – B) volts, the peak-to-peak value of the differential transmitter output signal or the differential receiver input signal is defined as differential peak-to-peak voltage,  $V_{DIFFp-p} = 2 \times V_{DIFFp} = 2 \times |(A - B)|$  volts, which is twice of differential swing in amplitude, or twice of the differential peak. For example, the output differential peak-to-peak voltage can also be calculated as  $V_{TX-DIFFp-p} = 2 \times |V_{OD}|$ .

- Common mode voltage,  $V_{cm}$ The common mode voltage is equal to one half of the sum of the voltages between each conductor

| Symbol                 | Parameter                   | Min | Nom | Max | Unit | Comments                                                                                                                                                 |

|------------------------|-----------------------------|-----|-----|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>crosslink</sub> | Crosslink<br>random timeout | 0   |     | 1   | ms   | This random timeout helps resolve conflicts in crosslink configuration by eventually resulting in only one downstream and one upstream port. See Note 7. |

Notes:

1. No test load is necessarily associated with this value.

- 2. Specified at the measurement point into a timing and voltage compliance test load as shown in Figure 50 and measured over any 250 consecutive TX UIs. (Also see the transmitter compliance eye diagram shown in Figure 48.)

- 3. A T<sub>TX-EYE</sub> = 0.70 UI provides for a total sum of deterministic and random jitter budget of T<sub>TX-JITTER-MAX</sub> = 0.30 UI for the transmitter collected over any 250 consecutive TX UIs. The T<sub>TX-EYE-MEDIAN-to-MAX-JITTER</sub> median is less than half of the total TX jitter budget collected over any 250 consecutive TX UIs. Note that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value.

- 4. The transmitter input impedance shall result in a differential return loss greater than or equal to 12 dB and a common mode return loss greater than or equal to 6 dB over a frequency range of 50 MHz to 1.25 GHz. This input impedance requirement applies to all valid input levels. The reference impedance for return loss measurements is 50  $\Omega$  to ground for both the D+ and D- line (that is, as measured by a vector network analyzer with 50- $\Omega$  probes—see Figure 50). Note that the series capacitors C<sub>TX</sub> is optional for the return loss measurement.

- 5. Measured between 20%–80% at transmitter package pins into a test load as shown in Figure 50 for both V<sub>TX-D+</sub> and V<sub>TX-D-</sub>.

- 6. See Section 4.3.1.8 of the PCI Express Base Specifications Rev 1.0a.

- 7. See Section 4.2.6.3 of the PCI Express Base Specifications Rev 1.0a.

- 8. MPC8548E SerDes transmitter does not have CTX built in. An external AC coupling capacitor is required.

# 17.4.2 Transmitter Compliance Eye Diagrams

The TX eye diagram in Figure 48 is specified using the passive compliance/test measurement load (see Figure 50) in place of any real PCI Express interconnect +RX component.

There are two eye diagrams that must be met for the transmitter. Both eye diagrams must be aligned in time using the jitter median to locate the center of the eye diagram. The different eye diagrams differ in voltage depending whether it is a transition bit or a de-emphasized bit. The exact reduced voltage level of the de-emphasized bit is always relative to the transition bit.

The eye diagram must be valid for any 250 consecutive UIs.

A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The eye diagram is created using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI.

### NOTE

It is recommended that the recovered TX UI is calculated using all edges in the 3500 consecutive UI interval with a fit algorithm using a minimization merit function (for example, least squares and median deviation fits).

Table 72 provides the pin-out listing for the MPC8547E 783 FC-PBGA package.

### NOTE

All note references in the following table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

| Signal                          | Package Pin Number                                                                                                                                                                                     | Pin Type | Power<br>Supply  | Notes    |  |  |  |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|--|--|--|

| PCI1 (One 64-Bit or One 32-Bit) |                                                                                                                                                                                                        |          |                  |          |  |  |  |

| PCI1_AD[63:32]                  | AB14, AC15, AA15, Y16, W16, AB16, AC16,<br>AA16, AE17, AA18, W18, AC17, AD16, AE16,<br>Y17, AC18, AB18, AA19, AB19, AB21, AA20,<br>AC20, AB20, AB22, AC22, AD21, AB23, AF23,<br>AD23, AE23, AC23, AC24 | I/O      | OV <sub>DD</sub> | 17       |  |  |  |

| PCI1_AD[31:0]                   | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15          | I/O      | OV <sub>DD</sub> | 17       |  |  |  |

| PCI1_C_BE[7:4]                  | AF15, AD14, AE15, AD15                                                                                                                                                                                 | I/O      | OV <sub>DD</sub> | 17       |  |  |  |

| PCI1_C_BE[3:0]                  | AF9, AD11, Y12, Y13                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 17       |  |  |  |

| PCI1_PAR64                      | W15                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_GNT[4:1]                   | AG6, AE6, AF5, AH5                                                                                                                                                                                     | 0        | OV <sub>DD</sub> | 5, 9, 35 |  |  |  |

| PCI1_GNT0                       | AG5                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_IRDY                       | AF11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_PAR                        | AD12                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_PERR                       | AC12                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_SERR                       | V13                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2, 4     |  |  |  |

| PCI1_STOP                       | W12                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_TRDY                       | AG11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_REQ[4:1]                   | AH2, AG4, AG3, AH4                                                                                                                                                                                     | I        | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_REQ0                       | AH3                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_CLK                        | AH26                                                                                                                                                                                                   | I        | OV <sub>DD</sub> | 39       |  |  |  |

| PCI1_DEVSEL                     | AH11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_FRAME                      | AE11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_IDSEL                      | AG9                                                                                                                                                                                                    | I        | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_REQ64                      | AF14                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2, 5,10  |  |  |  |

| PCI1_ACK64                      | V15                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| Reserved                        | AE28                                                                                                                                                                                                   | —        | —                | 2        |  |  |  |

| Reserved                        | AD26                                                                                                                                                                                                   | _        | —                | 2        |  |  |  |

| Reserved                        | AD25                                                                                                                                                                                                   | —        | —                | 2        |  |  |  |

### Table 72. MPC8547E Pinout Listing

| Signal                        | Package Pin Number                   | Pin Type  | Power<br>Supply  | Notes          |  |  |

|-------------------------------|--------------------------------------|-----------|------------------|----------------|--|--|

| TSEC2_TX_ER                   | R10                                  | 0         | LV <sub>DD</sub> | 5, 9, 33       |  |  |

| Three-S                       | peed Ethernet Controller (Gigabit Et | hernet 3) |                  | -              |  |  |

| TSEC3_TXD[3:0]                | V8, W10, Y10, W7                     | 0         | TV <sub>DD</sub> | 5, 9, 29       |  |  |

| TSEC3_RXD[3:0]                | Y1, W3, W5, W4                       | I         | TV <sub>DD</sub> | —              |  |  |

| TSEC3_GTX_CLK                 | W8                                   | 0         | TV <sub>DD</sub> | _              |  |  |

| TSEC3_RX_CLK                  | W2                                   | I         | TV <sub>DD</sub> | —              |  |  |

| TSEC3_RX_DV                   | W1                                   | I         | TV <sub>DD</sub> | —              |  |  |

| TSEC3_RX_ER                   | Y2                                   | I         | TV <sub>DD</sub> | —              |  |  |

| TSEC3_TX_CLK                  | V10                                  | I         | TV <sub>DD</sub> | —              |  |  |

| TSEC3_TX_EN                   | V9                                   | 0         | TV <sub>DD</sub> | 30             |  |  |

| Three-S                       | peed Ethernet Controller (Gigabit Et | hernet 4) |                  | -              |  |  |

| TSEC4_TXD[3:0]/TSEC3_TXD[7:4] | AB8, Y7, AA7, Y8                     | 0         | TV <sub>DD</sub> | 1, 5, 9,<br>29 |  |  |

| TSEC4_RXD[3:0]/TSEC3_RXD[7:4] | AA1, Y3, AA2, AA4                    | I         | TV <sub>DD</sub> | 1              |  |  |

| TSEC4_GTX_CLK                 | AA5                                  | 0         | TV <sub>DD</sub> |                |  |  |

| TSEC4_RX_CLK/TSEC3_COL        | Y5                                   | I         | TV <sub>DD</sub> | 1              |  |  |

| TSEC4_RX_DV/TSEC3_CRS         | AA3                                  | I/O       | TV <sub>DD</sub> | 1, 31          |  |  |

| TSEC4_TX_EN/TSEC3_TX_ER       | AB6                                  | 0         | TV <sub>DD</sub> | 1, 30          |  |  |

|                               | DUART                                |           |                  |                |  |  |

| UART_CTS[0:1]                 | AB3, AC5                             | I         | OV <sub>DD</sub> | —              |  |  |

| UART_RTS[0:1]                 | AC6, AD7                             | 0         | OV <sub>DD</sub> | —              |  |  |

| UART_SIN[0:1]                 | AB5, AC7                             | I         | OV <sub>DD</sub> | —              |  |  |

| UART_SOUT[0:1]                | AB7, AD8                             | 0         | OV <sub>DD</sub> | —              |  |  |

|                               | I <sup>2</sup> C Interface           |           |                  | -              |  |  |

| IIC1_SCL                      | AG22                                 | I/O       | OV <sub>DD</sub> | 4, 27          |  |  |

| IIC1_SDA                      | AG21                                 | I/O       | OV <sub>DD</sub> | 4, 27          |  |  |

| IIC2_SCL                      | AG15                                 | I/O       | OV <sub>DD</sub> | 4, 27          |  |  |

| IIC2_SDA                      | AG14                                 | I/O       | OV <sub>DD</sub> | 4, 27          |  |  |

|                               | SerDes                               |           |                  | -              |  |  |

| SD_RX[0:3]                    | M28, N26, P28, R26                   | I         | XV <sub>DD</sub> | —              |  |  |

| SD_RX[0:3]                    | M27, N25, P27, R25                   | I         | XV <sub>DD</sub> |                |  |  |

| SD_TX[0:3]                    | M22, N20, P22, R20                   | 0         | XV <sub>DD</sub> | _              |  |  |

| SD_TX[0:3]                    | M23, N21, P23, R21                   | 0         | XV <sub>DD</sub> | _              |  |  |

| Reserved                      | W26, Y28, AA26, AB28                 | —         | —                | 40             |  |  |

| Reserved                      | W25, Y27, AA25, AB27                 | —         |                  | 40             |  |  |

### Table 72. MPC8547E Pinout Listing (continued)

| Signal           | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Pin Type                                                            | Power<br>Supply  | Notes        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------|--------------|

|                  | DFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I I                                                                 |                  |              |

| L1_TSTCLK        | AC25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I                                                                   | OV <sub>DD</sub> | 25           |

| L2_TSTCLK        | AE22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I                                                                   | OV <sub>DD</sub> | 25           |

| LSSD_MODE        | AH20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I                                                                   | $OV_{DD}$        | 25           |

| TEST_SEL         | AH14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I                                                                   | $OV_{DD}$        | 25           |

|                  | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |                  | •            |

| THERM0           | AG1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —                                                                   | _                | 14           |

| THERM1           | AH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —                                                                   | _                | 14           |

|                  | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     |                  | •            |

| ASLEEP           | AH18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                   | OV <sub>DD</sub> | 9, 19,<br>29 |

|                  | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I I                                                                 |                  |              |

| GND              | A11, B7, B24, C1, C3, C5, C12, C15, C26, D8,<br>D11, D16, D20, D22, E1, E5, E9, E12, E15, E17,<br>F4, F26, G12, G15, G18, G21, G24, H2, H6, H8,<br>H28, J4, J12, J15, J17, J27, K7, K9, K11, K27,<br>L3, L5, L12, L16, N11, N13, N15, N17, N19, P4,<br>P9, P12, P14, P16, P18, R11, R13, R15, R17,<br>R19, T4, T12, T14, T16, T18, U8, U11, U13,<br>U15, U17, U19, V4, V12, V18, W6, W19, Y4, Y9,<br>Y11, Y19, AA6, AA14, AA17, AA22, AA23, AB4,<br>AC2, AC11, AC19, AC26, AD5, AD9, AD22,<br>AE3, AE14, AF6, AF10, AF13, AG8, AG27,<br>K28, L24, L26, N24, N27, P25, R28, T24, T26,<br>U24, V25, W28, Y24, Y26, AA24, AA27, AB25,<br>AC28, L21, L23, N22, P20, R23, T21, U22, V20,<br>W23, Y21, U27 | _                                                                   | _                |              |

| OV <sub>DD</sub> | V16, W11, W14, Y18, AA13, AA21, AB11,<br>AB17, AB24, AC4, AC9, AC21, AD6, AD13,<br>AD17, AD19, AE10, AE8, AE24, AF4, AF12,<br>AF22, AF27, AG26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for PCI<br>and other<br>standards<br>(3.3 V)                  | OV <sub>DD</sub> | _            |

| LV <sub>DD</sub> | N8, R7, T9, U6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>TSEC1 and<br>TSEC2<br>(2.5 V, 3.3 V)                   | LV <sub>DD</sub> | _            |

| TV <sub>DD</sub> | W9, Y6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Power for<br>TSEC3 and<br>TSEC4<br>(2,5 V, 3.3 V)                   | TV <sub>DD</sub> | —            |

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15,<br>E2, E8, E11, E18, F5, F12, F16, G3, G7, G9,<br>G11, H5, H12, H15, H17, J10, K3, K12, K16,<br>K18, L6, M4, M8, M13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Power for<br>DDR1 and<br>DDR2 DRAM<br>I/O voltage<br>(1.8 V, 2.5 V) | GV <sub>DD</sub> | —            |

Package Description

| Signal                 | Package Pin Number                     | Pin Type | Power<br>Supply  | Notes           |

|------------------------|----------------------------------------|----------|------------------|-----------------|

| SD_TX[0:3]             | M23, N21, P23, R21                     | 0        | XV <sub>DD</sub> | —               |

| Reserved               | W26, Y28, AA26, AB28                   | _        | _                | 40              |

| Reserved               | W25, Y27, AA25, AB27                   | —        | —                | 40              |

| Reserved               | U20, V22, W20, Y22                     | —        | —                | 15              |

| Reserved               | U21, V23, W21, Y23                     | —        | —                | 15              |

| SD_PLL_TPD             | U28                                    | 0        | XV <sub>DD</sub> | 24              |

| SD_REF_CLK             | T28                                    | I        | XV <sub>DD</sub> | —               |

| SD_REF_CLK             | T27                                    | I        | XV <sub>DD</sub> | —               |

| Reserved               | AC1, AC3                               | _        | —                | 2               |

| Reserved               | M26, V28                               | _        | —                | 32              |

| Reserved               | M25, V27                               | _        | —                | 34              |

| Reserved               | M20, M21, T22, T23                     | _        | —                | 38              |

|                        | General-Purpose Output                 |          |                  |                 |

| GPOUT[24:31]           | K26, K25, H27, G28, H25, J26, K24, K23 | 0        | BV <sub>DD</sub> | —               |

|                        | System Control                         |          |                  |                 |

| HRESET                 | AG17                                   | I        | OV <sub>DD</sub> | —               |

| HRESET_REQ             | AG16                                   | 0        | OV <sub>DD</sub> | 29              |

| SRESET                 | AG20                                   | I        | OV <sub>DD</sub> | —               |

| CKSTP_IN               | AA9                                    | I        | OV <sub>DD</sub> | —               |

| CKSTP_OUT              | AA8                                    | 0        | OV <sub>DD</sub> | 2, 4            |

|                        | Debug                                  |          | •                |                 |

| TRIG_IN                | AB2                                    | I        | OV <sub>DD</sub> | —               |

| TRIG_OUT/READY/QUIESCE | AB1                                    | 0        | OV <sub>DD</sub> | 6, 9,<br>19, 29 |

| MSRCID[0:1]            | AE4, AG2                               | 0        | OV <sub>DD</sub> | 5, 6, 9         |

| MSRCID[2:4]            | AF3, AF1, AF2                          | 0        | OV <sub>DD</sub> | 6, 19,<br>29    |

| MDVAL                  | AE5                                    | 0        | OV <sub>DD</sub> | 6               |

| CLK_OUT                | AE21                                   | 0        | OV <sub>DD</sub> | 11              |

|                        | Clock                                  |          |                  |                 |

| RTC                    | AF16                                   | I        | OV <sub>DD</sub> | —               |

| SYSCLK                 | AH17                                   | I        | OV <sub>DD</sub> | —               |

|                        | JTAG                                   | •        |                  |                 |

| ТСК                    | AG28                                   | I        | OV <sub>DD</sub> | —               |

| TDI                    | AH28                                   | I        | OV <sub>DD</sub> | 12              |

### Package Description

| Signal        | Package Pin Number | Pin Type                                       | Power<br>Supply       | Notes |

|---------------|--------------------|------------------------------------------------|-----------------------|-------|

| SENSEVSS      | M16                | —                                              | —                     | 13    |

|               | Analog Signals     |                                                |                       |       |

| MVREF         | A18                | l<br>Reference<br>voltage<br>signal for<br>DDR | MVREF                 | _     |

| SD_IMP_CAL_RX | L28                | I                                              | 200 Ω (±1%)<br>to GND | —     |

| SD_IMP_CAL_TX | AB26               | I                                              | 100 Ω (±1%)<br>to GND | —     |

| SD_PLL_TPA    | U26                | 0                                              | AVDD_SRDS             | 24    |

### Table 74. MPC8543E Pinout Listing (continued)

**Note:** All note references in this table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

#### Clocking

|                               | Maxin   |     |          |      |      |       |

|-------------------------------|---------|-----|----------|------|------|-------|

| Characteristic                | 800 MHz |     | 1000 MHz |      | Unit | Notes |

|                               | Min     | Max | Min      | Max  |      |       |

| e500 core processor frequency | 800     | 800 | 800      | 1000 | MHz  | 1, 2  |

### Table 77. Processor Core Clocking Specifications (MPC8543E)

Notes:

1. **Caution:** The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

2.)The minimum e500 core frequency is based on the minimum platform frequency of 333 MHz.

### Table 78. Memory Bus Clocking Specifications (MPC8548E and MPC8547E)

| Characteristic         | Maximum Processor Core Frequency<br>1000, 1200, 1333 MHz |     |     | Notes |

|------------------------|----------------------------------------------------------|-----|-----|-------|

|                        | Min                                                      | Мах |     |       |

| Memory bus clock speed | 166                                                      | 266 | MHz | 1, 2  |

Notes:

1. **Caution:** The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

2. The memory bus speed is half of the DDR/DDR2 data rate, hence, half of the platform clock frequency.

### Table 79. Memory Bus Clocking Specifications (MPC8545E)

| Characteristic         | Maximum Process<br>800, 1000, | Unit | Notes |      |

|------------------------|-------------------------------|------|-------|------|

|                        | Min                           | Мах  |       |      |

| Memory bus clock speed | 166                           | 200  | MHz   | 1, 2 |

Notes:

Caution: The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

2. The memory bus speed is half of the DDR/DDR2 data rate, hence, half of the platform clock frequency.

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4              | 04/2009 | <ul> <li>In Table 1, "Absolute Maximum Ratings <sup>1</sup>," and in Table 2, "Recommended Operating Conditions," moved text, "MII management voltage" from LV<sub>DD</sub>/TV<sub>DD</sub> to OV<sub>DD</sub>, added "Ethernet management" to OVDD row of input voltage section.</li> <li>In Table 5, "SYSCLK AC Timing Specifications," added notes 7 and 8 to SYSCLK frequency and cycle time.</li> <li>In Table 36, "MII Management DC Electrical Characteristics," changed all instances of LV<sub>DD</sub>/OV<sub>DD</sub> to OV<sub>DD</sub>.</li> <li>Modified Section 16, "High-Speed Serial Interfaces (HSSI)," to reflect that there is only one SerDes.</li> <li>Modified DDR clk rate min from 133 to 166 MHz.</li> <li>Modified note in Table 75, "Processor Core Clocking Specifications (MPC8548E and MPC8547E), "."</li> <li>In Table 56, "Differential Transmitter (TX) Output Specifications," modified equations in Comments column, and changed all instances of "LO" to "L0." Also added note 8.</li> <li>In Table 57, "Differential Receiver (RX) Input Specifications," modified equations in Comments column, and in note 3, changed "TRX-EYE-MEDIAN-to-MAX-JITTER," to "T<sub>RX-EYE-MEDIAN-to-MAX-JITTER</sub>."</li> <li>Modified Table 83, "Frequency Options of SYSCLK with Respect to Memory Bus Speeds."</li> <li>Added a note on Section 4.1, "System Clock Timing," to limit the SYSCLK to 100 MHz if the core frequency is less than 1200 MHz</li> <li>In Table 71, "MPC8543E Pinout ListingTable 72, "MPC8547E Pinout ListingTable 73, "MPC8545E Pinout ListingTable 74, "MPC8543E Pinout Listing," added note 5 to LA[28:31].</li> <li>Added note to Table 83, "Frequency Options of SYSCLK with Respect to Memory Bus Speeds."</li> </ul>                                                                                                 |

| 3              | 01/2009 | <ul> <li>[Section 4.6, "Platform Frequency Requirements for PCI-Express and Serial RapidIO." Changed minimum frequency equation to be 527 MHz for PCI x8.</li> <li>In Table 5, added note 7.</li> <li>Section 4.5, "Platform to FIFO Restrictions." Changed platform clock frequency to 4.2.</li> <li>Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1Gb Mbps)—GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics." Added MII after GMII and add 'or 2.5 V' after 3.3 V.</li> <li>In Table 23, modified table title to include GMII, MII, RMII, and TBI.</li> <li>In Table 24 and Table 25, changed clock period minimum to 5.3.</li> <li>In Table 26, Table 27, Table 28, Table 29, and Table 30, removed subtitle from table title.</li> <li>In Table 30 and Figure 15, changed all instances of PMA to TSEC<i>n</i>.</li> <li>In Table 34, Table 35, Figure 18, and Figure 20, changed all instances of REF_CLK to TSEC<i>n</i>_TX_CLK.</li> <li>In Table 36, changed all instances of OV<sub>DD</sub> to LV<sub>DD</sub>/TV<sub>DD</sub>.</li> <li>In Table 36, changed all instances of OV<sub>DD</sub> to LV<sub>DD</sub>/TV<sub>DD</sub>.</li> <li>In Table 37, "MII Management AC Timing Specifications," changed MDC minimum clock pulse width high from 32 to 48 ns.</li> <li>Added new section, Section 16, "High-Speed Serial Interfaces (HSSI)."</li> <li>Section 16.1, "DC Requirements for PCI Express SD_REF_CLK and SD_REF_CLK." Added new paragraph.</li> <li>Section 17.1, "DC Requirements for Serial RapidIO SD_REF_CLK and SD_REF_CLK." Added new paragraph.</li> <li>Added information to Figure 63, both in figure and in note.</li> <li>Section 22.3, "Decoupling Recommendations." Modified the recommendation.</li> <li>Table 87, "Part Numbering Nomenclature." In Silicon Version column added Ver. 2.1.2.</li> </ul> |

### Table 88. Document Revision History (continued)