#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 800MHz                                                                |

| Co-Processors/DSP               | Signal Processing; SPE                                                |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                      |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (4)                                                   |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                      |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                     |

| Package / Case                  | 783-BBGA, FCBGA                                                       |

| Supplier Device Package         | 783-FCBGA (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8543vuang |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Overview

- Memory prefetching of PCI read accesses

- Supports posting of processor-to-PCI and PCI-to-memory writes

- PCI 3.3-V compatible

- Selectable hardware-enforced coherency

- Serial RapidIO<sup>™</sup> interface unit

- Supports RapidIO<sup>™</sup> Interconnect Specification, Revision 1.2

- Both  $1 \times$  and  $4 \times$  LP-serial link interfaces

- Long- and short-haul electricals with selectable pre-compensation

- Transmission rates of 1.25, 2.5, and 3.125 Gbaud (data rates of 1.0, 2.0, and 2.5 Gbps) per lane

- Auto detection of 1- and 4-mode operation during port initialization

- Link initialization and synchronization

- Large and small size transport information field support selectable at initialization time

- 34-bit addressing

- Up to 256 bytes data payload

- All transaction flows and priorities

- Atomic set/clr/inc/dec for read-modify-write operations

- Generation of IO\_READ\_HOME and FLUSH with data for accessing cache-coherent data at a remote memory system

- Receiver-controlled flow control

- Error detection, recovery, and time-out for packets and control symbols as required by the RapidIO specification

- Register and register bit extensions as described in part VIII (Error Management) of the RapidIO specification

- Hardware recovery only

- Register support is not required for software-mediated error recovery.

- Accept-all mode of operation for fail-over support

- Support for RapidIO error injection

- Internal LP-serial and application interface-level loopback modes

- Memory and PHY BIST for at-speed production test

- RapidIO-compatible message unit

- 4 Kbytes of payload per message

- Up to sixteen 256-byte segments per message

- Two inbound data message structures within the inbox

- Capable of receiving three letters at any mailbox

- Two outbound data message structures within the outbox

- Capable of sending three letters simultaneously

- Single segment multicast to up to 32 devIDs

- Chaining and direct modes in the outbox

#### Overview

- Single inbound doorbell message structure

- Facility to accept port-write messages

- PCI Express interface

- PCI Express 1.0a compatible

- Supports x8,x4,x2, and x1 link widths

- Auto-detection of number of connected lanes

- Selectable operation as root complex or endpoint

- Both 32- and 64-bit addressing

- 256-byte maximum payload size

- Virtual channel 0 only

- Traffic class 0 only

- Full 64-bit decode with 32-bit wide windows

- Pin multiplexing for the high-speed I/O interfaces supports one of the following configurations:

- 8 PCI Express

- 4 PCI Express and 4 serial RapidIO

- Power management

- Supports power saving modes: doze, nap, and sleep

- Employs dynamic power management, which automatically minimizes power consumption of blocks when they are idle

- System performance monitor

- Supports eight 32-bit counters that count the occurrence of selected events

- Ability to count up to 512 counter-specific events

- Supports 64 reference events that can be counted on any of the eight counters

- Supports duration and quantity threshold counting

- Burstiness feature that permits counting of burst events with a programmable time between bursts

- Triggering and chaining capability

- Ability to generate an interrupt on overflow

- System access port

- Uses JTAG interface and a TAP controller to access entire system memory map

- Supports 32-bit accesses to configuration registers

- Supports cache-line burst accesses to main memory

- Supports large block (4-Kbyte) uploads and downloads

- Supports continuous bit streaming of entire block for fast upload and download

- JTAG boundary scan, designed to comply with IEEE Std. 1149.1<sup>TM</sup>

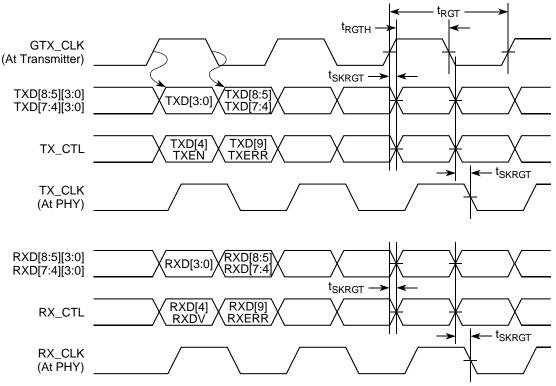

Figure 17. RGMII and RTBI AC Timing and Multiplexing Diagrams

# 8.2.7 RMII AC Timing Specifications

This section describes the RMII transmit and receive AC timing specifications.

# 8.2.7.1 RMII Transmit AC Timing Specifications

The RMII transmit AC timing specifications are in this table.

| Table 34. | RMII Transmit | AC Timing | Specifications |

|-----------|---------------|-----------|----------------|

|-----------|---------------|-----------|----------------|

| Parameter/Condition                       | Symbol <sup>1</sup> | Min  | Тур  | Max  | Unit |

|-------------------------------------------|---------------------|------|------|------|------|

| TSECn_TX_CLK clock period                 | t <sub>RMT</sub>    | 15.0 | 20.0 | 25.0 | ns   |

| TSEC <i>n</i> _TX_CLK duty cycle          | t <sub>RMTH</sub>   | 35   | 50   | 65   | %    |

| TSECn_TX_CLK peak-to-peak jitter          | t <sub>RMTJ</sub>   | _    | _    | 250  | ps   |

| Rise time TSEC <i>n</i> _TX_CLK (20%–80%) | t <sub>RMTR</sub>   | 1.0  | _    | 2.0  | ns   |

| Fall time TSEC <i>n</i> _TX_CLK (80%–20%) | t <sub>RMTF</sub>   | 1.0  | _    | 2.0  | ns   |

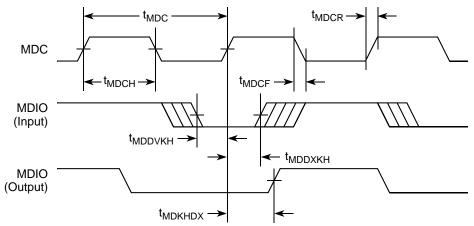

#### **Ethernet Management Interface Electrical Characteristics**

#### Table 37. MII Management AC Timing Specifications (continued)

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  is 3.3 V ± 5%.

| Parameter     | Symbol <sup>1</sup> | Min | Тур | Мах | Unit | Notes |

|---------------|---------------------|-----|-----|-----|------|-------|

| MDC fall time | t <sub>MDHF</sub>   |     |     | 10  | ns   | 4     |

#### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MDKHDX</sub> symbolizes management data timing (MD) for the time t<sub>MDC</sub> from clock reference (K) high (H) until data outputs (D) are invalid (X) or data hold time. Also, t<sub>MDDVKH</sub> symbolizes management data timing (MD) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MDC</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

- 2. This parameter is dependent on the eTSEC system clock speed, which is half of the Platform Frequency (f<sub>CCB</sub>). The actual ECn\_MDC output clock frequency for a specific eTSEC port can be programmed by configuring the MgmtClk bit field of device's MIIMCFG register, based on the platform (CCB) clock running for the device. The formula is: Platform Frequency (CCB) ÷ (2 × Frequency Divider determined by MIICFG[MgmtClk] encoding selection). For example, if MIICFG[MgmtClk] = 000 and the platform (CCB) is currently running at 533 MHz, f<sub>MDC</sub> = 533) ÷ (2 × 4 × 8) = 533) ÷ 64 = 8.3 MHz. That is, for a system running at a particular platform frequency (f<sub>CCB</sub>), the ECn\_MDC output clock frequency can be programmed between maximum f<sub>MDC</sub> = f<sub>CCB</sub> ÷ 64 and minimum f<sub>MDC</sub> = f<sub>CCB</sub> ÷ 448. See 14.5.3.6.6, "MII Management Configuration Register (MIIMCFG)," in the MPC8548E PowerQUICC™ III Integrated Processor Family Reference Manual for more detail.

- 3. The maximum ECn\_MDC output clock frequency is defined based on the maximum platform frequency for device (533 MHz) divided by 64, while the minimum ECn\_MDC output clock frequency is defined based on the minimum platform frequency for device (333 MHz) divided by 448, following the formula described in Note 2 above.

- 4. Guaranteed by design.

- 5. t<sub>CCB</sub> is the platform (CCB) clock period.

Figure 21 shows the MII management AC timing diagram.

Figure 21. MII Management Interface Timing Diagram

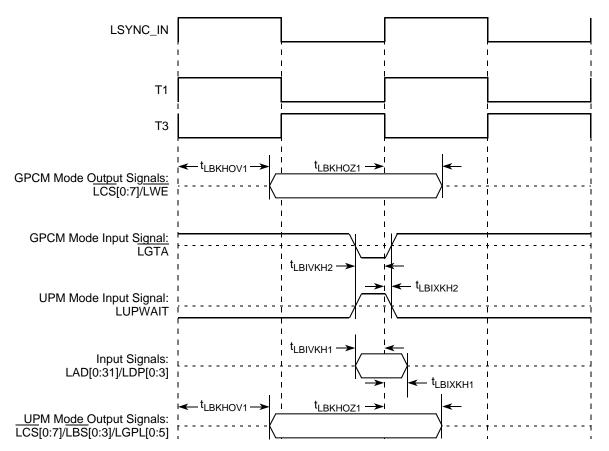

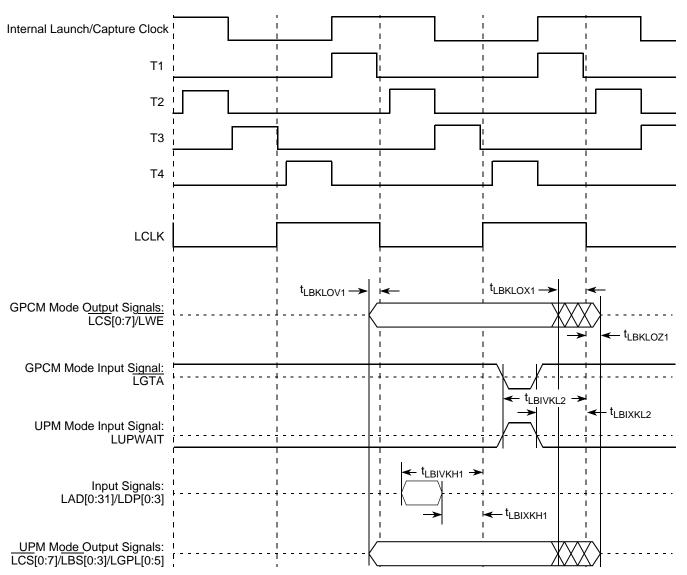

Figure 25. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 (PLL Enabled)

#### Local Bus

Figure 28. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 8 or 16 (PLL Bypass Mode)

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min      | Мах      | Unit | Notes |

|----------------------------------------------------------------------------|--------------------------------------------|----------|----------|------|-------|

| Valid times:<br>Boundary-scan data<br>TDO                                  | t <sub>jtkldv</sub><br>t <sub>jtklov</sub> | 4<br>2   | 20<br>10 | ns   | 5     |

| Output hold times:<br>Boundary-scan data<br>TDO                            | t <sub>jtkldx</sub><br>t <sub>jtklox</sub> | 30<br>30 |          | ns   | 5     |

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>jtkldz</sub><br>t <sub>jtkloz</sub> | 3<br>3   | 19<br>9  | ns   | 5, 6  |

Table 44. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup> (continued)

#### Notes:

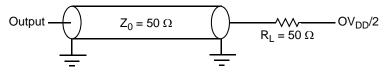

- All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 29). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- 5. Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

- 6. Guaranteed by design.

Figure 29 provides the AC test load for TDO and the boundary-scan outputs.

Figure 29. AC Test Load for the JTAG Interface

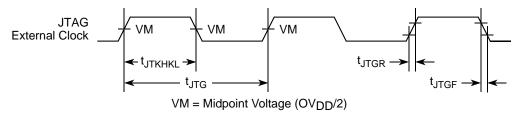

Figure 30 provides the JTAG clock input timing diagram.

Figure 30. JTAG Clock Input Timing Diagram

## Table 53. PCI-X AC Timing Specifications at 66 MHz (continued)

| Parameter                                        | Symbol              | Min | Max | Unit | Notes |

|--------------------------------------------------|---------------------|-----|-----|------|-------|

| HRESET to PCI-X initialization pattern hold time | t <sub>PCRHIX</sub> | 0   | 50  | ns   | 6, 11 |

Notes:

- 1. See the timing measurement conditions in the PCI-X 1.0a Specification.

- 2. Minimum times are measured at the package pin (not the test point). Maximum times are measured with the test point and load circuit.

- 3. Setup time for point-to-point signals applies to REQ and GNT only. All other signals are bused.

- 4. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 5. Setup time applies only when the device is not driving the pin. Devices cannot drive and receive signals at the same time.

- 6. Maximum value is also limited by delay to the first transaction (time for HRESET high to first configuration access, t<sub>PCRHFV</sub>). The PCI-X initialization pattern control signals after the rising edge of HRESET must be negated no later than two clocks before the first FRAME and must be floated no later than one clock before FRAME is asserted.

- 7. A PCI-X device is permitted to have the minimum values shown for t<sub>PCKHOV</sub> and t<sub>CYC</sub> only in PCI-X mode. In conventional mode, the device must meet the requirements specified in PCI 2.2 for the appropriate clock frequency.

- 8. Device must meet this specification independent of how many outputs switch simultaneously.

9. The timing parameter t<sub>PCRHFV</sub> is a minimum of 10 clocks rather than the minimum of 5 clocks in the PCI-X 1.0a Specification.

10.Guaranteed by characterization.

11.Guaranteed by design.

This table provides the PCI-X AC timing specifications at 133 MHz. Note that the maximum PCI-X frequency in synchronous mode is 110 MHz.

| Parameter                                         | Symbol              | Min | Max | Unit   | Notes         |

|---------------------------------------------------|---------------------|-----|-----|--------|---------------|

| SYSCLK to signal valid delay                      | <sup>t</sup> PCKHOV | _   | 3.8 | ns     | 1, 2, 3, 7, 8 |

| Output hold from SYSCLK                           | t <sub>PCKHOX</sub> | 0.7 | _   | ns     | 1, 11         |

| SYSCLK to output high impedance                   | t <sub>PCKHOZ</sub> |     | 7   | ns     | 1, 4, 8, 12   |

| Input setup time to SYSCLK                        | t <sub>PCIVKH</sub> | 1.2 | _   | ns     | 3, 5, 9, 11   |

| Input hold time from SYSCLK                       | t <sub>PCIXKH</sub> | 0.5 | -   | ns     | 11            |

| REQ64 to HRESET setup time                        | t <sub>PCRVRH</sub> | 10  | _   | clocks | 12            |

| HRESET to REQ64 hold time                         | t <sub>PCRHRX</sub> | 0   | 50  | ns     | 12            |

| HRESET high to first FRAME assertion              | t <sub>PCRHFV</sub> | 10  | _   | clocks | 10, 12        |

| PCI-X initialization pattern to HRESET setup time | <sup>t</sup> PCIVRH | 10  |     | clocks | 12            |

#### Table 54. PCI-X AC Timing Specifications at 133 MHz

#### PCI/PCI-X

## Table 54. PCI-X AC Timing Specifications at 133 MHz (continued)

| Parameter                                        | Symbol              | Min | Max | Unit | Notes |

|--------------------------------------------------|---------------------|-----|-----|------|-------|

| HRESET to PCI-X initialization pattern hold time | t <sub>PCRHIX</sub> | 0   | 50  | ns   | 6, 12 |

Notes:

1. See the timing measurement conditions in the PCI-X 1.0a Specification.

- 2. Minimum times are measured at the package pin (not the test point). Maximum times are measured with the test point and load circuit.

- 3. Setup time for point-to-point signals applies to REQ and GNT only. All other signals are bused.

- 4. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 5. Setup time applies only when the device is not driving the pin. Devices cannot drive and receive signals at the same time.

- 6. Maximum value is also limited by delay to the first transaction (time for HRESET high to first configuration access, t<sub>PCRHFV</sub>). The PCI-X initialization pattern control signals after the rising edge of HRESET must be negated no later than two clocks before the first FRAME and must be floated no later than one clock before FRAME is asserted.

- 7. A PCI-X device is permitted to have the minimum values shown for t<sub>PCKHOV</sub> and t<sub>CYC</sub> only in PCI-X mode. In conventional mode, the device must meet the requirements specified in PCI 2.2 for the appropriate clock frequency.

8. Device must meet this specification independent of how many outputs switch simultaneously.

9. The timing parameter t<sub>PCIVKH</sub> is a minimum of 1.4 ns rather than the minimum of 1.2 ns in the PCI-X 1.0a Specification.

- 10. The timing parameter t<sub>PCRHFV</sub> is a minimum of 10 clocks rather than the minimum of 5 clocks in the *PCI-X 1.0a Specification.*

- 11. Guaranteed by characterization.

12. Guaranteed by design.

PCI Express

| Symbol                                      | Parameter                                                                      | Min   | Nom | Мах | Unit | Comments                                                                                                                                                                                             |

|---------------------------------------------|--------------------------------------------------------------------------------|-------|-----|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>RX-CM-ACp</sub>                      | AC peak<br>common mode<br>input voltage                                        |       | _   | 150 | mV   | $V_{\text{RX-CM-ACp}} =  V_{\text{RXD+}} - V_{\text{RXD-}} /2 + V_{\text{RX-CM-DC}}$ $V_{\text{RX-CM-DC}} = DC_{(\text{avg})} \text{ of }  V_{\text{RX-D+}} + V_{\text{RX-D-}}  \div 2.$ See Note 2. |

| RL <sub>RX-DIFF</sub>                       | Differential return loss                                                       | 15    |     | _   | dB   | Measured over 50 MHz to 1.25 GHz with the D+<br>and D– lines biased at +300 mV and –300 mV,<br>respectively. See Note 4.                                                                             |

| RL <sub>RX-CM</sub>                         | Common mode<br>return loss                                                     | 6     |     | —   | dB   | Measured over 50 MHz to 1.25 GHz with the D+<br>and D– lines biased at 0 V. See Note 4.                                                                                                              |

| Z <sub>RX-DIFF-DC</sub>                     | DC differential input impedance                                                | 80    | 100 | 120 | Ω    | RX DC differential mode impedance. See Note 5.                                                                                                                                                       |

| Z <sub>RX-DC</sub>                          | DC input<br>impedance                                                          | 40    | 50  | 60  | Ω    | Required RX D+ as well as D– DC impedance (50 $\pm$ 20% tolerance). See Notes 2 and 5.                                                                                                               |

| Z <sub>RX-HIGH-IMP-DC</sub>                 | Powered down<br>DC input<br>impedance                                          | 200 k | _   | —   | Ω    | Required RX D+ as well as D– DC impedance<br>when the receiver terminations do not have<br>power. See Note 6.                                                                                        |

| V <sub>RX-IDLE-DET-DIFFp-p</sub>            | Electrical idle<br>detect threshold                                            | 65    | _   | 175 | mV   | $V_{RX-IDLE-DET-DIFF_{P-P}} = 2 \times  V_{RX-D+} - V_{RX-D-} .$<br>Measured at the package pins of the receiver                                                                                     |

| T <sub>RX-IDLE-DET-DIFF-</sub><br>ENTERTIME | Unexpected<br>electrical idle<br>enter detect<br>threshold<br>integration time |       | _   | 10  | ms   | An unexpected electrical idle ( $V_{RX-DIFFp-p} < V_{RX-IDLE-DET-DIFFp-p}$ ) must be recognized no longer than $T_{RX-IDLE-DET-DIFF-ENTERING}$ to signal an unexpected idle condition.               |

# Table 57. Differential Receiver (RX) Input Specifications (continued)

**Package Description**

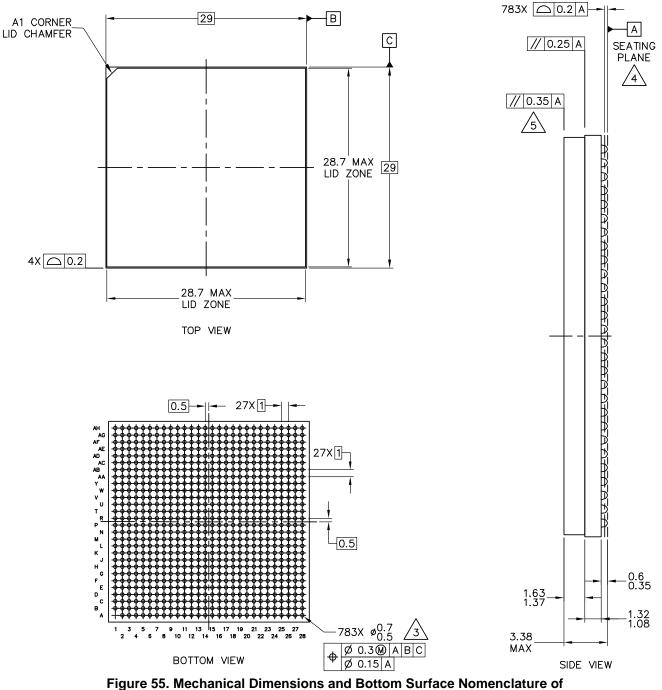

# 19.2 Mechanical Dimensions of the HiCTE FC-CBGA and FC-PBGA with Full Lid

The following figures show the mechanical dimensions and bottom surface nomenclature for the MPC8548E HiCTE FC-CBGA and FC-PBGA packages.

the HiCTE FC-CBGA and FC-PBGA with Full Lid

#### **Package Description**

#### Notes:

- 1. All dimensions are in millimeters.

- 2. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 5. Parallelism measurement shall exclude any effect of mark on top surface of package.

- 6. All dimensions are symmetric across the package center lines unless dimensioned otherwise.

| Signal                        | Package Pin Number                       | Pin Type | Power<br>Supply  | Notes          |

|-------------------------------|------------------------------------------|----------|------------------|----------------|

| Three                         | -Speed Ethernet Controller (Gigabit Ethe | ernet 2) |                  |                |

| TSEC2_RXD[7:0]                | P2, R2, N1, N2, P3, M2, M1, N3           | I        | LV <sub>DD</sub> | _              |

| TSEC2_TXD[7:0]                | N9, N10, P8, N7, R9, N5, R8, N6          | 0        | LV <sub>DD</sub> | 5, 9, 33       |

| TSEC2_COL                     | P1                                       | I        | LV <sub>DD</sub> |                |

| TSEC2_CRS                     | R6                                       | I/O      | LV <sub>DD</sub> | 20             |

| TSEC2_GTX_CLK                 | P6                                       | 0        | LV <sub>DD</sub> |                |

| TSEC2_RX_CLK                  | N4                                       | I        | LV <sub>DD</sub> | —              |

| TSEC2_RX_DV                   | P5                                       | I        | LV <sub>DD</sub> | —              |

| TSEC2_RX_ER                   | R1                                       | I        | LV <sub>DD</sub> | —              |

| TSEC2_TX_CLK                  | P10                                      | I        | LV <sub>DD</sub> | —              |

| TSEC2_TX_EN                   | P7                                       | 0        | LV <sub>DD</sub> | 30             |

| TSEC2_TX_ER                   | R10                                      | 0        | LV <sub>DD</sub> | 5, 9, 33       |

| Three                         | -Speed Ethernet Controller (Gigabit Ethe | ernet 3) |                  |                |

| TSEC3_TXD[3:0]                | V8, W10, Y10, W7                         | 0        | TV <sub>DD</sub> | 5, 9, 29       |

| TSEC3_RXD[3:0]                | Y1, W3, W5, W4                           | I        | TV <sub>DD</sub> | —              |

| TSEC3_GTX_CLK                 | W8                                       | 0        | TV <sub>DD</sub> | —              |

| TSEC3_RX_CLK                  | W2                                       | I        | TV <sub>DD</sub> | —              |

| TSEC3_RX_DV                   | W1                                       | I        | TV <sub>DD</sub> | —              |

| TSEC3_RX_ER                   | Y2                                       | I        | TV <sub>DD</sub> | —              |

| TSEC3_TX_CLK                  | V10                                      | I        | TV <sub>DD</sub> | —              |

| TSEC3_TX_EN                   | V9                                       | 0        | TV <sub>DD</sub> | 30             |

| Three                         | -Speed Ethernet Controller (Gigabit Ethe | ernet 4) |                  |                |

| TSEC4_TXD[3:0]/TSEC3_TXD[7:4] | AB8, Y7, AA7, Y8                         | 0        | TV <sub>DD</sub> | 1, 5, 9,<br>29 |

| TSEC4_RXD[3:0]/TSEC3_RXD[7:4] | AA1, Y3, AA2, AA4                        | I        | TV <sub>DD</sub> | 1              |

| TSEC4_GTX_CLK                 | AA5                                      | 0        | TV <sub>DD</sub> | —              |

| TSEC4_RX_CLK/TSEC3_COL        | Y5                                       | I        | TV <sub>DD</sub> | 1              |

| TSEC4_RX_DV/TSEC3_CRS         | AA3                                      | I/O      | TV <sub>DD</sub> | 1, 31          |

| TSEC4_TX_EN/TSEC3_TX_ER       | AB6                                      | 0        | TV <sub>DD</sub> | 1, 30          |

|                               | DUART                                    |          |                  |                |

| UART_CTS[0:1]                 | AB3, AC5                                 | I        | OV <sub>DD</sub> | —              |

| UART_RTS[0:1]                 | AC6, AD7                                 | 0        | OV <sub>DD</sub> | —              |

| UART_SIN[0:1]                 | AB5, AC7                                 | I        | OV <sub>DD</sub> | -              |

| UART_SOUT[0:1]                | AB7, AD8                                 | 0        | OV <sub>DD</sub> | 1 —            |

# Table 71. MPC8548E Pinout Listing (continued)

|                               |                                      |           | _                |                |

|-------------------------------|--------------------------------------|-----------|------------------|----------------|

| Signal                        | Package Pin Number                   | Pin Type  | Power<br>Supply  | Notes          |

| TSEC2_TX_ER                   | R10                                  | 0         | LV <sub>DD</sub> | 5, 9, 33       |

| Three-S                       | peed Ethernet Controller (Gigabit Et | hernet 3) |                  | -              |

| TSEC3_TXD[3:0]                | V8, W10, Y10, W7                     | 0         | TV <sub>DD</sub> | 5, 9, 29       |

| TSEC3_RXD[3:0]                | Y1, W3, W5, W4                       | I         | TV <sub>DD</sub> | —              |

| TSEC3_GTX_CLK                 | W8                                   | 0         | TV <sub>DD</sub> | _              |

| TSEC3_RX_CLK                  | W2                                   | I         | TV <sub>DD</sub> | —              |

| TSEC3_RX_DV                   | W1                                   | I         | TV <sub>DD</sub> | —              |

| TSEC3_RX_ER                   | Y2                                   | I         | TV <sub>DD</sub> | —              |

| TSEC3_TX_CLK                  | V10                                  | I         | TV <sub>DD</sub> | —              |

| TSEC3_TX_EN                   | V9                                   | 0         | TV <sub>DD</sub> | 30             |

| Three-S                       | peed Ethernet Controller (Gigabit Et | hernet 4) |                  | -              |

| TSEC4_TXD[3:0]/TSEC3_TXD[7:4] | AB8, Y7, AA7, Y8                     | 0         | TV <sub>DD</sub> | 1, 5, 9,<br>29 |

| TSEC4_RXD[3:0]/TSEC3_RXD[7:4] | AA1, Y3, AA2, AA4                    | I         | TV <sub>DD</sub> | 1              |

| TSEC4_GTX_CLK                 | AA5                                  | 0         | TV <sub>DD</sub> |                |

| TSEC4_RX_CLK/TSEC3_COL        | Y5                                   | I         | TV <sub>DD</sub> | 1              |

| TSEC4_RX_DV/TSEC3_CRS         | AA3                                  | I/O       | TV <sub>DD</sub> | 1, 31          |

| TSEC4_TX_EN/TSEC3_TX_ER       | AB6                                  | 0         | TV <sub>DD</sub> | 1, 30          |

|                               | DUART                                |           |                  |                |

| UART_CTS[0:1]                 | AB3, AC5                             | I         | OV <sub>DD</sub> | —              |

| UART_RTS[0:1]                 | AC6, AD7                             | 0         | OV <sub>DD</sub> | —              |

| UART_SIN[0:1]                 | AB5, AC7                             | I         | OV <sub>DD</sub> | —              |

| UART_SOUT[0:1]                | AB7, AD8                             | 0         | OV <sub>DD</sub> | —              |

|                               | I <sup>2</sup> C Interface           |           |                  |                |

| IIC1_SCL                      | AG22                                 | I/O       | OV <sub>DD</sub> | 4, 27          |

| IIC1_SDA                      | AG21                                 | I/O       | OV <sub>DD</sub> | 4, 27          |

| IIC2_SCL                      | AG15                                 | I/O       | OV <sub>DD</sub> | 4, 27          |

| IIC2_SDA                      | AG14                                 | I/O       | OV <sub>DD</sub> | 4, 27          |

|                               | SerDes                               |           |                  | -              |

| SD_RX[0:3]                    | M28, N26, P28, R26                   | I         | XV <sub>DD</sub> | —              |

| SD_RX[0:3]                    | M27, N25, P27, R25                   | I         | XV <sub>DD</sub> |                |

| SD_TX[0:3]                    | M22, N20, P22, R20                   | 0         | XV <sub>DD</sub> | _              |

| SD_TX[0:3]                    | M23, N21, P23, R21                   | 0         | XV <sub>DD</sub> | _              |

| Reserved                      | W26, Y28, AA26, AB28                 | —         | —                | 40             |

| Reserved                      | W25, Y27, AA25, AB27                 | —         |                  | 40             |

# Table 72. MPC8547E Pinout Listing (continued)

Package Description

| Signal         | Package Pin Number                                                                                                                                                                                                                                                                                               | Pin Type | Power<br>Supply  | Notes |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| PCI1_TRDY      | AG11                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2     |

| PCI1_REQ[4:1]  | AH2, AG4, AG3, AH4                                                                                                                                                                                                                                                                                               | I        | OV <sub>DD</sub> |       |

| PCI1_REQ0      | AH3                                                                                                                                                                                                                                                                                                              | I/O      | OV <sub>DD</sub> | —     |

| PCI1_CLK       | AH26                                                                                                                                                                                                                                                                                                             | I        | OV <sub>DD</sub> | 39    |

| PCI1_DEVSEL    | AH11                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2     |

| PCI1_FRAME     | AE11                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2     |

| PCI1_IDSEL     | AG9                                                                                                                                                                                                                                                                                                              | I        | OV <sub>DD</sub> | _     |

| cfg_pci1_width | AF14                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 112   |

| Reserved       | V15                                                                                                                                                                                                                                                                                                              | —        | _                | 110   |

| Reserved       | AE28                                                                                                                                                                                                                                                                                                             | —        | —                | 2     |

| Reserved       | AD26                                                                                                                                                                                                                                                                                                             | —        | _                | 110   |

| Reserved       | AD25                                                                                                                                                                                                                                                                                                             | —        | _                | 110   |

| Reserved       | AE26                                                                                                                                                                                                                                                                                                             | —        | —                | 110   |

| cfg_pci1_clk   | AG24                                                                                                                                                                                                                                                                                                             | I        | OV <sub>DD</sub> | 5     |

| Reserved       | AF25                                                                                                                                                                                                                                                                                                             | —        | _                | 101   |

| Reserved       | AE25                                                                                                                                                                                                                                                                                                             | _        | —                | 110   |

| Reserved       | AG25                                                                                                                                                                                                                                                                                                             | —        | _                | 110   |

| Reserved       | AD24                                                                                                                                                                                                                                                                                                             | —        | _                | 110   |

| Reserved       | AF24                                                                                                                                                                                                                                                                                                             | —        | _                | 110   |

| Reserved       | AD27                                                                                                                                                                                                                                                                                                             | —        | _                | 110   |

| Reserved       | AD28, AE27, W17, AF26                                                                                                                                                                                                                                                                                            | —        | _                | 110   |

| Reserved       | AH25                                                                                                                                                                                                                                                                                                             | —        | _                | 110   |

|                | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                                       |          |                  |       |

| MDQ[0:63]      | L18, J18, K14, L13, L19, M18, L15, L14, A17,<br>B17, A13, B12, C18, B18, B13, A12, H18, F18,<br>J14, F15, K19, J19, H16, K15, D17, G16, K13,<br>D14, D18, F17, F14, E14, A7, A6, D5, A4, C8,<br>D7, B5, B4, A2, B1, D1, E4, A3, B2, D2, E3, F3,<br>G4, J5, K5, F6, G5, J6, K4, J1, K2, M5, M3, J3,<br>J2, L1, M6 | I/O      | GV <sub>DD</sub> | _     |

| MECC[0:7]      | H13, F13, F11, C11, J13, G13, D12, M12                                                                                                                                                                                                                                                                           | I/O      | GV <sub>DD</sub> |       |

| MDM[0:8]       | M17, C16, K17, E16, B6, C4, H4, K1, E13                                                                                                                                                                                                                                                                          | 0        | $GV_DD$          |       |

| MDQS[0:8]      | M15, A16, G17, G14, A5, D3, H1, L2, C13                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> |       |

| MDQS[0:8]      | L17, B16, J16, H14, C6, C2, H3, L4, D13                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> | _     |

| MA[0:15]       | A8, F9, D9, B9, A9, L10, M10, H10, K10, G10,<br>B8, E10, B10, G6, A10, L11                                                                                                                                                                                                                                       | 0        | GV <sub>DD</sub> | _     |

| MBA[0:2]       | F7, J7, M11                                                                                                                                                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —     |

# Table 74. MPC8543E Pinout Listing (continued)

#### Clocking

|                               | Maximum Processor Core Frequency |     |          |      |      |       |

|-------------------------------|----------------------------------|-----|----------|------|------|-------|

| Characteristic                | 800 MHz                          |     | 1000 MHz |      | Unit | Notes |

|                               | Min                              | Max | Min      | Max  |      |       |

| e500 core processor frequency | 800                              | 800 | 800      | 1000 | MHz  | 1, 2  |

## Table 77. Processor Core Clocking Specifications (MPC8543E)

Notes:

1. **Caution:** The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

2.)The minimum e500 core frequency is based on the minimum platform frequency of 333 MHz.

# Table 78. Memory Bus Clocking Specifications (MPC8548E and MPC8547E)

| Characteristic         | Maximum Process<br>1000, 1200 | Unit | Notes |      |

|------------------------|-------------------------------|------|-------|------|

|                        | Min                           | Мах  |       |      |

| Memory bus clock speed | 166                           | 266  | MHz   | 1, 2 |

Notes:

1. **Caution:** The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

2. The memory bus speed is half of the DDR/DDR2 data rate, hence, half of the platform clock frequency.

#### Table 79. Memory Bus Clocking Specifications (MPC8545E)

| Characteristic         | Maximum Process<br>800, 1000, | Unit | Notes |      |

|------------------------|-------------------------------|------|-------|------|

|                        | Min                           | Мах  |       |      |

| Memory bus clock speed | 166                           | 200  | MHz   | 1, 2 |

Notes:

Caution: The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

2. The memory bus speed is half of the DDR/DDR2 data rate, hence, half of the platform clock frequency.

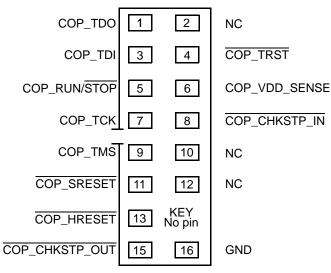

as shown in Figure 63. If this is not possible, the isolation resistor allows future access to  $\overline{\text{TRST}}$  in case a JTAG interface may need to be wired onto the system in future debug situations.

• No pull-up/pull-down is required for TDI, TMS, TDO, or TCK.

Figure 62. COP Connector Physical Pinout

System Design Information

# 22.10 Guidelines for High-Speed Interface Termination

This section provides the guidelines for high-speed interface termination when the SerDes interface is entirely unused and when it is partly unused.

# 22.10.1 SerDes Interface Entirely Unused

If the high-speed SerDes interface is not used at all, the unused pin must be terminated as described in this section.

The following pins must be left unconnected (float):

- SD\_TX[7:0]

- <u>SD\_TX</u>[7:0]

- Reserved pins T22, T23, M20, M21

The following pins must be connected to GND:

- SD\_RX[7:0]

- <u>SD\_RX</u>[7:0]

- SD\_REF\_CLK

- SD\_REF\_CLK

# NOTE

It is recommended to power down the unused lane through SRDSCR1[0:7] register (offset =  $0xE_0F08$ ) (This prevents the oscillations and holds the receiver output in a fixed state.) that maps to SERDES lane 0 to lane 7 accordingly.

Pins V28 and M26 must be tied to  $XV_{DD}$ . Pins V27 and M25 must be tied to GND through a 300- $\Omega$  resistor.

In Rev 2.0 silicon, POR configuration pin cfg\_srds\_en on TSEC4\_TXD[2]/TSEC3\_TXD[6] can be used to power down SerDes block.

# 22.10.2 SerDes Interface Partly Unused

If only part of the high-speed SerDes interface pins are used, the remaining high-speed serial I/O pins must be terminated as described in this section.

The following pins must be left unconnected (float) if not used:

- SD\_TX[7:0]

- <u>SD\_TX</u>[7:0]

- Reserved pins: T22, T23, M20, M21

The following pins must be connected to GND if not used:

- SD\_RX[7:0]

- $\overline{\text{SD}_{RX}}[7:0]$

- SD\_REF\_CLK

# 23 Ordering Information

Ordering information for the parts fully covered by this specification document is provided in Section 23.1, "Part Numbers Fully Addressed by this Document."

# 23.1 Part Numbers Fully Addressed by this Document

This table provides the Freescale part numbering nomenclature for the device. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part-numbering scheme also includes an application modifier that may specify special application conditions. Each part number also contains a revision code that refers to the die mask revision number.

| MPC             | nnnnn              | t                                       | рр                                                               | ff                                                            | С                                          | r                                                                                                                                                                              |

|-----------------|--------------------|-----------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product<br>Code | Part<br>Identifier | Temperature                             | Package <sup>1, 2, 3</sup>                                       | Processor<br>Frequency <sup>4</sup>                           | Core<br>Frequency                          | Silicon Version                                                                                                                                                                |

| MPC             | 8548E<br>8548      | Blank = 0 to 105°C<br>C = −40° to 105°C | HX = CBGA<br>VU = Pb-free CBGA<br>PX = PBGA<br>VT = Pb-free PBGA | AV = 1500 <sup>3</sup><br>AU = 1333<br>AT = 1200<br>AQ = 1000 | J = 533<br>H = 500 <sup>5</sup><br>G = 400 | Blank = Ver. 2.0<br>(SVR = 0x80390020)<br>A = Ver. 2.1.1<br>B = Ver. 2.1.2<br>C = Ver. 2.1.3<br>(SVR = 0x80390021)<br>D = Ver. 3.1.x<br>(SVR = 0x80390031)<br>Blank = Ver. 2.0 |

|                 |                    |                                         |                                                                  |                                                               |                                            | (SVR = 0x80310020)<br>A = Ver. 2.1.1<br>B = Ver. 2.1.2<br>C = Ver. 2.1.3<br>(SVR = 0x80310021)<br>D = Ver. 3.1.x<br>(SVR = 0x80310031)                                         |

|                 | 8547E              |                                         |                                                                  | AU = 1333<br>AT = 1200<br>AQ = 1000                           | J = 533<br>G = 400                         | Blank = Ver. 2.0 (SVR = 0x80390120) A = Ver. 2.1.1 B = Ver. 2.1.2 C = Ver. 2.1.3 (SVR = 0x80390121) D = Ver. 3.1.x (SVR = 0x80390131)                                          |

|                 | 8547               |                                         |                                                                  |                                                               |                                            | Blank = Ver. 2.0 (SVR = 0x80390120)<br>A = Ver. 2.1.1<br>B = Ver. 2.1.2<br>C = Ver. 2.1.3<br>(SVR = 0x80310121)<br>D = Ver. 3.1.x<br>(SVR = 0x80310131)                        |

# Table 87. Part Numbering Nomenclature

...

# 24 Document Revision History

The following table provides a revision history for this hardware specification.

#### Rev. Date Substantive Change(s) Number • Updated Section 21.2, "Thermal for Version 2.1.1, 2.1.2, and 2.1.3 Silicon FC-PBGA with Full Lid and 9 02/2012 Version 3.1.x Silicon with Stamped Lid," with version 3.0 silicon information. Added Figure 56, "Mechanical Dimensions and Bottom Surface Nomenclature of the FC-PBGA with Stamped Lid." • Updated Table 87, "Part Numbering Nomenclature," with version 3.0 silicon information. Removed Note from Section 5.1. "Power-On Ramp Rate". • Changed the Table 10 title to "Power Supply Ramp Rate". • Removed table 11. • Updated the title of Section 21.2, "Thermal for Version 2.1.1, 2.1.2, and 2.1.3 Silicon FC-PBGA with Full Lid and Version 3.1.x Silicon with Stamped Lid" to include Thermal Version 2.1.3 and Version 3.1.x Silicon. Corrected the leaded Solder Ball composition in Table 70, "Package Parameters" • Updated Table 87, "Part Numbering Nomenclature," with Version 3.1.x silicon information. • Updated the Min and Max value of TDO in the valid times row of Table 44, "JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup>" from 4 and 25 to 2 and 10 respectively . 8 04/2011 Added Section 14.1, "GPOUT/GPIN Electrical Characteristics." • Updated Table 71, "MPC8548E Pinout Listing," Table 72, "MPC8547E Pinout Listing," Table 73, "MPC8545E Pinout Listing," and Table 74, "MPC8543E Pinout Listing," to reflect that the TDO signal is not driven during HRSET\* assertion. • Updated Table 87, "Part Numbering Nomenclature" with Ver. 2.1.3 silicon information. In Table 37, "MII Management AC Timing Specifications, modified the fifth row from "MDC to MDIO 7 09/2010 delay tMDKHDX (16 x tptb\_clk x 8) - 3 - (16 x tptb\_clk x 8) + 3" to "MDC to MDIO delay tMDKHDX $(16 \times tCCB \times 8) - 3 - (16 \times tCCB \times 8) + 3."$ Updated Figure 55, "Mechanical Dimensions and Bottom Surface Nomenclature of the HiCTE FC-CBGA and FC-PBGA with Full Lid and figure notes. 6 12/2009 • In Section 5.1, "Power-On Ramp Rate" added explanation that Power-On Ramp Rate is required to avoid falsely triggering ESD circuitry. In Table 13 changed required ramp rate from 545 V/s for MVREF and VDD/XVDD/SVDD to 3500 V/s for MVREF and 4000 V/s for VDD. • In Table 13 deleted ramp rate requirement for XVDD/SVDD. In Table 13 footnote 1 changed voltage range of concern from 0-400 mV to 20-500mV. In Table 13 added footnote 2 explaining that VDD voltage ramp rate is intended to control ramp rate of AVDD pins. 5 10/2009 • In Table 27, "GMII Receive AC Timing Specifications," changed duty cycle specification from 40/60 to 35/75 for RX CLK duty cycle. Updated tMDKHDX in Table 37, "MII Management AC Timing Specifications." • Added a reference to Revision 2.1.2. • Updated Table 55, "MII Management AC Timing Specifications." Added Section 5.1, "Power-On Ramp Rate."

## Table 88. Document Revision History