#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 800MHz                                                                 |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                                  |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                       |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (4)                                                    |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | Cryptography, Random Number Generator                                  |

| Package / Case                  | 783-BBGA, FCBGA                                                        |

| Supplier Device Package         | 783-FCBGA (29x29)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8545evuanj |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Performance monitor facility that is similar to, but separate from, the device performance monitor

The e500 defines features that are not implemented on this device. It also generally defines some features that this device implements more specifically. An understanding of these differences can be critical to ensure proper operations.

- 512-Kbyte L2 cache/SRAM

- Flexible configuration.

- Full ECC support on 64-bit boundary in both cache and SRAM modes

- Cache mode supports instruction caching, data caching, or both.

- External masters can force data to be allocated into the cache through programmed memory ranges or special transaction types (stashing).

- 1, 2, or 4 ways can be configured for stashing only.

- Eight-way set-associative cache organization (32-byte cache lines)

- Supports locking entire cache or selected lines. Individual line locks are set and cleared through Book E instructions or by externally mastered transactions.

- Global locking and Flash clearing done through writes to L2 configuration registers

- Instruction and data locks can be Flash cleared separately.

- SRAM features include the following:

- I/O devices access SRAM regions by marking transactions as snoopable (global).

- Regions can reside at any aligned location in the memory map.

- Byte-accessible ECC is protected using read-modify-write transaction accesses for smaller-than-cache-line accesses.

- Address translation and mapping unit (ATMU)

- Eight local access windows define mapping within local 36-bit address space.

- Inbound and outbound ATMUs map to larger external address spaces.

- Three inbound windows plus a configuration window on PCI/PCI-X and PCI Express

- Four inbound windows plus a default window on RapidIO<sup>™</sup>

- Four outbound windows plus default translation for PCI/PCI-X and PCI Express

- Eight outbound windows plus default translation for RapidIO with segmentation and sub-segmentation support

- DDR/DDR2 memory controller

- Programmable timing supporting DDR and DDR2 SDRAM

- 64-bit data interface

- Four banks of memory supported, each up to 4 Gbytes, to a maximum of 16 Gbytes

- DRAM chip configurations from 64 Mbits to 4 Gbits with ×8/×16 data ports

- Full ECC support

- Page mode support

- Up to 16 simultaneous open pages for DDR

- Dedicated single data rate SDRAM controller

- Parity support

- Default boot ROM chip select with configurable bus width (8, 16, or 32 bits)

- Four enhanced three-speed Ethernet controllers (eTSECs)

- Three-speed support (10/100/1000 Mbps)

- Four controllers designed to comply with IEEE Std. 802.3<sup>®</sup>, 802.3<sup>u</sup>, 802.3<sup>x</sup>, 802.3<sup>z</sup>, 802.3<sup>ac</sup>, and 802.3<sup>ab</sup>

- Support for various Ethernet physical interfaces:

- 1000 Mbps full-duplex IEEE 802.3 GMII, IEEE 802.3z TBI, RTBI, and RGMII

- 10/100 Mbps full and half-duplex IEEE 802.3 MII, IEEE 802.3 RGMII, and RMII

- Flexible configuration for multiple PHY interface configurations. See Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1Gb Mbps)—GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics," for more information.

- TCP/IP acceleration and QoS features available

- IP v4 and IP v6 header recognition on receive

- IP v4 header checksum verification and generation

- TCP and UDP checksum verification and generation

- Per-packet configurable acceleration

- Recognition of VLAN, stacked (queue in queue) VLAN, IEEE Std 802.2<sup>™</sup>, PPPoE session, MPLS stacks, and ESP/AH IP-security headers

- Supported in all FIFO modes

- Quality of service support:

- Transmission from up to eight physical queues

- Reception to up to eight physical queues

- Full- and half-duplex Ethernet support (1000 Mbps supports only full duplex):

- IEEE 802.3 full-duplex flow control (automatic PAUSE frame generation or software-programmed PAUSE frame generation and recognition)

- Programmable maximum frame length supports jumbo frames (up to 9.6 Kbytes) and IEEE Std. 802.1<sup>TM</sup> virtual local area network (VLAN) tags and priority

- VLAN insertion and deletion

- Per-frame VLAN control word or default VLAN for each eTSEC

- Extracted VLAN control word passed to software separately

- Retransmission following a collision

- CRC generation and verification of inbound/outbound frames

- Programmable Ethernet preamble insertion and extraction of up to 7 bytes

- MAC address recognition:

- Exact match on primary and virtual 48-bit unicast addresses

## 2.1.3 Output Driver Characteristics

The following table provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

| Driver Type                           | Programmable<br>Output Impedance<br>(Ω) | Supply<br>Voltage                                    | Notes |

|---------------------------------------|-----------------------------------------|------------------------------------------------------|-------|

| Local bus interface utilities signals | 25<br>25                                | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V | 1     |

|                                       | 45(default)<br>45(default)              | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V |       |

| PCI signals                           | 25                                      | OV <sub>DD</sub> = 3.3 V                             | 2     |

|                                       | 45(default)                             |                                                      |       |

| DDR signal                            | 18<br>36 (half strength mode)           | GV <sub>DD</sub> = 2.5 V                             | 3     |

| DDR2 signal                           | 18<br>36 (half strength mode)           | GV <sub>DD</sub> = 1.8 V                             | 3     |

| TSEC/10/100 signals                   | 45                                      | L/TV <sub>DD</sub> = 2.5/3.3 V                       | —     |

| DUART, system control, JTAG           | 45                                      | OV <sub>DD</sub> = 3.3 V                             | —     |

| 12C                                   | 150                                     | OV <sub>DD</sub> = 3.3 V                             |       |

Table 3. Output Drive Capability

Notes:

1. The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

2. The drive strength of the PCI interface is determined by the setting of the PCI\_GNT1 signal at reset.

3. The drive strength of the DDR interface in half-strength mode is at  $T_i = 105^{\circ}C$  and at  $GV_{DD}$  (min).

## 2.2 Power Sequencing

The device requires its power rails to be applied in a specific sequence in order to ensure proper device operation. These requirements are as follows for power-up:

- 1. V<sub>DD</sub>, AV<sub>DD</sub>, BV<sub>DD</sub>, LV<sub>DD</sub>, OV<sub>DD</sub>, SV<sub>DD</sub>, TV<sub>DD</sub>, XV<sub>DD</sub>

- 2.  $GV_{DD}$

All supplies must be at their stable values within 50 ms.

## NOTE

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

## NOTE

In order to guarantee MCKE low during power-up, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power-up, then the sequencing for  $GV_{DD}$  is not required.

DUART

# 7 DUART

This section describes the DC and AC electrical specifications for the DUART interface of the device.

## 7.1 DUART DC Electrical Characteristics

This table provides the DC electrical characteristics for the DUART interface.

## Table 20. DUART DC Electrical Characteristics

| Parameter                                                                 | Symbol          | Min  | Мах                    | Unit |

|---------------------------------------------------------------------------|-----------------|------|------------------------|------|

| High-level input voltage                                                  | V <sub>IH</sub> | 2    | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                   | V <sub>IL</sub> | -0.3 | 0.8                    | V    |

| Input current $(V_{IN}^{1} = 0 V \text{ or } V_{IN} = V_{DD})$            | I <sub>IN</sub> | —    | ±5                     | μΑ   |

| High-level output voltage ( $OV_{DD} = min, I_{OH} = -2 mA$ )             | V <sub>OH</sub> | 2.4  | —                      | V    |

| Low-level output voltage (OV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA) | V <sub>OL</sub> | —    | 0.4                    | V    |

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

## 7.2 DUART AC Electrical Specifications

This table provides the AC timing parameters for the DUART interface.

## Table 21. DUART AC Timing Specifications

| Parameter         | Value                       | Unit | Notes   |

|-------------------|-----------------------------|------|---------|

| Minimum baud rate | f <sub>CCB</sub> /1,048,576 | baud | 1, 2    |

| Maximum baud rate | f <sub>CCB</sub> /16        | baud | 1, 2, 3 |

| Oversample rate   | 16                          |      | 1, 4    |

Notes:

1. Guaranteed by design.

2. f<sub>CCB</sub> refers to the internal platform clock.

3. Actual attainable baud rate is limited by the latency of interrupt processing.

4. The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

| Parameter                                                             | Symbol <sup>1</sup>  | Min  | Max  | Unit | Notes |

|-----------------------------------------------------------------------|----------------------|------|------|------|-------|

| LGTA/LUPWAIT input hold from local bus clock                          | t <sub>LBIXKL2</sub> | -1.3 |      | ns   | 4, 5  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | t <sub>LBOTOT</sub>  | 1.5  |      | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)             | t <sub>LBKLOV1</sub> | _    | -0.3 | ns   |       |

| Local bus clock to data valid for LAD/LDP                             | t <sub>LBKLOV2</sub> | _    | -0.1 | ns   | 4     |

| Local bus clock to address valid for LAD                              | t <sub>LBKLOV3</sub> | _    | 0    | ns   | 4     |

| Local bus clock to LALE assertion                                     | t <sub>LBKLOV4</sub> | _    | 0    | ns   | 4     |

| Output hold from local bus clock (except LAD/LDP and LALE)            | t <sub>LBKLOX1</sub> | -3.7 |      | ns   | 4     |

| Output hold from local bus clock for LAD/LDP                          | t <sub>LBKLOX2</sub> | -3.7 |      | ns   | 4     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)    | t <sub>LBKLOZ1</sub> | _    | 0.2  | ns   | 7     |

| Local bus clock to output high impedance for LAD/LDP                  | t <sub>LBKLOZ2</sub> | _    | 0.2  | ns   | 7     |

#### Table 42. Local Bus Timing Parameters—PLL Bypassed (continued)

#### Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKH0X</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

All timings are in reference to local bus clock for PLL bypass mode. Timings may be negative with respect to the local bus clock because the actual launch and capture of signals is done with the internal launch/capture clock, which precedes LCLK by t<sub>LBKHKT</sub>.

Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

4. All signals are measured from  $BV_{DD}/2$  of the rising edge of local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 3.3-V signaling levels.

5. Input timings are measured at the pin.

6. The value of t<sub>LBOTOT</sub> is the measurement of the minimum time between the negation of LALE and any change in LAD.

7. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 8. Guaranteed by characterization.

- 9. Guaranteed by design.

| Symbol                            | Parameter                                                                                                            | Min | Nom | Max           | Unit | Comments                                                                                                                                                                                                                                 |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------|-----|-----|---------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>TX-DC-CM</sub>             | The TX DC<br>common mode<br>voltage                                                                                  | 0   | —   | 3.6           | V    | The allowed DC common mode voltage under any conditions. See Note 6.                                                                                                                                                                     |

| I <sub>TX-SHORT</sub>             | TX short circuit<br>current limit                                                                                    | —   | —   | 90            | mA   | The total current the transmitter can provide when shorted to its ground                                                                                                                                                                 |

| T <sub>TX-IDLE-MIN</sub>          | Minimum time<br>spent in<br>electrical idle                                                                          | 50  | _   |               | UI   | Minimum time a transmitter must be in electrical<br>idle utilized by the receiver to start looking for an<br>electrical idle exit after successfully receiving an<br>electrical idle ordered set                                         |

| T <sub>TX-IDLE-SET-TO-IDLE</sub>  | Maximum time<br>to transition to a<br>valid electrical<br>idle after<br>sending an<br>electrical idle<br>ordered set | _   | _   | 20            | UI   | After sending an electrical idle ordered set, the transmitter must meet all electrical idle specifications within this time. This is considered a debounce time for the transmitter to meet electrical idle after transitioning from L0. |

| T <sub>TX-IDLE-TO-DIFF-DATA</sub> | Maximum time<br>to transition to<br>valid TX<br>specifications<br>after leaving an<br>electrical idle<br>condition   | _   | _   | 20            | UI   | Maximum time to meet all TX specifications when<br>transitioning from electrical idle to sending<br>differential data. This is considered a debounce<br>time for the TX to meet all TX specifications after<br>leaving electrical idle   |

| RL <sub>TX-DIFF</sub>             | Differential return loss                                                                                             | 12  | —   | _             | dB   | Measured over 50 MHz to 1.25 GHz.<br>See Note 4.                                                                                                                                                                                         |

| RL <sub>TX-CM</sub>               | Common mode<br>return loss                                                                                           | 6   | —   | —             | dB   | Measured over 50 MHz to 1.25 GHz.<br>See Note 4.                                                                                                                                                                                         |

| Z <sub>TX-DIFF-DC</sub>           | DC differential<br>TX impedance                                                                                      | 80  | 100 | 120           | Ω    | TX DC differential mode low impedance                                                                                                                                                                                                    |

| Z <sub>TX-DC</sub>                | Transmitter DC impedance                                                                                             | 40  | —   | —             | Ω    | Required TX D+ as well as D– DC impedance during all states                                                                                                                                                                              |

| L <sub>TX-SKEW</sub>              | Lane-to-lane<br>output skew                                                                                          | _   | —   | 500<br>+ 2 UI | ps   | Static skew between any two transmitter lanes within a single Link                                                                                                                                                                       |

| C <sub>TX</sub>                   | AC coupling capacitor                                                                                                | 75  | _   | 200           | nF   | All transmitters shall be AC coupled. The AC coupling is required either within the media or within the transmitting component itself. See note 8.                                                                                       |

## 18.5 Explanatory Note on Transmitter and Receiver Specifications

AC electrical specifications are given for transmitter and receiver. Long- and short-run interfaces at three baud rates (a total of six cases) are described.

The parameters for the AC electrical specifications are guided by the XAUI electrical interface specified in Clause 47 of IEEE 802.3ae-2002.

XAUI has similar application goals to Serial RapidIO, as described in Section 8.1. The goal of this standard is that electrical designs for Serial RapidIO can reuse electrical designs for XAUI, suitably modified for applications at the baud intervals and reaches described herein.

## 18.6 Transmitter Specifications

LP-serial transmitter electrical and timing specifications are stated in the text and tables of this section.

The differential return loss, S11, of the transmitter in each case shall be better than:

- -10 dB for (baud frequency)/10 < Freq(f) < 625 MHz, and

- $-10 \text{ dB} + 10\log(f/625 \text{ MHz}) \text{ dB}$  for  $625 \text{ MHz} \le \text{Freq}(f) \le \text{baud}$  frequency

The reference impedance for the differential return loss measurements is  $100-\Omega$  resistive. Differential return loss includes contributions from on-chip circuitry, chip packaging, and any off-chip components related to the driver. The output impedance requirement applies to all valid output levels.

It is recommended that the 20%–80% rise/fall time of the transmitter, as measured at the transmitter output, in each case have a minimum value 60 ps.

It is recommended that the timing skew at the output of an LP-serial transmitter between the two signals that comprise a differential pair not exceed 25 ps at 1.25 GB, 20 ps at 2.50 GB, and 15 ps at 3.125 GB.

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                         |

|-----------------------------|---------------------|-------|------|--------|-------------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Unit   | Notes                                                                         |

| Output voltage              | Vo                  | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal<br>comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mV p-p | _                                                                             |

| Deterministic jitter        | J <sub>D</sub>      | _     | 0.17 | UI p-p | _                                                                             |

| Total jitter                | J <sub>T</sub>      | _     | 0.35 | UI p-p | _                                                                             |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link              |

| Unit Interval               | UI                  | 800   | 800  | ps     | ±100 ppm                                                                      |

| Table 59. Short Run Transmitter | AC Timing Spe | cifications—1.25 GBaud |

|---------------------------------|---------------|------------------------|

|                                 | Ao mining ope |                        |

#### Serial RapidIO

| Characteristic              | Symbol              | Range |         | Unit   | Notes                                                                      |

|-----------------------------|---------------------|-------|---------|--------|----------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | lin Max | Onit   | NOICES                                                                     |

| Output voltage              | V <sub>O</sub>      | -0.40 | 2.30    | V      | Voltage relative to COMMON of either signal comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 800   | 1600    | mVp-p  | —                                                                          |

| Deterministic jitter        | J <sub>D</sub>      | —     | 0.17    | UI p-p | —                                                                          |

| Total jitter                | J <sub>T</sub>      | —     | 0.35    | UI p-p | —                                                                          |

| Multiple output skew        | S <sub>MO</sub>     | —     | 1000    | ps     | Skew at the transmitter output between lanes of a multilane link           |

| Unit interval               | UI                  | 400   | 400     | ps     | ±100 ppm                                                                   |

## Table 64. Long Run Transmitter AC Timing Specifications—3.125 GBaud

| Characteristic              | Symbol              | Range   |      | Unit   | Notes                                                                         |

|-----------------------------|---------------------|---------|------|--------|-------------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min Max | Onic | NULES  |                                                                               |

| Output voltage              | V <sub>O</sub>      | -0.40   | 2.30 | V      | Voltage relative to COMMON of either signal<br>comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 800     | 1600 | mVp-p  | —                                                                             |

| Deterministic jitter        | J <sub>D</sub>      | —       | 0.17 | UI p-p | —                                                                             |

| Total jitter                | J <sub>T</sub>      | —       | 0.35 | UI p-p | —                                                                             |

| Multiple output skew        | S <sub>MO</sub>     | —       | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link              |

| Unit interval               | UI                  | 320     | 320  | ps     | ±100 ppm                                                                      |

For each baud rate at which an LP-serial transmitter is specified to operate, the output eye pattern of the transmitter shall fall entirely within the unshaded portion of the transmitter output compliance mask shown in Figure 52 with the parameters specified in Table 65 when measured at the output pins of the device and the device is driving a  $100-\Omega \pm 5\%$  differential resistive load. The output eye pattern of an LP-serial

components are included in this requirement. The reference impedance for return loss measurements is  $100-\Omega$  resistive for differential return loss and  $25-\Omega$  resistive for common mode.

| Characteristic                                     | Symbol          | Range |                   | Unit   | Notes                                                        |

|----------------------------------------------------|-----------------|-------|-------------------|--------|--------------------------------------------------------------|

| Characteristic                                     | Symbol          | Min   | Max               | Unit   | NOICS                                                        |

| Differential input voltage                         | V <sub>IN</sub> | 200   | 1600              | mVp-p  | Measured at receiver                                         |

| Deterministic jitter tolerance                     | J <sub>D</sub>  | 0.37  | —                 | UI p-p | Measured at receiver                                         |

| Combined deterministic and random jitter tolerance | J <sub>DR</sub> | 0.55  | —                 | UI p-p | Measured at receiver                                         |

| Total jitter tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65  | _                 | UI p-p | Measured at receiver                                         |

| Multiple input skew                                | S <sub>MI</sub> | —     | 24                | ns     | Skew at the receiver input between lanes of a multilane link |

| Bit error rate                                     | BER             | —     | 10 <sup>-12</sup> | —      | —                                                            |

| Unit interval                                      | UI              | 800   | 800               | ps     | ±100 ppm                                                     |

#### Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter, and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 53. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk, and other variable system effects.

### Table 67. Receiver AC Timing Specifications—2.5 GBaud

| Characteristic                                     | Symbol          | Range |                   | Unit   | Notes                                                        |

|----------------------------------------------------|-----------------|-------|-------------------|--------|--------------------------------------------------------------|

| Characteristic                                     | Symbol          | Min   | Max               | Unit   | NULES                                                        |

| Differential input voltage                         | V <sub>IN</sub> | 200   | 1600              | mVp-p  | Measured at receiver                                         |

| Deterministic jitter tolerance                     | J <sub>D</sub>  | 0.37  | _                 | UI p-p | Measured at receiver                                         |

| Combined deterministic and random jitter tolerance | J <sub>DR</sub> | 0.55  | —                 | UI p-p | Measured at receiver                                         |

| Total jitter tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65  | —                 | UI p-p | Measured at receiver                                         |

| Multiple input skew                                | S <sub>MI</sub> | _     | 24                | ns     | Skew at the receiver input between lanes of a multilane link |

| Bit error rate                                     | BER             | _     | 10 <sup>-12</sup> |        | —                                                            |

| Unit interval                                      | UI              | 400   | 400               | ps     | ±100 ppm                                                     |

#### Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter, and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 53. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk, and other variable system effects.

## **19 Package Description**

This section details package parameters, pin assignments, and dimensions.

## **19.1 Package Parameters**

The package parameters for both the HiCTE FC-CBGA and FC-PBGA are provided in Table 70.

| Parameter               | CBGA <sup>1</sup> | PBGA <sup>2</sup> |

|-------------------------|-------------------|-------------------|

| Package outline         | 29 mm × 29 mm     | 29 mm × 29 mm     |

| Interconnects           | 783               | 783               |

| Ball pitch              | 1 mm              | 1 mm              |

| Ball diameter (typical) | 0.6 mm            | 0.6 mm            |

| Solder ball             | 63% Sn            | 63% Sn            |

|                         | 37% Pb            | 37% Pb            |

|                         | 0% Ag             | 0% Ag             |

| Solder ball (lead-free) | 95% Sn            | 96.5% Sn          |

|                         | 4.5% Ag           | 3.5% Ag           |

|                         | 0.5% Cu           |                   |

Table 70. Package Parameters

Notes:

1. The HiCTE FC-CBGA package is available on only Version 2.0 of the device.

2. The FC-PBGA package is available on only versions 2.1.1 and 2.1.2, and 3.0 of the device.

| Signal                        | Package Pin Number                       | Pin Type | Power<br>Supply  | Notes          |

|-------------------------------|------------------------------------------|----------|------------------|----------------|

| Three                         | -Speed Ethernet Controller (Gigabit Ethe | ernet 2) |                  |                |

| TSEC2_RXD[7:0]                | P2, R2, N1, N2, P3, M2, M1, N3           | I        | LV <sub>DD</sub> | _              |

| TSEC2_TXD[7:0]                | N9, N10, P8, N7, R9, N5, R8, N6          | 0        | LV <sub>DD</sub> | 5, 9, 33       |

| TSEC2_COL                     | P1                                       | I        | LV <sub>DD</sub> |                |

| TSEC2_CRS                     | R6                                       | I/O      | LV <sub>DD</sub> | 20             |

| TSEC2_GTX_CLK                 | P6                                       | 0        | LV <sub>DD</sub> |                |

| TSEC2_RX_CLK                  | N4                                       | I        | LV <sub>DD</sub> | —              |

| TSEC2_RX_DV                   | P5                                       | I        | LV <sub>DD</sub> | —              |

| TSEC2_RX_ER                   | R1                                       | I        | LV <sub>DD</sub> | —              |

| TSEC2_TX_CLK                  | P10                                      | I        | LV <sub>DD</sub> | —              |

| TSEC2_TX_EN                   | P7                                       | 0        | LV <sub>DD</sub> | 30             |

| TSEC2_TX_ER                   | R10                                      | 0        | LV <sub>DD</sub> | 5, 9, 33       |

| Three                         | -Speed Ethernet Controller (Gigabit Ethe | ernet 3) |                  |                |

| TSEC3_TXD[3:0]                | V8, W10, Y10, W7                         | 0        | TV <sub>DD</sub> | 5, 9, 29       |

| TSEC3_RXD[3:0]                | Y1, W3, W5, W4                           | I        | TV <sub>DD</sub> | —              |

| TSEC3_GTX_CLK                 | W8                                       | 0        | TV <sub>DD</sub> | —              |

| TSEC3_RX_CLK                  | W2                                       | I        | TV <sub>DD</sub> | —              |

| TSEC3_RX_DV                   | W1                                       | I        | TV <sub>DD</sub> | —              |

| TSEC3_RX_ER                   | Y2                                       | I        | TV <sub>DD</sub> | —              |

| TSEC3_TX_CLK                  | V10                                      | I        | TV <sub>DD</sub> | —              |

| TSEC3_TX_EN                   | V9                                       | 0        | TV <sub>DD</sub> | 30             |

| Three                         | -Speed Ethernet Controller (Gigabit Ethe | ernet 4) |                  |                |

| TSEC4_TXD[3:0]/TSEC3_TXD[7:4] | AB8, Y7, AA7, Y8                         | 0        | TV <sub>DD</sub> | 1, 5, 9,<br>29 |

| TSEC4_RXD[3:0]/TSEC3_RXD[7:4] | AA1, Y3, AA2, AA4                        | I        | TV <sub>DD</sub> | 1              |

| TSEC4_GTX_CLK                 | AA5                                      | 0        | TV <sub>DD</sub> | —              |

| TSEC4_RX_CLK/TSEC3_COL        | Y5                                       | I        | TV <sub>DD</sub> | 1              |

| TSEC4_RX_DV/TSEC3_CRS         | AA3                                      | I/O      | TV <sub>DD</sub> | 1, 31          |

| TSEC4_TX_EN/TSEC3_TX_ER       | AB6                                      | 0        | TV <sub>DD</sub> | 1, 30          |

|                               | DUART                                    |          |                  |                |

| UART_CTS[0:1]                 | AB3, AC5                                 | I        | OV <sub>DD</sub> | —              |

| UART_RTS[0:1]                 | AC6, AD7                                 | 0        | OV <sub>DD</sub> | —              |

| UART_SIN[0:1]                 | AB5, AC7                                 | I        | OV <sub>DD</sub> | -              |

| UART_SOUT[0:1]                | AB7, AD8                                 | 0        | OV <sub>DD</sub> | 1 —            |

## Table 71. MPC8548E Pinout Listing (continued)

| Signal                        | Package Pin Number                   | Pin Type  | Power<br>Supply  | Notes          |  |  |

|-------------------------------|--------------------------------------|-----------|------------------|----------------|--|--|

| TSEC2_TX_ER                   | R10                                  | 0         | LV <sub>DD</sub> | 5, 9, 33       |  |  |

| Three-S                       | peed Ethernet Controller (Gigabit Et | hernet 3) |                  | -              |  |  |

| TSEC3_TXD[3:0]                | V8, W10, Y10, W7                     | 0         | TV <sub>DD</sub> | 5, 9, 29       |  |  |

| TSEC3_RXD[3:0]                | Y1, W3, W5, W4                       | I         | TV <sub>DD</sub> | —              |  |  |

| TSEC3_GTX_CLK                 | W8                                   | 0         | TV <sub>DD</sub> | _              |  |  |

| TSEC3_RX_CLK                  | W2                                   | I         | TV <sub>DD</sub> | —              |  |  |

| TSEC3_RX_DV                   | W1                                   | I         | TV <sub>DD</sub> | —              |  |  |

| TSEC3_RX_ER                   | Y2                                   | I         | TV <sub>DD</sub> | —              |  |  |

| TSEC3_TX_CLK                  | V10                                  | I         | TV <sub>DD</sub> | —              |  |  |

| TSEC3_TX_EN                   | V9                                   | 0         | TV <sub>DD</sub> | 30             |  |  |

| Three-S                       | peed Ethernet Controller (Gigabit Et | hernet 4) |                  | -              |  |  |

| TSEC4_TXD[3:0]/TSEC3_TXD[7:4] | AB8, Y7, AA7, Y8                     | 0         | TV <sub>DD</sub> | 1, 5, 9,<br>29 |  |  |

| TSEC4_RXD[3:0]/TSEC3_RXD[7:4] | AA1, Y3, AA2, AA4                    | I         | TV <sub>DD</sub> | 1              |  |  |

| TSEC4_GTX_CLK                 | AA5                                  | 0         | TV <sub>DD</sub> |                |  |  |

| TSEC4_RX_CLK/TSEC3_COL        | Y5                                   | I         | TV <sub>DD</sub> | 1              |  |  |

| TSEC4_RX_DV/TSEC3_CRS         | AA3                                  | I/O       | TV <sub>DD</sub> | 1, 31          |  |  |

| TSEC4_TX_EN/TSEC3_TX_ER       | AB6                                  | 0         | TV <sub>DD</sub> | 1, 30          |  |  |

|                               | DUART                                |           |                  |                |  |  |

| UART_CTS[0:1]                 | AB3, AC5                             | I         | OV <sub>DD</sub> | —              |  |  |

| UART_RTS[0:1]                 | AC6, AD7                             | 0         | OV <sub>DD</sub> | —              |  |  |

| UART_SIN[0:1]                 | AB5, AC7                             | I         | OV <sub>DD</sub> | —              |  |  |

| UART_SOUT[0:1]                | AB7, AD8                             | 0         | OV <sub>DD</sub> | —              |  |  |

|                               | I <sup>2</sup> C Interface           |           |                  | -              |  |  |

| IIC1_SCL                      | AG22                                 | I/O       | OV <sub>DD</sub> | 4, 27          |  |  |

| IIC1_SDA                      | AG21                                 | I/O       | OV <sub>DD</sub> | 4, 27          |  |  |

| IIC2_SCL                      | AG15                                 | I/O       | OV <sub>DD</sub> | 4, 27          |  |  |

| IIC2_SDA                      | AG14                                 | I/O       | OV <sub>DD</sub> | 4, 27          |  |  |

|                               | SerDes                               |           |                  | -              |  |  |

| SD_RX[0:3]                    | M28, N26, P28, R26                   | I         | XV <sub>DD</sub> | —              |  |  |

| SD_RX[0:3]                    | M27, N25, P27, R25                   | I         | XV <sub>DD</sub> |                |  |  |

| SD_TX[0:3]                    | M22, N20, P22, R20                   | 0         | XV <sub>DD</sub> | _              |  |  |

| SD_TX[0:3]                    | M23, N21, P23, R21                   | 0         | XV <sub>DD</sub> | _              |  |  |

| Reserved                      | W26, Y28, AA26, AB28                 | —         | —                | 40             |  |  |

| Reserved                      | W25, Y27, AA25, AB27                 | —         |                  | 40             |  |  |

## Table 72. MPC8547E Pinout Listing (continued)

Package Description

| Signal                | Package Pin Number                              | Pin Type | Power<br>Supply  | Notes |

|-----------------------|-------------------------------------------------|----------|------------------|-------|

| UDE                   | AH16                                            | I        | OV <sub>DD</sub> | _     |

| MCP                   | AG19                                            | I        | OV <sub>DD</sub> | _     |

| IRQ[0:7]              | AG23, AF18, AE18, AF20, AG18, AF17, AH24, AE20  | I        | OV <sub>DD</sub> | -     |

| IRQ[8]                | AF19                                            | I        | OV <sub>DD</sub> | —     |

| IRQ[9]/DMA_DREQ3      | AF21                                            | I        | OV <sub>DD</sub> | 1     |

| IRQ[10]/DMA_DACK3     | AE19                                            | I/O      | OV <sub>DD</sub> | 1     |

| IRQ[11]/DMA_DDONE3    | AD20                                            | I/O      | OV <sub>DD</sub> | 1     |

| IRQ_OUT               | AD18                                            | 0        | OV <sub>DD</sub> | 2, 4  |

|                       | Ethernet Management Interface                   |          | 1                |       |

| EC_MDC                | AB9                                             | 0        | OV <sub>DD</sub> | 5, 9  |

| EC_MDIO               | AC8                                             | I/O      | OV <sub>DD</sub> | _     |

|                       | Gigabit Reference Clock                         |          |                  |       |

| EC_GTX_CLK125         | V11                                             | I        | LV <sub>DD</sub> |       |

|                       | Three-Speed Ethernet Controller (Gigabit Ethern | et 1)    | 1                |       |

| TSEC1_RXD[7:0]        | R5, U1, R3, U2, V3, V1, T3, T2                  | I        | LV <sub>DD</sub> |       |

| TSEC1_TXD[7:0]        | T10, V7, U10, U5, U4, V6, T5, T8                | 0        | LV <sub>DD</sub> | 5, 9  |

| TSEC1_COL             | R4                                              | I        | LV <sub>DD</sub> |       |

| TSEC1_CRS             | V5                                              | I/O      | LV <sub>DD</sub> | 20    |

| TSEC1_GTX_CLK         | U7                                              | 0        | LV <sub>DD</sub> |       |

| TSEC1_RX_CLK          | U3                                              | I        | LV <sub>DD</sub> |       |

| TSEC1_RX_DV           | V2                                              | I        | LV <sub>DD</sub> | _     |

| TSEC1_RX_ER           | T1                                              | I        | LV <sub>DD</sub> | _     |

| TSEC1_TX_CLK          | Т6                                              | I        | LV <sub>DD</sub> |       |

| TSEC1_TX_EN           | U9                                              | 0        | LV <sub>DD</sub> | 30    |

| TSEC1_TX_ER           | Τ7                                              | 0        | LV <sub>DD</sub> | _     |

| GPIN[0:7]             | P2, R2, N1, N2, P3, M2, M1, N3                  | I        | LV <sub>DD</sub> | 103   |

| GPOUT[0:5]            | N9, N10, P8, N7, R9, N5                         | 0        | LV <sub>DD</sub> | _     |

| cfg_dram_type0/GPOUT6 | R8                                              | 0        | LV <sub>DD</sub> | 5, 9  |

| GPOUT7                | N6                                              | 0        | LV <sub>DD</sub> | —     |

| Reserved              | P1                                              | _        | _                | 104   |

| Reserved              | R6                                              |          | —                | 104   |

| Reserved              | P6                                              |          | _                | 15    |

| Reserved              | N4                                              | _        | _                | 105   |

Package Description

| Signal           | Package Pin Number                                                                                                                                                | Pin Type                                                            | Power<br>Supply  | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------|-------|

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15,<br>E2, E8, E11, E18, F5, F12, F16, G3, G7, G9,<br>G11, H5, H12, H15, H17, J10, K3, K12, K16,<br>K18, L6, M4, M8, M13 | Power for<br>DDR1 and<br>DDR2 DRAM<br>I/O voltage<br>(1.8 V, 2.5 V) | GV <sub>DD</sub> | _     |

| BV <sub>DD</sub> | C21, C24, C27, E20, E25, G19, G23, H26, J20                                                                                                                       | Power for local<br>bus (1.8 V,<br>2.5 V, 3.3 V)                     | BV <sub>DD</sub> | -     |

| V <sub>DD</sub>  | M19, N12, N14, N16, N18, P11, P13, P15, P17,<br>P19, R12, R14, R16, R18, T11, T13, T15, T17,<br>T19, U12, U14, U16, U18, V17, V19                                 | Power for core<br>(1.1 V)                                           | V <sub>DD</sub>  | -     |

| SV <sub>DD</sub> | L25, L27, M24, N28, P24, P26, R24, R27, T25,<br>V24, V26, W24, W27, Y25, AA28, AC27                                                                               | Core power for<br>SerDes<br>transceivers<br>(1.1 V)                 | SV <sub>DD</sub> | -     |

| XV <sub>DD</sub> | L20, L22, N23, P21, R22, T20, U23, V21, W22,<br>Y20                                                                                                               | Pad power for<br>SerDes<br>transceivers<br>(1.1 V)                  | XV <sub>DD</sub> | -     |

| AVDD_LBIU        | J28                                                                                                                                                               | Power for local<br>bus PLL<br>(1.1 V)                               | _                | 26    |

| AVDD_PCI1        | AH21                                                                                                                                                              | Power for<br>PCI1 PLL<br>(1.1 V)                                    | —                | 26    |

| AVDD_PCI2        | AH22                                                                                                                                                              | Power for<br>PCI2 PLL<br>(1.1 V)                                    | _                | 26    |

| AVDD_CORE        | AH15                                                                                                                                                              | Power for<br>e500 PLL (1.1<br>V)                                    | _                | 26    |

| AVDD_PLAT        | AH19                                                                                                                                                              | Powerfor CCB<br>PLL (1.1 V)                                         | —                | 26    |

| AVDD_SRDS        | U25                                                                                                                                                               | Power for<br>SRDSPLL (1.1<br>V)                                     | _                | 26    |

| SENSEVDD         | M14                                                                                                                                                               | 0                                                                   | V <sub>DD</sub>  | 13    |

| SENSEVSS         | M16                                                                                                                                                               | —                                                                   | —                | 13    |

|                  | Analog Signals                                                                                                                                                    |                                                                     |                  |       |

| MVREF            | A18                                                                                                                                                               | I<br>Reference<br>voltage signal<br>for DDR                         | MVREF            |       |

## Table 73. MPC8545E Pinout Listing (continued)

| Signal        | Package Pin Number | Pin Type | Power<br>Supply | Notes |

|---------------|--------------------|----------|-----------------|-------|

| SD_IMP_CAL_RX | L28                | I        | 200 Ω to<br>GND | —     |

| SD_IMP_CAL_TX | AB26               | I        | 100 Ω to<br>GND | —     |

| SD_PLL_TPA    | U26                | 0        | —               | 24    |

### Table 73. MPC8545E Pinout Listing (continued)

Note: All note references in this table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 74 provides the pin-out listing for the MPC8543E 783 FC-PBGA package.

## NOTE

All note references in the following table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 74. MPC8543E Pinout Listing

| Signal         | Package Pin Number                                                                                                                                                                            | Pin Type | Power<br>Supply  | Notes    |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|--|

|                | PCI1 (One 32-Bit)                                                                                                                                                                             |          |                  |          |  |

| Reserved       | AB14, AC15, AA15, Y16, W16, AB16, AC16,<br>AA16, AE17, AA18, W18, AC17, AD16, AE16,<br>Y17, AC18,                                                                                             |          | _                | 110      |  |

| GPOUT[8:15]    | AB18, AA19, AB19, AB21, AA20, AC20, AB20, AB22                                                                                                                                                | 0        | OV <sub>DD</sub> | —        |  |

| GPIN[8:15]     | AC22, AD21, AB23, AF23, AD23, AE23, AC23, AC24                                                                                                                                                | I        | OV <sub>DD</sub> | 111      |  |

| PCI1_AD[31:0]  | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15 | I/O      | OV <sub>DD</sub> | 17       |  |

| Reserved       | AF15, AD14, AE15, AD15                                                                                                                                                                        | _        | -                | 110      |  |

| PCI1_C_BE[3:0] | AF9, AD11, Y12, Y13                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 17       |  |

| Reserved       | W15                                                                                                                                                                                           |          |                  | 110      |  |

| PCI1_GNT[4:1]  | AG6, AE6, AF5, AH5                                                                                                                                                                            | 0        | OV <sub>DD</sub> | 5, 9, 35 |  |

| PCI1_GNT0      | AG5                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | —        |  |

| PCI1_IRDY      | AF11                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | 2        |  |

| PCI1_PAR       | AD12                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | —        |  |

| PCI1_PERR      | AC12                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | 2        |  |

| PCI1_SERR      | V13                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2, 4     |  |

| PCI1_STOP      | W12                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |  |

| Signal                 | Package Pin Number                       | Pin Type | Power<br>Supply  | Notes           |  |

|------------------------|------------------------------------------|----------|------------------|-----------------|--|

| IIC1_SDA               | AG21                                     | I/O      | OV <sub>DD</sub> | 4, 27           |  |

| IIC2_SCL               | AG15                                     | I/O      | OV <sub>DD</sub> | 4, 27           |  |

| IIC2_SDA               | AG14                                     | I/O      | OV <sub>DD</sub> | 4, 27           |  |

|                        | SerDes                                   | 1        |                  |                 |  |

| SD_RX[0:7]             | M28, N26, P28, R26, W26, Y28, AA26, AB28 | Ι        | XV <sub>DD</sub> | —               |  |

| SD_RX[0:7]             | M27, N25, P27, R25, W25, Y27, AA25, AB27 | Ι        | XV <sub>DD</sub> | _               |  |

| SD_TX[0:7]             | M22, N20, P22, R20, U20, V22, W20, Y22   | 0        | XV <sub>DD</sub> | —               |  |

| SD_TX[0:7]             | M23, N21, P23, R21, U21, V23, W21, Y23   | 0        | XV <sub>DD</sub> | _               |  |

| SD_PLL_TPD             | U28                                      | 0        | XV <sub>DD</sub> | 24              |  |

| SD_REF_CLK             | T28                                      | Ι        | XV <sub>DD</sub> | —               |  |

| SD_REF_CLK             | T27                                      | I        | XV <sub>DD</sub> | _               |  |

| Reserved               | AC1, AC3                                 | —        | _                | 2               |  |

| Reserved               | M26, V28                                 | _        | —                | 32              |  |

| Reserved               | M25, V27                                 | _        | _                | 34              |  |

| Reserved               | M20, M21, T22, T23                       | —        | _                | 38              |  |

|                        | General-Purpose Output                   |          |                  | •               |  |

| GPOUT[24:31]           | K26, K25, H27, G28, H25, J26, K24, K23   | 0        | BV <sub>DD</sub> | —               |  |

|                        | System Control                           |          |                  |                 |  |

| HRESET                 | AG17                                     | Ι        | OV <sub>DD</sub> | —               |  |

| HRESET_REQ             | AG16                                     | 0        | $OV_DD$          | 29              |  |

| SRESET                 | AG20                                     | I        | OV <sub>DD</sub> | —               |  |

| CKSTP_IN               | AA9                                      | Ι        | $OV_{DD}$        | —               |  |

| CKSTP_OUT              | AA8                                      | 0        | $OV_{DD}$        | 2, 4            |  |

|                        | Debug                                    |          |                  |                 |  |

| TRIG_IN                | AB2                                      | Ι        | OV <sub>DD</sub> | —               |  |

| TRIG_OUT/READY/QUIESCE | AB1                                      | 0        | OV <sub>DD</sub> | 6, 9, 19,<br>29 |  |

| MSRCID[0:1]            | AE4, AG2                                 | 0        | OV <sub>DD</sub> | 5, 6, 9         |  |

| MSRCID[2:4]            | AF3, AF1, AF2                            | 0        | $OV_{DD}$        | 6, 19, 29       |  |

| MDVAL                  | AE5                                      | 0        | $OV_{DD}$        | 6               |  |

| CLK_OUT                | AE21                                     | 0        | $OV_{DD}$        | 11              |  |

|                        | Clock                                    |          |                  |                 |  |

| RTC                    | AF16                                     | Ι        | $OV_{DD}$        | —               |  |

| SYSCLK                 | AH17                                     | I        | OV <sub>DD</sub> |                 |  |

# 20 Clocking

This section describes the PLL configuration of the device. Note that the platform clock is identical to the core complex bus (CCB) clock.

## 20.1 Clock Ranges

Table 75 through Table 77 provide the clocking specifications for the processor cores and Table 78, through Table 80 provide the clocking specifications for the memory bus.

|                               | Maximum Processor Core Frequency |      |          |      |          |      |      |       |

|-------------------------------|----------------------------------|------|----------|------|----------|------|------|-------|

| Characteristic                | 1000 MHz                         |      | 1200 MHz |      | 1333 MHz |      | Unit | Notes |

|                               | Min                              | Max  | Min      | Мах  | Min      | Max  |      |       |

| e500 core processor frequency | 800                              | 1000 | 800      | 1200 | 800      | 1333 | MHz  | 1, 2  |

Table 75. Processor Core Clocking Specifications (MPC8548E and MPC8547E)

Notes:

Caution: The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

2.)The minimum e500 core frequency is based on the minimum platform frequency of 333 MHz.

## Table 76. Processor Core Clocking Specifications (MPC8545E)

|                               | Maximum Processor Core Frequency |     |          |      |          |      |      |       |

|-------------------------------|----------------------------------|-----|----------|------|----------|------|------|-------|

| Characteristic                | 800 MHz                          |     | 1000 MHz |      | 1200 MHz |      | Unit | Notes |

|                               | Min                              | Max | Min      | Max  | Min      | Max  |      |       |

| e500 core processor frequency | 800                              | 800 | 800      | 1000 | 800      | 1200 | MHz  | 1, 2  |

Notes:

1. **Caution:** The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

2.)The minimum e500 core frequency is based on the minimum platform frequency of 333 MHz.

#### System Design Information

#### Notes:

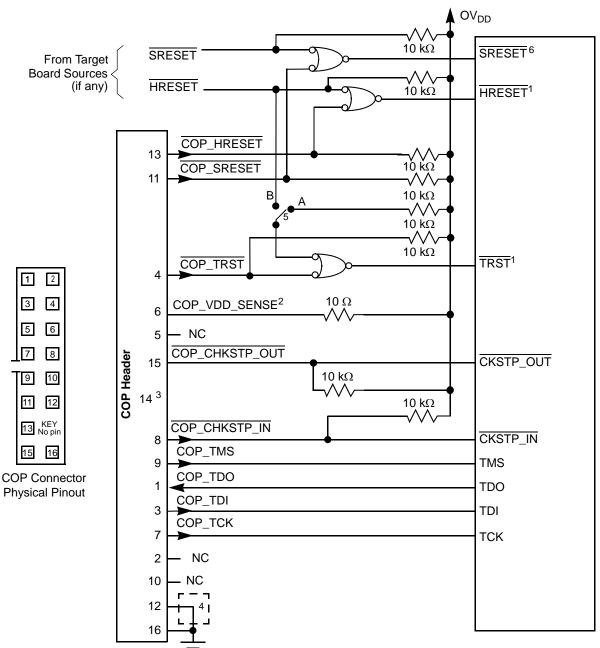

- 1. The COP port and target board must be able to independently assert HRESET and TRST to the processor in order to fully control the processor as shown here.

- 2. Populate this with a 10– $\Omega$  resistor for short-circuit/current-limiting protection.

- 3. The KEY location (pin 14) is not physically present on the COP header.

- 4. Although pin 12 is defined as a No-Connect, some debug tools may use pin 12 as an additional GND pin for improved signal integrity.

- This switch is included as a precaution for BSDL testing. The switch must be closed to position A during BSDL testing to avoid accidentally asserting the TRST line. If BSDL testing is not being performed, this switch must be closed to position B.

- 6. Asserting SRESET causes a machine check interrupt to the e500 core.

### Figure 63. JTAG Interface Connection

#### **Ordering Information**

| MPC             | nnnnn              | t                                       | рр                                                               | ff                                  | С                 | r                                                                                                                  |

|-----------------|--------------------|-----------------------------------------|------------------------------------------------------------------|-------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------|

| Product<br>Code | Part<br>Identifier | Temperature                             | Package <sup>1, 2, 3</sup>                                       | Processor<br>Frequency <sup>4</sup> | Core<br>Frequency | Silicon Version                                                                                                    |

| MPC             | 8545E              | Blank = 0 to 105°C<br>C = −40° to 105°C | HX = CBGA<br>VU = Pb-free CBGA<br>PX = PBGA<br>VT = Pb-free PBGA | AT = 1200<br>AQ = 1000<br>AN = 800  | G = 400           | Blank = Ver. 2.0<br>(SVR = 0x80390220)<br>A = Ver. 2.1.1<br>B = Ver. 2.1.2<br>D = Ver. 3.1.x<br>(SVR = 0x80390231) |

|                 | 8545               |                                         |                                                                  |                                     |                   | Blank = Ver. 2.0<br>(SVR = 0x80310220)<br>A = Ver. 2.1.1<br>B = Ver. 2.1.2<br>D = Ver. 3.1.x<br>(SVR = 0x80310231) |

|                 | 8543E              |                                         |                                                                  | AQ = 1000<br>AN = 800               |                   | Blank = Ver. 2.0<br>(SVR = 0x803A0020)<br>A = Ver. 2.1.1<br>B = Ver. 2.1.2<br>D = Ver. 3.1.x<br>(SVR = 0x803A0031) |

|                 | 8543               |                                         |                                                                  |                                     |                   | Blank = Ver. 2.0<br>(SVR = 0x80320020)<br>A = Ver. 2.1.1<br>B = Ver. 2.1.2<br>D = Ver. 3.1.x<br>(SVR = 0x80320031) |

### Table 87. Part Numbering Nomenclature (continued)

### Notes:

1. See Section 19, "Package Description," for more information on available package types.

2. The HiCTE FC-CBGA package is available on only Version 2.0 of the device.

3. The FC-PBGA package is available on only Version 2.1.1, 2.1.2, and 2.1.3 of the device.

- Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by part number specifications may support other maximum core frequencies.

- 5. This speed available only for silicon Version 2.1.1, 2.1.2, and 2.1.3.

#### How to Reach Us:

Home Page: www.freescale.com

#### Web Support: http://www.freescale.com/support

USA/Europe or Locations Not Listed: Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road

2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life. or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale, the Freescale logo, CodeWarrior, ColdFire, PowerQUICC, QorIQ, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc. Reg., U.S. Pat. & Tm. Off. CoreNet, QorIQ Qonverge, QUICC Engine, and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2012 Freescale Semiconductor, Inc.

Document Number: MPC8548EEC Rev. 9 02/2012