# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 1.2GHz                                                                |

| Co-Processors/DSP               | Signal Processing; SPE                                                |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                      |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | ·                                                                     |

| Ethernet                        | 10/100/1000Mbps (4)                                                   |

| SATA                            | ·                                                                     |

| USB                             | · .                                                                   |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                      |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                     |

| Package / Case                  | 783-BBGA, FCBGA                                                       |

| Supplier Device Package         | 783-FCBGA (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8545hxatg |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.3 eTSEC Gigabit Reference Clock Timing

The following table provides the eTSEC gigabit reference clocks (EC\_GTX\_CLK125) AC timing specifications for the device.

| Parameter/Condition                                                  | Symbol            | Min      | Тур | Max         | Unit | Notes |

|----------------------------------------------------------------------|-------------------|----------|-----|-------------|------|-------|

| EC_GTX_CLK125 frequency                                              | f <sub>G125</sub> | _        | 125 | —           | MHz  | _     |

| EC_GTX_CLK125 cycle time                                             | t <sub>G125</sub> | —        | 8   | —           | ns   |       |

| EC_GTX_CLK125 rise and fall time<br>L/TVDD = 2.5 V<br>L/TVDD = 3.3 V |                   | —        | _   | 0.75<br>1.0 | ns   | 1     |

| EC_GTX_CLK125 duty cycle<br>GMII, TBI<br>1000Base-T for RGMII, RTBI  |                   | 45<br>47 | _   | 55<br>53    | %    | 2, 3  |

| Table 6. EC_ | GTX_CLK125 AC Tim | ning Specifications |

|--------------|-------------------|---------------------|

|--------------|-------------------|---------------------|

Notes:

1. Rise and fall times for EC\_GTX\_CLK125 are measured from 0.5 and 2.0 V for L/TV<sub>DD</sub> = 2.5 V, and from 0.6 and 2.7 V for L/TV<sub>DD</sub> = 3.3 V.

- 2. Timing is guaranteed by design and characterization.

- 3. EC\_GTX\_CLK125 is used to generate the GTX clock TSEC*n*\_GTX\_CLK for the eTSEC transmitter with 2% degradation. EC\_GTX\_CLK125 duty cycle can be loosened from 47/53% as long as the PHY device can tolerate the duty cycle generated by the TSEC*n*\_GTX\_CLK. See Section 8.2.6, "RGMII and RTBI AC Timing Specifications," for duty cycle for 10Base-T and 100Base-T reference clock.

## 4.4 PCI/PCI-X Reference Clock Timing

When the PCI/PCI-X controller is configured for asynchronous operation, the reference clock for the PCI/PCI-x controller is not the SYSCLK input, but instead the PCIn\_CLK. The following table provides the PCI/PCI-X reference clock AC timing specifications for the device.

| Table 7. PCIn_CLK AC Timing Specifications | Table 7. PCI <i>n</i> | CLK | AC Timing | Specifications |

|--------------------------------------------|-----------------------|-----|-----------|----------------|

|--------------------------------------------|-----------------------|-----|-----------|----------------|

At recommended operating conditions (see Table 2) with  $OV_{DD} = 3.3 \text{ V} \pm 165 \text{ mV}$ .

| Parameter/Condition         | Symbol                                    | Min | Тур | Мах | Unit | Notes |

|-----------------------------|-------------------------------------------|-----|-----|-----|------|-------|

| PCIn_CLK frequency          | f <sub>PCICLK</sub>                       | 16  | —   | 133 | MHz  | —     |

| PCIn_CLK cycle time         | t <sub>PCICLK</sub>                       | 7.5 | —   | 60  | ns   | —     |

| PCIn_CLK rise and fall time | t <sub>PCIKH</sub> , t <sub>PCIKL</sub>   | 0.6 | 1.0 | 2.1 | ns   | 1, 2  |

| PCIn_CLK duty cycle         | t <sub>PCIKHKL</sub> /t <sub>PCICLK</sub> | 40  | —   | 60  | %    | 2     |

Notes:

1. Rise and fall times for SYSCLK are measured at 0.6 and 2.7 V.

2. Timing is guaranteed by design and characterization.

### 6.2.2 DDR SDRAM Output AC Timing Specifications

### Table 19. DDR SDRAM Output AC Timing Specifications

At recommended operating conditions.

| Parameter                                                                          | Symbol <sup>1</sup>                         | Min                             | Max                         | Unit | Notes |

|------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------|-----------------------------|------|-------|

| MCK[n] cycle time, MCK[n]/MCK[n] crossing                                          | t <sub>MCK</sub>                            | 3.75                            | 6                           | ns   | 2     |

| ADDR/CMD output setup with respect to MCK<br>533 MHz<br>400 MHz<br>333 MHz         | t <sub>DDKHAS</sub>                         | 1.48<br>1.95<br>2.40            |                             | ns   | 3     |

| ADDR/CMD output hold with respect to MCK<br>533 MHz<br>400 MHz<br>333 MHz          | t <sub>DDKHAX</sub>                         | 1.48<br>1.95<br>2.40            |                             | ns   | 3     |

| MCS[ <i>n</i> ] output setup with respect to MCK<br>533 MHz<br>400 MHz<br>333 MHz  | t <sub>DDKHCS</sub>                         | 1.48<br>1.95<br>2.40            |                             | ns   | 3     |

| MCS[ <i>n</i> ] output hold with respect to MCK<br>533 MHz<br>400 MHz<br>333 MHz   | t <sub>DDKHCX</sub>                         | 1.48<br>1.95<br>2.40            |                             | ns   | 3     |

| MCK to MDQS Skew                                                                   | t <sub>DDKHMH</sub>                         | -0.6                            | 0.6                         | ns   | 4     |

| MDQ/MECC/MDM output setup with respect<br>to MDQS<br>533 MHz<br>400 MHz<br>333 MHz | <sup>t</sup> DDKHDS,<br><sup>t</sup> DDKLDS | 538<br>700<br>900               |                             | ps   | 5     |

| MDQ/MECC/MDM output hold with respect to<br>MDQS<br>533 MHz<br>400 MHz<br>333 MHz  | <sup>t</sup> DDKHDX,<br><sup>t</sup> DDKLDX | 538<br>700<br>900               |                             | ps   | 5     |

| MDQS preamble start                                                                | t <sub>DDKHMP</sub>                         | $-0.5\times t_{\text{MCK}}-0.6$ | $-0.5 \times t_{MCK}$ + 0.6 | ns   | 6     |

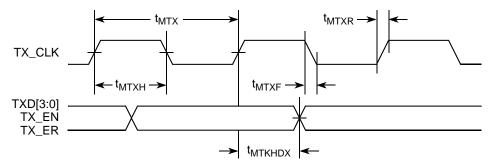

Figure 11 shows the MII transmit AC timing diagram.

Figure 11. MII Transmit AC Timing Diagram

### 8.2.3.2 MII Receive AC Timing Specifications

This table provides the MII receive AC timing specifications.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min  | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                 | t <sub>MRX</sub> 2                  | _    | 400 | _   | ns   |

| RX_CLK clock period 100 Mbps                | t <sub>MRX</sub>                    |      | 40  |     | ns   |

| RX_CLK duty cycle                           | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | _   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub>                 | 10.0 | _   | _   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub>                 | 10.0 | _   | _   | ns   |

| RX_CLK clock rise (20%–80%)                 | t <sub>MRXR</sub> <sup>2</sup>      | 1.0  | _   | 4.0 | ns   |

| RX_CLK clock fall time (80%–20%)            | t <sub>MRXF</sub> <sup>2</sup>      | 1.0  | _   | 4.0 | ns   |

Notes:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

2. Guaranteed by design.

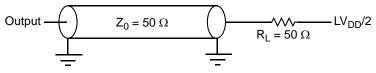

Figure 12 provides the AC test load for eTSEC.

Figure 12. eTSEC AC Test Load

#### Enhanced Three-Speed Ethernet (eTSEC)

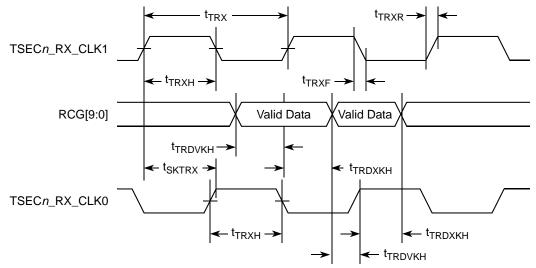

Figure 15 shows the TBI receive AC timing diagram.

Figure 15. TBI Receive AC Timing Diagram

### 8.2.5 TBI Single-Clock Mode AC Specifications

When the eTSEC is configured for TBI modes, all clocks are supplied from external sources to the relevant eTSEC interface. In single-clock TBI mode, when TBICON[CLKSEL] = 1, a 125-MHz TBI receive clock is supplied on the TSEC $n_RX_CLK$  pin (no receive clock is used on TSEC $n_TX_CLK$  in this mode, whereas for the dual-clock mode this is the PMA1 receive clock). The 125-MHz transmit clock is applied on the TSEC\_GTX\_CLK125 pin in all TBI modes.

A summary of the single-clock TBI mode AC specifications for receive appears in Table 32.

| Parameter/Condition                       | Symbol                 | Min | Тур | Max | Unit |

|-------------------------------------------|------------------------|-----|-----|-----|------|

| RX_CLK clock period                       | t <sub>TRRX</sub>      | 7.5 | 8.0 | 8.5 | ns   |

| RX_CLK duty cycle                         | t <sub>TRRH/TRRX</sub> | 40  | 50  | 60  | %    |

| RX_CLK peak-to-peak jitter                | t <sub>TRRJ</sub>      | —   | _   | 250 | ps   |

| Rise time RX_CLK (20%-80%)                | t <sub>TRRR</sub>      | —   | _   | 1.0 | ns   |

| Fall time RX_CLK (80%–20%)                | t <sub>TRRF</sub>      | —   | _   | 1.0 | ns   |

| RCG[9:0] setup time to RX_CLK rising edge | t <sub>trrdvkh</sub>   | 2.0 | _   | —   | ns   |

| RCG[9:0] hold time to RX_CLK rising edge  | t <sub>trrdxkh</sub>   | 1.0 | _   | —   | ns   |

# 9 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals MDIO (management data input/output) and MDC (management data clock). The electrical characteristics for GMII, RGMII, RMII, TBI, and RTBI are specified in "Section 8, "Enhanced Three-Speed Ethernet (eTSEC)."

### 9.1 MII Management DC Electrical Characteristics

The MDC and MDIO are defined to operate at a supply voltage of 3.3 V. The DC electrical characteristics for MDIO and MDC are provided in this table.

| Parameter                                                            | Symbol           | Min  | Мах                    | Unit |

|----------------------------------------------------------------------|------------------|------|------------------------|------|

| Supply voltage (3.3 V)                                               | OV <sub>DD</sub> | 3.13 | 3.47                   | V    |

| Output high voltage ( $OV_{DD} = Min, I_{OH} = -1.0 mA$ )            | V <sub>OH</sub>  | 2.10 | OV <sub>DD</sub> + 0.3 | V    |

| Output low voltage (OV <sub>DD</sub> =Min, I <sub>OL</sub> = 1.0 mA) | V <sub>OL</sub>  | GND  | 0.50                   | V    |

| Input high voltage                                                   | V <sub>IH</sub>  | 2.0  | —                      | V    |

| Input low voltage                                                    | V <sub>IL</sub>  | _    | 0.90                   | V    |

| Input high current ( $OV_{DD} = Max, V_{IN}^1 = 2.1 V$ )             | I <sub>IH</sub>  | _    | 40                     | μA   |

| Input low current ( $OV_{DD} = Max$ , $V_{IN} = 0.5 V$ )             | IIL              | -600 | —                      | μΑ   |

Table 36. MII Management DC Electrical Characteristics

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

### 9.2 MII Management AC Electrical Specifications

This table provides the MII management AC timing specifications.

### Table 37. MII Management AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  is 3.3 V ± 5%.

| Parameter                  | Symbol <sup>1</sup> | Min                             | Тур | Мах                                | Unit | Notes   |

|----------------------------|---------------------|---------------------------------|-----|------------------------------------|------|---------|

| MDC frequency              | f <sub>MDC</sub>    | 0.72                            | 2.5 | 8.3                                | MHz  | 2, 3, 4 |

| MDC period                 | t <sub>MDC</sub>    | 120.5                           | _   | 1389                               | ns   | —       |

| MDC clock pulse width high | t <sub>MDCH</sub>   | 32                              | _   | —                                  | ns   | _       |

| MDC to MDIO valid          | t <sub>MDKHDV</sub> | $16 \times t_{CCB}$             | _   | —                                  | ns   | 5       |

| MDC to MDIO delay          | t <sub>MDKHDX</sub> | (16 × t <sub>CCB</sub> × 8) – 3 | _   | $(16 \times t_{CCB} \times 8) + 3$ | ns   | 5       |

| MDIO to MDC setup time     | t <sub>MDD∨KH</sub> | 5                               | _   | —                                  | ns   | _       |

| MDIO to MDC hold time      | t <sub>MDDXKH</sub> | 0                               | _   | —                                  | ns   | —       |

| MDC rise time              | t <sub>MDCR</sub>   | _                               |     | 10                                 | ns   | 4       |

## **10.2 Local Bus AC Electrical Specifications**

This table describes the timing parameters of the local bus interface at  $BV_{DD} = 3.3$  V. For information about the frequency range of local bus, see Section 20.1, "Clock Ranges."

| Parameter                                                             | Symbol <sup>1</sup>                 | Min | Max | Unit | Notes |

|-----------------------------------------------------------------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                  | t <sub>LBK</sub>                    | 7.5 | 12  | ns   | 2     |

| Local bus duty cycle                                                  | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43  | 57  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                  | t <sub>LBKSKEW</sub>                | _   | 150 | ps   | 7, 8  |

| Input setup to local bus clock (except LGTA/LUPWAIT)                  | t <sub>LBIVKH1</sub>                | 1.8 |     | ns   | 3, 4  |

| LGTA/LUPWAIT input setup to local bus clock                           | t <sub>LBIVKH2</sub>                | 1.7 | _   | ns   | 3, 4  |

| Input hold from local bus clock (except LGTA/LUPWAIT)                 | t <sub>LBIXKH1</sub>                | 1.0 | _   | ns   | 3, 4  |

| LGTA/LUPWAIT input hold from local bus clock                          | t <sub>LBIXKH2</sub>                | 1.0 |     | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | t <sub>LBOTOT</sub>                 | 1.5 | _   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)             | t <sub>LBKHOV1</sub>                | _   | 2.0 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                             | t <sub>LBKHOV2</sub>                | _   | 2.2 | ns   | 3     |

| Local bus clock to address valid for LAD                              | t <sub>LBKHOV3</sub>                | _   | 2.3 | ns   | 3     |

| Local bus clock to LALE assertion                                     | t <sub>LBKHOV4</sub>                | _   | 2.3 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)            | t <sub>LBKHOX1</sub>                | 0.7 | _   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                          | t <sub>LBKHOX2</sub>                | 0.7 | _   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)    | t <sub>LBKHOZ1</sub>                |     | 2.5 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP                  | t <sub>LBKHOZ2</sub>                | _   | 2.5 | ns   | 5     |

### Table 40. Local Bus Timing Parameters (BV<sub>DD</sub> = 3.3 V)—PLL Enabled

### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKH0X</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

- 2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 8. Guaranteed by design.

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min      | Мах      | Unit | Notes |

|----------------------------------------------------------------------------|--------------------------------------------|----------|----------|------|-------|

| Valid times:<br>Boundary-scan data<br>TDO                                  | t <sub>jtkldv</sub><br>t <sub>jtklov</sub> | 4<br>2   | 20<br>10 | ns   | 5     |

| Output hold times:<br>Boundary-scan data<br>TDO                            | t <sub>jtkldx</sub><br>t <sub>jtklox</sub> | 30<br>30 |          | ns   | 5     |

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>jtkldz</sub><br>t <sub>jtkloz</sub> | 3<br>3   | 19<br>9  | ns   | 5, 6  |

Table 44. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup> (continued)

#### Notes:

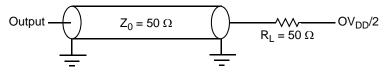

- All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 29). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- 5. Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

- 6. Guaranteed by design.

Figure 29 provides the AC test load for TDO and the boundary-scan outputs.

Figure 29. AC Test Load for the JTAG Interface

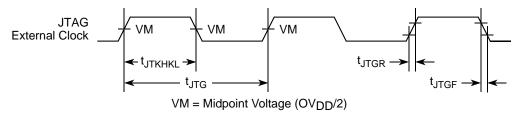

Figure 30 provides the JTAG clock input timing diagram.

Figure 30. JTAG Clock Input Timing Diagram

### l<sup>2</sup>C

# 13 I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the I<sup>2</sup>C interfaces of the device.

# **13.1** I<sup>2</sup>C DC Electrical Characteristics

This table provides the DC electrical characteristics for the  $I^2C$  interfaces.

### Table 45. I<sup>2</sup>C DC Electrical Characteristics

| Parameter                                                                                                | Symbol              | Min                  | Мах                                | Unit | Notes |

|----------------------------------------------------------------------------------------------------------|---------------------|----------------------|------------------------------------|------|-------|

| Input high voltage level                                                                                 | V <sub>IH</sub>     | $0.7 \times OV_{DD}$ | OV <sub>DD</sub> + 0.3             | V    | _     |

| Input low voltage level                                                                                  | V <sub>IL</sub>     | -0.3                 | $0.3 	imes OV_{DD}$                | V    | —     |

| Low level output voltage                                                                                 | V <sub>OL</sub>     | 0                    | $0.2 \times \text{OV}_{\text{DD}}$ | V    | 1     |

| Pulse width of spikes which must be suppressed by the input filter                                       | t <sub>I2KHKL</sub> | 0                    | 50                                 | ns   | 2     |

| Input current each I/O pin (input voltage is between $0.1 \times OV_{DD}$ and $0.9 \times OV_{DD}$ (max) | I                   | -10                  | 10                                 | μΑ   | 3     |

| Capacitance for each I/O pin                                                                             | Cl                  | —                    | 10                                 | pF   | —     |

### Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

- 2. See the MPC8548E PowerQUICC<sup>™</sup> III Integrated Processor Family Reference Manual, for information on the digital filter used.

- 3. I/O pins obstruct the SDA and SCL lines if  $\ensuremath{\mathsf{OV}_{\mathsf{DD}}}$  is switched off.

# **13.2** I<sup>2</sup>C AC Electrical Specifications

This table provides the AC timing parameters for the  $I^2C$  interfaces.

Table 46. I<sup>2</sup>C AC Electrical Specifications

| Parameter                                                                                    | Symbol <sup>1</sup> | Min | Max | Unit | Notes |

|----------------------------------------------------------------------------------------------|---------------------|-----|-----|------|-------|

| SCL clock frequency                                                                          | f <sub>I2C</sub>    | 0   | 400 | kHz  | —     |

| Low period of the SCL clock                                                                  | t <sub>I2CL</sub>   | 1.3 | —   | μS   | 4     |

| High period of the SCL clock                                                                 | t <sub>I2CH</sub>   | 0.6 | —   | μS   | 4     |

| Setup time for a repeated START condition                                                    | t <sub>I2SVKH</sub> | 0.6 | —   | μS   | 4     |

| Hold time (repeated) START condition (after this period, the first clock pulse is generated) | t <sub>I2SXKL</sub> | 0.6 | —   | μS   | 4     |

| Data setup time                                                                              | t <sub>I2DVKH</sub> | 100 | —   | ns   | 4     |

| Data input hold time:<br>CBUS compatible masters<br>I <sup>2</sup> C bus devices             | t <sub>I2DXKL</sub> | 0   |     | μs   | 2     |

| Data output delay time:                                                                      | t <sub>I2OVKL</sub> | —   | 0.9 | —    | 3     |

| Set-up time for STOP condition                                                               | t <sub>I2PVKH</sub> | 0.6 | —   | μS   | —     |

| Bus free time between a STOP and START condition                                             | t <sub>I2KHDX</sub> | 1.3 |     | μS   |       |

| 3. The maximum t <sub>I2DXKL</sub> | has only to be met if the device does not stretch the LC | DW period (t <sub>I2CL</sub> ) of the SCL signal. |

|------------------------------------|----------------------------------------------------------|---------------------------------------------------|

|                                    |                                                          |                                                   |

For the detail of I<sup>2</sup>C frequency calculation, see Determining the I<sup>2</sup>C Frequency Divider Ratio for SCL (AN2919). Note that the

200 MHz

390 kHz

0x26

512

133 MHz

346 kHz

0x00

384

#### 4. Guaranteed by design.

FDR bit setting

I<sup>2</sup>C source clock frequency

Actual FDR divider selected

Actual I<sup>2</sup>C SCL frequency generated

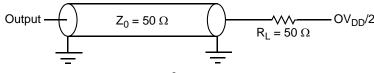

Figure 33 provides the AC test load for the  $I^2C$ .

Figure 33. I<sup>2</sup>C AC Test Load

#### 57

### Table 46. I<sup>2</sup>C AC Electrical Specifications (continued)

| Parameter                                                                       | Symbol <sup>1</sup> | Min                                | Мах | Unit | Notes |

|---------------------------------------------------------------------------------|---------------------|------------------------------------|-----|------|-------|

| Noise margin at the LOW level for each connected device (including hysteresis)  | V <sub>NL</sub>     | $0.1 \times OV_{DD}$               |     | V    | —     |

| Noise margin at the HIGH level for each connected device (including hysteresis) | V <sub>NH</sub>     | $0.2 \times \text{OV}_{\text{DD}}$ | —   | V    | —     |

#### Notes:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>12DVKH</sub> symbolizes I<sup>2</sup>C timing (I2) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>12C</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>12SXKL</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the start condition (S) went invalid (X) relative to the t<sub>12C</sub> clock reference (K) going to the stop condition (P) reaching the valid state (V) relative to the t<sub>12C</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

2. As a transmitter, the device provides a delay time of at least 300 ns for the SDA signal (see the V<sub>IH</sub>(min) of the SCL signal) to bridge the undefined region of the falling edge of SCL to avoid unintended generation of Start or Stop condition. When the device acts as the I<sup>2</sup>C bus master while transmitting, the device drives both SCL and SDA. As long as the load on SCL and SDA are balanced, the device would not cause unintended generation of Start or Stop condition. Therefore, the 300 ns SDA output delay time is not a concern. If, under some rare condition, the 300 ns SDA output delay time is required for the device as a transmitter, the following setting is recommended for the FDR bit field of the I2CFDR register to ensure both the desired I<sup>2</sup>C SCL clock frequency and SDA output delay time are achieved, assuming that the desired I<sup>2</sup>C SCL clock frequency is 400 kHz and the Digital Filter Sampling Rate Register (I2CDFSRR) is programmed with its default setting of 0x10 (decimal 16):

266 MHz

378 kHz

0x05

704

333 MHz

0x2A

371 kHz

896

I<sup>2</sup>C source clock frequency is half of the CCB clock frequency for the device.

### PCI/PCI-X

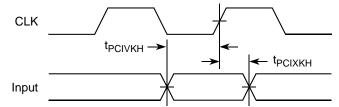

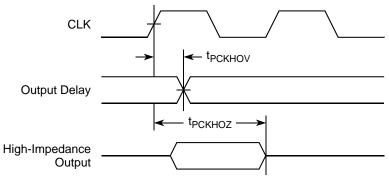

Figure 36 shows the PCI/PCI-X input AC timing conditions.

Figure 36. PCI/PCI-X Input AC Timing Measurement Conditions

Figure 37 shows the PCI/PCI-X output AC timing conditions.

Table 53 provides the PCI-X AC timing specifications at 66 MHz.

| Table 53. PCI-X AC Timing | <b>Specifications at 66 MHz</b> |

|---------------------------|---------------------------------|

|---------------------------|---------------------------------|

| Parameter                                         | Symbol              | Min | Max | Unit   | Notes         |

|---------------------------------------------------|---------------------|-----|-----|--------|---------------|

| SYSCLK to signal valid delay                      | <sup>t</sup> PCKHOV | —   | 3.8 | ns     | 1, 2, 3, 7, 8 |

| Output hold from SYSCLK                           | t <sub>РСКНОХ</sub> | 0.7 | —   | ns     | 1, 10         |

| SYSCLK to output high impedance                   | t <sub>PCKHOZ</sub> | —   | 7   | ns     | 1, 4, 8, 11   |

| Input setup time to SYSCLK                        | t <sub>PCIVKH</sub> | 1.7 | —   | ns     | 3, 5          |

| Input hold time from SYSCLK                       | t <sub>PCIXKH</sub> | 0.5 | —   | ns     | 10            |

| REQ64 to HRESET setup time                        | t <sub>PCRVRH</sub> | 10  | —   | clocks | 11            |

| HRESET to REQ64 hold time                         | t <sub>PCRHRX</sub> | 0   | 50  | ns     | 11            |

| HRESET high to first FRAME assertion              | t <sub>PCRHFV</sub> | 10  | —   | clocks | 9, 11         |

| PCI-X initialization pattern to HRESET setup time | <sup>t</sup> PCIVRH | 10  | —   | clocks | 11            |

| Signal           | Package Pin Number                                                                                                                                                | Pin Type                                                          | Power<br>Supply  | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------|-------|

| LV <sub>DD</sub> | N8, R7, T9, U6                                                                                                                                                    | Power for<br>TSEC1 and<br>TSEC2<br>(2.5 V, 3.3 V)                 | LV <sub>DD</sub> | _     |

| TV <sub>DD</sub> | W9, Y6                                                                                                                                                            | Power for<br>TSEC3 and<br>TSEC4<br>(2,5 V, 3.3 V)                 | TV <sub>DD</sub> | _     |

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15,<br>E2, E8, E11, E18, F5, F12, F16, G3, G7, G9,<br>G11, H5, H12, H15, H17, J10, K3, K12, K16,<br>K18, L6, M4, M8, M13 | Power for<br>DDR1 and<br>DDR2 DRAM<br>I/O voltage<br>(1.8 V, 2.5) | GV <sub>DD</sub> |       |

| BV <sub>DD</sub> | C21, C24, C27, E20, E25, G19, G23, H26, J20                                                                                                                       | Power for local<br>bus (1.8 V,<br>2.5 V, 3.3 V)                   | BV <sub>DD</sub> |       |

| V <sub>DD</sub>  | M19, N12, N14, N16, N18, P11, P13, P15, P17,<br>P19, R12, R14, R16, R18, T11, T13, T15, T17,<br>T19, U12, U14, U16, U18, V17, V19                                 | Power for core<br>(1.1 V)                                         | V <sub>DD</sub>  |       |

| SV <sub>DD</sub> | L25, L27, M24, N28, P24, P26, R24, R27, T25,<br>V24, V26, W24, W27, Y25, AA28, AC27                                                                               | Core Power<br>for SerDes<br>transceivers<br>(1.1 V)               | SV <sub>DD</sub> | —     |

| XV <sub>DD</sub> | L20, L22, N23, P21, R22, T20, U23, V21, W22,<br>Y20                                                                                                               | Pad Power for<br>SerDes<br>transceivers<br>(1.1 V)                | XV <sub>DD</sub> |       |

| AVDD_LBIU        | J28                                                                                                                                                               | Power for local<br>bus PLL<br>(1.1 V)                             | _                | 26    |

| AVDD_PCI1        | AH21                                                                                                                                                              | Power for<br>PCI1 PLL<br>(1.1 V)                                  | _                | 26    |

| AVDD_PCI2        | AH22                                                                                                                                                              | Power for<br>PCI2 PLL<br>(1.1 V)                                  | _                | 26    |

| AVDD_CORE        | AH15                                                                                                                                                              | Power for<br>e500 PLL (1.1<br>V)                                  | _                | 26    |

| AVDD_PLAT        | AH19                                                                                                                                                              | Powerfor CCB<br>PLL (1.1 V)                                       | —                | 26    |

| AVDD_SRDS        | U25                                                                                                                                                               | Power for<br>SRDSPLL<br>(1.1 V)                                   | _                | 26    |

| SENSEVDD         | M14                                                                                                                                                               | 0                                                                 | V <sub>DD</sub>  | 13    |

### Table 71. MPC8548E Pinout Listing (continued)

| Signal                   | Package Pin Number                                                                                                                                                      | Pin Type | Power<br>Supply  | Notes        |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|--------------|

|                          | Local Bus Controller Interface                                                                                                                                          |          |                  |              |

| LAD[0:31]                | E27, B20, H19, F25, A20, C19, E28, J23, A25,<br>K22, B28, D27, D19, J22, K20, D28, D25, B25,<br>E22, F22, F21, C25, C22, B23, F20, A23, A22,<br>E19, A21, D21, F19, B21 | I/O      | BV <sub>DD</sub> | _            |

| LDP[0:3]                 | K21, C28, B26, B22                                                                                                                                                      | I/O      | BV <sub>DD</sub> | —            |

| LA[27]                   | H21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LA[28:31]                | H20, A27, D26, A28                                                                                                                                                      | 0        | BV <sub>DD</sub> | 5, 7, 9      |

| LCS[0:4]                 | J25, C20, J24, G26, A26                                                                                                                                                 | 0        | BV <sub>DD</sub> | —            |

| LCS5/DMA_DREQ2           | D23                                                                                                                                                                     | I/O      | BV <sub>DD</sub> | 1            |

| LCS6/DMA_DACK2           | G20                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 1            |

| LCS7/DMA_DDONE2          | E21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 1            |

| LWE0/LBS0/LSDDQM[0]      | G25                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LWE1/LBS1/LSDDQM[1]      | C23                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LWE2/LBS2/LSDDQM[2]      | J21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LWE3/LBS3/LSDDQM[3]      | A24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LALE                     | H24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9      |

| LBCTL                    | G27                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9      |

| LGPL0/LSDA10             | F23                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LGPL1/LSDWE              | G22                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LGPL2/LOE/LSDRAS         | B27                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9      |

| LGPL3/LSDCAS             | F24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LGPL4/LGTA/LUPWAIT/LPBSE | H23                                                                                                                                                                     | I/O      | BV <sub>DD</sub> | —            |

| LGPL5                    | E26                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LCKE                     | E24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | —            |

| LCLK[0:2]                | E23, D24, H22                                                                                                                                                           | 0        | BV <sub>DD</sub> | —            |

| LSYNC_IN                 | F27                                                                                                                                                                     | I        | BV <sub>DD</sub> | —            |

| LSYNC_OUT                | F28                                                                                                                                                                     | 0        | BV <sub>DD</sub> | —            |

|                          | DMA                                                                                                                                                                     |          |                  |              |

| DMA_DACK[0:1]            | AD3, AE1                                                                                                                                                                | 0        | OV <sub>DD</sub> | 5, 9,<br>107 |

| DMA_DREQ[0:1]            | AD4, AE2                                                                                                                                                                | I        | OV <sub>DD</sub> | _            |

| DMA_DDONE[0:1]           | AD2, AD1                                                                                                                                                                | 0        | OV <sub>DD</sub> | _            |

|                          | Programmable Interrupt Controller                                                                                                                                       |          |                  |              |

| UDE                      | AH16                                                                                                                                                                    | I        | OV <sub>DD</sub> | _            |

| MCP                      | AG19                                                                                                                                                                    | l        | OV <sub>DD</sub> |              |

### Table 73. MPC8545E Pinout Listing (continued)

| Signal                 | Package Pin Number                                                                                                                                                                                                                                                                                               | Pin Type | Power<br>Supply  | Notes    |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

| PCI1_FRAME             | AE11                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_IDSEL             | AG9                                                                                                                                                                                                                                                                                                              | I        | OV <sub>DD</sub> | —        |

| PCI1_REQ64/PCI2_FRAME  | AF14                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2, 5, 10 |

| PCI1_ACK64/PCI2_DEVSEL | V15                                                                                                                                                                                                                                                                                                              | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_CLK               | AE28                                                                                                                                                                                                                                                                                                             | l        | OV <sub>DD</sub> | 39       |

| PCI2_IRDY              | AD26                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_PERR              | AD25                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_GNT[4:1]          | AE26, AG24, AF25, AE25                                                                                                                                                                                                                                                                                           | 0        | OV <sub>DD</sub> | 5, 9, 35 |

| PCI2_GNT0              | AG25                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | _        |

| PCI2_SERR              | AD24                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2,4      |

| PCI2_STOP              | AF24                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_TRDY              | AD27                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_REQ[4:1]          | AD28, AE27, W17, AF26                                                                                                                                                                                                                                                                                            | l        | OV <sub>DD</sub> | —        |

| PCI2_REQ0              | AH25                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | _        |

|                        | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                                       |          | •                | •        |

| MDQ[0:63]              | L18, J18, K14, L13, L19, M18, L15, L14, A17,<br>B17, A13, B12, C18, B18, B13, A12, H18, F18,<br>J14, F15, K19, J19, H16, K15, D17, G16, K13,<br>D14, D18, F17, F14, E14, A7, A6, D5, A4, C8,<br>D7, B5, B4, A2, B1, D1, E4, A3, B2, D2, E3, F3,<br>G4, J5, K5, F6, G5, J6, K4, J1, K2, M5, M3, J3,<br>J2, L1, M6 | I/O      | GV <sub>DD</sub> | _        |

| MECC[0:7]              | H13, F13, F11, C11, J13, G13, D12, M12                                                                                                                                                                                                                                                                           | I/O      | GV <sub>DD</sub> | _        |

| MDM[0:8]               | M17, C16, K17, E16, B6, C4, H4, K1, E13                                                                                                                                                                                                                                                                          | 0        | GV <sub>DD</sub> | _        |

| MDQS[0:8]              | M15, A16, G17, G14, A5, D3, H1, L2, C13                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> | _        |

| MDQS[0:8]              | L17, B16, J16, H14, C6, C2, H3, L4, D13                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> | _        |

| MA[0:15]               | A8, F9, D9, B9, A9, L10, M10, H10, K10, G10,<br>B8, E10, B10, G6, A10, L11                                                                                                                                                                                                                                       | 0        | GV <sub>DD</sub> | —        |

| MBA[0:2]               | F7, J7, M11                                                                                                                                                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —        |

| MWE                    | E7                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | _        |

| MCAS                   | H7                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | _        |

| MRAS                   | L8                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | _        |

| MCKE[0:3]              | F10, C10, J11, H11                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | 11       |

| MCS[0:3]               | K8, J8, G8, F8                                                                                                                                                                                                                                                                                                   | 0        | GV <sub>DD</sub> | —        |

| MCK[0:5]               | H9, B15, G2, M9, A14, F1                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> | -        |

| MCK[0:5]               | J9, A15, G1, L9, B14, F2                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> | —        |

| MODT[0:3]              | E6, K6, L7, M7                                                                                                                                                                                                                                                                                                   | 0        | GV <sub>DD</sub> |          |

| Signal                | Package Pin Number                              | Pin Type | Power<br>Supply  | Notes |

|-----------------------|-------------------------------------------------|----------|------------------|-------|

| UDE                   | AH16                                            | I        | OV <sub>DD</sub> | _     |

| MCP                   | AG19                                            | I        | OV <sub>DD</sub> | _     |

| IRQ[0:7]              | AG23, AF18, AE18, AF20, AG18, AF17, AH24, AE20  | I        | OV <sub>DD</sub> | -     |

| IRQ[8]                | AF19                                            | I        | OV <sub>DD</sub> | —     |

| IRQ[9]/DMA_DREQ3      | AF21                                            | Ι        | OV <sub>DD</sub> | 1     |

| IRQ[10]/DMA_DACK3     | AE19                                            | I/O      | OV <sub>DD</sub> | 1     |

| IRQ[11]/DMA_DDONE3    | AD20                                            | I/O      | OV <sub>DD</sub> | 1     |

| IRQ_OUT               | AD18                                            | 0        | OV <sub>DD</sub> | 2, 4  |

|                       | Ethernet Management Interface                   |          | 1                |       |

| EC_MDC                | AB9                                             | 0        | OV <sub>DD</sub> | 5, 9  |

| EC_MDIO               | AC8                                             | I/O      | OV <sub>DD</sub> | _     |

|                       | Gigabit Reference Clock                         |          |                  |       |

| EC_GTX_CLK125         | V11                                             | I        | LV <sub>DD</sub> |       |

|                       | Three-Speed Ethernet Controller (Gigabit Ethern | et 1)    | 1                |       |

| TSEC1_RXD[7:0]        | R5, U1, R3, U2, V3, V1, T3, T2                  | I        | LV <sub>DD</sub> |       |

| TSEC1_TXD[7:0]        | T10, V7, U10, U5, U4, V6, T5, T8                | 0        | LV <sub>DD</sub> | 5, 9  |

| TSEC1_COL             | R4                                              | I        | LV <sub>DD</sub> |       |

| TSEC1_CRS             | V5                                              | I/O      | LV <sub>DD</sub> | 20    |

| TSEC1_GTX_CLK         | U7                                              | 0        | LV <sub>DD</sub> | _     |

| TSEC1_RX_CLK          | U3                                              | I        | LV <sub>DD</sub> |       |

| TSEC1_RX_DV           | V2                                              | I        | LV <sub>DD</sub> | _     |

| TSEC1_RX_ER           | T1                                              | I        |                  | _     |

| TSEC1_TX_CLK          | Т6                                              | I        | LV <sub>DD</sub> | —     |

| TSEC1_TX_EN           | U9                                              | 0        | LV <sub>DD</sub> | 30    |

| TSEC1_TX_ER           | Т7                                              | 0        | LV <sub>DD</sub> | _     |

| GPIN[0:7]             | P2, R2, N1, N2, P3, M2, M1, N3                  | I        | LV <sub>DD</sub> | 103   |

| GPOUT[0:5]            | .5] N9, N10, P8, N7, R9, N5 O                   |          | LV <sub>DD</sub> | _     |

| cfg_dram_type0/GPOUT6 | R8                                              | 0        | LV <sub>DD</sub> | 5, 9  |

| GPOUT7                | N6                                              | 0        | LV <sub>DD</sub> | —     |

| Reserved              | P1                                              | _        | —                | 104   |

| Reserved              | R6                                              |          | —                | 104   |

| Reserved              | P6                                              |          | —                | 15    |

| Reserved              | N4                                              | _        | _                | 105   |

| Signal                 | Package Pin Number                       | Pin Type    | Power<br>Supply  | Notes           |

|------------------------|------------------------------------------|-------------|------------------|-----------------|

| IIC1_SDA               | AG21                                     | I/O         | OV <sub>DD</sub> | 4, 27           |

| IIC2_SCL               | AG15                                     | AG15 I/O OV |                  |                 |

| IIC2_SDA               | AG14                                     | I/O         | OV <sub>DD</sub> | 4, 27           |

|                        | SerDes                                   | 1           |                  |                 |

| SD_RX[0:7]             | M28, N26, P28, R26, W26, Y28, AA26, AB28 | Ι           | XV <sub>DD</sub> | —               |

| SD_RX[0:7]             | M27, N25, P27, R25, W25, Y27, AA25, AB27 | I           | XV <sub>DD</sub> | _               |

| SD_TX[0:7]             | M22, N20, P22, R20, U20, V22, W20, Y22   | 0           | XV <sub>DD</sub> | —               |

| SD_TX[0:7]             | M23, N21, P23, R21, U21, V23, W21, Y23   | 0           | XV <sub>DD</sub> | _               |

| SD_PLL_TPD             | U28                                      | 0           | XV <sub>DD</sub> | 24              |

| SD_REF_CLK             | T28                                      | Ι           | XV <sub>DD</sub> | —               |

| SD_REF_CLK             | T27                                      | I           | XV <sub>DD</sub> | _               |

| Reserved               | AC1, AC3                                 | —           | _                | 2               |

| Reserved               | M26, V28                                 | —           | _                | 32              |

| Reserved               | M25, V27                                 | _           | _                | 34              |

| Reserved               | M20, M21, T22, T23                       | —           | _                | 38              |

|                        | General-Purpose Output                   |             |                  |                 |

| GPOUT[24:31]           | K26, K25, H27, G28, H25, J26, K24, K23   | 0           | $BV_DD$          | —               |

|                        | System Control                           |             |                  |                 |

| HRESET                 | AG17                                     | Ι           | OV <sub>DD</sub> | —               |

| HRESET_REQ             | AG16                                     | 0           | $OV_DD$          | 29              |

| SRESET                 | AG20                                     | I           | OV <sub>DD</sub> | —               |

| CKSTP_IN               | AA9 I                                    |             | $OV_{DD}$        | —               |

| CKSTP_OUT              | AA8                                      | 0           | OV <sub>DD</sub> | 2, 4            |

|                        | Debug                                    |             |                  |                 |

| TRIG_IN                | AB2                                      | Ι           | $OV_{DD}$        | —               |

| TRIG_OUT/READY/QUIESCE | AB1                                      | 0           | OV <sub>DD</sub> | 6, 9, 19,<br>29 |

| MSRCID[0:1]            | AE4, AG2                                 | 0           | $OV_{DD}$        | 5, 6, 9         |

| MSRCID[2:4]            | AF3, AF1, AF2                            | 0           | $OV_{DD}$        | 6, 19, 29       |

| MDVAL                  | AE5                                      | 0           | $OV_{DD}$        | 6               |

| CLK_OUT                | AE21                                     | 0           | OV <sub>DD</sub> | 11              |

|                        | Clock                                    |             |                  |                 |

| RTC                    | AF16                                     | Ι           | $OV_{DD}$        | —               |

| SYSCLK                 | AH17                                     | I           | OV <sub>DD</sub> |                 |

| Signal           | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Type                                              | Power<br>Supply  | Notes     |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|-----------|

|                  | JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11                                                    |                  |           |

| ТСК              | AG28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | —         |

| TDI              | AH28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 12        |

| TDO              | AF28 O OV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                       |                  |           |

| TMS              | AH27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 12        |

| TRST             | AH23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 12        |

|                  | DFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       |                  |           |

| L1_TSTCLK        | AC25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 25        |

| L2_TSTCLK        | AE22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 25        |

| LSSD_MODE        | AH20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 25        |

| TEST_SEL         | AH14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 109       |