Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                       |

|---------------------------------|-----------------------------------------------------------------------|

| Product Status                  | Obsolete                                                              |

| Core Processor                  | PowerPC e500                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 1.0GHz                                                                |

| Co-Processors/DSP               | Signal Processing; SPE                                                |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                      |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (4)                                                   |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                      |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                     |

| Package / Case                  | 783-BBGA, FCBGA                                                       |

| Supplier Device Package         | 783-FCBGA (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8545vuaqg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

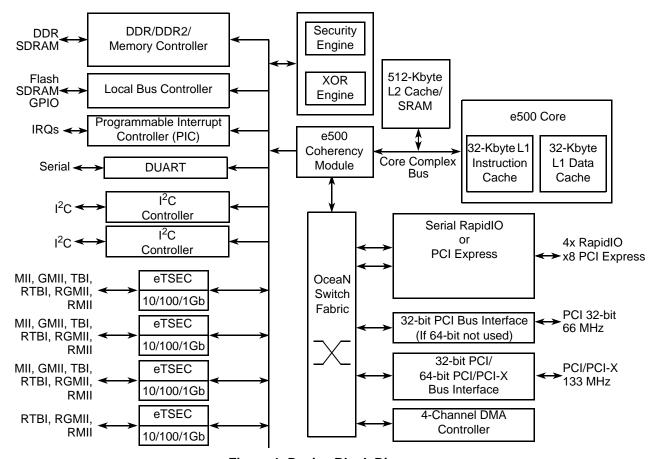

Figure 1. Device Block Diagram

## 1.1 Key Features

The following list provides an overview of the device feature set:

- High-performance 32-bit core built on Power Architecture® technology.

- 32-Kbyte L1 instruction cache and 32-Kbyte L1 data cache with parity protection. Caches can be locked entirely or on a per-line basis, with separate locking for instructions and data.

- Signal-processing engine (SPE) APU (auxiliary processing unit). Provides an extensive instruction set for vector (64-bit) integer and fractional operations. These instructions use both the upper and lower words of the 64-bit GPRs as they are defined by the SPE APU.

- Double-precision floating-point APU. Provides an instruction set for double-precision (64-bit) floating-point instructions that use the 64-bit GPRs.

- 36-bit real addressing

- Embedded vector and scalar single-precision floating-point APUs. Provide an instruction set for single-precision (32-bit) floating-point instructions.

- Memory management unit (MMU). Especially designed for embedded applications. Supports 4-Kbyte to 4-Gbyte page sizes.

- Enhanced hardware and software debug support

Table 2. Recommended Operating Conditions (continued)

| Characteristic             | Symbol | Recommended<br>Value | Unit | Notes |

|----------------------------|--------|----------------------|------|-------|

| Junction temperature range | Tj     | 0 to 105             | °C   | _     |

#### Notes:

- 1. This voltage is the input to the filter discussed in Section 22.2, "PLL Power Supply Filtering," and not necessarily the voltage at the AV<sub>DD</sub> pin, which may be reduced from V<sub>DD</sub> by the filter.

- 2. Caution: MV<sub>IN</sub> must not exceed GV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 3. Caution: OV<sub>IN</sub> must not exceed OV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 4. Caution: L/TV<sub>IN</sub> must not exceed L/TV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

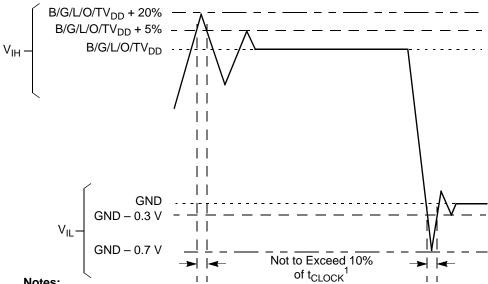

The following figure shows the undershoot and overshoot voltages at the interfaces of this device.

#### Notes:

- 1. t<sub>CLOCK</sub> refers to the clock period associated with the respective interface:

- For I<sup>2</sup>C and JTAG, t<sub>CLOCK</sub> references SYSCLK. For DDR, t<sub>CLOCK</sub> references MCLK.

- For eTSEC, t<sub>CLOCK</sub> references EC\_GTX\_CLK125.

- For LBIU, t<sub>CLOCK</sub> references LCLK.

- For PCI, t<sub>CLOCK</sub> references PCIn\_CLK or SYSCLK.

- For SerDes, t<sub>CLOCK</sub> references SD\_REF\_CLK.

- 2. Note that with the PCI overshoot allowed (as specified above), the device does not fully comply with the maximum AC ratings and device protection guideline outlined in the PCI rev. 2.2 standard (section 4.2.2.3).

Figure 2. Overshoot/Undershoot Voltage for GV<sub>DD</sub>/OV<sub>DD</sub>/LV<sub>DD</sub>/BV<sub>DD</sub>/TV<sub>DD</sub>

The core voltage must always be provided at nominal 1.1 V. Voltage to the processor interface I/Os are provided through separate sets of supply pins and must be provided at the voltages shown in Table 2. The input voltage threshold scales with respect to the associated I/O supply voltage. OV<sub>DD</sub> and LV<sub>DD</sub> based receivers are simple CMOS I/O circuits and satisfy appropriate LVCMOS type specifications. The DDR SDRAM interface uses a single-ended differential receiver referenced the externally supplied MV<sub>RFF</sub> signal (nominally set to GV<sub>DD</sub>/2) as is appropriate for the SSTL2 electrical signaling standard.

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

## 2.1.3 Output Driver Characteristics

The following table provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

**Programmable** Supply **Output Impedance Notes Driver Type** Voltage  $(\Omega)$ Local bus interface utilities signals 25  $BV_{DD} = 3.3 V$ 1 25  $BV_{DD} = 2.5 V$  $BV_{DD} = 3.3 V$ 45(default) 45(default)  $BV_{DD} = 2.5 V$  $\overline{O}V_{DD} = 3.3 V$ PCI signals 25 45(default) DDR signal  $GV_{DD} = 2.5 V$ 36 (half strength mode)  $GV_{DD} = 1.8 V$ DDR2 signal 3 36 (half strength mode)  $L/TV_{DD} = 2.5/3.3 V$ 45 TSEC/10/100 signals DUART, system control, JTAG 45  $OV_{DD} = 3.3 V$ I2C  $OV_{DD} = 3.3 V$ 150

**Table 3. Output Drive Capability**

#### Notes:

- 1. The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

- 2. The drive strength of the PCI interface is determined by the setting of the PCI\_GNT1 signal at reset.

- 3. The drive strength of the DDR interface in half-strength mode is at  $T_i = 105$ °C and at  $GV_{DD}$  (min).

# 2.2 Power Sequencing

The device requires its power rails to be applied in a specific sequence in order to ensure proper device operation. These requirements are as follows for power-up:

- 1.  $V_{DD}$ ,  $AV_{DD}$ ,  $BV_{DD}$ ,  $LV_{DD}$ ,  $OV_{DD}$ ,  $SV_{DD}$ ,  $TV_{DD}$ ,  $XV_{DD}$

- $2. \text{ GV}_{\text{DD}}$

All supplies must be at their stable values within 50 ms.

#### NOTE

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

#### **NOTE**

In order to guarantee MCKE low during power-up, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power-up, then the sequencing for  $GV_{DD}$  is not required.

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

#### **Power Characteristics** 3

The estimated typical power dissipation for the core complex bus (CCB) versus the core frequency for this family of PowerQUICC III devices is shown in the following table.

**Table 4. Device Power Dissipation**

| CCB Frequency <sup>1</sup> | Core Frequency | SLEEP <sup>2</sup> | Typical-65 <sup>3</sup> | Typical-105 <sup>4</sup> | Maximum <sup>5</sup> | Unit |

|----------------------------|----------------|--------------------|-------------------------|--------------------------|----------------------|------|

| 400                        | 800            | 2.7                | 4.6                     | 7.5                      | 8.1                  | W    |

|                            | 1000           | 2.7                | 5.0                     | 7.9                      | 8.5                  | W    |

|                            | 1200           | 2.7                | 5.4                     | 8.3                      | 8.9                  |      |

| 500                        | 1500           | 11.5               | 13.6                    | 16.5                     | 18.6                 | W    |

| 533                        | 1333           | 6.2                | 7.9                     | 10.8                     | 12.8                 | W    |

#### Notes:

- 1. CCB frequency is the SoC platform frequency, which corresponds to the DDR data rate.

- 2. SLEEP is based on  $V_{DD} = 1.1 \text{ V}$ ,  $T_i = 65^{\circ}\text{C}$ .

- Typical-65 is based on V<sub>DD</sub> = 1.1 V, T<sub>j</sub> = 65°C, running Dhrystone.

Typical-105 is based on V<sub>DD</sub> = 1.1 V, T<sub>j</sub> = 105°C, running Dhrystone.

Maximum is based on V<sub>DD</sub> = 1.1 V, T<sub>j</sub> = 105°C, running a smoke test.

# 4.3 eTSEC Gigabit Reference Clock Timing

GMII. TBI

The following table provides the eTSEC gigabit reference clocks (EC\_GTX\_CLK125) AC timing specifications for the device.

Parameter/Condition **Symbol** Min Max Unit **Notes** Typ EC\_GTX\_CLK125 frequency 125 MHz f<sub>G125</sub> EC\_GTX\_CLK125 cycle time 8 ns t<sub>G125</sub> EC\_GTX\_CLK125 rise and fall time 1 ns t<sub>G125R</sub>, t<sub>G125F</sub> 0.75 L/TVDD = 2.5 V1.0 L/TVDD = 3.3 V% EC\_GTX\_CLK125 duty cycle 2, 3 t<sub>G125H</sub>/t<sub>G125</sub>

45

47

55

53

Table 6. EC\_GTX\_CLK125 AC Timing Specifications

#### Notes:

- 1. Rise and fall times for EC\_GTX\_CLK125 are measured from 0.5 and 2.0 V for L/TV<sub>DD</sub> = 2.5 V, and from 0.6 and 2.7 V for L/TV<sub>DD</sub> = 3.3 V.

- 2. Timing is guaranteed by design and characterization.

1000Base-T for RGMII, RTBI

3. EC\_GTX\_CLK125 is used to generate the GTX clock TSEC\_n\_GTX\_CLK for the eTSEC transmitter with 2% degradation. EC\_GTX\_CLK125 duty cycle can be loosened from 47/53% as long as the PHY device can tolerate the duty cycle generated by the TSEC\_n\_GTX\_CLK. See Section 8.2.6, "RGMII and RTBI AC Timing Specifications," for duty cycle for 10Base-T and 100Base-T reference clock.

# 4.4 PCI/PCI-X Reference Clock Timing

When the PCI/PCI-X controller is configured for asynchronous operation, the reference clock for the PCI/PCI-x controller is not the SYSCLK input, but instead the PCIn\_CLK. The following table provides the PCI/PCI-X reference clock AC timing specifications for the device.

Table 7. PCIn\_CLK AC Timing Specifications

At recommended operating conditions (see Table 2) with  $OV_{DD} = 3.3 \text{ V} \pm 165 \text{ mV}$ .

| Parameter/Condition         | Symbol                                    | Min | Тур | Max | Unit | Notes |

|-----------------------------|-------------------------------------------|-----|-----|-----|------|-------|

| PCIn_CLK frequency          | f <sub>PCICLK</sub>                       | 16  | _   | 133 | MHz  | _     |

| PCIn_CLK cycle time         | t <sub>PCICLK</sub>                       | 7.5 | _   | 60  | ns   | _     |

| PCIn_CLK rise and fall time | t <sub>PCIKH</sub> , t <sub>PCIKL</sub>   | 0.6 | 1.0 | 2.1 | ns   | 1, 2  |

| PCIn_CLK duty cycle         | t <sub>PCIKHKL</sub> /t <sub>PCICLK</sub> | 40  | _   | 60  | %    | 2     |

#### Notes:

- 1. Rise and fall times for SYSCLK are measured at 0.6 and 2.7 V.

- 2. Timing is guaranteed by design and characterization.

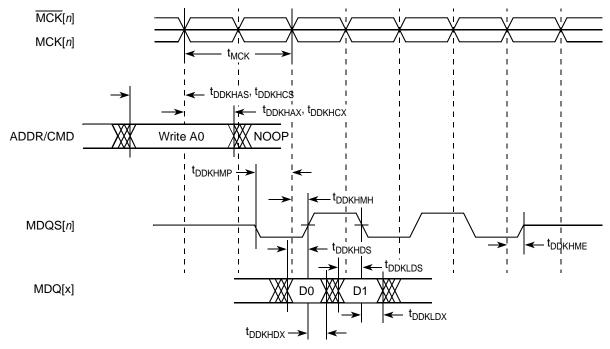

Figure 4 shows the DDR SDRAM output timing diagram.+

Figure 4. DDR SDRAM Output Timing Diagram

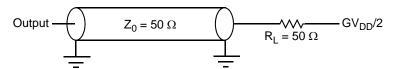

Figure 5 provides the AC test load for the DDR bus.

Figure 5. DDR AC Test Load

#### **Enhanced Three-Speed Ethernet (eTSEC)**

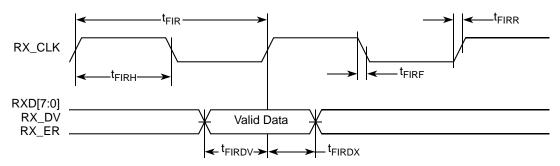

Figure 7. FIFO Receive AC Timing Diagram

# 8.2.2 GMII AC Timing Specifications

This section describes the GMII transmit and receive AC timing specifications.

## 8.2.2.1 GMII Transmit AC Timing Specifications

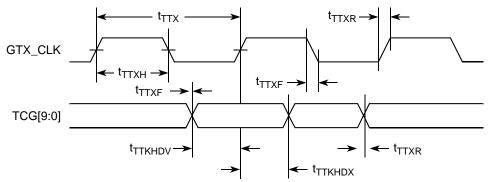

This table provides the GMII transmit AC timing specifications.

**Table 26. GMII Transmit AC Timing Specifications**

| Parameter/Condition                               | Symbol <sup>1</sup>            | Min | Тур | Max | Unit |

|---------------------------------------------------|--------------------------------|-----|-----|-----|------|

| GMII data TXD[7:0], TX_ER, TX_EN setup time       | t <sub>GTKHDV</sub>            | 2.5 | _   | _   | ns   |

| GTX_CLK to GMII data TXD[7:0], TX_ER, TX_EN delay | t <sub>GTKHDX</sub>            | 0.5 | _   | 5.0 | ns   |

| GTX_CLK data clock rise time (20%–80%)            | t <sub>GTXR</sub> <sup>2</sup> | _   | _   | 1.0 | ns   |

| GTX_CLK data clock fall time (80%–20%)            | t <sub>GTXF</sub> <sup>2</sup> | _   | _   | 1.0 | ns   |

#### Notes:

30

- 1. The symbols used for timing specifications follow the pattern t<sub>(first two letters of functional block)</sub>(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>GTKHDV</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) going invalid (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GTX</sub> represents the GMII(G) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. Guaranteed by design.

Figure 14 shows the TBI transmit AC timing diagram.

Figure 14. TBI Transmit AC Timing Diagram

## 8.2.4.2 TBI Receive AC Timing Specifications

This table provides the TBI receive AC timing specifications.

**Table 31. TBI Receive AC Timing Specifications**

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур  | Max | Unit |

|---------------------------------------------|-------------------------------------|-----|------|-----|------|

| TSECn_RX_CLK[0:1] clock period              | t <sub>TRX</sub>                    | _   | 16.0 | _   | ns   |

| TSECn_RX_CLK[0:1] skew                      | t <sub>SKTRX</sub>                  | 7.5 | _    | 8.5 | ns   |

| TSECn_RX_CLK[0:1] duty cycle                | t <sub>TRXH</sub> /t <sub>TRX</sub> | 40  | _    | 60  | %    |

| RCG[9:0] setup time to rising TSECn_RX_CLK  | t <sub>TRDVKH</sub>                 | 2.5 | _    | _   | ns   |

| RCG[9:0] hold time to rising TSECn_RX_CLK   | t <sub>TRDXKH</sub>                 | 1.5 | _    | _   | ns   |

| TSECn_RX_CLK[0:1] clock rise time (20%–80%) | t <sub>TRXR</sub> <sup>2</sup>      | 0.7 | _    | 2.4 | ns   |

| TSECn_RX_CLK[0:1] clock fall time (80%–20%) | t <sub>TRXF</sub> <sup>2</sup>      | 0.7 | _    | 2.4 | ns   |

#### Notes:

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>TRDVKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>TRDXKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TRX</sub> represents the TBI (T) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall). For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (TRX).

- 2. Guaranteed by design.

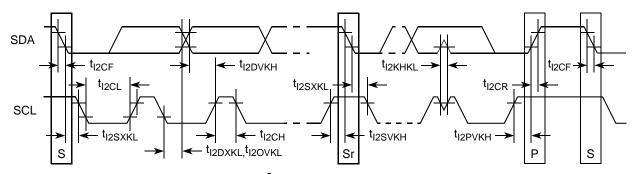

Figure 34 shows the AC timing diagram for the I<sup>2</sup>C bus.

Figure 34. I<sup>2</sup>C Bus AC Timing Diagram

#### PCI/PCI-X

## Table 54. PCI-X AC Timing Specifications at 133 MHz (continued)

| Parameter                                        | Symbol              | Min | Max | Unit | Notes |

|--------------------------------------------------|---------------------|-----|-----|------|-------|

| HRESET to PCI-X initialization pattern hold time | t <sub>PCRHIX</sub> | 0   | 50  | ns   | 6, 12 |

#### Notes:

- 1. See the timing measurement conditions in the PCI-X 1.0a Specification.

- 2. Minimum times are measured at the package pin (not the test point). Maximum times are measured with the test point and load circuit.

- 3. Setup time for point-to-point signals applies to REQ and GNT only. All other signals are bused.

- 4. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 5. Setup time applies only when the device is not driving the pin. Devices cannot drive and receive signals at the same time.

- 6. Maximum value is also limited by delay to the first transaction (time for HRESET high to first configuration access, t<sub>PCRHFV</sub>). The PCI-X initialization pattern control signals after the rising edge of HRESET must be negated no later than two clocks before the first FRAME and must be floated no later than one clock before FRAME is asserted.

- 7. A PCI-X device is permitted to have the minimum values shown for t<sub>PCKHOV</sub> and t<sub>CYC</sub> only in PCI-X mode. In conventional mode, the device must meet the requirements specified in PCI 2.2 for the appropriate clock frequency.

- 8. Device must meet this specification independent of how many outputs switch simultaneously.

- 9. The timing parameter tpcIVKH is a minimum of 1.4 ns rather than the minimum of 1.2 ns in the PCI-X 1.0a Specification.

- 10. The timing parameter t<sub>PCRHFV</sub> is a minimum of 10 clocks rather than the minimum of 5 clocks in the *PCI-X 1.0a* Specification.

- 11. Guaranteed by characterization.

- 12. Guaranteed by design.

#### **High-Speed Serial Interfaces (HSSI)**

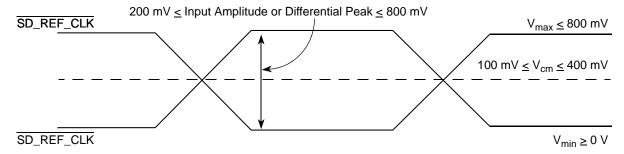

- The input amplitude of the differential clock must be between 400 and 1600 mV differential peak-peak (or between 200 and 800 mV differential peak). In other words, each signal wire of the differential pair must have a single-ended swing less than 800 mV and greater than 200 mV. This requirement is the same for both external DC- or AC-coupled connection.

- For external DC-coupled connection, as described in Section 16.2.1, "SerDes Reference Clock Receiver Characteristics," the maximum average current requirements sets the requirement for average voltage (common mode voltage) to be between 100 and 400 mV. Figure 40 shows the SerDes reference clock input requirement for DC-coupled connection scheme.

- For external AC-coupled connection, there is no common mode voltage requirement for the clock driver. Since the external AC-coupling capacitor blocks the DC level, the clock driver and the SerDes reference clock receiver operate in different command mode voltages. The SerDes reference clock receiver in this connection scheme has its common mode voltage set to SGND\_SRDSn. Each signal wire of the differential inputs is allowed to swing below and above the command mode voltage (SGND\_SRDSn). Figure 41 shows the SerDes reference clock input requirement for AC-coupled connection scheme.

## • Single-ended mode

- The reference clock can also be single-ended. The SD\_REF\_CLK input amplitude (single-ended swing) must be between 400 and 800 mV peak-to-peak (from V<sub>min</sub> to V<sub>max</sub>) with SD\_REF\_CLK either left unconnected or tied to ground.

- The SD\_REF\_CLK input average voltage must be between 200 and 400 mV. Figure 42 shows the SerDes reference clock input requirement for single-ended signaling mode.

- To meet the input amplitude requirement, the reference clock inputs might need to be DC- or AC-coupled externally. For the best noise performance, the reference of the clock could be DC- or AC-coupled into the unused phase (SD\_REF\_CLK) through the same source impedance as the clock input (SD\_REF\_CLK) in use.

Figure 40. Differential Reference Clock Input DC Requirements (External DC-Coupled)

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

73

# 17 PCI Express

This section describes the DC and AC electrical specifications for the PCI Express bus of the MPC8548E.

# 17.1 <u>DC Requirements for PCI Express SD\_REF\_CLK and SD\_REF\_CLK</u>

For more information, see Section 16.2, "SerDes Reference Clocks."

## 17.2 AC Requirements for PCI Express SerDes Clocks

Table 55 lists the AC requirements for the PCI Express SerDes clocks.

Table 55. SD\_REF\_CLK and SD\_REF\_CLK AC Requirements

| Symbol             | Parameter Description                                                                     | Min             | Тур | Max | Unit | Notes |

|--------------------|-------------------------------------------------------------------------------------------|-----------------|-----|-----|------|-------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                         | _               | 10  | _   | ns   | 1     |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles. | _               | _   | 100 | ps   |       |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location.              | <del>-</del> 50 | _   | 50  | ps   | _     |

#### Note:

# 17.3 Clocking Dependencies

The ports on the two ends of a link must transmit data at a rate that is within 600 parts per million (ppm) of each other at all times. This is specified to allow bit rate clock sources with a  $\pm 300$  ppm tolerance.

# 17.4 Physical Layer Specifications

The following is a summary of the specifications for the physical layer of PCI Express on this device. For further details as well as the specifications of the transport and data link layer see *PCI Express Base Specification*. *Rev.* 1.0a.

# 17.4.1 Differential Transmitter (TX) Output

Table 56 defines the specifications for the differential output at all transmitters (TXs). The parameters are specified at the component pins.

<sup>1.</sup> Typical based on PCI Express Specification 2.0.

#### Notes:

- 1. All dimensions are in millimeters.

- 2. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 5. Parallelism measurement shall exclude any effect of mark on top surface of package.

- 6. All dimensions are symmetric across the package center lines unless dimensioned otherwise.

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

Table 71. MPC8548E Pinout Listing (continued)

| Signal                   | Package Pin Number                                                                                                                                             | Pin Type | Power<br>Supply  | Notes    |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

| MWE                      | E7                                                                                                                                                             | 0        | GV <sub>DD</sub> | _        |

| MCAS                     | H7                                                                                                                                                             | 0        | GV <sub>DD</sub> | _        |

| MRAS                     | L8                                                                                                                                                             | 0        | GV <sub>DD</sub> | _        |

| MCKE[0:3]                | F10, C10, J11, H11                                                                                                                                             | 0        | GV <sub>DD</sub> | 11       |

| MCS[0:3]                 | K8, J8, G8, F8                                                                                                                                                 | 0        | GV <sub>DD</sub> | _        |

| MCK[0:5]                 | H9, B15, G2, M9, A14, F1                                                                                                                                       | 0        | GV <sub>DD</sub> | <u> </u> |

| MCK[0:5]                 | J9, A15, G1, L9, B14, F2                                                                                                                                       | 0        | GV <sub>DD</sub> | <u> </u> |

| MODT[0:3]                | E6, K6, L7, M7                                                                                                                                                 | 0        | GV <sub>DD</sub> | <u> </u> |

| MDIC[0:1]                | A19, B19                                                                                                                                                       | I/O      | GV <sub>DD</sub> | 36       |

|                          | Local Bus Controller Interface                                                                                                                                 |          |                  |          |

| LAD[0:31]                | E27, B20, H19, F25, A20, C19, E28, J23, A25, K22, B28, D27, D19, J22, K20, D28, D25, B25, E22, F22, F21, C25, C22, B23, F20, A23, A22, E19, A21, D21, F19, B21 | I/O      | BV <sub>DD</sub> | _        |

| LDP[0:3]                 | K21, C28, B26, B22                                                                                                                                             | I/O      | BV <sub>DD</sub> | <u> </u> |

| LA[27]                   | H21                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 9     |

| LA[28:31]                | H20, A27, D26, A28                                                                                                                                             | 0        | BV <sub>DD</sub> | 5, 7, 9  |

| LCS[0:4]                 | J25, C20, J24, G26, A26                                                                                                                                        | 0        | BV <sub>DD</sub> |          |

| LCS5/DMA_DREQ2           | D23                                                                                                                                                            | I/O      | BV <sub>DD</sub> | 1        |

| LCS6/DMA_DACK2           | G20                                                                                                                                                            | 0        | BV <sub>DD</sub> | 1        |

| LCS7/DMA_DDONE2          | E21                                                                                                                                                            | 0        | BV <sub>DD</sub> | 1        |

| LWE0/LBS0/LSDDQM[0]      | G25                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 9     |

| LWE1/LBS1/LSDDQM[1]      | C23                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 9     |

| LWE2/LBS2/LSDDQM[2]      | J21                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 9     |

| LWE3/LBS3/LSDDQM[3]      | A24                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 9     |

| LALE                     | H24                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 8, 9  |

| LBCTL                    | G27                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 8, 9  |

| LGPL0/LSDA10             | F23                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 9     |

| LGPL1/LSDWE              | G22                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 9     |

| LGPL2/LOE/LSDRAS         | B27                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 8, 9  |

| LGPL3/LSDCAS             | F24                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 9     |

| LGPL4/LGTA/LUPWAIT/LPBSE | H23                                                                                                                                                            | I/O      | BV <sub>DD</sub> | _        |

| LGPL5                    | E26                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 9     |

| LCKE                     | E24                                                                                                                                                            | 0        | BV <sub>DD</sub> | _        |

| LCLK[0:2]                | E23, D24, H22                                                                                                                                                  | 0        | BV <sub>DD</sub> | _        |

## **Package Description**

Table 71. MPC8548E Pinout Listing (continued)

| Signal                 | Package Pin Number                       | Pin Type | Power<br>Supply  | Notes           |

|------------------------|------------------------------------------|----------|------------------|-----------------|

|                        | I <sup>2</sup> C interface               |          |                  | -               |

| IIC1_SCL               | AG22                                     | I/O      | OV <sub>DD</sub> | 4, 27           |

| IIC1_SDA               | AG21                                     | I/O      | OV <sub>DD</sub> | 4, 27           |

| IIC2_SCL               | AG15                                     | I/O      | OV <sub>DD</sub> | 4, 27           |

| IIC2_SDA               | AG14                                     | I/O      | OV <sub>DD</sub> | 4, 27           |

|                        | SerDes                                   |          |                  | •               |

| SD_RX[0:7]             | M28, N26, P28, R26, W26, Y28, AA26, AB28 | I        | $XV_{DD}$        | _               |

| SD_RX[0:7]             | M27, N25, P27, R25, W25, Y27, AA25, AB27 | I        | $XV_{DD}$        | _               |

| SD_TX[0:7]             | M22, N20, P22, R20, U20, V22, W20, Y22   | 0        | $XV_{DD}$        | _               |

| SD_TX[0:7]             | M23, N21, P23, R21, U21, V23, W21, Y23   | 0        | $XV_{DD}$        | _               |

| SD_PLL_TPD             | U28                                      | 0        | $XV_{DD}$        | 24              |

| SD_REF_CLK             | T28                                      | I        | $XV_{DD}$        | 3               |

| SD_REF_CLK             | T27                                      | I        | $XV_{DD}$        | 3               |

| Reserved               | AC1, AC3                                 | _        | _                | 2               |

| Reserved               | M26, V28                                 | _        | _                | 32              |

| Reserved               | M25, V27                                 | _        | _                | 34              |

| Reserved               | M20, M21, T22, T23                       | _        | _                | 38              |

|                        | General-Purpose Output                   |          |                  | -               |

| GPOUT[24:31]           | K26, K25, H27, G28, H25, J26, K24, K23   | 0        | BV <sub>DD</sub> | _               |

|                        | System Control                           |          |                  | -               |

| HRESET                 | AG17                                     | I        | OV <sub>DD</sub> | _               |

| HRESET_REQ             | AG16                                     | 0        | OV <sub>DD</sub> | 29              |

| SRESET                 | AG20                                     | I        | OV <sub>DD</sub> | _               |

| CKSTP_IN               | AA9                                      | I        | OV <sub>DD</sub> | _               |

| CKSTP_OUT              | AA8                                      | 0        | OV <sub>DD</sub> | 2, 4            |

|                        | Debug                                    |          |                  | -               |

| TRIG_IN                | AB2                                      | I        | OV <sub>DD</sub> | _               |

| TRIG_OUT/READY/QUIESCE | AB1                                      | 0        | OV <sub>DD</sub> | 6, 9,<br>19, 29 |

| MSRCID[0:1]            | AE4, AG2                                 | 0        | OV <sub>DD</sub> | 5, 6, 9         |

| MSRCID[2:4]            | AF3, AF1, AF2                            | 0        | OV <sub>DD</sub> | 6, 19,<br>29    |

| MDVAL                  | AE5                                      | 0        | OV <sub>DD</sub> | 6               |

| CLK_OUT                | AE21                                     | 0        | OV <sub>DD</sub> | 11              |

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

## Table 71. MPC8548E Pinout Listing (continued)

| Signal | Package Pin Number | Pin Type | Power<br>Supply | Notes |  |

|--------|--------------------|----------|-----------------|-------|--|

|--------|--------------------|----------|-----------------|-------|--|

- 25. These are test signals for factory use only and must be pulled up (100  $\Omega$ –1 k $\Omega$ ) to OV<sub>DD</sub> for normal machine operation.

- 26.Independent supplies derived from board V<sub>DD</sub>.

- 27.Recommend a pull-up resistor (~1 k $\Omega$ ) be placed on this pin to OV<sub>DD</sub>.

- 29. The following pins must NOT be pulled down during power-on reset: TSEC3\_TXD[3], TSEC4\_TXD3/TSEC3\_TXD7, HRESET\_REQ, TRIG\_OUT/READY/QUIESCE, MSRCID[2:4], ASLEEP.

- 30. This pin requires an external 4.7-k $\Omega$  pull-down resistor to prevent PHY from seeing a valid transmit enable before it is actively driven.

- 31. This pin is only an output in eTSEC3 FIFO mode when used as Rx flow control.

- 32. These pins must be connected to XV<sub>DD</sub>.

- 33.TSEC2\_TXD1, TSEC2\_TX\_ER are multiplexed as cfg\_dram\_type[0:1]. They must be valid at power-up, even before HRESET assertion.

- 34. These pins must be pulled to ground through a 300- $\Omega$  (±10%) resistor.

- 35.When a PCI block is disabled, either the POR config pin that selects between internal and external arbiter must be pulled down to select external arbiter if there is any other PCI device connected on the PCI bus, or leave the PCIn\_AD pins as 'no connect' or terminated through 2–10 kΩ pull-up resistors with the default of internal arbiter if the PCIn\_AD pins are not connected to any other PCI device. The PCI block drives the PCIn\_AD pins if it is configured to be the PCI arbiter—through POR config pins—irrespective of whether it is disabled via the DEVDISR register or not. It may cause contention if there is any other PCI device connected on the bus.

- 36.MDIC0 is grounded through an 18.2- $\Omega$  precision 1% resistor and MDIC1 is connected to GV<sub>DD</sub> through an 18.2- $\Omega$  precision 1% resistor. These pins are used for automatic calibration of the DDR IOs.

- 38. These pins must be left floating.

- 39. If PCI1 or PCI2 is configured as PCI asynchronous mode, a valid clock must be provided on pin PCI1\_CLK or PCI2\_CLK. Otherwise the processor will not boot up.

- 40. These pins must be connected to GND.

- 101. This pin requires an external 4.7-k $\Omega$  resistor to GND.

- 102.For Rev. 2.x silicon, DMA\_DACK[0:1] must be 0b11 during POR configuration; for rev. 1.x silicon, the pin values during POR configuration are don't care.

- 103.If these pins are not used as GPINn (general-purpose input), they must be pulled low (to GND) or high (to  $LV_{DD}$ ) through 2–10 k $\Omega$  resistors.

- 104. These must be pulled low to GND through 2–10 k $\Omega$  resistors if they are not used.

- 105. These must be pulled low or high to  $LV_{DD}$  through 2–10 k $\Omega$  resistors if they are not used.

- 106. For rev. 2.x silicon, DMA\_DACK[0:1] must be 0b10 during POR configuration; for rev. 1.x silicon, the pin values during POR configuration are don't care.

- 107.For rev. 2.x silicon, DMA\_DACK[0:1] must be 0b01 during POR configuration; for rev. 1.x silicon, the pin values during POR configuration are don't care.

- 108.For rev. 2.x silicon, DMA\_DACK[0:1] must be 0b11 during POR configuration; for rev. 1.x silicon, the pin values during POR configuration are don't care.

- 109. This is a test signal for factory use only and must be pulled down (100  $\Omega$  1 k $\Omega$ ) to GND for normal machine operation.

- 110. These pins must be pulled high to  $OV_{DD}$  through 2–10 k $\Omega$  resistors.

- 111.If these pins are not used as GPINn (general-purpose input), they must be pulled low (to GND) or high (to OV<sub>DD</sub>) through 2–10 k $\Omega$  resistors.

- 112. This pin must not be pulled down during POR configuration.

- 113. These should be pulled low or high to  ${\rm OV_{DD}}$  through 2–10 k $\Omega$  resistors.

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

## **Package Description**

Table 73. MPC8545E Pinout Listing (continued)

| Signal                 | Package Pin Number                                                                                                                                                                                                                                                                             | Pin Type | Power<br>Supply  | Notes    |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

| PCI1_FRAME             | AE11                                                                                                                                                                                                                                                                                           | I/O      | $OV_{DD}$        | 2        |

| PCI1_IDSEL             | AG9                                                                                                                                                                                                                                                                                            | I        | $OV_{DD}$        | _        |

| PCI1_REQ64/PCI2_FRAME  | AF14                                                                                                                                                                                                                                                                                           | I/O      | $OV_{DD}$        | 2, 5, 10 |

| PCI1_ACK64/PCI2_DEVSEL | V15                                                                                                                                                                                                                                                                                            | I/O      | $OV_{DD}$        | 2        |

| PCI2_CLK               | AE28                                                                                                                                                                                                                                                                                           | I        | $OV_{DD}$        | 39       |

| PCI2_IRDY              | AD26                                                                                                                                                                                                                                                                                           | I/O      | $OV_{DD}$        | 2        |

| PCI2_PERR              | AD25                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_GNT[4:1]          | AE26, AG24, AF25, AE25                                                                                                                                                                                                                                                                         | 0        | $OV_{DD}$        | 5, 9, 35 |

| PCI2_GNT0              | AG25                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | _        |

| PCI2_SERR              | AD24                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2,4      |

| PCI2_STOP              | AF24                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_TRDY              | AD27                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_REQ[4:1]          | AD28, AE27, W17, AF26                                                                                                                                                                                                                                                                          | I        | OV <sub>DD</sub> | _        |

| PCI2_REQ0              | AH25                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | _        |

|                        | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                     |          | 1                |          |

| MDQ[0:63]              | L18, J18, K14, L13, L19, M18, L15, L14, A17, B17, A13, B12, C18, B18, B13, A12, H18, F18, J14, F15, K19, J19, H16, K15, D17, G16, K13, D14, D18, F17, F14, E14, A7, A6, D5, A4, C8, D7, B5, B4, A2, B1, D1, E4, A3, B2, D2, E3, F3, G4, J5, K5, F6, G5, J6, K4, J1, K2, M5, M3, J3, J2, L1, M6 | I/O      | GV <sub>DD</sub> | _        |

| MECC[0:7]              | H13, F13, F11, C11, J13, G13, D12, M12                                                                                                                                                                                                                                                         | I/O      | GV <sub>DD</sub> | <u> </u> |

| MDM[0:8]               | M17, C16, K17, E16, B6, C4, H4, K1, E13                                                                                                                                                                                                                                                        | 0        | GV <sub>DD</sub> | _        |

| MDQS[0:8]              | M15, A16, G17, G14, A5, D3, H1, L2, C13                                                                                                                                                                                                                                                        | I/O      | GV <sub>DD</sub> | _        |

| MDQS[0:8]              | L17, B16, J16, H14, C6, C2, H3, L4, D13                                                                                                                                                                                                                                                        | I/O      | GV <sub>DD</sub> | _        |

| MA[0:15]               | A8, F9, D9, B9, A9, L10, M10, H10, K10, G10,<br>B8, E10, B10, G6, A10, L11                                                                                                                                                                                                                     | 0        | GV <sub>DD</sub> | _        |

| MBA[0:2]               | F7, J7, M11                                                                                                                                                                                                                                                                                    | 0        | GV <sub>DD</sub> | <u> </u> |

| MWE                    | E7                                                                                                                                                                                                                                                                                             | 0        | GV <sub>DD</sub> | _        |

| MCAS                   | H7                                                                                                                                                                                                                                                                                             | 0        | GV <sub>DD</sub> | _        |

| MRAS                   | L8                                                                                                                                                                                                                                                                                             | 0        | GV <sub>DD</sub> | T —      |

| MCKE[0:3]              | F10, C10, J11, H11                                                                                                                                                                                                                                                                             | 0        | GV <sub>DD</sub> | 11       |

| MCS[0:3]               | K8, J8, G8, F8                                                                                                                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | 1 —      |

| MCK[0:5]               | H9, B15, G2, M9, A14, F1                                                                                                                                                                                                                                                                       | 0        | GV <sub>DD</sub> | <u> </u> |

| MCK[0:5]               | J9, A15, G1, L9, B14, F2                                                                                                                                                                                                                                                                       | 0        | GV <sub>DD</sub> | 1 —      |

| MODT[0:3]              | E6, K6, L7, M7                                                                                                                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | 1 —      |

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

Table 74. MPC8543E Pinout Listing (continued)

| Signal         | Package Pin Number | Pin Type                                       | Power<br>Supply       | Notes |  |

|----------------|--------------------|------------------------------------------------|-----------------------|-------|--|

| SENSEVSS       | M16                | _                                              | _                     | 13    |  |

| Analog Signals |                    |                                                |                       |       |  |

| MVREF          | A18                | I<br>Reference<br>voltage<br>signal for<br>DDR | MVREF                 | _     |  |

| SD_IMP_CAL_RX  | L28                | I                                              | 200 Ω (±1%)<br>to GND | _     |  |

| SD_IMP_CAL_TX  | AB26               | I                                              | 100 Ω (±1%)<br>to GND | _     |  |

| SD_PLL_TPA     | U26                | 0                                              | AVDD_SRDS             | 24    |  |

**Note:** All note references in this table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 77. Processor Core Clocking Specifications (MPC8543E)

| Characteristic                | Maximum Processor Core Frequency |     |          |      |      |       |

|-------------------------------|----------------------------------|-----|----------|------|------|-------|

|                               | 800 MHz                          |     | 1000 MHz |      | Unit | Notes |

|                               | Min                              | Max | Min      | Max  |      |       |

| e500 core processor frequency | 800                              | 800 | 800      | 1000 | MHz  | 1, 2  |

#### Notes:

- Caution: The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

- 2.) The minimum e500 core frequency is based on the minimum platform frequency of 333 MHz.

Table 78. Memory Bus Clocking Specifications (MPC8548E and MPC8547E)

|                        | Maximum Process      | Unit | Notes |      |

|------------------------|----------------------|------|-------|------|

| Characteristic         | 1000, 1200, 1333 MHz |      |       |      |

|                        | Min                  | Max  |       |      |

| Memory bus clock speed | 166                  | 266  | MHz   | 1, 2 |

#### Notes:

- Caution: The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

- 2. The memory bus speed is half of the DDR/DDR2 data rate, hence, half of the platform clock frequency.

Table 79. Memory Bus Clocking Specifications (MPC8545E)

| Characteristic         | Maximum Processor Core Frequency<br>800, 1000, 1200 MHz |     | Unit | Notes |

|------------------------|---------------------------------------------------------|-----|------|-------|

|                        | Min                                                     | Max |      |       |

| Memory bus clock speed | 166                                                     | 200 | MHz  | 1, 2  |

#### Notes:

- Caution: The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

- 2. The memory bus speed is half of the DDR/DDR2 data rate, hence, half of the platform clock frequency.

## 22.10 Guidelines for High-Speed Interface Termination

This section provides the guidelines for high-speed interface termination when the SerDes interface is entirely unused and when it is partly unused.

## 22.10.1 SerDes Interface Entirely Unused

If the high-speed SerDes interface is not used at all, the unused pin must be terminated as described in this section.

The following pins must be left unconnected (float):

- SD\_TX[7:0]

- SD\_TX[7:0]

- Reserved pins T22, T23, M20, M21

The following pins must be connected to GND:

- SD\_RX[7:0]

- SD RX[7:0]

- SD\_REF\_CLK

- SD REF CLK

#### NOTE

It is recommended to power down the unused lane through SRDSCR1[0:7] register (offset =  $0xE_0F08$ ) (This prevents the oscillations and holds the receiver output in a fixed state.) that maps to SERDES lane 0 to lane 7 accordingly.

Pins V28 and M26 must be tied to  $XV_{DD}$ . Pins V27 and M25 must be tied to GND through a 300- $\Omega$  resistor.

In Rev 2.0 silicon, POR configuration pin cfg\_srds\_en on TSEC4\_TXD[2]/TSEC3\_TXD[6] can be used to power down SerDes block.

## 22.10.2 SerDes Interface Partly Unused

If only part of the high-speed SerDes interface pins are used, the remaining high-speed serial I/O pins must be terminated as described in this section.

The following pins must be left unconnected (float) if not used:

- SD\_TX[7:0]

- $\overline{SD}TX[7:0]$

- Reserved pins: T22, T23, M20, M21

The following pins must be connected to GND if not used:

- SD RX[7:0]

- SD RX[7:0]

- SD\_REF\_CLK

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9