Welcome to **E-XFL.COM**

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

# **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                                                                      |                                                                          |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Product Status                                                               | Obsolete                                                                 |

| Floduct Status                                                               | Obsolete                                                                 |

| Core Processor                                                               | PowerPC e500                                                             |

| Number of Cores/Bus Width                                                    | 1 Core, 32-Bit                                                           |

| Speed                                                                        | 1.0GHz                                                                   |

| Co-Processors/DSP                                                            | Signal Processing; SPE, Security; SEC                                    |

| RAM Controllers                                                              | DDR, DDR2, SDRAM                                                         |

| Graphics Acceleration                                                        | No                                                                       |

| Display & Interface Controllers                                              | -                                                                        |

| Ethernet                                                                     | 10/100/1000Mbps (4)                                                      |

| SATA                                                                         |                                                                          |

| JAIA                                                                         | -                                                                        |

| USB                                                                          | <u> </u>                                                                 |

|                                                                              | -<br>1.8V, 2.5V, 3.3V                                                    |

| USB                                                                          | 1.8V, 2.5V, 3.3V<br>0°C ~ 105°C (TA)                                     |

| USB<br>Voltage - I/O                                                         |                                                                          |

| USB  Voltage - I/O  Operating Temperature                                    | 0°C ~ 105°C (TA)                                                         |

| USB  Voltage - I/O  Operating Temperature  Security Features                 | 0°C ~ 105°C (TA)  Cryptography, Random Number Generator                  |

| USB  Voltage - I/O  Operating Temperature  Security Features  Package / Case | 0°C ~ 105°C (TA)  Cryptography, Random Number Generator  783-BBGA, FCBGA |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Overview

- Up to 32 simultaneous open pages for DDR2

- Contiguous or discontiguous memory mapping

- Read-modify-write support for RapidIO atomic increment, decrement, set, and clear transactions

- Sleep mode support for self-refresh SDRAM

- On-die termination support when using DDR2

- Supports auto refreshing

- On-the-fly power management using CKE signal

- Registered DIMM support

- Fast memory access via JTAG port

- 2.5-V SSTL\_2 compatible I/O (1.8-V SSTL\_1.8 for DDR2)

- Support for battery-backed main memory

- Programmable interrupt controller (PIC)

- Programming model is compliant with the OpenPIC architecture.

- Supports 16 programmable interrupt and processor task priority levels

- Supports 12 discrete external interrupts

- Supports 4 message interrupts with 32-bit messages

- Supports connection of an external interrupt controller such as the 8259 programmable interrupt controller

- Four global high-resolution timers/counters that can generate interrupts

- Supports a variety of other internal interrupt sources

- Supports fully nested interrupt delivery

- Interrupts can be routed to external pin for external processing.

- Interrupts can be routed to the e500 core's standard or critical interrupt inputs.

- Interrupt summary registers allow fast identification of interrupt source.

- Integrated security engine (SEC) optimized to process all the algorithms associated with IPSec, IKE, WTLS/WAP, SSL/TLS, and 3GPP

- Four crypto-channels, each supporting multi-command descriptor chains

- Dynamic assignment of crypto-execution units via an integrated controller

- Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

- PKEU—public key execution unit

- RSA and Diffie-Hellman; programmable field size up to 2048 bits

- Elliptic curve cryptography with F<sub>2</sub>m and F(p) modes and programmable field size up to 511 bits

- DEU—Data Encryption Standard execution unit

- DES, 3DES

- Two key (K1, K2) or three key (K1, K2, K3)

- ECB and CBC modes for both DES and 3DES

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

- VRRP and HSRP support for seamless router fail-over

- Up to 16 exact-match MAC addresses supported

- Broadcast address (accept/reject)

- Hash table match on up to 512 multicast addresses

- Promiscuous mode

- Buffer descriptors backward compatible with MPC8260 and MPC860T 10/100 Ethernet programming models

- RMON statistics support

- 10-Kbyte internal transmit and 2-Kbyte receive FIFOs

- MII management interface for control and status

- Ability to force allocation of header information and buffer descriptors into L2 cache

# • OCeaN switch fabric

- Full crossbar packet switch

- Reorders packets from a source based on priorities

- Reorders packets to bypass blocked packets

- Implements starvation avoidance algorithms

- Supports packets with payloads of up to 256 bytes

# • Integrated DMA controller

- Four-channel controller

- All channels accessible by both the local and remote masters

- Extended DMA functions (advanced chaining and striding capability)

- Support for scatter and gather transfers

- Misaligned transfer capability

- Interrupt on completed segment, link, list, and error

- Supports transfers to or from any local memory or I/O port

- Selectable hardware-enforced coherency (snoop/no snoop)

- Ability to start and flow control each DMA channel from external 3-pin interface

- Ability to launch DMA from single write transaction

### • Two PCI/PCI-X controllers

- PCI 2.2 and PCI-X 1.0 compatible

- One 32-/64-bit PCI/PCI-X port with support for speeds of up to 133 MHz (maximum PCI-X frequency in synchronous mode is 110 MHz)

- One 32-bit PCI port with support for speeds from 16 to 66 MHz (available when the other port is in 32-bit mode)

- Host and agent mode support

- 64-bit dual address cycle (DAC) support

- PCI-X supports multiple split transactions

- Supports PCI-to-memory and memory-to-PCI streaming

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

### **Local Bus**

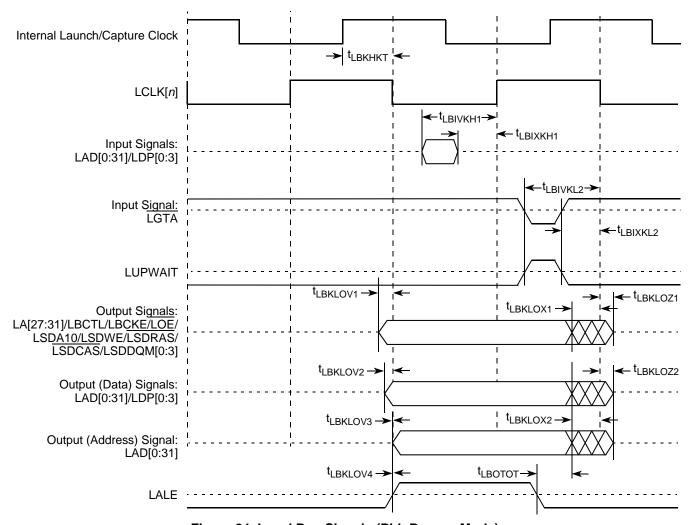

Figure 24. Local Bus Signals (PLL Bypass Mode)

# **NOTE**

In PLL bypass mode, LCLK[n] is the inverted version of the internal clock with the delay of  $t_{LBKHKT}$ . In this mode, signals are launched at the rising edge of the internal clock and are captured at falling edge of the internal clock with the exception of  $\overline{LGTA}/LUPWAIT$  (which is captured on the rising edge of the internal clock).

### GPOUT/GPIN 14

This section describes the DC and AC electrical specifications for the GP<sub>OUT</sub>/GP<sub>IN</sub> bus of the device.

#### 14.1 **GP<sub>OUT</sub>/GP<sub>IN</sub> Electrical Characteristics**

Table 47 and Table 48 provide the DC electrical characteristics for the GP<sub>OUT</sub> interface.

Table 47. GP<sub>OUT</sub> DC Electrical Characteristics (3.3 V DC)

| Parameter                                                                      | Symbol           | Min                    | Max  | Unit |

|--------------------------------------------------------------------------------|------------------|------------------------|------|------|

| Supply voltage 3.3 V                                                           | BV <sub>DD</sub> | 3.13                   | 3.47 | V    |

| High-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = -2 mA) | V <sub>OH</sub>  | BV <sub>DD</sub> – 0.2 | _    | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)   | V <sub>OL</sub>  | _                      | 0.2  | V    |

Table 48. GP<sub>OUT</sub> DC Electrical Characteristics (2.5 V DC)

| Parameter                                                                   | Symbol           | Min       | Max                    | Unit        |

|-----------------------------------------------------------------------------|------------------|-----------|------------------------|-------------|

| Supply voltage 2.5 V                                                        | BV <sub>DD</sub> | 2.37      | 2.63                   | V           |

| High-level output voltage (BV <sub>DD</sub> = min, I <sub>OH</sub> = -1 mA) | V <sub>OH</sub>  | 2.0       | BV <sub>DD</sub> + 0.3 | <b>&gt;</b> |

| Low-level output voltage (BV <sub>DD</sub> min, I <sub>OL</sub> = 1 mA)     | V <sub>OL</sub>  | GND – 0.3 | 0.4                    | V           |

Table 49 and Table 50 provide the DC electrical characteristics for the GP<sub>IN</sub> interface.

Table 49. GP<sub>IN</sub> DC Electrical Characteristics (3.3 V DC)

| Parameter                                                                                   | Symbol           | Min  | Max                    | Unit |

|---------------------------------------------------------------------------------------------|------------------|------|------------------------|------|

| Supply voltage 3.3 V                                                                        | BV <sub>DD</sub> | 3.13 | 3.47                   | V    |

| High-level input voltage                                                                    | V <sub>IH</sub>  | 2    | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                                     | $V_{IL}$         | -0.3 | 0.8                    | V    |

| Input current (BV <sub>IN</sub> <sup>1</sup> = 0 V or BV <sub>IN</sub> = BV <sub>DD</sub> ) | I <sub>IN</sub>  |      | ±5                     | μΑ   |

# Note:

1. The symbol  ${\rm BV_{IN}}$ , in this case, represents the  ${\rm BV_{IN}}$  symbol referenced in Table 1.

### **High-Speed Serial Interfaces (HSSI)** 16

The device features one Serializer/Deserializer (SerDes) interface to be used for high-speed serial interconnect applications. The SerDes interface can be used for PCI Express and/or serial RapidIO data transfers.

This section describes the common portion of SerDes DC electrical specifications, which is the DC requirement for SerDes reference clocks. The SerDes data lane's transmitter and receiver reference circuits are also shown.

#### 16.1 **Signal Terms Definition**

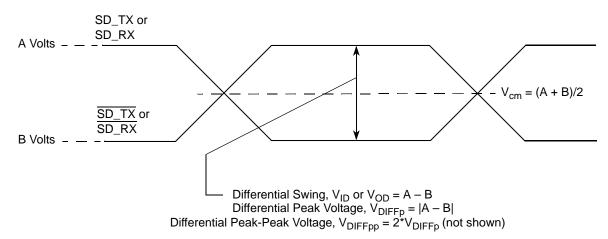

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

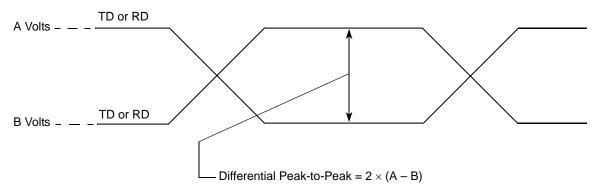

Figure 38 shows how the signals are defined. For illustration purpose, only one SerDes lane is used for the description. The figure shows a waveform for either a transmitter output (SD TX and SD TX) or a receiver input (SD\_RX and  $\overline{SD_RX}$ ). Each signal swings between A volts and B volts where A > B.

Using this waveform, the definitions are as follows. To simplify the illustration, the following definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signaling environment.

- Single-ended swing The transmitter output signals and the receiver input signals SD\_TX, SD\_TX, SD\_RX and SD\_RX each have a peak-to-peak swing of A - B volts. This is also referred as each signal wire's single-ended swing.

- Differential output voltage, V<sub>OD</sub> (or differential output swing): The differential output voltage (or swing) of the transmitter, V<sub>OD</sub>, is defined as the difference of the two complimentary output voltages:  $V_{SD-TX} - V_{\overline{SD-TX}}$ . The  $V_{OD}$  value can be either positive or negative.

- Differential input voltage, V<sub>ID</sub> (or differential input swing): The differential input voltage (or swing) of the receiver, V<sub>ID</sub>, is defined as the difference of the two complimentary input voltages:  $V_{SD-RX} - V_{\overline{SD-RX}}$ . The  $V_{ID}$  value can be either positive or negative.

- Differential peak voltage, V<sub>DIFFp</sub> The peak value of the differential transmitter output signal or the differential receiver input signal is defined as differential peak voltage,  $V_{DIFFp} = |A - B|$  volts.

- Differential peak-to-peak, V<sub>DIFFp-p</sub> Because the differential output signal of the transmitter and the differential input signal of the receiver each range from A - B to -(A - B) volts, the peak-to-peak value of the differential transmitter output signal or the differential receiver input signal is defined as differential peak-to-peak voltage,  $V_{DIFFp-p} = 2 \times V_{DIFFp} = 2 \times |(A-B)|$  volts, which is twice of differential swing in amplitude, or twice of the differential peak. For example, the output differential peak-to-peak voltage can also be calculated as  $V_{TX-DIFFp-p} = 2 \times |V_{OD}|$ .

- Common mode voltage, V<sub>cm</sub> The common mode voltage is equal to one half of the sum of the voltages between each conductor

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9 Freescale Semiconductor 65 of a balanced interchange circuit and ground. In this example, for SerDes output,  $V_{cm\_out} = V_{SD\_TX} + V_{\overline{SD\_TX}} = (A + B)/2$ , which is the arithmetic mean of the two complimentary output voltages within a differential pair. In a system, the common mode voltage may often differ from one component's output to the other's input. Sometimes, it may be even different between the receiver input and driver output circuits within the same component. It is also referred to as the DC offset.

Figure 38. Differential Voltage Definitions for Transmitter or Receiver

To illustrate these definitions using real values, consider the case of a CML (current mode logic) transmitter that has a common mode voltage of 2.25 V and each of its outputs, TD and  $\overline{\text{TD}}$ , has a swing that goes between 2.5 and 2.0 V. Using these values, the peak-to-peak voltage swing of each signal (TD or  $\overline{\text{TD}}$ ) is 500 mVp-p, which is referred as the single-ended swing for each signal. In this example, since the differential signaling environment is fully symmetrical, the transmitter output's differential swing (V<sub>OD</sub>) has the same amplitude as each signal's single-ended swing. The differential output signal ranges between 500 and –500 mV, in other words, V<sub>OD</sub> is 500 mV in one phase and –500 mV in the other phase. The peak differential voltage (V<sub>DIFFp-D</sub>) is 500 mV. The peak-to-peak differential voltage (V<sub>DIFFp-D</sub>) is 1000 mVp-p.

# 16.2 SerDes Reference Clocks

The SerDes reference clock inputs are applied to an internal PLL whose output creates the clock used by the corresponding SerDes lanes. The SerDes reference clocks inputs are SD\_REF\_CLK and SD\_REF\_CLK for PCI Express and serial RapidIO.

The following sections describe the SerDes reference clock requirements and some application information.

# 16.2.1 SerDes Reference Clock Receiver Characteristics

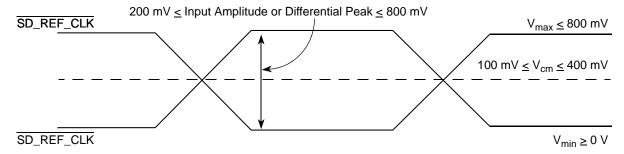

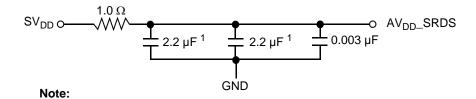

Figure 39 shows a receiver reference diagram of the SerDes reference clocks.

- The supply voltage requirements for XV<sub>DD SRDS2</sub> are specified in Table 1 and Table 2.

- SerDes Reference clock receiver reference circuit structure:

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

### **High-Speed Serial Interfaces (HSSI)**

- The input amplitude of the differential clock must be between 400 and 1600 mV differential peak-peak (or between 200 and 800 mV differential peak). In other words, each signal wire of the differential pair must have a single-ended swing less than 800 mV and greater than 200 mV. This requirement is the same for both external DC- or AC-coupled connection.

- For external DC-coupled connection, as described in Section 16.2.1, "SerDes Reference Clock Receiver Characteristics," the maximum average current requirements sets the requirement for average voltage (common mode voltage) to be between 100 and 400 mV. Figure 40 shows the SerDes reference clock input requirement for DC-coupled connection scheme.

- For external AC-coupled connection, there is no common mode voltage requirement for the clock driver. Since the external AC-coupling capacitor blocks the DC level, the clock driver and the SerDes reference clock receiver operate in different command mode voltages. The SerDes reference clock receiver in this connection scheme has its common mode voltage set to SGND\_SRDSn. Each signal wire of the differential inputs is allowed to swing below and above the command mode voltage (SGND\_SRDSn). Figure 41 shows the SerDes reference clock input requirement for AC-coupled connection scheme.

### • Single-ended mode

- The reference clock can also be single-ended. The SD\_REF\_CLK input amplitude (single-ended swing) must be between 400 and 800 mV peak-to-peak (from V<sub>min</sub> to V<sub>max</sub>) with SD\_REF\_CLK either left unconnected or tied to ground.

- The SD\_REF\_CLK input average voltage must be between 200 and 400 mV. Figure 42 shows the SerDes reference clock input requirement for single-ended signaling mode.

- To meet the input amplitude requirement, the reference clock inputs might need to be DC- or AC-coupled externally. For the best noise performance, the reference of the clock could be DC- or AC-coupled into the unused phase (SD\_REF\_CLK) through the same source impedance as the clock input (SD\_REF\_CLK) in use.

Figure 40. Differential Reference Clock Input DC Requirements (External DC-Coupled)

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

# **18.3 Signal Definitions**

LP-serial links use differential signaling. This section defines terms used in the description and specification of differential signals. Figure 51 shows how the signals are defined. The figures show waveforms for either a transmitter output (TD and  $\overline{\text{TD}}$ ) or a receiver input (RD and  $\overline{\text{RD}}$ ). Each signal swings between A volts and B volts where A > B. Using these waveforms, the definitions are as follows:

- 1. The transmitter output signals and the receiver input signals TD, TD, RD, and RD each have a peak-to-peak swing of A B volts.

- 2. The differential output signal of the transmitter,  $V_{OD}$ , is defined as  $V_{TD} V_{\overline{TD}}$ .

- 3. The differential input signal of the receiver,  $V_{ID}$ , is defined as  $V_{RD} V_{\overline{RD}}$ .

- 4. The differential output signal of the transmitter and the differential input signal of the receiver each range from A B to -(A B) volts.

- 5. The peak value of the differential transmitter output signal and the differential receiver input signal is A B volts.

- 6. The peak-to-peak value of the differential transmitter output signal and the differential receiver input signal is  $2 \times (A B)$  volts.

Figure 51. Differential Peak-Peak Voltage of Transmitter or Receiver

To illustrate these definitions using real values, consider the case of a CML (current mode logic) transmitter that has a common mode voltage of 2.25 V and each of its outputs, TD and  $\overline{\text{TD}}$ , has a swing that goes between 2.5 and 2.0 V. Using these values, the peak-to-peak voltage swing of the signals TD and  $\overline{\text{TD}}$  is 500 mVp-p. The differential output signal ranges between 500 and -500 mV. The peak differential voltage is 500 mV. The peak-to-peak differential voltage is 1000 mVp-p.

# 18.4 Equalization

With the use of high-speed serial links, the interconnect media causes degradation of the signal at the receiver. Effects such as inter-symbol interference (ISI) or data dependent jitter are produced. This loss can be large enough to degrade the eye opening at the receiver beyond what is allowed in the specification. To negate a portion of these effects, equalization can be used. The most common equalization techniques that can be used are:

- A passive high pass filter network placed at the receiver. This is often referred to as passive equalization.

- The use of active circuits in the receiver. This is often referred to as adaptive equalization.

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

# 18.5 Explanatory Note on Transmitter and Receiver Specifications

AC electrical specifications are given for transmitter and receiver. Long- and short-run interfaces at three baud rates (a total of six cases) are described.

The parameters for the AC electrical specifications are guided by the XAUI electrical interface specified in Clause 47 of IEEE 802.3ae-2002.

XAUI has similar application goals to Serial RapidIO, as described in Section 8.1. The goal of this standard is that electrical designs for Serial RapidIO can reuse electrical designs for XAUI, suitably modified for applications at the baud intervals and reaches described herein.

# 18.6 Transmitter Specifications

LP-serial transmitter electrical and timing specifications are stated in the text and tables of this section.

The differential return loss, S11, of the transmitter in each case shall be better than:

- -10 dB for (baud frequency)/10 < Freq(f) < 625 MHz, and

- $-10 \text{ dB} + 10 \log(f/625 \text{ MHz}) \text{ dB for } 625 \text{ MHz} \leq \text{Freq}(f) \leq \text{baud frequency}$

The reference impedance for the differential return loss measurements is  $100-\Omega$  resistive. Differential return loss includes contributions from on-chip circuitry, chip packaging, and any off-chip components related to the driver. The output impedance requirement applies to all valid output levels.

It is recommended that the 20%-80% rise/fall time of the transmitter, as measured at the transmitter output, in each case have a minimum value 60 ps.

It is recommended that the timing skew at the output of an LP-serial transmitter between the two signals that comprise a differential pair not exceed 25 ps at 1.25 GB, 20 ps at 2.50 GB, and 15 ps at 3.125 GB.

| Characteristic              | Symbol          | Range   |      | Unit   | Notes                                                                      |  |

|-----------------------------|-----------------|---------|------|--------|----------------------------------------------------------------------------|--|

| Citalacteristic             | Symbol          | Min Max |      |        | Notes                                                                      |  |

| Output voltage              | Vo              | -0.40   | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |  |

| Differential output voltage | $V_{DIFFPP}$    | 500     | 1000 | mV p-p | _                                                                          |  |

| Deterministic jitter        | $J_{D}$         | _       | 0.17 | UI p-p | _                                                                          |  |

| Total jitter                | J <sub>T</sub>  | _       | 0.35 | UI p-p | _                                                                          |  |

| Multiple output skew        | S <sub>MO</sub> | _       | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |  |

| Unit Interval               | UI              | 800     | 800  | ps     | ±100 ppm                                                                   |  |

Table 59. Short Run Transmitter AC Timing Specifications—1.25 GBaud

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

# 19.3 Pinout Listings

# **NOTE**

The DMA\_DACK[0:1] and TEST\_SEL/TEST\_SEL pins must be set to a proper state during POR configuration. See the pinlist table of the individual device for more details.

For MPC8548/47/45, GPIOs are still available on PCI1\_AD[63:32]/PC2\_AD[31:0] pins if they are not used for PCI functionality.

For MPC8545/43, eTSEC does not support 16 bit FIFO mode.

Table 71 provides the pinout listing for the MPC8548E 783 FC-PBGA package.

Table 71. MPC8548E Pinout Listing

| Signal                        | Package Pin Number                                                                                                                                                                                     | Pin Type | Power<br>Supply  | Notes    |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

|                               | PCI1 and PCI2 (One 64-Bit or Two 32-Bit)                                                                                                                                                               |          |                  |          |

| PCI1_AD[63:32]/PCI2_AD[31:0]  | AB14, AC15, AA15, Y16, W16, AB16, AC16,<br>AA16, AE17, AA18, W18, AC17, AD16, AE16,<br>Y17, AC18, AB18, AA19, AB19, AB21, AA20,<br>AC20, AB20, AB22, AC22, AD21, AB23, AF23,<br>AD23, AE23, AC23, AC24 | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_AD[31:0]                 | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15          | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_C_BE[7:4]/PCI2_C_BE[3:0] | AF15, AD14, AE15, AD15                                                                                                                                                                                 | I/O      | $OV_{DD}$        | 17       |

| PCI1_C_BE[3:0]                | AF9, AD11, Y12, Y13                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_PAR64/PCI2_PAR           | W15                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> |          |

| PCI1_GNT[4:1]                 | AG6, AE6, AF5, AH5                                                                                                                                                                                     | 0        | OV <sub>DD</sub> | 5, 9, 35 |

| PCI1_GNT0                     | AG5                                                                                                                                                                                                    | I/O      | $OV_{DD}$        | _        |

| PCI1_IRDY                     | AF11                                                                                                                                                                                                   | I/O      | $OV_{DD}$        | 2        |

| PCI1_PAR                      | AD12                                                                                                                                                                                                   | I/O      | $OV_{DD}$        | _        |

| PCI1_PERR                     | AC12                                                                                                                                                                                                   | I/O      | $OV_{DD}$        | 2        |

| PCI1_SERR                     | V13                                                                                                                                                                                                    | I/O      | $OV_{DD}$        | 2, 4     |

| PCI1_STOP                     | W12                                                                                                                                                                                                    | I/O      | $OV_{DD}$        | 2        |

| PCI1_TRDY                     | AG11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

# **Package Description**

Table 71. MPC8548E Pinout Listing (continued)

| Signal                 | Package Pin Number                                                                                                                                                                                                                                                                             | Pin Type | Power<br>Supply  | Notes    |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

| PCI1_REQ[4:1]          | AH2, AG4, AG3, AH4                                                                                                                                                                                                                                                                             | I        | OV <sub>DD</sub> | _        |

|                        |                                                                                                                                                                                                                                                                                                |          |                  | _        |

|                        |                                                                                                                                                                                                                                                                                                |          |                  | _        |

|                        |                                                                                                                                                                                                                                                                                                |          |                  | _        |

|                        |                                                                                                                                                                                                                                                                                                |          |                  | _        |

| PCI1_REQ0              | AH3                                                                                                                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | _        |

| PCI1_CLK               | AH26                                                                                                                                                                                                                                                                                           | ı        | OV <sub>DD</sub> | 39       |

| PCI1_DEVSEL            | AH11                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_FRAME             | AE11                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_IDSEL             | AG9                                                                                                                                                                                                                                                                                            | I        | OV <sub>DD</sub> | _        |

| PCI1_REQ64/PCI2_FRAME  | AF14                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2, 5, 10 |

| PCI1_ACK64/PCI2_DEVSEL | V15                                                                                                                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_CLK               | AE28                                                                                                                                                                                                                                                                                           | I        | OV <sub>DD</sub> | 39       |

| PCI2_IRDY              | AD26                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_PERR              | AD25                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_GNT[4:1]          | AE26, AG24, AF25, AE25                                                                                                                                                                                                                                                                         | 0        | OV <sub>DD</sub> | 5, 9, 35 |

| PCI2_GNT0              | AG25                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | _        |

| PCI2_SERR              | AD24                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2, 4     |

| PCI2_STOP              | AF24                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_TRDY              | AD27                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_REQ[4:1]          | AD28, AE27, W17, AF26                                                                                                                                                                                                                                                                          | l        | OV <sub>DD</sub> | _        |

| PCI2_REQ0              | AH25                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | _        |

|                        | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                     |          |                  | - I      |

| MDQ[0:63]              | L18, J18, K14, L13, L19, M18, L15, L14, A17, B17, A13, B12, C18, B18, B13, A12, H18, F18, J14, F15, K19, J19, H16, K15, D17, G16, K13, D14, D18, F17, F14, E14, A7, A6, D5, A4, C8, D7, B5, B4, A2, B1, D1, E4, A3, B2, D2, E3, F3, G4, J5, K5, F6, G5, J6, K4, J1, K2, M5, M3, J3, J2, L1, M6 | I/O      | GV <sub>DD</sub> | _        |

| MECC[0:7]              | H13, F13, F11, C11, J13, G13, D12, M12                                                                                                                                                                                                                                                         | I/O      | GV <sub>DD</sub> | _        |

| MDM[0:8]               | M17, C16, K17, E16, B6, C4, H4, K1, E13                                                                                                                                                                                                                                                        | 0        | GV <sub>DD</sub> | _        |

| MDQS[0:8]              | M15, A16, G17, G14, A5, D3, H1, L2, C13                                                                                                                                                                                                                                                        | I/O      | GV <sub>DD</sub> | _        |

| MDQS[0:8]              | L17, B16, J16, H14, C6, C2, H3, L4, D13                                                                                                                                                                                                                                                        | I/O      | GV <sub>DD</sub> | _        |

| MA[0:15]               | A8, F9, D9, B9, A9, L10, M10, H10, K10, G10,<br>B8, E10, B10, G6, A10, L11                                                                                                                                                                                                                     | 0        | GV <sub>DD</sub> | _        |

| MBA[0:2]               | F7, J7, M11                                                                                                                                                                                                                                                                                    | 0        | GV <sub>DD</sub> | _        |

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

Table 71. MPC8548E Pinout Listing (continued)

| Signal           | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Pin Type                                           | Power<br>Supply  | Notes        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------|--------------|

|                  | Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                    |                  | •            |

| RTC              | AF16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                  | OV <sub>DD</sub> | _            |

| SYSCLK           | AH17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                  | OV <sub>DD</sub> | <u> </u>     |

|                  | JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                    |                  | •            |

| TCK              | AG28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                  | $OV_{DD}$        | _            |

| TDI              | AH28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                  | $OV_{DD}$        | 12           |

| TDO              | AF28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                  | OV <sub>DD</sub> | <u> </u>     |

| TMS              | AH27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                  | $OV_{DD}$        | 12           |

| TRST             | AH23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                  | OV <sub>DD</sub> | 12           |

|                  | DFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                    |                  | •            |

| L1_TSTCLK        | AC25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Ţ                                                  | $OV_{DD}$        | 25           |

| L2_TSTCLK        | AE22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Ţ                                                  | $OV_{DD}$        | 25           |

| LSSD_MODE        | AH20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                  | $OV_{DD}$        | 25           |

| TEST_SEL         | AH14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                  | $OV_{DD}$        | 25           |

|                  | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                    |                  | •            |

| THERM0           | AG1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                  | _                | 14           |

| THERM1           | AH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                  | _                | 14           |

|                  | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                    |                  | •            |

| ASLEEP           | AH18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                  | OV <sub>DD</sub> | 9, 19,<br>29 |

|                  | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    |                  |              |

| GND              | A11, B7, B24, C1, C3, C5, C12, C15, C26, D8, D11, D16, D20, D22, E1, E5, E9, E12, E15, E17, F4, F26, G12, G15, G18, G21, G24, H2, H6, H8, H28, J4, J12, J15, J17, J27, K7, K9, K11, K27, L3, L5, L12, L16, N11, N13, N15, N17, N19, P4, P9, P12, P14, P16, P18, R11, R13, R15, R17, R19, T4, T12, T14, T16, T18, U8, U11, U13, U15, U17, U19, V4, V12, V18, W6, W19, Y4, Y9, Y11, Y19, AA6, AA14, AA17, AA22, AA23, AB4, AC2, AC11, AC19, AC26, AD5, AD9, AD22, AE3, AE14, AF6, AF10, AF13, AG8, AG27, K28, L24, L26, N24, N27, P25, R28, T24, T26, U24, V25, W28, Y24, Y26, AA24, AA27, AB25, AC28, L21, L23, N22, P20, R23, T21, U22, V20, W23, Y21, U27 |                                                    | _                | _            |

| OV <sub>DD</sub> | V16, W11, W14, Y18, AA13, AA21, AB11,<br>AB17, AB24, AC4, AC9, AC21, AD6, AD13,<br>AD17, AD19, AE10, AE8, AE24, AF4, AF12,<br>AF22, AF27, AG26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Power for PCI<br>and other<br>standards<br>(3.3 V) | OV <sub>DD</sub> |              |

Table 72 provides the pin-out listing for the MPC8547E 783 FC-PBGA package.

# **NOTE**

All note references in the following table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 72. MPC8547E Pinout Listing

| Signal         | Package Pin Number                                                                                                                                                                                     | Pin Type | Power<br>Supply  | Notes    |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

|                | PCI1 (One 64-Bit or One 32-Bit)                                                                                                                                                                        |          |                  | •        |

| PCI1_AD[63:32] | AB14, AC15, AA15, Y16, W16, AB16, AC16,<br>AA16, AE17, AA18, W18, AC17, AD16, AE16,<br>Y17, AC18, AB18, AA19, AB19, AB21, AA20,<br>AC20, AB20, AB22, AC22, AD21, AB23, AF23,<br>AD23, AE23, AC23, AC24 | 1/O      | OV <sub>DD</sub> | 17       |

| PCI1_AD[31:0]  | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15          | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_C_BE[7:4] | AF15, AD14, AE15, AD15                                                                                                                                                                                 | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_C_BE[3:0] | AF9, AD11, Y12, Y13                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_PAR64     | W15                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | _        |

| PCI1_GNT[4:1]  | AG6, AE6, AF5, AH5                                                                                                                                                                                     | 0        | OV <sub>DD</sub> | 5, 9, 35 |

| PCI1_GNT0      | AG5                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | _        |

| PCI1_IRDY      | AF11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_PAR       | AD12                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | _        |

| PCI1_PERR      | AC12                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_SERR      | V13                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2, 4     |

| PCI1_STOP      | W12                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_TRDY      | AG11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_REQ[4:1]  | AH2, AG4, AG3, AH4                                                                                                                                                                                     | I        | OV <sub>DD</sub> | _        |

| PCI1_REQ0      | AH3                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | _        |

| PCI1_CLK       | AH26                                                                                                                                                                                                   | I        | OV <sub>DD</sub> | 39       |

| PCI1_DEVSEL    | AH11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_FRAME     | AE11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_IDSEL     | AG9                                                                                                                                                                                                    | ļ        | OV <sub>DD</sub> | _        |

| PCI1_REQ64     | AF14                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2, 5,10  |

| PCI1_ACK64     | V15                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2        |

| Reserved       | AE28                                                                                                                                                                                                   | _        | _                | 2        |

| Reserved       | AD26                                                                                                                                                                                                   | _        | _                | 2        |

| Reserved       | AD25                                                                                                                                                                                                   | _        | _                | 2        |

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

Table 72. MPC8547E Pinout Listing (continued)

| Signal                        | Package Pin Number                   | Pin Type  | Power<br>Supply  | Notes          |

|-------------------------------|--------------------------------------|-----------|------------------|----------------|

| TSEC2_TX_ER                   | R10                                  | 0         | LV <sub>DD</sub> | 5, 9, 33       |

| Three-S                       | peed Ethernet Controller (Gigabit Et | hernet 3) | •                | 1              |

| TSEC3_TXD[3:0]                | V8, W10, Y10, W7                     | 0         | TV <sub>DD</sub> | 5, 9, 29       |

| TSEC3_RXD[3:0]                | Y1, W3, W5, W4                       | I         | TV <sub>DD</sub> | _              |

| TSEC3_GTX_CLK                 | W8                                   | 0         | TV <sub>DD</sub> | <u> </u>       |

| TSEC3_RX_CLK                  | W2                                   | I         | TV <sub>DD</sub> | _              |

| TSEC3_RX_DV                   | W1                                   | I         | TV <sub>DD</sub> | _              |

| TSEC3_RX_ER                   | Y2                                   | I         | TV <sub>DD</sub> | _              |

| TSEC3_TX_CLK                  | V10                                  | I         | TV <sub>DD</sub> | _              |

| TSEC3_TX_EN                   | V9                                   | 0         | TV <sub>DD</sub> | 30             |

| Three-S                       | peed Ethernet Controller (Gigabit Et | hernet 4) |                  |                |

| TSEC4_TXD[3:0]/TSEC3_TXD[7:4] | AB8, Y7, AA7, Y8                     | 0         | TV <sub>DD</sub> | 1, 5, 9,<br>29 |

| TSEC4_RXD[3:0]/TSEC3_RXD[7:4] | AA1, Y3, AA2, AA4                    | I         | TV <sub>DD</sub> | 1              |

| TSEC4_GTX_CLK                 | AA5                                  | 0         | TV <sub>DD</sub> |                |

| TSEC4_RX_CLK/TSEC3_COL        | Y5                                   | I         | TV <sub>DD</sub> | 1              |

| TSEC4_RX_DV/TSEC3_CRS         | AA3                                  | I/O       | TV <sub>DD</sub> | 1, 31          |

| TSEC4_TX_EN/TSEC3_TX_ER       | AB6                                  | 0         | TV <sub>DD</sub> | 1, 30          |

| ·                             | DUART                                | •         |                  | •              |

| UART_CTS[0:1]                 | AB3, AC5                             | I         | OV <sub>DD</sub> | _              |

| UART_RTS[0:1]                 | AC6, AD7                             | 0         | $OV_{DD}$        | _              |

| UART_SIN[0:1]                 | AB5, AC7                             | I         | OV <sub>DD</sub> | _              |

| UART_SOUT[0:1]                | AB7, AD8                             | 0         | $OV_{DD}$        | _              |

| ·                             | I <sup>2</sup> C Interface           |           |                  |                |

| IIC1_SCL                      | AG22                                 | I/O       | OV <sub>DD</sub> | 4, 27          |

| IIC1_SDA                      | AG21                                 | I/O       | $OV_{DD}$        | 4, 27          |

| IIC2_SCL                      | AG15                                 | I/O       | $OV_{DD}$        | 4, 27          |

| IIC2_SDA                      | AG14                                 | I/O       | $OV_{DD}$        | 4, 27          |

|                               | SerDes                               | •         |                  | •              |

| SD_RX[0:3]                    | M28, N26, P28, R26                   | I         | $XV_{DD}$        | _              |

| SD_RX[0:3]                    | M27, N25, P27, R25                   | I         | $XV_{DD}$        | _              |

| SD_TX[0:3]                    | M22, N20, P22, R20                   | 0         | $XV_{DD}$        |                |

| SD_TX[0:3]                    | M23, N21, P23, R21                   | 0         | $XV_{DD}$        | _              |

| Reserved                      | W26, Y28, AA26, AB28                 |           | _                | 40             |

| Reserved                      | W25, Y27, AA25, AB27                 | _         | _                | 40             |

Table 72. MPC8547E Pinout Listing (continued)

| Signal           | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Pin Type                                                            | Power<br>Supply  | Notes        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------|--------------|

|                  | DFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                     |                  | -            |

| L1_TSTCLK        | AC25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                                   | $OV_{DD}$        | 25           |

| L2_TSTCLK        | AE22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                                   | $OV_{DD}$        | 25           |

| LSSD_MODE        | AH20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                                   | $OV_{DD}$        | 25           |

| TEST_SEL         | AH14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                                   | $OV_{DD}$        | 25           |

|                  | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                     |                  | -            |