#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                       |

|---------------------------------|-----------------------------------------------------------------------|

| Product Status                  | Obsolete                                                              |

| Core Processor                  | PowerPC e500                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 1.0GHz                                                                |

| Co-Processors/DSP               | Signal Processing; SPE                                                |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                      |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (4)                                                   |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                      |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                     |

| Package / Case                  | 783-BBGA, FCBGA                                                       |

| Supplier Device Package         | 783-FCBGA (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8548vuaqg |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Dedicated single data rate SDRAM controller

- Parity support

- Default boot ROM chip select with configurable bus width (8, 16, or 32 bits)

- Four enhanced three-speed Ethernet controllers (eTSECs)

- Three-speed support (10/100/1000 Mbps)

- Four controllers designed to comply with IEEE Std. 802.3<sup>®</sup>, 802.3<sup>u</sup>, 802.3<sup>x</sup>, 802.3<sup>z</sup>, 802.3<sup>ac</sup>, and 802.3<sup>ab</sup>

- Support for various Ethernet physical interfaces:

- 1000 Mbps full-duplex IEEE 802.3 GMII, IEEE 802.3z TBI, RTBI, and RGMII

- 10/100 Mbps full and half-duplex IEEE 802.3 MII, IEEE 802.3 RGMII, and RMII

- Flexible configuration for multiple PHY interface configurations. See Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1Gb Mbps)—GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics," for more information.

- TCP/IP acceleration and QoS features available

- IP v4 and IP v6 header recognition on receive

- IP v4 header checksum verification and generation

- TCP and UDP checksum verification and generation

- Per-packet configurable acceleration

- Recognition of VLAN, stacked (queue in queue) VLAN, IEEE Std 802.2<sup>™</sup>, PPPoE session, MPLS stacks, and ESP/AH IP-security headers

- Supported in all FIFO modes

- Quality of service support:

- Transmission from up to eight physical queues

- Reception to up to eight physical queues

- Full- and half-duplex Ethernet support (1000 Mbps supports only full duplex):

- IEEE 802.3 full-duplex flow control (automatic PAUSE frame generation or software-programmed PAUSE frame generation and recognition)

- Programmable maximum frame length supports jumbo frames (up to 9.6 Kbytes) and IEEE Std. 802.1<sup>TM</sup> virtual local area network (VLAN) tags and priority

- VLAN insertion and deletion

- Per-frame VLAN control word or default VLAN for each eTSEC

- Extracted VLAN control word passed to software separately

- Retransmission following a collision

- CRC generation and verification of inbound/outbound frames

- Programmable Ethernet preamble insertion and extraction of up to 7 bytes

- MAC address recognition:

- Exact match on primary and virtual 48-bit unicast addresses

# 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the device. This device is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

# 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

# 2.1.1 Absolute Maximum Ratings

The following table provides the absolute maximum ratings.

| 1 |

|---|

|   |

| Characteristic                                                                                                         |                                                                                                                       | Symbol                                      | Max Value                                                            | Unit | Notes |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------|------|-------|

| Core supply voltage                                                                                                    |                                                                                                                       | V <sub>DD</sub>                             | -0.3 to 1.21                                                         | V    | _     |

| PLL supply vo                                                                                                          | ltage                                                                                                                 | AV <sub>DD</sub>                            | -0.3 to 1.21                                                         | V    | _     |

| Core power su                                                                                                          | upply for SerDes transceivers                                                                                         | SV <sub>DD</sub>                            | -0.3 to 1.21                                                         | V    | _     |

| Pad power su                                                                                                           | pply for SerDes transceivers                                                                                          | XV <sub>DD</sub>                            | -0.3 to 1.21                                                         | V    | —     |

| DDR and DDF                                                                                                            | R2 DRAM I/O voltage                                                                                                   | GV <sub>DD</sub>                            | -0.3 to 2.75<br>-0.3 to 1.98                                         | V    | 2     |

| Three-speed Ethernet I/O voltage                                                                                       |                                                                                                                       | LV <sub>DD</sub> (for eTSEC1<br>and eTSEC2) | -0.3 to 3.63<br>-0.3 to 2.75                                         | V    |       |

|                                                                                                                        |                                                                                                                       | TV <sub>DD</sub> (for eTSEC3<br>and eTSEC4) | -0.3 to 3.63<br>-0.3 to 2.75                                         |      | 3     |

| PCI/PCI-X, DUART, system control and power management, I <sup>2</sup> C, Ethernet MII management, and JTAG I/O voltage |                                                                                                                       | OV <sub>DD</sub>                            | -0.3 to 3.63                                                         | V    |       |

| Local bus I/O voltage                                                                                                  |                                                                                                                       | BV <sub>DD</sub>                            | -0.3 to 3.63<br>-0.3 to 2.75                                         | V    | —     |

| Input voltage                                                                                                          | DDR/DDR2 DRAM signals                                                                                                 | MV <sub>IN</sub>                            | –0.3 to (GV <sub>DD</sub> + 0.3)                                     | V    | 4     |

|                                                                                                                        | DDR/DDR2 DRAM reference                                                                                               | MV <sub>REF</sub>                           | -0.3 to<br>(GV <sub>DD</sub> /2 + 0.3)                               | V    | _     |

|                                                                                                                        | Three-speed Ethernet I/O signals                                                                                      | LV <sub>IN</sub><br>TV <sub>IN</sub>        | -0.3 to (LV <sub>DD</sub> + 0.3)<br>-0.3 to (TV <sub>DD</sub> + 0.3) | V    | 4     |

|                                                                                                                        | Local bus signals                                                                                                     | BV <sub>IN</sub>                            | -0.3 to (BV <sub>DD</sub> + 0.3)                                     | _    | —     |

|                                                                                                                        | DUART, SYSCLK, system control and power<br>management, I <sup>2</sup> C, Ethernet MII management,<br>and JTAG signals | OV <sub>IN</sub>                            | -0.3 to (OV <sub>DD</sub> + 0.3)                                     | V    | 4     |

|                                                                                                                        | PCI/PCI-X                                                                                                             | OV <sub>IN</sub>                            | -0.3 to (OV <sub>DD</sub> + 0.3)                                     | V    | 4     |

# 2.1.3 Output Driver Characteristics

The following table provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

| Driver Type                           | Programmable<br>Output Impedance<br>(Ω) | Supply<br>Voltage                                    | Notes |

|---------------------------------------|-----------------------------------------|------------------------------------------------------|-------|

| Local bus interface utilities signals | 25<br>25                                | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V | 1     |

|                                       | 45(default)<br>45(default)              | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V |       |

| PCI signals                           | 25                                      | OV <sub>DD</sub> = 3.3 V                             | 2     |

|                                       | 45(default)                             |                                                      |       |

| DDR signal                            | 18<br>36 (half strength mode)           | GV <sub>DD</sub> = 2.5 V                             | 3     |

| DDR2 signal                           | 18<br>36 (half strength mode)           | GV <sub>DD</sub> = 1.8 V                             | 3     |

| TSEC/10/100 signals                   | 45                                      | L/TV <sub>DD</sub> = 2.5/3.3 V                       | —     |

| DUART, system control, JTAG           | 45                                      | OV <sub>DD</sub> = 3.3 V                             | —     |

| 12C                                   | 150                                     | OV <sub>DD</sub> = 3.3 V                             |       |

Table 3. Output Drive Capability

Notes:

1. The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

2. The drive strength of the PCI interface is determined by the setting of the PCI\_GNT1 signal at reset.

3. The drive strength of the DDR interface in half-strength mode is at  $T_i = 105^{\circ}C$  and at  $GV_{DD}$  (min).

# 2.2 Power Sequencing

The device requires its power rails to be applied in a specific sequence in order to ensure proper device operation. These requirements are as follows for power-up:

- 1. V<sub>DD</sub>, AV<sub>DD</sub>, BV<sub>DD</sub>, LV<sub>DD</sub>, OV<sub>DD</sub>, SV<sub>DD</sub>, TV<sub>DD</sub>, XV<sub>DD</sub>

- 2.  $GV_{DD}$

All supplies must be at their stable values within 50 ms.

#### NOTE

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

#### NOTE

In order to guarantee MCKE low during power-up, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power-up, then the sequencing for  $GV_{DD}$  is not required.

# 4.3 eTSEC Gigabit Reference Clock Timing

The following table provides the eTSEC gigabit reference clocks (EC\_GTX\_CLK125) AC timing specifications for the device.

| Parameter/Condition                                                  | Symbol            | Min      | Тур | Max         | Unit | Notes |

|----------------------------------------------------------------------|-------------------|----------|-----|-------------|------|-------|

| EC_GTX_CLK125 frequency                                              | f <sub>G125</sub> | _        | 125 | —           | MHz  | _     |

| EC_GTX_CLK125 cycle time                                             | t <sub>G125</sub> | —        | 8   | —           | ns   |       |

| EC_GTX_CLK125 rise and fall time<br>L/TVDD = 2.5 V<br>L/TVDD = 3.3 V |                   | —        | _   | 0.75<br>1.0 | ns   | 1     |

| EC_GTX_CLK125 duty cycle<br>GMII, TBI<br>1000Base-T for RGMII, RTBI  |                   | 45<br>47 | _   | 55<br>53    | %    | 2, 3  |

| Table 6. EC_ | GTX_CLK125 AC Tim | ning Specifications |

|--------------|-------------------|---------------------|

|--------------|-------------------|---------------------|

Notes:

1. Rise and fall times for EC\_GTX\_CLK125 are measured from 0.5 and 2.0 V for L/TV<sub>DD</sub> = 2.5 V, and from 0.6 and 2.7 V for L/TV<sub>DD</sub> = 3.3 V.

- 2. Timing is guaranteed by design and characterization.

- 3. EC\_GTX\_CLK125 is used to generate the GTX clock TSEC*n*\_GTX\_CLK for the eTSEC transmitter with 2% degradation. EC\_GTX\_CLK125 duty cycle can be loosened from 47/53% as long as the PHY device can tolerate the duty cycle generated by the TSEC*n*\_GTX\_CLK. See Section 8.2.6, "RGMII and RTBI AC Timing Specifications," for duty cycle for 10Base-T and 100Base-T reference clock.

# 4.4 PCI/PCI-X Reference Clock Timing

When the PCI/PCI-X controller is configured for asynchronous operation, the reference clock for the PCI/PCI-x controller is not the SYSCLK input, but instead the PCIn\_CLK. The following table provides the PCI/PCI-X reference clock AC timing specifications for the device.

| Table 7. PCIn_CLK AC Timing Specifications | Table 7. PCI <i>n</i> | CLK | AC Timing | Specifications |

|--------------------------------------------|-----------------------|-----|-----------|----------------|

|--------------------------------------------|-----------------------|-----|-----------|----------------|

At recommended operating conditions (see Table 2) with  $OV_{DD} = 3.3 \text{ V} \pm 165 \text{ mV}$ .

| Parameter/Condition         | Symbol                                    | Min | Тур | Мах | Unit | Notes |

|-----------------------------|-------------------------------------------|-----|-----|-----|------|-------|

| PCIn_CLK frequency          | f <sub>PCICLK</sub>                       | 16  | —   | 133 | MHz  | —     |

| PCIn_CLK cycle time         | t <sub>PCICLK</sub>                       | 7.5 | —   | 60  | ns   | —     |

| PCIn_CLK rise and fall time | t <sub>PCIKH</sub> , t <sub>PCIKL</sub>   | 0.6 | 1.0 | 2.1 | ns   | 1, 2  |

| PCIn_CLK duty cycle         | t <sub>PCIKHKL</sub> /t <sub>PCICLK</sub> | 40  | —   | 60  | %    | 2     |

Notes:

1. Rise and fall times for SYSCLK are measured at 0.6 and 2.7 V.

2. Timing is guaranteed by design and characterization.

# 5 **RESET** Initialization

This section describes the AC electrical specifications for the RESET initialization timing requirements of the device. The following table provides the RESET initialization AC timing specifications for the DDR SDRAM component(s).

| Parameter/Condition                                                                                     | Min | Max | Unit    | Notes |

|---------------------------------------------------------------------------------------------------------|-----|-----|---------|-------|

| Required assertion time of HRESET                                                                       | 100 |     | μS      | —     |

| Minimum assertion time for SRESET                                                                       | 3   |     | SYSCLKs | 1     |

| PLL input setup time with stable SYSCLK before HRESET negation                                          | 100 |     | μS      | —     |

| Input setup time for POR configs (other than PLL config) with respect to negation of HRESET             | 4   | —   | SYSCLKs | 1     |

| Input hold time for all POR configs (including PLL config) with respect to negation of HRESET           | 2   | _   | SYSCLKs | 1     |

| Maximum valid-to-high impedance time for actively driven POR configs with respect to negation of HRESET | —   | 5   | SYSCLKs | 1     |

| Table 8. RESET Initialization | Timing | Specifications |

|-------------------------------|--------|----------------|

|-------------------------------|--------|----------------|

#### Note:

1. SYSCLK is the primary clock input for the device.

The following table provides the PLL lock times.

#### Table 9. PLL Lock Times

| Parameter/Condition              | Min | Мах | Unit |

|----------------------------------|-----|-----|------|

| Core and platform PLL lock times | —   | 100 | μs   |

| Local bus PLL lock time          | —   | 50  | μs   |

| PCI/PCI-X bus PLL lock time      | —   | 50  | μs   |

## 5.1 Power-On Ramp Rate

This section describes the AC electrical specifications for the power-on ramp rate requirements.

Controlling the maximum power-on ramp rate is required to avoid falsely triggering the ESD circuitry. The following table provides the power supply ramp rate specifications.

| Table 10. | Power | Supply | Ramp Rate |

|-----------|-------|--------|-----------|

|-----------|-------|--------|-----------|

| Parameter                    | Min | Мах  | Unit | Notes |

|------------------------------|-----|------|------|-------|

| Required ramp rate for MVREF | _   | 3500 | V/s  | 1     |

| Required ramp rate for VDD   |     | 4000 | V/s  | 1, 2  |

Note:

1. Maximum ramp rate from 200 to 500 mV is most critical as this range may falsely trigger the ESD circuitry.

2. VDD itself is not vulnerable to false ESD triggering; however, as per Section 22.2, "PLL Power Supply Filtering," the recommended AVDD\_CORE, AVDD\_PLAT, AVDD\_LBIU, AVDD\_PCI1 and AVDD\_PCI2 filters are all connected to VDD. Their ramp rates must be equal to or less than the VDD ramp rate.

# 6 DDR and DDR2 SDRAM

This section describes the DC and AC electrical specifications for the DDR SDRAM interface of the device. Note that  $GV_{DD}(typ) = 2.5 \text{ V}$  for DDR SDRAM, and  $GV_{DD}(typ) = 1.8 \text{ V}$  for DDR2 SDRAM.

# 6.1 DDR SDRAM DC Electrical Characteristics

The following table provides the recommended operating conditions for the DDR2 SDRAM controller of the device when  $GV_{DD}(typ) = 1.8 \text{ V}.$

| Parameter/Condition                              | Symbol            | Min                       | Мах                       | Unit | Notes |

|--------------------------------------------------|-------------------|---------------------------|---------------------------|------|-------|

| I/O supply voltage                               | GV <sub>DD</sub>  | 1.71                      | 1.89                      | V    | 1     |

| I/O reference voltage                            | MV <sub>REF</sub> | $0.49 \times GV_{DD}$     | $0.51 \times GV_{DD}$     | V    | 2     |

| I/O termination voltage                          | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04  | MV <sub>REF</sub> + 0.04  | V    | 3     |

| Input high voltage                               | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.125 | GV <sub>DD</sub> + 0.3    | V    | —     |

| Input low voltage                                | V <sub>IL</sub>   | -0.3                      | MV <sub>REF</sub> – 0.125 | V    | —     |

| Output leakage current                           | I <sub>OZ</sub>   | -50                       | 50                        | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>OH</sub>   | -13.4                     | —                         | mA   | _     |

| Output low current (V <sub>OUT</sub> = 0.280 V)  | I <sub>OL</sub>   | 13.4                      | —                         | mA   |       |

Table 11. DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V

#### Notes:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $V_{DD}$  at all times.

2.  $MV_{REF}$  is expected to be equal to 0.5 ×  $GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}$  may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail must track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled,  $0 V \le V_{OUT} \le GV_{DD}$ .

This table provides the DDR2 I/O capacitance when  $GV_{DD}(typ) = 1.8$  V.

#### Table 12. DDR2 SDRAM Capacitance for GV<sub>DD</sub>(typ)=1.8 V

| Parameter/Condition                          | Symbol           | Min | Мах | Unit | Notes |

|----------------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS, DQS | C <sub>DIO</sub> | _   | 0.5 | pF   | 1     |

Note:

1. This parameter is sampled.  $GV_{DD} = 1.8 \text{ V} \pm 0.090 \text{ V}$ , f = 1 MHz, T<sub>A</sub> = 25°C,  $V_{OUT} = GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

| Parameters                                                                      | Symbol                             | Min    | Мах                                      | Unit | Notes   |

|---------------------------------------------------------------------------------|------------------------------------|--------|------------------------------------------|------|---------|

| Supply voltage 2.5 V                                                            | LV <sub>DD</sub> /TV <sub>DD</sub> | 2.37   | 2.63                                     | V    | 1, 2    |

| Output high voltage ( $LV_{DD}/TV_{DD} = Min$ ,<br>$I_{OH} = -1.0 \text{ mA}$ ) | V <sub>OH</sub>                    | 2.00   | LV <sub>DD</sub> /TV <sub>DD</sub> + 0.3 | V    | _       |

| Output low voltage ( $LV_{DD}/TV_{DD} = Min$ ,<br>I <sub>OL</sub> = 1.0 mA)     | V <sub>OL</sub>                    | GND0.3 | 0.40                                     | V    | _       |

| Input high voltage                                                              | V <sub>IH</sub>                    | 1.70   | $LV_{DD}/TV_{DD} + 0.3$                  | V    | —       |

| Input low voltage                                                               | V <sub>IL</sub>                    | -0.3   | 0.90                                     | V    | —       |

| Input high current ( $V_{IN} = LV_{DD}$ , $V_{IN} = TV_{DD}$ )                  | Ι <sub>ΙΗ</sub>                    | —      | 10                                       | μA   | 1, 2, 3 |

| Input low current (V <sub>IN</sub> = GND)                                       | ١ <sub>١L</sub>                    | -15    | —                                        | μA   | 3       |

Table 23. GMII, MII, RMII, TBI, RGMII, RTBI, and FIFO DC Electrical Characteristics

Notes:

1.  $LV_{DD}$  supports eTSECs 1 and 2.

2.  $\mathsf{TV}_{\mathsf{DD}}$  supports eTSECs 3 and 4.

3. Note that the symbol  $V_{IN}$ , in this case, represents the  $LV_{IN}$  and  $TV_{IN}$  symbols referenced in Table 1 and Table 2.

# 8.2 FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications

The AC timing specifications for FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI are presented in this section.

## 8.2.1 FIFO AC Specifications

The basis for the AC specifications for the eTSEC's FIFO modes is the double data rate RGMII and RTBI specifications, since they have similar performances and are described in a source-synchronous fashion like FIFO modes. However, the FIFO interface provides deliberate skew between the transmitted data and source clock in GMII fashion.

When the eTSEC is configured for FIFO modes, all clocks are supplied from external sources to the relevant eTSEC interface. That is, the transmit clock must be applied to the eTSEC*n*'s TSEC*n*\_TX\_CLK, while the receive clock must be applied to pin TSEC*n*\_RX\_CLK. The eTSEC internally uses the transmit clock to synchronously generate transmit data and outputs an echoed copy of the transmit clock back out onto the TSEC*n*\_GTX\_CLK pin (while transmit data appears on TSEC*n*\_TXD[7:0], for example). It is intended that external receivers capture eTSEC transmit data using the clock on TSEC*n*\_GTX\_CLK as a source- synchronous timing reference. Typically, the clock edge that launched the data can be used, since the clock is delayed by the eTSEC to allow acceptable set-up margin at the receiver. Note that there is relationship between the maximum FIFO speed and the platform speed. For more information see Section 4.5, "Platform to FIFO Restrictions."

# 9 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals MDIO (management data input/output) and MDC (management data clock). The electrical characteristics for GMII, RGMII, RMII, TBI, and RTBI are specified in "Section 8, "Enhanced Three-Speed Ethernet (eTSEC)."

# 9.1 MII Management DC Electrical Characteristics

The MDC and MDIO are defined to operate at a supply voltage of 3.3 V. The DC electrical characteristics for MDIO and MDC are provided in this table.

| Parameter                                                            | Symbol           | Min  | Мах                    | Unit |

|----------------------------------------------------------------------|------------------|------|------------------------|------|

| Supply voltage (3.3 V)                                               | OV <sub>DD</sub> | 3.13 | 3.47                   | V    |

| Output high voltage ( $OV_{DD} = Min, I_{OH} = -1.0 mA$ )            | V <sub>OH</sub>  | 2.10 | OV <sub>DD</sub> + 0.3 | V    |

| Output low voltage (OV <sub>DD</sub> =Min, I <sub>OL</sub> = 1.0 mA) | V <sub>OL</sub>  | GND  | 0.50                   | V    |

| Input high voltage                                                   | V <sub>IH</sub>  | 2.0  | —                      | V    |

| Input low voltage                                                    | V <sub>IL</sub>  | _    | 0.90                   | V    |

| Input high current ( $OV_{DD} = Max, V_{IN}^1 = 2.1 V$ )             | I <sub>IH</sub>  | _    | 40                     | μA   |

| Input low current ( $OV_{DD} = Max$ , $V_{IN} = 0.5 V$ )             | IIL              | -600 | —                      | μΑ   |

Table 36. MII Management DC Electrical Characteristics

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

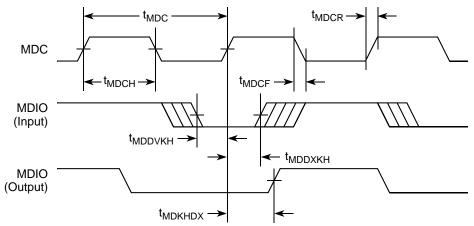

# 9.2 MII Management AC Electrical Specifications

This table provides the MII management AC timing specifications.

#### Table 37. MII Management AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  is 3.3 V ± 5%.

| Parameter                  | Symbol <sup>1</sup> | Min                             | Тур | Мах                                | Unit | Notes   |

|----------------------------|---------------------|---------------------------------|-----|------------------------------------|------|---------|

| MDC frequency              | f <sub>MDC</sub>    | 0.72                            | 2.5 | 8.3                                | MHz  | 2, 3, 4 |

| MDC period                 | t <sub>MDC</sub>    | 120.5                           | _   | 1389                               | ns   | —       |

| MDC clock pulse width high | t <sub>MDCH</sub>   | 32                              | _   | —                                  | ns   | _       |

| MDC to MDIO valid          | t <sub>MDKHDV</sub> | $16 \times t_{CCB}$             | _   | —                                  | ns   | 5       |

| MDC to MDIO delay          | t <sub>MDKHDX</sub> | (16 × t <sub>CCB</sub> × 8) – 3 | _   | $(16 \times t_{CCB} \times 8) + 3$ | ns   | 5       |

| MDIO to MDC setup time     | t <sub>MDD∨KH</sub> | 5                               | _   | —                                  | ns   | _       |

| MDIO to MDC hold time      | t <sub>MDDXKH</sub> | 0                               | _   | —                                  | ns   | —       |

| MDC rise time              | t <sub>MDCR</sub>   | _                               |     | 10                                 | ns   | 4       |

#### **Ethernet Management Interface Electrical Characteristics**

#### Table 37. MII Management AC Timing Specifications (continued)

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  is 3.3 V ± 5%.

| Parameter     | Symbol <sup>1</sup> | Min | Тур | Мах | Unit | Notes |

|---------------|---------------------|-----|-----|-----|------|-------|

| MDC fall time | t <sub>MDHF</sub>   |     |     | 10  | ns   | 4     |

#### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MDKHDX</sub> symbolizes management data timing (MD) for the time t<sub>MDC</sub> from clock reference (K) high (H) until data outputs (D) are invalid (X) or data hold time. Also, t<sub>MDDVKH</sub> symbolizes management data timing (MD) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MDC</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

- 2. This parameter is dependent on the eTSEC system clock speed, which is half of the Platform Frequency (f<sub>CCB</sub>). The actual ECn\_MDC output clock frequency for a specific eTSEC port can be programmed by configuring the MgmtClk bit field of device's MIIMCFG register, based on the platform (CCB) clock running for the device. The formula is: Platform Frequency (CCB) ÷ (2 × Frequency Divider determined by MIICFG[MgmtClk] encoding selection). For example, if MIICFG[MgmtClk] = 000 and the platform (CCB) is currently running at 533 MHz, f<sub>MDC</sub> = 533) ÷ (2 × 4 × 8) = 533) ÷ 64 = 8.3 MHz. That is, for a system running at a particular platform frequency (f<sub>CCB</sub>), the ECn\_MDC output clock frequency can be programmed between maximum f<sub>MDC</sub> = f<sub>CCB</sub> ÷ 64 and minimum f<sub>MDC</sub> = f<sub>CCB</sub> ÷ 448. See 14.5.3.6.6, "MII Management Configuration Register (MIIMCFG)," in the MPC8548E PowerQUICC™ III Integrated Processor Family Reference Manual for more detail.

- 3. The maximum ECn\_MDC output clock frequency is defined based on the maximum platform frequency for device (533 MHz) divided by 64, while the minimum ECn\_MDC output clock frequency is defined based on the minimum platform frequency for device (333 MHz) divided by 448, following the formula described in Note 2 above.

- 4. Guaranteed by design.

- 5. t<sub>CCB</sub> is the platform (CCB) clock period.

Figure 21 shows the MII management AC timing diagram.

Figure 21. MII Management Interface Timing Diagram

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min      | Мах      | Unit | Notes |

|----------------------------------------------------------------------------|--------------------------------------------|----------|----------|------|-------|

| Valid times:<br>Boundary-scan data<br>TDO                                  | t <sub>jtkldv</sub><br>t <sub>jtklov</sub> | 4<br>2   | 20<br>10 | ns   | 5     |

| Output hold times:<br>Boundary-scan data<br>TDO                            | t <sub>jtkldx</sub><br>t <sub>jtklox</sub> | 30<br>30 |          | ns   | 5     |

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>jtkldz</sub><br>t <sub>jtkloz</sub> | 3<br>3   | 19<br>9  | ns   | 5, 6  |

Table 44. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup> (continued)

#### Notes:

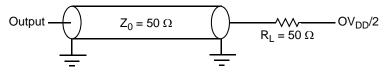

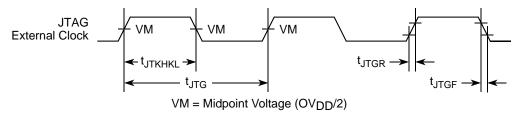

- All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 29). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- 5. Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

- 6. Guaranteed by design.

Figure 29 provides the AC test load for TDO and the boundary-scan outputs.

Figure 29. AC Test Load for the JTAG Interface

Figure 30 provides the JTAG clock input timing diagram.

Figure 30. JTAG Clock Input Timing Diagram

JTAG

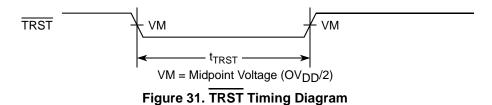

Figure 31 provides the  $\overline{\text{TRST}}$  timing diagram.

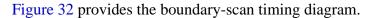

Figure 32. Boundary-Scan Timing Diagram

# 14 GP<sub>OUT</sub>/GP<sub>IN</sub>

This section describes the DC and AC electrical specifications for the GP<sub>OUT</sub>/GP<sub>IN</sub> bus of the device.

# 14.1 GP<sub>OUT</sub>/GP<sub>IN</sub> Electrical Characteristics

Table 47 and Table 48 provide the DC electrical characteristics for the GP<sub>OUT</sub> interface.

| Parameter                                                                      | Symbol           | Min                    | Мах  | Unit |

|--------------------------------------------------------------------------------|------------------|------------------------|------|------|

| Supply voltage 3.3 V                                                           | BV <sub>DD</sub> | 3.13                   | 3.47 | V    |

| High-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = -2 mA) | V <sub>OH</sub>  | BV <sub>DD</sub> – 0.2 | _    | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)   | V <sub>OL</sub>  | —                      | 0.2  | V    |

Table 47. GP<sub>OUT</sub> DC Electrical Characteristics (3.3 V DC)

Table 48. GP<sub>OUT</sub> DC Electrical Characteristics (2.5 V DC)

| Parameter                                                                  | Symbol           | Min       | Мах                    | Unit |

|----------------------------------------------------------------------------|------------------|-----------|------------------------|------|

| Supply voltage 2.5 V                                                       | BV <sub>DD</sub> | 2.37      | 2.63                   | V    |

| High-level output voltage<br>( $BV_{DD} = min, I_{OH} = -1 mA$ )           | V <sub>OH</sub>  | 2.0       | BV <sub>DD</sub> + 0.3 | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> min, I <sub>OL</sub> = 1 mA) | V <sub>OL</sub>  | GND – 0.3 | 0.4                    | V    |

Table 49 and Table 50 provide the DC electrical characteristics for the GP<sub>IN</sub> interface.

Table 49. GP<sub>IN</sub> DC Electrical Characteristics (3.3 V DC)

| Parameter                                                                                      | Symbol           | Min  | Мах                    | Unit |

|------------------------------------------------------------------------------------------------|------------------|------|------------------------|------|

| Supply voltage 3.3 V                                                                           | BV <sub>DD</sub> | 3.13 | 3.47                   | V    |

| High-level input voltage                                                                       | V <sub>IH</sub>  | 2    | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                                        | V <sub>IL</sub>  | -0.3 | 0.8                    | V    |

| Input current<br>(BV <sub>IN</sub> <sup>1</sup> = 0 V or BV <sub>IN</sub> = BV <sub>DD</sub> ) | I <sub>IN</sub>  | _    | ±5                     | μA   |

Note:

1. The symbol  $\mathsf{BV}_{\mathsf{IN}}$ , in this case, represents the  $\mathsf{BV}_{\mathsf{IN}}$  symbol referenced in Table 1.

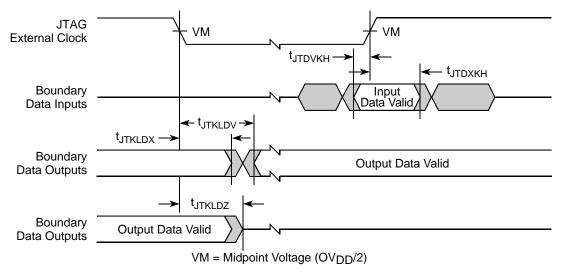

- The SD\_REF\_CLK and SD\_REF\_CLK are internally AC-coupled differential inputs as shown in Figure 39. Each differential clock input (SD\_REF\_CLK or SD\_REF\_CLK) has a 50-Ω termination to SGND\_SRDSn (xcorevss) followed by on-chip AC-coupling.

- The external reference clock driver must be able to drive this termination.

- The SerDes reference clock input can be either differential or single-ended. See the differential mode and single-ended mode description below for further detailed requirements.

- The maximum average current requirement that also determines the common mode voltage range:

- When the SerDes reference clock differential inputs are DC coupled externally with the clock driver chip, the maximum average current allowed for each input pin is 8 mA. In this case, the exact common mode input voltage is not critical as long as it is within the range allowed by the maximum average current of 8 mA (see the following bullet for more detail), since the input is AC-coupled on-chip.

- This current limitation sets the maximum common mode input voltage to be less than 0.4 V (0.4 V/50 = 8 mA) while the minimum common mode input level is 0.1 V above SGND\_SRDS*n* (xcorevss). For example, a clock with a 50/50 duty cycle can be produced by a clock driver with output driven by its current source from 0 to 16 mA (0–0.8 V), such that each phase of the differential input has a single-ended swing from 0 V to 800 mV with the common mode voltage at 400 mV.

- If the device driving the SD\_REF\_CLK and  $\overline{\text{SD}_{\text{REF}_{\text{CLK}}}}$  inputs cannot drive 50 Ω to SGND\_SRDS*n* (xcorevss) DC, or it exceeds the maximum input current limitations, then it must be AC-coupled off-chip.

- The input amplitude requirement:

- This requirement is described in detail in the following sections.

Figure 39. Receiver of SerDes Reference Clocks

## 16.2.2 DC Level Requirement for SerDes Reference Clocks

The DC level requirement for the SerDes reference clock inputs is different depending on the signaling mode used to connect the clock driver chip and SerDes reference clock inputs as described below:

• Differential mode

components are included in this requirement. The reference impedance for return loss measurements is  $100-\Omega$  resistive for differential return loss and  $25-\Omega$  resistive for common mode.

| Characteristic                                     | Symbol          | Rai  | nge               | Unit   | Notes                                                        |

|----------------------------------------------------|-----------------|------|-------------------|--------|--------------------------------------------------------------|

| Characteristic                                     | Symbol          | Min  | Max               | Unit   | NOICS                                                        |

| Differential input voltage                         | V <sub>IN</sub> | 200  | 1600              | mVp-p  | Measured at receiver                                         |

| Deterministic jitter tolerance                     | J <sub>D</sub>  | 0.37 | —                 | UI p-p | Measured at receiver                                         |

| Combined deterministic and random jitter tolerance | J <sub>DR</sub> | 0.55 | —                 | UI p-p | Measured at receiver                                         |

| Total jitter tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65 | _                 | UI p-p | Measured at receiver                                         |

| Multiple input skew                                | S <sub>MI</sub> | —    | 24                | ns     | Skew at the receiver input between lanes of a multilane link |

| Bit error rate                                     | BER             | —    | 10 <sup>-12</sup> | —      | —                                                            |

| Unit interval                                      | UI              | 800  | 800               | ps     | ±100 ppm                                                     |

#### Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter, and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 53. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk, and other variable system effects.

#### Table 67. Receiver AC Timing Specifications—2.5 GBaud

| Characteristic                                     | Symbol          | Range |                   | Unit   | Notes                                                        |  |

|----------------------------------------------------|-----------------|-------|-------------------|--------|--------------------------------------------------------------|--|

| Characteristic                                     | Symbol          | Min   | Max               | Unit   | 10163                                                        |  |

| Differential input voltage                         | V <sub>IN</sub> | 200   | 1600              | mVp-p  | Measured at receiver                                         |  |

| Deterministic jitter tolerance                     | J <sub>D</sub>  | 0.37  | _                 | UI p-p | Measured at receiver                                         |  |

| Combined deterministic and random jitter tolerance | J <sub>DR</sub> | 0.55  | _                 | UI p-p | Measured at receiver                                         |  |

| Total jitter tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65  | _                 | UI p-p | Measured at receiver                                         |  |

| Multiple input skew                                | S <sub>MI</sub> | _     | 24                | ns     | Skew at the receiver input between lanes of a multilane link |  |

| Bit error rate                                     | BER             | _     | 10 <sup>-12</sup> |        | —                                                            |  |

| Unit interval                                      | UI              | 400   | 400               | ps     | ±100 ppm                                                     |  |

#### Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter, and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 53. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk, and other variable system effects.

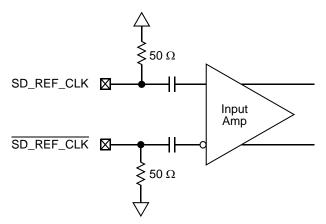

# 18.8 Receiver Eye Diagrams

For each baud rate at which an LP-serial receiver is specified to operate, the receiver shall meet the corresponding bit error rate specification (Table 66, Table 67, and Table 68) when the eye pattern of the receiver test signal (exclusive of sinusoidal jitter) falls entirely within the unshaded portion of the receiver input compliance mask shown in Figure 54 with the parameters specified in Table 69. The eye pattern of the receiver test signal is measured at the input pins of the receiving device with the device replaced with a  $100-\Omega \pm 5\%$  differential resistive load.

Figure 54. Receiver Input Compliance Mask

Table 69. Receiver Input Compliance Mask Parameters Exclusive of Sinusoidal Jitter

| Receiver Type | V <sub>DIFF</sub> min<br>(mV) | V <sub>DIFF</sub> max<br>(mV) | A (UI) | B (UI) |

|---------------|-------------------------------|-------------------------------|--------|--------|

| 1.25 GBaud    | 100                           | 800                           | 0.275  | 0.400  |

| 2.5 GBaud     | 100                           | 800                           | 0.275  | 0.400  |

| 3.125 GBaud   | 100                           | 800                           | 0.275  | 0.400  |

## **18.9 Measurement and Test Requirements**

Since the LP-serial electrical specification are guided by the XAUI electrical interface specified in Clause 47 of IEEE Std. 802.3ae-2002, the measurement and test requirements defined here are similarly guided by Clause 47. Additionally, the CJPAT test pattern defined in Annex 48A of IEEE Std.

Package Description

| Table 72. MPC8547E Pinout Listing (continued | I) |

|----------------------------------------------|----|

|----------------------------------------------|----|

| Signal                 | Package Pin Number                     | Pin Type | Power<br>Supply  | Notes           |

|------------------------|----------------------------------------|----------|------------------|-----------------|

| Reserved               | U20, V22, W20, Y22                     | _        |                  | 15              |

| Reserved               | U21, V23, W21, Y23                     | —        | —                | 15              |

| SD_PLL_TPD             | U28                                    | 0        | XV <sub>DD</sub> | 24              |

| SD_REF_CLK             | T28                                    | I        | XV <sub>DD</sub> | —               |

| SD_REF_CLK             | T27                                    | I        | XV <sub>DD</sub> | —               |

| Reserved               | AC1, AC3                               | —        | _                | 2               |

| Reserved               | M26, V28                               | —        | —                | 32              |

| Reserved               | M25, V27                               | —        | —                | 34              |

| Reserved               | M20, M21, T22, T23                     | —        | —                | 38              |

| · · · · ·              | General-Purpose Output                 |          | I                | •               |

| GPOUT[24:31]           | K26, K25, H27, G28, H25, J26, K24, K23 | 0        | BV <sub>DD</sub> | —               |

| · · · ·                | System Control                         |          |                  | •               |

| HRESET                 | AG17                                   | I        | OV <sub>DD</sub> | —               |

| HRESET_REQ             | AG16                                   | 0        | OV <sub>DD</sub> | 29              |

| SRESET                 | AG20                                   | I        | OV <sub>DD</sub> | —               |

| CKSTP_IN               | AA9                                    | I        | OV <sub>DD</sub> | —               |

| CKSTP_OUT              | AA8                                    | 0        | OV <sub>DD</sub> | 2, 4            |

|                        | Debug                                  |          |                  |                 |

| TRIG_IN                | AB2                                    | I        | OV <sub>DD</sub> | —               |

| TRIG_OUT/READY/QUIESCE | AB1                                    | 0        | OV <sub>DD</sub> | 6, 9,<br>19, 29 |

| MSRCID[0:1]            | AE4, AG2                               | 0        | OV <sub>DD</sub> | 5, 6, 9         |

| MSRCID[2:4]            | AF3, AF1, AF2                          | 0        | OV <sub>DD</sub> | 6, 19,<br>29    |

| MDVAL                  | AE5                                    | 0        | OV <sub>DD</sub> | 6               |

| CLK_OUT                | AE21                                   | 0        | OV <sub>DD</sub> | 11              |

|                        | Clock                                  | •        |                  |                 |

| RTC                    | AF16                                   | I        | OV <sub>DD</sub> | —               |

| SYSCLK                 | AH17                                   | I        | OV <sub>DD</sub> | —               |

|                        | JTAG                                   | •        |                  |                 |

| ТСК                    | AG28                                   | I        | OV <sub>DD</sub> | —               |

| TDI                    | AH28                                   | I        | OV <sub>DD</sub> | 12              |

| TDO                    | AF28                                   | 0        | OV <sub>DD</sub> | —               |

| TMS                    | AH27                                   | I        | OV <sub>DD</sub> | 12              |

| TRST                   | AH23                                   | I        | OV <sub>DD</sub> | 12              |

Package Description

| Signal                 | Package Pin Number                     | Pin Type | Power<br>Supply  | Notes           |

|------------------------|----------------------------------------|----------|------------------|-----------------|

| SD_TX[0:3]             | M23, N21, P23, R21                     | 0        | XV <sub>DD</sub> | —               |

| Reserved               | Reserved W26, Y28, AA26, AB28          |          | _                | 40              |

| Reserved               | W25, Y27, AA25, AB27                   | —        | —                | 40              |

| Reserved               | U20, V22, W20, Y22                     | —        | —                | 15              |

| Reserved               | U21, V23, W21, Y23                     | —        | —                | 15              |

| SD_PLL_TPD             | U28                                    | 0        | XV <sub>DD</sub> | 24              |

| SD_REF_CLK             | T28                                    | I        | XV <sub>DD</sub> | —               |

| SD_REF_CLK             | T27                                    | I        | XV <sub>DD</sub> | —               |

| Reserved               | AC1, AC3                               | —        | —                | 2               |

| Reserved               | M26, V28                               | —        | —                | 32              |

| Reserved               | M25, V27                               | —        | —                | 34              |

| Reserved               | M20, M21, T22, T23                     | —        | —                | 38              |

|                        | General-Purpose Output                 |          | I                |                 |

| GPOUT[24:31]           | K26, K25, H27, G28, H25, J26, K24, K23 | 0        | BV <sub>DD</sub> | —               |

|                        | System Control                         |          |                  |                 |

| HRESET                 | AG17                                   | I        | OV <sub>DD</sub> | —               |

| HRESET_REQ             | AG16                                   | 0        | OV <sub>DD</sub> | 29              |

| SRESET                 | AG20                                   | I        | OV <sub>DD</sub> | —               |

| CKSTP_IN               | AA9                                    | I        | OV <sub>DD</sub> | —               |

| CKSTP_OUT              | AA8                                    | 0        | OV <sub>DD</sub> | 2, 4            |

|                        | Debug                                  |          | •                |                 |

| TRIG_IN                | AB2                                    | I        | OV <sub>DD</sub> | —               |

| TRIG_OUT/READY/QUIESCE | AB1                                    | 0        | OV <sub>DD</sub> | 6, 9,<br>19, 29 |

| MSRCID[0:1]            | AE4, AG2                               | 0        | OV <sub>DD</sub> | 5, 6, 9         |

| MSRCID[2:4]            | AF3, AF1, AF2                          | 0        | OV <sub>DD</sub> | 6, 19,<br>29    |

| MDVAL                  | AE5                                    | 0        | OV <sub>DD</sub> | 6               |

| CLK_OUT                | AE21                                   | 0        | OV <sub>DD</sub> | 11              |

|                        | Clock                                  |          |                  |                 |

| RTC                    | AF16                                   | I        | OV <sub>DD</sub> | —               |

| SYSCLK                 | AH17                                   | I        | OV <sub>DD</sub> | —               |

|                        | JTAG                                   | •        |                  |                 |

| ТСК                    | AG28                                   | I        | OV <sub>DD</sub> | —               |

| TDI                    | AH28                                   | I        | OV <sub>DD</sub> | 12              |

| Signal           | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Type                                              | Power<br>Supply  | Notes     |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|-----------|

|                  | JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11                                                    |                  |           |

| ТСК              | AG28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | —         |

| TDI              | AH28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 12        |

| TDO              | AF28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                     | $OV_{DD}$        | —         |

| TMS              | AH27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 12        |

| TRST             | AH23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 12        |

|                  | DFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       |                  |           |

| L1_TSTCLK        | AC25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 25        |

| L2_TSTCLK        | AE22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 25        |

| LSSD_MODE        | AH20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 25        |

| TEST_SEL         | AH14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 109       |

|                  | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |                  |           |

| THERM0           | AG1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                     | _                | 14        |

| THERM1           | AH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                     | _                | 14        |

|                  | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                       |                  |           |

| ASLEEP           | AH18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                     | $OV_{DD}$        | 9, 19, 29 |

|                  | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                       |                  |           |

| GND              | <ul> <li>A11, B7, B24, C1, C3, C5, C12, C15, C26, D8,<br/>D11, D16, D20, D22, E1, E5, E9, E12, E15, E17,<br/>F4, F26, G12, G15, G18, G21, G24, H2, H6, H8,<br/>H28, J4, J12, J15, J17, J27, K7, K9, K11, K27,<br/>L3, L5, L12, L16, N11, N13, N15, N17, N19, P4,<br/>P9, P12, P14, P16, P18, R11, R13, R15, R17,<br/>R19, T4, T12, T14, T16, T18, U8, U11, U13,<br/>U15, U17, U19, V4, V12, V18, W6, W19, Y4, Y9,<br/>Y11, Y19, AA6, AA14, AA17, AA22, AA23, AB4,<br/>AC2, AC11, AC19, AC26, AD5, AD9, AD22,<br/>AE3, AE14, AF6, AF10, AF13, AG8, AG27,<br/>K28, L24, L26, N24, N27, P25, R28, T24, T26,<br/>U24, V25, W28, Y24, Y26, AA24, AA27, AB25,<br/>AC28, L21, L23, N22, P20, R23, T21, U22, V20,<br/>W23, Y21, U27</li> </ul> | _                                                     |                  |           |

| OV <sub>DD</sub> | V16, W11, W14, Y18, AA13, AA21, AB11,<br>AB17, AB24, AC4, AC9, AC21, AD6, AD13,<br>AD17, AD19, AE10, AE8, AE24, AF4, AF12,<br>AF22, AF27, AG26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Power for<br>PCI and<br>other<br>standards<br>(3.3 V) | OV <sub>DD</sub> | _         |

| LV <sub>DD</sub> | N8, R7, T9, U6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Power for<br>TSEC1 and<br>TSEC2<br>(2.5 V, 3.3 V)     | LV <sub>DD</sub> | _         |

| Characteristic        | JEDEC Board | Symbol                | Value | Unit | Notes |

|-----------------------|-------------|-----------------------|-------|------|-------|

| Die junction-to-board | N/A         | $R_{	extsf{	heta}JB}$ | 5     | °C/W | 3     |

| Die junction-to-case  | N/A         | $R_{	ext{	heta}JC}$   | 0.8   | °C/W | 4     |

Table 85. Package Thermal Characteristics for FC-PBGA (continued)

Notes:

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

- 3. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 4. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1). The cold plate temperature is used for the case temperature, measured value includes the thermal resistance of the interface layer.

# 21.3 Heat Sink Solution

Every system application has different conditions that the thermal management solution must solve. As such, providing a recommended heat sink has not been found to be very useful. When a heat sink is chosen, give special consideration to the mounting technique. Mounting the heat sink to the printed-circuit board is the recommended procedure using a maximum of 10 lbs force (45 Newtons) perpendicular to the package and board. Clipping the heat sink to the package is not recommended.

# 22 System Design Information

This section provides electrical design recommendations for successful application of the device.

# 22.1 System Clocking