#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

### Details

ĿХF

| Product Status                  | Obsolete                                                   |

|---------------------------------|------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                               |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                             |

| Speed                           | 1.0GHz                                                     |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                      |

| RAM Controllers                 | DDR, DDR2, SDRAM                                           |

| Graphics Acceleration           | No                                                         |

| Display & Interface Controllers |                                                            |

| Ethernet                        | 10/100/1000Mbps (4)                                        |

| SATA                            | -                                                          |

| USB                             | - ·                                                        |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                           |

| Operating Temperature           | 0°C ~ 105°C (TA)                                           |

| Security Features               | Cryptography, Random Number Generator                      |

| Package / Case                  | 783-BBGA, FCBGA                                            |

| Supplier Device Package         | 783-FCBGA (29x29)                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8543evuaqg |

|                                 |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Performance monitor facility that is similar to, but separate from, the device performance monitor

The e500 defines features that are not implemented on this device. It also generally defines some features that this device implements more specifically. An understanding of these differences can be critical to ensure proper operations.

- 512-Kbyte L2 cache/SRAM

- Flexible configuration.

- Full ECC support on 64-bit boundary in both cache and SRAM modes

- Cache mode supports instruction caching, data caching, or both.

- External masters can force data to be allocated into the cache through programmed memory ranges or special transaction types (stashing).

- 1, 2, or 4 ways can be configured for stashing only.

- Eight-way set-associative cache organization (32-byte cache lines)

- Supports locking entire cache or selected lines. Individual line locks are set and cleared through Book E instructions or by externally mastered transactions.

- Global locking and Flash clearing done through writes to L2 configuration registers

- Instruction and data locks can be Flash cleared separately.

- SRAM features include the following:

- I/O devices access SRAM regions by marking transactions as snoopable (global).

- Regions can reside at any aligned location in the memory map.

- Byte-accessible ECC is protected using read-modify-write transaction accesses for smaller-than-cache-line accesses.

- Address translation and mapping unit (ATMU)

- Eight local access windows define mapping within local 36-bit address space.

- Inbound and outbound ATMUs map to larger external address spaces.

- Three inbound windows plus a configuration window on PCI/PCI-X and PCI Express

- Four inbound windows plus a default window on RapidIO<sup>™</sup>

- Four outbound windows plus default translation for PCI/PCI-X and PCI Express

- Eight outbound windows plus default translation for RapidIO with segmentation and sub-segmentation support

- DDR/DDR2 memory controller

- Programmable timing supporting DDR and DDR2 SDRAM

- 64-bit data interface

- Four banks of memory supported, each up to 4 Gbytes, to a maximum of 16 Gbytes

- DRAM chip configurations from 64 Mbits to 4 Gbits with ×8/×16 data ports

- Full ECC support

- Page mode support

- Up to 16 simultaneous open pages for DDR

**Power Characteristics**

### **Power Characteristics** 3

The estimated typical power dissipation for the core complex bus (CCB) versus the core frequency for this family of PowerQUICC III devices is shown in the following table.

| CCB Frequency <sup>1</sup> | Core Frequency | SLEEP <sup>2</sup> | Typical-65 <sup>3</sup> | Typical-105 <sup>4</sup> | Maximum <sup>5</sup> | Unit |

|----------------------------|----------------|--------------------|-------------------------|--------------------------|----------------------|------|

| 400                        | 800            | 2.7                | 4.6                     | 7.5                      | 8.1                  | W    |

|                            | 1000           | 2.7                | 5.0                     | 7.9                      | 8.5                  | W    |

|                            | 1200           | 2.7                | 5.4                     | 8.3                      | 8.9                  |      |

| 500                        | 1500           | 11.5               | 13.6                    | 16.5                     | 18.6                 | W    |

| 533                        | 1333           | 6.2                | 7.9                     | 10.8                     | 12.8                 | W    |

## **Table 4. Device Power Dissipation**

Notes:

1. CCB frequency is the SoC platform frequency, which corresponds to the DDR data rate.

2. SLEEP is based on  $V_{DD}$  = 1.1 V,  $T_i$  = 65°C.

3. Typical-65 is based on  $V_{DD} = 1.1 \text{ V}$ ,  $T_j = 65^{\circ}\text{C}$ , running Dhrystone. 4. Typical-105 is based on  $V_{DD} = 1.1 \text{ V}$ ,  $T_j = 105^{\circ}\text{C}$ , running Dhrystone. 5. Maximum is based on  $V_{DD} = 1.1 \text{ V}$ ,  $T_j = 105^{\circ}\text{C}$ , running a smoke test.

# 4.5 Platform to FIFO Restrictions

Note the following FIFO maximum speed restrictions based on platform speed.

For FIFO GMII mode:

FIFO TX/RX clock frequency ≤ platform clock frequency/4.2

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency must be no more than 127 MHz.

For FIFO encoded mode:

FIFO TX/RX clock frequency  $\leq$  platform clock frequency/4.2

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency must be no more than 167 MHz.

# 4.6 Platform Frequency Requirements for PCI-Express and Serial RapidIO

The CCB clock frequency must be considered for proper operation of the high-speed PCI-Express and Serial RapidIO interfaces as described below.

For proper PCI Express operation, the CCB clock frequency must be greater than:

See *MPC8548ERM*, *Rev.* 2, *PowerQUICC III Integrated Processor Family Reference Manual*, Section 18.1.3.2, "Link Width," for PCI Express interface width details.

For proper serial RapidIO operation, the CCB clock frequency must be greater than:

$2 \times (0.80) \times (Serial RapidIO interface frequency) \times (Serial RapidIO link width)$

64

See *MPC8548ERM*, *Rev.* 2, *PowerQUICC III Integrated Processor Family Reference Manual*, Section 17.4, "1x/4x LP-Serial Signal Descriptions," for serial RapidIO interface width and frequency details.

# 4.7 Other Input Clocks

For information on the input clocks of other functional blocks of the platform see the specific section of this document.

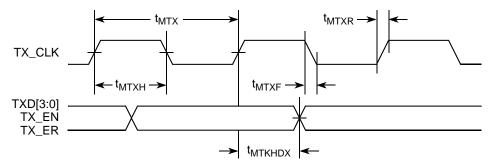

Figure 11 shows the MII transmit AC timing diagram.

Figure 11. MII Transmit AC Timing Diagram

## 8.2.3.2 MII Receive AC Timing Specifications

This table provides the MII receive AC timing specifications.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min  | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                 | t <sub>MRX</sub> 2                  | _    | 400 | _   | ns   |

| RX_CLK clock period 100 Mbps                | t <sub>MRX</sub>                    |      | 40  |     | ns   |

| RX_CLK duty cycle                           | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | _   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub>                 | 10.0 | _   | _   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub>                 | 10.0 | _   | _   | ns   |

| RX_CLK clock rise (20%–80%)                 | t <sub>MRXR</sub> <sup>2</sup>      | 1.0  | _   | 4.0 | ns   |

| RX_CLK clock fall time (80%–20%)            | t <sub>MRXF</sub> <sup>2</sup>      | 1.0  | _   | 4.0 | ns   |

Notes:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

2. Guaranteed by design.

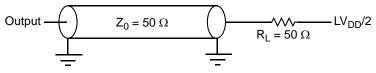

Figure 12 provides the AC test load for eTSEC.

Figure 12. eTSEC AC Test Load

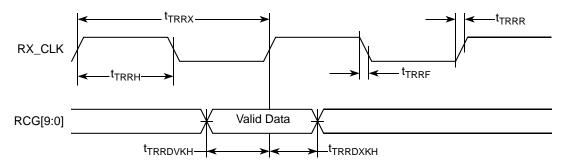

A timing diagram for TBI receive appears in Figure 16.

Figure 16. TBI Single-Clock Mode Receive AC Timing Diagram

## 8.2.6 RGMII and RTBI AC Timing Specifications

This table presents the RGMII and RTBI AC timing specifications.

| Parameter/Condition                                    | Symbol <sup>1</sup>                   | Min               | Тур | Max              | Unit |

|--------------------------------------------------------|---------------------------------------|-------------------|-----|------------------|------|

| Data to clock output skew (at transmitter)             | t <sub>SKRGT</sub> 5                  | -500 <sup>6</sup> | 0   | 500 <sup>6</sup> | ps   |

| Data to clock input skew (at receiver) <sup>2</sup>    | t <sub>SKRGT</sub>                    | 1.0               | _   | 2.8              | ns   |

| Clock period <sup>3</sup>                              | t <sub>RGT</sub> 5                    | 7.2               | 8.0 | 8.8              | ns   |

| Duty cycle for 10BASE-T and 100BASE-TX <sup>3, 4</sup> | t <sub>RGTH</sub> /t <sub>RGT</sub> 5 | 45                | 50  | 55               | %    |

| Rise time (20%–80%)                                    | t <sub>RGTR</sub> 5                   | _                 | _   | 0.75             | ns   |

| Fall time (20%–80%)                                    | t <sub>RGTF</sub> 5                   | _                 |     | 0.75             | ns   |

## Table 33. RGMII and RTBI AC Timing Specifications

Notes:

In general, the clock reference symbol representation for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the TBI (T) receive (RX) clock. Note also that the notation for rise (R) and fall (F) times follows the clock symbol that is being represented. For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (RGT).

- 2. This implies that PC board design requires clocks to be routed such that an additional trace delay of greater than 1.5 ns is added to the associated clock signal.

- 3. For 10 and 100 Mbps,  $t_{RGT}$  scales to 400 ns  $\pm$  40 ns and 40 ns  $\pm$  4 ns, respectively.

- 4. Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned between.

5. Guaranteed by characterization.

6. In rev 1.0 silicon, due to errata, t<sub>SKRGT</sub> is -650 ps (min) and 650 ps (max). See "eTSEC 10" in the device errata document.

# 10 Local Bus

This section describes the DC and AC electrical specifications for the local bus interface of the device.

# **10.1** Local Bus DC Electrical Characteristics

This table provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 3.3 \text{ V DC}$ .

| Parameter                                                       | Symbol          | Min  | Мах                    | Unit |

|-----------------------------------------------------------------|-----------------|------|------------------------|------|

| High-level input voltage                                        | V <sub>IH</sub> | 2    | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                         | V <sub>IL</sub> | -0.3 | 0.8                    | V    |

| Input current $(V_{IN}^{1} = 0 V \text{ or } V_{IN} = BV_{DD})$ | I <sub>IN</sub> | _    | ±5                     | μA   |

| High-level output voltage ( $BV_{DD} = min, I_{OH} = -2 mA$ )   | V <sub>OH</sub> | 2.4  | —                      | V    |

| Low-level output voltage ( $BV_{DD} = min$ , $I_{OL} = 2 mA$ )  | V <sub>OL</sub> | —    | 0.4                    | V    |

Table 38. Local Bus DC Electrical Characteristics (3.3 V DC)

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1 and Table 2.

Table 39 provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 2.5 \text{ V DC}$ .

Table 39. Local Bus DC Electrical Characteristics (2.5 V DC)

| Parameter                                                       | Symbol          | Min  | Max                    | Unit |

|-----------------------------------------------------------------|-----------------|------|------------------------|------|

| High-level input voltage                                        | V <sub>IH</sub> | 1.70 | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                         | V <sub>IL</sub> | -0.3 | 0.7                    | V    |

| Input current $(V_{IN}^{1} = 0 V \text{ or } V_{IN} = BV_{DD})$ | I <sub>IH</sub> | _    | 10                     | μA   |

|                                                                 | I               |      | -15                    |      |

| High-level output voltage ( $BV_{DD} = min, I_{OH} = -1 mA$ )   | V <sub>OH</sub> | 2.0  | —                      | V    |

| Low-level output voltage ( $BV_{DD} = min$ , $I_{OL} = 1 mA$ )  | V <sub>OL</sub> | _    | 0.4                    | V    |

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1 and Table 2.

## NOTE

PLL bypass mode is required when LBIU frequency is at or below 83 MHz. When LBIU operates above 83 MHz, LBIU PLL is recommended to be enabled.

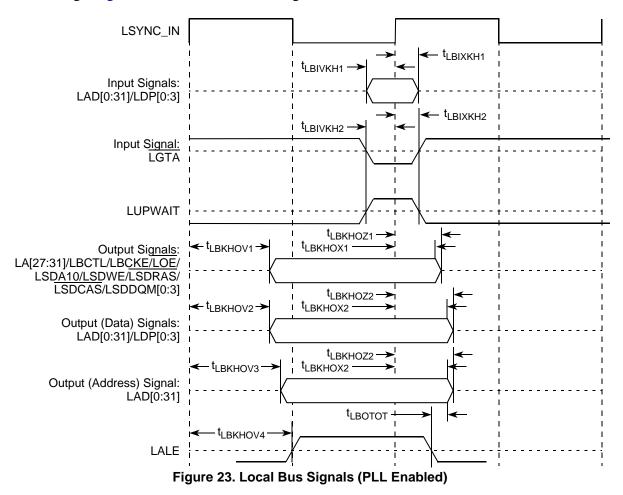

Figure 23 through Figure 28 show the local bus signals.

This table describes the timing parameters of the local bus interface at  $BV_{DD} = 3.3$  V with PLL disabled.

| Parameter                                             | Symbol <sup>1</sup>                 | Min  | Max | Unit | Notes |

|-------------------------------------------------------|-------------------------------------|------|-----|------|-------|

| Local bus cycle time                                  | t <sub>LBK</sub>                    | 12   | _   | ns   | 2     |

| Local bus duty cycle                                  | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43   | 57  | %    | _     |

| Internal launch/capture clock to LCLK delay           | t <sub>LBKHKT</sub>                 | 2.3  | 4.4 | ns   | 8     |

| Input setup to local bus clock (except LGTA/LUPWAIT)  | t <sub>LBIVKH1</sub>                | 6.2  | _   | ns   | 4, 5  |

| LGTA/LUPWAIT input setup to local bus clock           | t <sub>LBIVKL2</sub>                | 6.1  | _   | ns   | 4, 5  |

| Input hold from local bus clock (except LGTA/LUPWAIT) | t <sub>LBIXKH1</sub>                | -1.8 | _   | ns   | 4, 5  |

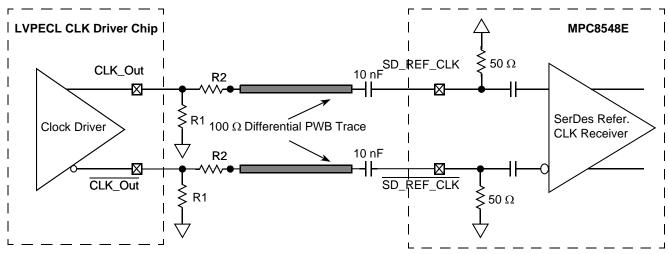

to AC-coupling. Its value could be ranged from 140 to 240  $\Omega$  depending on the clock driver vendor's requirement. R2 is used together with the SerDes reference clock receiver's 50- $\Omega$  termination resistor to attenuate the LVPECL output's differential peak level such that it meets the SerDes reference clock's differential input amplitude requirement (between 200 and 800 mV differential peak). For example, if the LVPECL output's differential peak is 900 mV and the desired SerDes reference clock input amplitude is selected as 600 mV, the attenuation factor is 0.67, which requires R2 = 25  $\Omega$ . Consult a clock driver chip manufacturer to verify whether this connection scheme is compatible with a particular clock driver chip.

Figure 45. AC-Coupled Differential Connection with LVPECL Clock Driver (Reference Only)

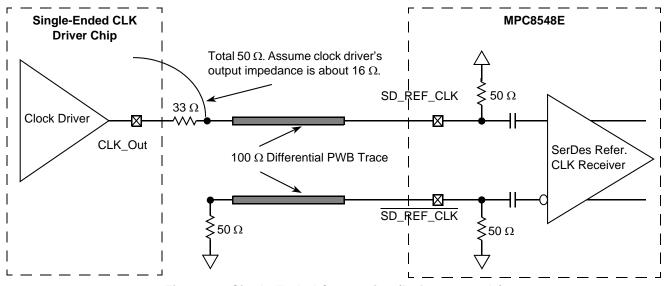

Figure 46 shows the SerDes reference clock connection reference circuits for a single-ended clock driver. It assumes the DC levels of the clock driver are compatible with the SerDes reference clock input's DC requirement.

Figure 46. Single-Ended Connection (Reference Only)

| Symbol                                      | Parameter                                                                                    | Min    | Nom  | Мах    | Unit | Comments                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------|----------------------------------------------------------------------------------------------|--------|------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI                                          | Unit interval                                                                                | 399.88 | 400  | 400.12 | ps   | Each UI is 400 ps ± 300 ppm. UI does not account<br>for spread spectrum clock dictated variations.<br>See Note 1.                                                                                                                                                                                                                                                                        |

| V <sub>TX-DIFFp-p</sub>                     | Differential<br>peak-to-peak<br>output voltage                                               | 0.8    | —    | 1.2    | V    | $V_{TX-DIFFp-p} = 2 \times  V_{TX-D+} - V_{TX-D-} $ . See Note 2.                                                                                                                                                                                                                                                                                                                        |

| V <sub>TX-DE-RATIO</sub>                    | De-emphasized<br>differential<br>output voltage<br>(ratio)                                   | -3.0   | -3.5 | -4.0   | dB   | Ratio of the $V_{TX-DIFFp-p}$ of the second and following bits after a transition divided by the $V_{TX-DIFFp-p}$ of the first bit after a transition. See Note 2.                                                                                                                                                                                                                       |

| T <sub>TX-EYE</sub>                         | Minimum TX<br>eye width                                                                      | 0.70   | _    | _      | UI   | The maximum transmitter jitter can be derived as $T_{TX-MAX-JITTER} = 1 - T_{TX-EYE} = 0.3$ UI.<br>See Notes 2 and 3.                                                                                                                                                                                                                                                                    |

| T <sub>TX-EYE-MEDIAN-to-</sub> MAX-JITTER   | Maximum time<br>between the<br>jitter median and<br>maximum<br>deviation from<br>the median. | _      |      | 0.15   | UI   | Jitter is defined as the measurement variation of<br>the crossing points ( $V_{TX-DIFFp-p} = 0$ V) in relation<br>to a recovered TX UI. A recovered TX UI is<br>calculated over 3500 consecutive unit intervals of<br>sample data. Jitter is measured using all edges of<br>the 250 consecutive UI in the center of the 3500<br>UI used for calculating the TX UI.<br>See Notes 2 and 3. |

| T <sub>TX-RISE</sub> , T <sub>TX-FALL</sub> | D+/D-TX output<br>rise/fall time                                                             | 0.125  | _    | —      | UI   | See Notes 2 and 5.                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>TX-CM-ACp</sub>                      | RMS AC peak<br>common mode<br>output voltage                                                 |        |      | 20     | mV   | $\begin{split} & V_{TX\text{-}CM\text{-}ACp} = RMS( V_{TXD\text{+}} + V_{TXD\text{-}} /2 - V_{TX\text{-}CM\text{-}DC}) \\ & V_{TX\text{-}CM\text{-}DC} = DC_{(avg)} \text{ of }  V_{TX\text{-}D\text{+}} + V_{TX\text{-}D\text{-}} /2. \\ & See Note 2. \end{split}$                                                                                                                     |

| V <sub>TX-CM-DC-ACTIVE-</sub> IDLE-DELTA    | Absolute delta of<br>dc common<br>mode voltage<br>during L0 and<br>electrical idle           | 0      | _    | 100    | mV   | $\begin{split}  V_{TX-CM-DC} & (during L0) + V_{TX-CM-Idle-DC} & (during electrical idle)  \leq 100 mV \\ V_{TX-CM-DC} &= DC_{(avg)} & of  V_{TX-D+} + V_{TX-D-} /2 \ [L0] \\ V_{TX-CM-Idle-DC} &= DC_{(avg)} & of  V_{TX-D+} + V_{TX-D-} /2 \\ [electrical idle] \\ See Note 2. \end{split}$                                                                                            |

| V <sub>TX-CM</sub> -DC-LINE-DELTA           | Absolute delta of<br>DC common<br>mode between<br>D+ and D–                                  | 0      |      | 25     | mV   | $\begin{split}  V_{TX-CM-DC-D+} - V_{TX-CM-DC-D-}  &\leq 25 \text{ mV} \\ V_{TX-CM-DC-D+} &= DC_{(avg)} \text{ of }  V_{TX-D+}  \\ V_{TX-CM-DC-D-} &= DC_{(avg)} \text{ of }  V_{TX-D-} . \\ \text{See Note 2.} \end{split}$                                                                                                                                                             |

| V <sub>TX</sub> -IDLE-DIFFp                 | Electrical idle<br>differential peak<br>output voltage                                       | 0      | _    | 20     | mV   | $V_{TX-IDLE-DIFFp} =  V_{TX-IDLE-D+} - V_{TX-IDLE-D-}  \le 20 \text{ mV.}$<br>See Note 2.                                                                                                                                                                                                                                                                                                |

| V <sub>TX-RCV-DETECT</sub>                  | The amount of<br>voltage change<br>allowed during<br>receiver<br>detection                   |        |      | 600    | mV   | The total amount of voltage change that a transmitter can apply to sense whether a low impedance receiver is present. See Note 6.                                                                                                                                                                                                                                                        |

### **PCI Express**

Figure 48. Minimum Transmitter Timing and Voltage Output Compliance Specifications

# 17.4.3 Differential Receiver (RX) Input Specifications

Table 57 defines the specifications for the differential input at all receivers (RXs). The parameters are specified at the component pins.

| Symbol                                       | Parameter                                                                                   | Min    | Nom | Max    | Unit | Comments                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------|---------------------------------------------------------------------------------------------|--------|-----|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI                                           | Unit interval                                                                               | 399.88 | 400 | 400.12 | ps   | Each UI is 400 ps $\pm$ 300 ppm. UI does not account<br>for spread spectrum clock dictated variations.<br>See Note 1.                                                                                                                                                                                                                                                                        |

| V <sub>RX-DIFFp-p</sub>                      | Differential<br>peak-to-peak<br>input voltage                                               | 0.175  | —   | 1.200  | V    | $V_{RX-DIFFp-p} = 2 \times  V_{RX-D+} - V_{RX-D-} $ . See Note 2.                                                                                                                                                                                                                                                                                                                            |

| T <sub>RX-EYE</sub>                          | Minimum<br>receiver eye<br>width                                                            | 0.4    | _   | _      | UI   | The maximum interconnect media and transmitter jitter that can be tolerated by the receiver can be derived as $T_{RX-MAX-JITTER} = 1 - T_{RX-EYE} = 0.6$ UI. See Notes 2 and 3.                                                                                                                                                                                                              |

| T <sub>RX-EYE-MEDIAN-to-</sub><br>MAX-JITTER | Maximum time<br>between the<br>jitter median and<br>maximum<br>deviation from<br>the median | —      |     | 0.3    | UI   | Jitter is defined as the measurement variation of<br>the crossing points ( $V_{RX-DIFFp-p} = 0$ V) in relation<br>to a recovered TX UI. A recovered TX UI is<br>calculated over 3500 consecutive unit intervals of<br>sample data. Jitter is measured using all edges of<br>the 250 consecutive UI in the center of the<br>3500 UI used for calculating the TX UI.<br>See Notes 2, 3, and 7. |

Table 57. Differential Receiver (RX) Input Specifications

# 18 Serial RapidIO

This section describes the DC and AC electrical specifications for the RapidIO interface of the MPC8548E, for the LP-Serial physical layer. The electrical specifications cover both single- and multiple-lane links. Two transmitters (short and long run) and a single receiver are specified for each of three baud rates, 1.25, 2.50, and 3.125 GBaud.

Two transmitter specifications allow for solutions ranging from simple board-to-board interconnect to driving two connectors across a backplane. A single receiver specification is given that accepts signals from both the short- and long-run transmitter specifications.

The short-run transmitter must be used mainly for chip-to-chip connections on either the same printed-circuit board or across a single connector. This covers the case where connections are made to a mezzanine (daughter) card. The minimum swings of the short-run specification reduce the overall power used by the transceivers.

The long-run transmitter specifications use larger voltage swings that are capable of driving signals across backplanes. This allows a user to drive signals across two connectors and a backplane. The specifications allow a distance of at least 50 cm at all baud rates.

All unit intervals are specified with a tolerance of  $\pm 100$  ppm. The worst case frequency difference between any transmit and receive clock is 200 ppm.

To ensure interoperability between drivers and receivers of different vendors and technologies, AC coupling at the receiver input must be used.

# 18.1 <u>DC Requirements</u> for Serial RapidIO SD\_REF\_CLK and SD\_REF\_CLK

For more information, see Section 16.2, "SerDes Reference Clocks."

# 18.2 <u>AC Requirements</u> for Serial RapidIO SD\_REF\_CLK and SD\_REF\_CLK

Table 58 lists the Serial RapidIO SD\_REF\_CLK and SD\_REF\_CLK AC requirements.

| Symbol             | Parameter Description                                                                     | Min | Тур   | Мах | Unit | Comments                                                               |

|--------------------|-------------------------------------------------------------------------------------------|-----|-------|-----|------|------------------------------------------------------------------------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                         | —   | 10(8) | —   | ns   | 8 ns applies only to serial<br>RapidIO with 125-MHz reference<br>clock |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles. | —   | —     | 80  | ps   | _                                                                      |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location.              | -40 | —     | 40  | ps   | _                                                                      |

## Table 58. SD\_REF\_CLK and SD\_REF\_CLK AC Requirements

# 18.3 Signal Definitions

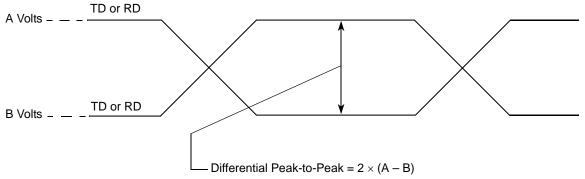

LP-serial links use differential signaling. This section defines terms used in the description and specification of differential signals. Figure 51 shows how the signals are defined. The figures show waveforms for either a transmitter output (TD and  $\overline{TD}$ ) or a receiver input (RD and  $\overline{RD}$ ). Each signal swings between A volts and B volts where A > B. Using these waveforms, the definitions are as follows:

- 1. The transmitter output signals and the receiver input signals TD,  $\overline{\text{TD}}$ , RD, and  $\overline{\text{RD}}$  each have a peak-to-peak swing of A B volts.

- 2. The differential output signal of the transmitter,  $V_{OD}$ , is defined as  $V_{TD} V_{\overline{TD}}$ .

- 3. The differential input signal of the receiver,  $V_{ID}$ , is defined as  $V_{RD} V_{\overline{RD}}$ .

- 4. The differential output signal of the transmitter and the differential input signal of the receiver each range from A B to -(A B) volts.

- 5. The peak value of the differential transmitter output signal and the differential receiver input signal is A B volts.

- 6. The peak-to-peak value of the differential transmitter output signal and the differential receiver input signal is  $2 \times (A B)$  volts.

Figure 51. Differential Peak–Peak Voltage of Transmitter or Receiver

To illustrate these definitions using real values, consider the case of a CML (current mode logic) transmitter that has a common mode voltage of 2.25 V and each of its outputs, TD and TD, has a swing that goes between 2.5 and 2.0 V. Using these values, the peak-to-peak voltage swing of the signals TD and TD is 500 mVp-p. The differential output signal ranges between 500 and -500 mV. The peak differential voltage is 500 mV. The peak-to-peak differential voltage is 1000 mVp-p.

# 18.4 Equalization

With the use of high-speed serial links, the interconnect media causes degradation of the signal at the receiver. Effects such as inter-symbol interference (ISI) or data dependent jitter are produced. This loss can be large enough to degrade the eye opening at the receiver beyond what is allowed in the specification. To negate a portion of these effects, equalization can be used. The most common equalization techniques that can be used are:

- A passive high pass filter network placed at the receiver. This is often referred to as passive equalization.

- The use of active circuits in the receiver. This is often referred to as adaptive equalization.

| Characteristic                                     | Symbol          | Range |                   | Unit   | Notes                                                        |

|----------------------------------------------------|-----------------|-------|-------------------|--------|--------------------------------------------------------------|

| Characteristic                                     | Symbol          | Min   | Max               | Onit   | NOICES                                                       |

| Differential input voltage                         | V <sub>IN</sub> | 200   | 1600              | mVp-p  | Measured at receiver                                         |

| Deterministic jitter tolerance                     | J <sub>D</sub>  | 0.37  | —                 | UI p-p | Measured at receiver                                         |

| Combined deterministic and random jitter tolerance | J <sub>DR</sub> | 0.55  | —                 | UI p-p | Measured at receiver                                         |

| Total jitter tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65  | _                 | UI p-p | Measured at receiver                                         |

| Multiple input skew                                | S <sub>MI</sub> | _     | 22                | ns     | Skew at the receiver input between lanes of a multilane link |

| Bit error rate                                     | BER             | _     | 10 <sup>-12</sup> |        | —                                                            |

| Unit interval                                      | UI              | 320   | 320               | ps     | ±100 ppm                                                     |

| Table 68. | <b>Receiver A</b> | C Timing | Specifications- | -3.125 GBaud |

|-----------|-------------------|----------|-----------------|--------------|

|-----------|-------------------|----------|-----------------|--------------|

## Note:

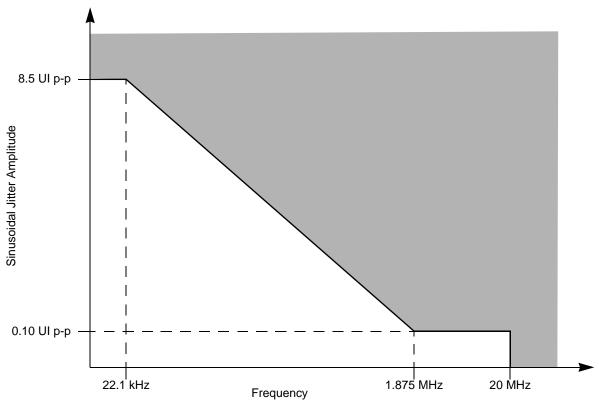

1. Total jitter is composed of three components, deterministic jitter, random jitter and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 53. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk and other variable system effects.

Figure 53. Single Frequency Sinusoidal Jitter Limits

### **Package Description**

## Notes:

- 1. All dimensions are in millimeters.

- 2. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 5. Parallelism measurement shall exclude any effect of mark on top surface of package.

- 6. All dimensions are symmetric across the package center lines unless dimensioned otherwise.

### Package Description

## Table 71. MPC8548E Pinout Listing (continued)

| Signal                                                                                                             | Package Pin Number                                                                                                                                                                                                                                                                                     | Pin Type                                                      | Power<br>Supply                                          | Notes                        |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------|------------------------------|

| 25.These are test signals for factory u                                                                            | ise only and must be pulled up (100 $\Omega$ –1 k $\Omega$ ) to                                                                                                                                                                                                                                        | OV <sub>DD</sub> for normal                                   | machine oper                                             | ration.                      |

| 26.Independent supplies derived from                                                                               | n board V <sub>DD</sub> .                                                                                                                                                                                                                                                                              |                                                               |                                                          |                              |

| 27.Recommend a pull-up resistor (~1                                                                                | $k\Omega$ ) be placed on this pin to $OV_{DD}$ .                                                                                                                                                                                                                                                       |                                                               |                                                          |                              |

|                                                                                                                    | oul <u>led down du</u> ring power-on reset: TSEC3_TXD<br>Y/QUIESCE, MSRCID[2:4], ASLEEP.                                                                                                                                                                                                               | [3], TSEC4_TXD                                                | 93/TSEC3_TX                                              | D7,                          |

| 30.This pin requires an external 4.7-ks driven.                                                                    | 2 pull-down resistor to prevent PHY from seeing a                                                                                                                                                                                                                                                      | valid transmit en                                             | able before it i                                         | s active                     |

| 31.This pin is only an output in eTSE                                                                              | C3 FIFO mode when used as Rx flow control.                                                                                                                                                                                                                                                             |                                                               |                                                          |                              |

| 32. These pins must be connected to 2                                                                              | XV <sub>DD</sub> .                                                                                                                                                                                                                                                                                     |                                                               |                                                          |                              |

| 33. <u>TSEC2_</u> TXD1, TSEC2_TX_ER ar<br>HRESET assertion.                                                        | e multiplexed as cfg_dram_type[0:1]. They must                                                                                                                                                                                                                                                         | be valid at powe                                              | er-up, even bet                                          | fore                         |

| 34.These pins must be pulled to grou                                                                               | nd through a 300- $\Omega$ (±10%) resistor.                                                                                                                                                                                                                                                            |                                                               |                                                          |                              |

| down to select external arbiter if the<br>connect' or terminated through 2–1<br>connected to any other PCI device. | er the POR config pin that selects between inter<br>ere is any other PCI device connected on the PC<br>0 k $\Omega$ pull-up resistors with the default of internal<br>. The PCI block drives the PCI <i>n</i> _AD pins if it is con-<br>thether it is disabled via the DEVDISR register of<br>the bus. | l bus, or leave th<br>arbiter if the PC<br>onfigured to be th | e PCI <i>n_</i> AD pi<br>n_AD pins are<br>e PCI arbiter– | ns as 'n<br>e not<br>–throug |

|                                                                                                                    | $2-\Omega$ precision 1% resistor and MDIC1 is connector automatic calibration of the DDR IOs.                                                                                                                                                                                                          | ed to GV <sub>DD</sub> throu                                  | gh an 18.2-Ω                                             | precisio                     |

| 38.These pins must be left floating.                                                                               |                                                                                                                                                                                                                                                                                                        |                                                               |                                                          |                              |

| 39. If PCI1 or PCI2 is configured as P<br>Otherwise the processor will not be                                      | CI asynchronous mode, a valid clock must be pr<br>oot up.                                                                                                                                                                                                                                              | ovided on pin PC                                              | CI1_CLK or PC                                            | CI2_CL                       |

| 40.These pins must be connected to                                                                                 | GND.                                                                                                                                                                                                                                                                                                   |                                                               |                                                          |                              |

| 101.This pin requires an external 4.7-                                                                             | $k\Omega$ resistor to GND.                                                                                                                                                                                                                                                                             |                                                               |                                                          |                              |

| 102.For Rev. 2.x silicon, DMA_DACK<br>POR configuration are don't care.                                            | [0:1] must be 0b11 during POR configuration; for                                                                                                                                                                                                                                                       | r rev. 1.x silicon, t                                         | the pin values                                           | during                       |

| 103.If these pins are not used as GPI<br>2–10 kΩ resistors.                                                        | Nn (general-purpose input), they must be pulled                                                                                                                                                                                                                                                        | low (to GND) or                                               | high (to LV <sub>DD</sub> )                              | ) throug                     |

| 104.These must be pulled low to GNI                                                                                | D through 2–10 k $\Omega$ resistors if they are not used.                                                                                                                                                                                                                                              |                                                               |                                                          |                              |

|                                                                                                                    | to $\text{LV}_{\text{DD}}$ through 2–10 k $\Omega$ resistors if they are no                                                                                                                                                                                                                            |                                                               |                                                          |                              |

| 106.For rev. 2.x silicon, DMA_DACK[(<br>configuration are don't care.                                              | ):1] must be 0b10 during POR configuration; for re                                                                                                                                                                                                                                                     | ev. 1.x silicon, the                                          | pin values du                                            | ring PO                      |

| 107.For rev. 2.x silicon, DMA_DACK[0 configuration are don't care.                                                 | ):1] must be 0b01 during POR configuration; for re                                                                                                                                                                                                                                                     | ev. 1.x silicon, the                                          | pin values du                                            | ring PO                      |

| 108.For rev. 2.x silicon, DMA_DACK[C configuration are don't care.                                                 | 0:1] must be 0b11 during POR configuration; for re                                                                                                                                                                                                                                                     | ev. 1.x silicon, the                                          | pin values du                                            | ring PO                      |

| 109.This is a test signal for factory us                                                                           | e only and must be pulled down (100 $\Omega$ – 1 k $\Omega$ )                                                                                                                                                                                                                                          | to GND for norm                                               | al machine op                                            | eration.                     |

| 110.These pins must be pulled high to                                                                              | o OV <sub>DD</sub> through 2–10 k $\Omega$ resistors.                                                                                                                                                                                                                                                  |                                                               |                                                          |                              |

| 111.If these pins are not used as GPII 2–10 k $\Omega$ resistors.                                                  | Nn (general-purpose input), they must be pulled                                                                                                                                                                                                                                                        | low (to GND) or I                                             | high (to OV <sub>DD</sub> )                              | ) throug                     |

| 112.This pin must not be pulled down                                                                               | during POR configuration.                                                                                                                                                                                                                                                                              |                                                               |                                                          |                              |

|                                                                                                                    |                                                                                                                                                                                                                                                                                                        |                                                               |                                                          |                              |

Package Description

| Signal                | Package Pin Number                              | Pin Type | Power<br>Supply  | Notes |

|-----------------------|-------------------------------------------------|----------|------------------|-------|

| UDE                   | AH16                                            | I        | OV <sub>DD</sub> | _     |

| MCP                   | AG19                                            | I        | OV <sub>DD</sub> | _     |

| IRQ[0:7]              | AG23, AF18, AE18, AF20, AG18, AF17, AH24, AE20  | I        | OV <sub>DD</sub> | -     |

| IRQ[8]                | AF19                                            | AF19 I   |                  | —     |

| IRQ[9]/DMA_DREQ3      | AF21                                            | I        | OV <sub>DD</sub> | 1     |

| IRQ[10]/DMA_DACK3     | AE19                                            | I/O      | OV <sub>DD</sub> | 1     |

| IRQ[11]/DMA_DDONE3    | AD20                                            | I/O      | OV <sub>DD</sub> | 1     |

| IRQ_OUT               | AD18                                            | 0        | OV <sub>DD</sub> | 2, 4  |

|                       | Ethernet Management Interface                   |          | 1                |       |

| EC_MDC                | AB9                                             | 0        | OV <sub>DD</sub> | 5, 9  |

| EC_MDIO               | AC8                                             | I/O      | OV <sub>DD</sub> | _     |

|                       | Gigabit Reference Clock                         |          |                  |       |

| EC_GTX_CLK125         | V11                                             | I        | LV <sub>DD</sub> |       |

|                       | Three-Speed Ethernet Controller (Gigabit Ethern | et 1)    | 1                |       |

| TSEC1_RXD[7:0]        | R5, U1, R3, U2, V3, V1, T3, T2                  | I        | LV <sub>DD</sub> |       |

| TSEC1_TXD[7:0]        | T10, V7, U10, U5, U4, V6, T5, T8                | 0        | LV <sub>DD</sub> | 5, 9  |

| TSEC1_COL             | R4                                              | I        | LV <sub>DD</sub> |       |

| TSEC1_CRS             | V5                                              | I/O      | LV <sub>DD</sub> | 20    |

| TSEC1_GTX_CLK         | U7                                              | 0        | LV <sub>DD</sub> |       |

| TSEC1_RX_CLK          | U3                                              | I        | LV <sub>DD</sub> |       |

| TSEC1_RX_DV           | V2                                              | I        | LV <sub>DD</sub> | _     |

| TSEC1_RX_ER           | T1                                              | I        | LV <sub>DD</sub> | _     |

| TSEC1_TX_CLK          | Т6                                              | I        | LV <sub>DD</sub> |       |

| TSEC1_TX_EN           | U9                                              | 0        | LV <sub>DD</sub> | 30    |

| TSEC1_TX_ER           | Τ7                                              | 0        | LV <sub>DD</sub> | _     |

| GPIN[0:7]             | P2, R2, N1, N2, P3, M2, M1, N3                  | I        | LV <sub>DD</sub> | 103   |

| GPOUT[0:5]            | N9, N10, P8, N7, R9, N5                         | 0        | LV <sub>DD</sub> | _     |

| cfg_dram_type0/GPOUT6 | R8                                              | 0        | LV <sub>DD</sub> | 5, 9  |

| GPOUT7                | N6                                              | 0        | LV <sub>DD</sub> | —     |

| Reserved              | P1                                              | _        | _                | 104   |

| Reserved              | R6                                              |          | —                | 104   |

| Reserved              | P6                                              |          | _                | 15    |

| Reserved              | N4                                              | _        | _                | 105   |

| Signal             | Package Pin Number                             | Pin Type | Power<br>Supply  | Notes     |

|--------------------|------------------------------------------------|----------|------------------|-----------|

| LSYNC_IN           | F27                                            | I        | BV <sub>DD</sub> | —         |

| LSYNC_OUT          | F28                                            | 0        | BV <sub>DD</sub> | —         |

|                    | DMA                                            |          |                  |           |

| DMA_DACK[0:1]      | AD3, AE1                                       | 0        | OV <sub>DD</sub> | 5, 9, 108 |

| DMA_DREQ[0:1]      | AD4, AE2                                       | I        | OV <sub>DD</sub> | —         |

| DMA_DDONE[0:1]     | AD2, AD1                                       | 0        | OV <sub>DD</sub> | —         |

|                    | Programmable Interrupt Controller              |          |                  | 1         |

| UDE                | AH16                                           | Ι        | OV <sub>DD</sub> | —         |

| MCP                | AG19                                           | I        | OV <sub>DD</sub> | —         |

| IRQ[0:7]           | AG23, AF18, AE18, AF20, AG18, AF17, AH24, AE20 | I        | $OV_{DD}$        | -         |

| IRQ[8]             | AF19                                           | I        | OV <sub>DD</sub> | —         |

| IRQ[9]/DMA_DREQ3   | AF21                                           | I        | OV <sub>DD</sub> | 1         |

| IRQ[10]/DMA_DACK3  | AE19                                           | I/O      | OV <sub>DD</sub> | 1         |

| IRQ[11]/DMA_DDONE3 | AD20                                           | I/O      | OV <sub>DD</sub> | 1         |

| IRQ_OUT            | AD18                                           | 0        | OV <sub>DD</sub> | 2, 4      |

|                    | Ethernet Management Interface                  |          |                  | 1         |

| EC_MDC             | AB9                                            | 0        | OV <sub>DD</sub> | 5, 9      |

| EC_MDIO            | AC8                                            | I/O      | OV <sub>DD</sub> | —         |

|                    | Gigabit Reference Clock                        |          |                  |           |

| EC_GTX_CLK125      | V11                                            | Ι        | $LV_{DD}$        | —         |

|                    | Three-Speed Ethernet Controller (Gigabit Ether | rnet 1)  |                  | •         |

| TSEC1_RXD[7:0]     | R5, U1, R3, U2, V3, V1, T3, T2                 | Ι        | LV <sub>DD</sub> | —         |

| TSEC1_TXD[7:0]     | T10, V7, U10, U5, U4, V6, T5, T8               | 0        | LV <sub>DD</sub> | 5, 9      |

| TSEC1_COL          | R4                                             | I        | LV <sub>DD</sub> | —         |

| TSEC1_CRS          | V5                                             | I/O      | LV <sub>DD</sub> | 20        |

| TSEC1_GTX_CLK      | U7                                             | 0        | LV <sub>DD</sub> | —         |

| TSEC1_RX_CLK       | U3                                             | I        | LV <sub>DD</sub> | _         |

| TSEC1_RX_DV        | V2                                             | I        | LV <sub>DD</sub> | _         |

| TSEC1_RX_ER        | T1                                             | I        | LV <sub>DD</sub> | -         |

| TSEC1_TX_CLK       | Т6                                             | I        | LV <sub>DD</sub> | —         |

| TSEC1_TX_EN        | U9                                             | 0        | LV <sub>DD</sub> | 30        |

| TSEC1_TX_ER        | Τ7                                             | 0        | LV <sub>DD</sub> | —         |

| GPIN[0:7]          | P2, R2, N1, N2, P3, M2, M1, N3                 | I        | LV <sub>DD</sub> | 103       |

| Signal                | Package Pin Number                    | Pin Type    | Power<br>Supply  | Notes    |

|-----------------------|---------------------------------------|-------------|------------------|----------|

| GPOUT[0:5]            | N9, N10, P8, N7, R9, N5               | 0           | LV <sub>DD</sub> |          |

| cfg_dram_type0/GPOUT6 | R8                                    | 0           | LV <sub>DD</sub> | 5, 9     |

| GPOUT7                | N6                                    | 0           | LV <sub>DD</sub> | -        |

| Reserved              | P1                                    | —           | _                | 104      |

| Reserved              | R6                                    | —           | _                | 104      |

| Reserved              | P6                                    | —           | —                | 15       |

| Reserved              | N4                                    | —           | _                | 105      |

| FIFO1_RXC2            | P5                                    | I           | LV <sub>DD</sub> | 104      |

| Reserved              | R1                                    | —           | _                | 104      |

| Reserved              | P10                                   | —           | _                | 105      |

| FIFO1_TXC2            | P7                                    | 0           | LV <sub>DD</sub> | 15       |

| cfg_dram_type1        | R10                                   | 0           | LV <sub>DD</sub> | 5, 9     |

| Thre                  | ee-Speed Ethernet Controller (Gigabit | Ethernet 3) |                  |          |

| TSEC3_TXD[3:0]        | V8, W10, Y10, W7                      | 0           | TV <sub>DD</sub> | 5, 9, 2  |

| TSEC3_RXD[3:0]        | Y1, W3, W5, W4                        | I           | TV <sub>DD</sub> | _        |

| TSEC3_GTX_CLK         | W8                                    | 0           | TV <sub>DD</sub> | _        |

| TSEC3_RX_CLK          | W2                                    | I           | TV <sub>DD</sub> | <b>—</b> |

| TSEC3_RX_DV           | W1                                    | I           | TV <sub>DD</sub> | _        |

| TSEC3_RX_ER           | Y2                                    | I           | TV <sub>DD</sub> | _        |

| TSEC3_TX_CLK          | V10                                   | I           | TV <sub>DD</sub> | _        |

| TSEC3_TX_EN           | V9                                    | 0           | TV <sub>DD</sub> | 30       |

| TSEC3_TXD[7:4]        | AB8, Y7, AA7, Y8                      | 0           | TV <sub>DD</sub> | 5, 9, 2  |

| TSEC3_RXD[7:4]        | AA1, Y3, AA2, AA4                     | I           | TV <sub>DD</sub> | _        |

| Reserved              | AA5                                   | _           | _                | 15       |

| TSEC3_COL             | Y5                                    | I           | TV <sub>DD</sub> | -        |

| TSEC3_CRS             | AA3                                   | I/O         | TV <sub>DD</sub> | 31       |

| TSEC3_TX_ER           | AB6                                   | 0           | TV <sub>DD</sub> | -        |

|                       | DUART                                 | 1           |                  |          |

| UART_CTS[0:1]         | AB3, AC5                              | I           | OV <sub>DD</sub> | -        |

| UART_RTS[0:1]         | AC6, AD7                              | 0           | OV <sub>DD</sub> | 1 -      |

| UART_SIN[0:1]         | AB5, AC7                              | I           |                  |          |

| UART_SOUT[0:1]        | AB7, AD8                              | 0           | OV <sub>DD</sub> | <u> </u> |

|                       | I <sup>2</sup> C interface            | I           |                  | _1       |

| IIC1_SCL              | AG22                                  | I/O         | OV <sub>DD</sub> | 4, 27    |

|                       |                                       |             |                  | _1       |

## Table 74. MPC8543E Pinout Listing (continued)

# 20.3 e500 Core PLL Ratio

This table describes the clock ratio between the e500 core complex bus (CCB) and the e500 core clock. This ratio is determined by the binary value of LBCTL, LALE, and LGPL2 at power up, as shown in this table.

| Binary Value of<br>LBCTL, LALE, LGPL2<br>Signals | e500 core:CCB Clock Ratio | Binary Value of<br>LBCTL, LALE, LGPL2<br>Signals | e500 core:CCB Clock Ratio |

|--------------------------------------------------|---------------------------|--------------------------------------------------|---------------------------|

| 000                                              | 4:1                       | 100                                              | 2:1                       |

| 001                                              | 9:2                       | 101                                              | 5:2                       |

| 010                                              | Reserved                  | 110                                              | 3:1                       |

| 011                                              | 3:2                       | 111                                              | 7:2                       |

| Table 82. e500 ( | Core to CCB | <b>Clock Ratio</b> |

|------------------|-------------|--------------------|

|------------------|-------------|--------------------|

# 20.4 Frequency Options

Table 83This table shows the expected frequency values for the platform frequency when using a CCB clock to SYSCLK ratio in comparison to the memory bus clock speed.

| CCB to<br>SYSCLK Ratio |       | SYSCLK (MHz) |       |            |           |           |     |     |        |  |  |

|------------------------|-------|--------------|-------|------------|-----------|-----------|-----|-----|--------|--|--|

|                        | 16.66 | 25           | 33.33 | 41.66      | 66.66     | 83        | 100 | 111 | 133.33 |  |  |

|                        |       | L            |       | Platform/C | CB Freque | ency (MHz | )   | •   |        |  |  |

| 2                      |       |              |       |            |           |           |     |     |        |  |  |

| 3                      |       |              |       |            |           |           |     | 333 | 400    |  |  |

| 4                      |       |              |       |            |           | 333       | 400 | 445 | 533    |  |  |

| 5                      |       |              |       |            | 333       | 415       | 500 |     |        |  |  |

| 6                      |       |              |       |            | 400       | 500       |     | -   |        |  |  |

| 8                      |       |              |       | 333        | 533       |           | -   |     |        |  |  |

| 9                      |       |              |       | 375        |           |           |     |     |        |  |  |

| 10                     |       |              | 333   | 417        |           |           |     |     |        |  |  |

| 12                     |       |              | 400   | 500        |           |           |     |     |        |  |  |

| 16                     |       | 400          | 533   |            |           |           |     |     |        |  |  |

| 20                     | 333   | 500          |       | -          |           |           |     |     |        |  |  |

Table 83. Frequency Options of SYSCLK with Respect to Memory Bus Speeds

**Note:** Due to errata Gen 13 the max sys clk frequency must not exceed 100 MHz if the core clk frequency is below 1200 MHz.

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4              | 04/2009 | <ul> <li>In Table 1, "Absolute Maximum Ratings <sup>1</sup>," and in Table 2, "Recommended Operating Conditions," moved text, "MII management voltage" from LV<sub>DD</sub>/TV<sub>DD</sub> to OV<sub>DD</sub>, added "Ethernet management" to OVDD row of input voltage section.</li> <li>In Table 5, "SYSCLK AC Timing Specifications," added notes 7 and 8 to SYSCLK frequency and cycle time.</li> <li>In Table 36, "MII Management DC Electrical Characteristics," changed all instances of LV<sub>DD</sub>/OV<sub>DD</sub> to OV<sub>DD</sub>.</li> <li>Modified Section 16, "High-Speed Serial Interfaces (HSSI)," to reflect that there is only one SerDes.</li> <li>Modified DDR clk rate min from 133 to 166 MHz.</li> <li>Modified note in Table 75, "Processor Core Clocking Specifications (MPC8548E and MPC8547E), "."</li> <li>In Table 56, "Differential Transmitter (TX) Output Specifications," modified equations in Comments column, and changed all instances of "LO" to "L0." Also added note 8.</li> <li>In Table 57, "Differential Receiver (RX) Input Specifications," modified equations in Comments column, and in note 3, changed "TRX-EYE-MEDIAN-to-MAX-JITTER," to "T<sub>RX-EYE-MEDIAN-to-MAX-JITTER</sub>."</li> <li>Modified Table 83, "Frequency Options of SYSCLK with Respect to Memory Bus Speeds."</li> <li>Added a note on Section 4.1, "System Clock Timing," to limit the SYSCLK to 100 MHz if the core frequency is less than 1200 MHz</li> <li>In Table 71, "MPC8543E Pinout ListingTable 72, "MPC8547E Pinout ListingTable 73, "MPC8545E Pinout ListingTable 74, "MPC8543E Pinout Listing," added note 5 to LA[28:31].</li> <li>Added note to Table 83, "Frequency Options of SYSCLK with Respect to Memory Bus Speeds."</li> </ul>                                                                                                 |

| 3              | 01/2009 | <ul> <li>[Section 4.6, "Platform Frequency Requirements for PCI-Express and Serial RapidIO." Changed minimum frequency equation to be 527 MHz for PCI x8.</li> <li>In Table 5, added note 7.</li> <li>Section 4.5, "Platform to FIFO Restrictions." Changed platform clock frequency to 4.2.</li> <li>Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1Gb Mbps)—GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics." Added MII after GMII and add 'or 2.5 V' after 3.3 V.</li> <li>In Table 23, modified table title to include GMII, MII, RMII, and TBI.</li> <li>In Table 24 and Table 25, changed clock period minimum to 5.3.</li> <li>In Table 26, Table 27, Table 28, Table 29, and Table 30, removed subtitle from table title.</li> <li>In Table 30 and Figure 15, changed all instances of PMA to TSEC<i>n</i>.</li> <li>In Table 34, Table 35, Figure 18, and Figure 20, changed all instances of REF_CLK to TSEC<i>n</i>_TX_CLK.</li> <li>In Table 36, changed all instances of OV<sub>DD</sub> to LV<sub>DD</sub>/TV<sub>DD</sub>.</li> <li>In Table 36, changed all instances of OV<sub>DD</sub> to LV<sub>DD</sub>/TV<sub>DD</sub>.</li> <li>In Table 37, "MII Management AC Timing Specifications," changed MDC minimum clock pulse width high from 32 to 48 ns.</li> <li>Added new section, Section 16, "High-Speed Serial Interfaces (HSSI)."</li> <li>Section 16.1, "DC Requirements for PCI Express SD_REF_CLK and SD_REF_CLK." Added new paragraph.</li> <li>Section 17.1, "DC Requirements for Serial RapidIO SD_REF_CLK and SD_REF_CLK." Added new paragraph.</li> <li>Added information to Figure 63, both in figure and in note.</li> <li>Section 22.3, "Decoupling Recommendations." Modified the recommendation.</li> <li>Table 87, "Part Numbering Nomenclature." In Silicon Version column added Ver. 2.1.2.</li> </ul> |

## Table 88. Document Revision History (continued)