#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                             |

|---------------------------------|----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                         |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                       |

| Speed                           | 800MHz                                                               |

| Co-Processors/DSP               | Signal Processing; SPE                                               |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                     |

| Graphics Acceleration           | Νο                                                                   |

| Display & Interface Controllers | -                                                                    |

| Ethernet                        | 10/100/1000Mbps (4)                                                  |

| SATA                            | -                                                                    |

| USB                             | -                                                                    |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                     |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                     |

| Security Features               | -                                                                    |

| Package / Case                  | 783-BBGA, FCBGA                                                      |

| Supplier Device Package         | 783-FCBGA (29x29)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8543hxang |

|                                 |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- VRRP and HSRP support for seamless router fail-over

- Up to 16 exact-match MAC addresses supported

- Broadcast address (accept/reject)

- Hash table match on up to 512 multicast addresses

- Promiscuous mode

- Buffer descriptors backward compatible with MPC8260 and MPC860T 10/100 Ethernet programming models

- RMON statistics support

- 10-Kbyte internal transmit and 2-Kbyte receive FIFOs

- MII management interface for control and status

- Ability to force allocation of header information and buffer descriptors into L2 cache

- OCeaN switch fabric

- Full crossbar packet switch

- Reorders packets from a source based on priorities

- Reorders packets to bypass blocked packets

- Implements starvation avoidance algorithms

- Supports packets with payloads of up to 256 bytes

- Integrated DMA controller

- Four-channel controller

- All channels accessible by both the local and remote masters

- Extended DMA functions (advanced chaining and striding capability)

- Support for scatter and gather transfers

- Misaligned transfer capability

- Interrupt on completed segment, link, list, and error

- Supports transfers to or from any local memory or I/O port

- Selectable hardware-enforced coherency (snoop/no snoop)

- Ability to start and flow control each DMA channel from external 3-pin interface

- Ability to launch DMA from single write transaction

- Two PCI/PCI-X controllers

- PCI 2.2 and PCI-X 1.0 compatible

- One 32-/64-bit PCI/PCI-X port with support for speeds of up to 133 MHz (maximum PCI-X frequency in synchronous mode is 110 MHz)

- One 32-bit PCI port with support for speeds from 16 to 66 MHz (available when the other port is in 32-bit mode)

- Host and agent mode support

- 64-bit dual address cycle (DAC) support

- PCI-X supports multiple split transactions

- Supports PCI-to-memory and memory-to-PCI streaming

#### Overview

- Memory prefetching of PCI read accesses

- Supports posting of processor-to-PCI and PCI-to-memory writes

- PCI 3.3-V compatible

- Selectable hardware-enforced coherency

- Serial RapidIO<sup>™</sup> interface unit

- Supports RapidIO<sup>™</sup> Interconnect Specification, Revision 1.2

- Both  $1 \times$  and  $4 \times$  LP-serial link interfaces

- Long- and short-haul electricals with selectable pre-compensation

- Transmission rates of 1.25, 2.5, and 3.125 Gbaud (data rates of 1.0, 2.0, and 2.5 Gbps) per lane

- Auto detection of 1- and 4-mode operation during port initialization

- Link initialization and synchronization

- Large and small size transport information field support selectable at initialization time

- 34-bit addressing

- Up to 256 bytes data payload

- All transaction flows and priorities

- Atomic set/clr/inc/dec for read-modify-write operations

- Generation of IO\_READ\_HOME and FLUSH with data for accessing cache-coherent data at a remote memory system

- Receiver-controlled flow control

- Error detection, recovery, and time-out for packets and control symbols as required by the RapidIO specification

- Register and register bit extensions as described in part VIII (Error Management) of the RapidIO specification

- Hardware recovery only

- Register support is not required for software-mediated error recovery.

- Accept-all mode of operation for fail-over support

- Support for RapidIO error injection

- Internal LP-serial and application interface-level loopback modes

- Memory and PHY BIST for at-speed production test

- RapidIO-compatible message unit

- 4 Kbytes of payload per message

- Up to sixteen 256-byte segments per message

- Two inbound data message structures within the inbox

- Capable of receiving three letters at any mailbox

- Two outbound data message structures within the outbox

- Capable of sending three letters simultaneously

- Single segment multicast to up to 32 devIDs

- Chaining and direct modes in the outbox

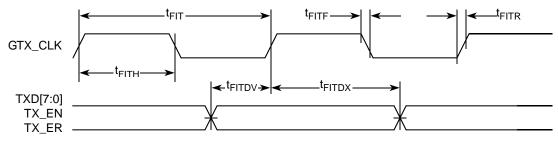

### A summary of the FIFO AC specifications appears in Table 24 and Table 25.

| Parameter/Condition                                    | Symbol                              | Min | Тур | Max  | Unit |

|--------------------------------------------------------|-------------------------------------|-----|-----|------|------|

| TX_CLK, GTX_CLK clock period                           | t <sub>FIT</sub>                    | 5.3 | 8.0 | 100  | ns   |

| TX_CLK, GTX_CLK duty cycle                             | t <sub>FITH</sub> /t <sub>FIT</sub> | 45  | 50  | 55   | %    |

| TX_CLK, GTX_CLK peak-to-peak jitter                    | t <sub>FITJ</sub>                   | —   | —   | 250  | ps   |

| Rise time TX_CLK (20%-80%)                             | t <sub>FITR</sub>                   | —   | —   | 0.75 | ns   |

| Fall time TX_CLK (80%–20%)                             | t <sub>FITF</sub>                   | —   | —   | 0.75 | ns   |

| FIFO data TXD[7:0], TX_ER, TX_EN setup time to GTX_CLK | t <sub>FITDV</sub>                  | 2.0 | —   | —    | ns   |

| GTX_CLK to FIFO data TXD[7:0], TX_ER, TX_EN hold time  | t <sub>FITDX</sub>                  | 0.5 | —   | 3.0  | ns   |

### Table 24. FIFO Mode Transmit AC Timing Specification

#### Table 25. FIFO Mode Receive AC Timing Specification

| Parameter/Condition                         | Symbol                              | Min | Тур | Max  | Unit |

|---------------------------------------------|-------------------------------------|-----|-----|------|------|

| RX_CLK clock period                         | t <sub>FIR</sub>                    | 5.3 | 8.0 | 100  | ns   |

| RX_CLK duty cycle                           | t <sub>FIRH</sub> /t <sub>FIR</sub> | 45  | 50  | 55   | %    |

| RX_CLK peak-to-peak jitter                  | t <sub>FIRJ</sub>                   | —   | —   | 250  | ps   |

| Rise time RX_CLK (20%-80%)                  | t <sub>FIRR</sub>                   | —   | —   | 0.75 | ns   |

| Fall time RX_CLK (80%–20%)                  | t <sub>FIRF</sub>                   | —   | —   | 0.75 | ns   |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>FIRDV</sub>                  | 1.5 | —   | —    | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>FIRDX</sub>                  | 0.5 |     |      | ns   |

#### Note:

1. The minimum cycle period of the TX\_CLK and RX\_CLK is dependent on the maximum platform frequency of the speed bins the part belongs to as well as the FIFO mode under operation. See Section 4.5, "Platform to FIFO Restrictions."

### Timing diagrams for FIFO appear in Figure 6 and Figure 7.

Figure 6. FIFO Transmit AC Timing Diagram

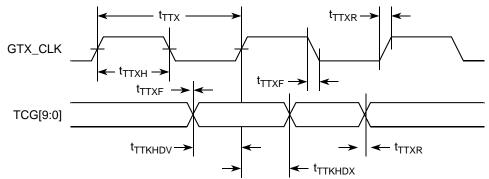

Figure 14 shows the TBI transmit AC timing diagram.

Figure 14. TBI Transmit AC Timing Diagram

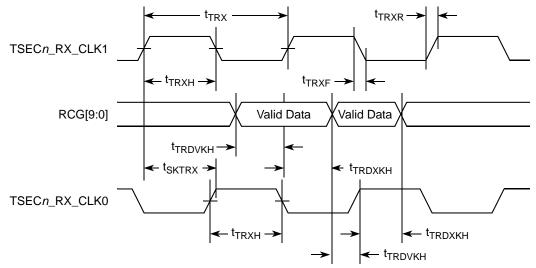

# 8.2.4.2 TBI Receive AC Timing Specifications

This table provides the TBI receive AC timing specifications.

| Table 31. TBI Receive AC | Timing Specifications |

|--------------------------|-----------------------|

|--------------------------|-----------------------|

| Parameter/Condition                                  | Symbol <sup>1</sup>                 | Min | Тур  | Мах | Unit |

|------------------------------------------------------|-------------------------------------|-----|------|-----|------|

| TSECn_RX_CLK[0:1] clock period                       | t <sub>TRX</sub>                    | —   | 16.0 | _   | ns   |

| TSECn_RX_CLK[0:1] skew                               | t <sub>SKTRX</sub>                  | 7.5 | _    | 8.5 | ns   |

| TSECn_RX_CLK[0:1] duty cycle                         | t <sub>TRXH</sub> /t <sub>TRX</sub> | 40  | _    | 60  | %    |

| RCG[9:0] setup time to rising TSECn_RX_CLK           | t <sub>TRDVKH</sub>                 | 2.5 | _    | _   | ns   |

| RCG[9:0] hold time to rising TSEC <i>n</i> _RX_CLK   | t <sub>TRDXKH</sub>                 | 1.5 | _    | _   | ns   |

| TSECn_RX_CLK[0:1] clock rise time (20%–80%)          | t <sub>TRXR</sub> <sup>2</sup>      | 0.7 | _    | 2.4 | ns   |

| TSEC <i>n</i> _RX_CLK[0:1] clock fall time (80%–20%) | t <sub>TRXF</sub> <sup>2</sup>      | 0.7 |      | 2.4 | ns   |

Notes:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>TRDVKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>TRDXKH</sub> symbolizes TBI receive timing (TR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>TRX</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TRX</sub> represents the TBI (T) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall). For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (TRX).</sub>

2. Guaranteed by design.

#### Enhanced Three-Speed Ethernet (eTSEC)

Figure 15 shows the TBI receive AC timing diagram.

Figure 15. TBI Receive AC Timing Diagram

# 8.2.5 TBI Single-Clock Mode AC Specifications

When the eTSEC is configured for TBI modes, all clocks are supplied from external sources to the relevant eTSEC interface. In single-clock TBI mode, when TBICON[CLKSEL] = 1, a 125-MHz TBI receive clock is supplied on the TSEC $n_RX_CLK$  pin (no receive clock is used on TSEC $n_TX_CLK$  in this mode, whereas for the dual-clock mode this is the PMA1 receive clock). The 125-MHz transmit clock is applied on the TSEC\_GTX\_CLK125 pin in all TBI modes.

A summary of the single-clock TBI mode AC specifications for receive appears in Table 32.

| Parameter/Condition                       | Symbol                 | Min | Тур | Max | Unit |

|-------------------------------------------|------------------------|-----|-----|-----|------|

| RX_CLK clock period                       | t <sub>TRRX</sub>      | 7.5 | 8.0 | 8.5 | ns   |

| RX_CLK duty cycle                         | t <sub>TRRH/TRRX</sub> | 40  | 50  | 60  | %    |

| RX_CLK peak-to-peak jitter                | t <sub>TRRJ</sub>      | —   | _   | 250 | ps   |

| Rise time RX_CLK (20%-80%)                | t <sub>TRRR</sub>      | —   | _   | 1.0 | ns   |

| Fall time RX_CLK (80%–20%)                | t <sub>TRRF</sub>      | —   | _   | 1.0 | ns   |

| RCG[9:0] setup time to RX_CLK rising edge | t <sub>trrdvkh</sub>   | 2.0 | _   | —   | ns   |

| RCG[9:0] hold time to RX_CLK rising edge  | t <sub>trrdxkh</sub>   | 1.0 | _   | —   | ns   |

| Parameter                                                                                      | Symbol           | Min  | Мах                    | Unit |

|------------------------------------------------------------------------------------------------|------------------|------|------------------------|------|

| Supply voltage 2.5 V                                                                           | BV <sub>DD</sub> | 2.37 | 2.63                   | V    |

| High-level input voltage                                                                       | V <sub>IH</sub>  | 1.70 | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                                        | V <sub>IL</sub>  | -0.3 | 0.7                    | V    |

| Input current<br>(BV <sub>IN</sub> <sup>1</sup> = 0 V or BV <sub>IN</sub> = BV <sub>DD</sub> ) | I <sub>IH</sub>  | _    | 10                     | μΑ   |

Table 50. GP<sub>IN</sub> DC Electrical Characteristics (2.5 V DC)

Note:

1. The symbol  $\mathsf{BV}_{\mathsf{IN}}$  in this case, represents the  $\mathsf{BV}_{\mathsf{IN}}$  symbol referenced in Table 1.

# 15 PCI/PCI-X

This section describes the DC and AC electrical specifications for the PCI/PCI-X bus of the device.

Note that the maximum PCI-X frequency in synchronous mode is 110 MHz.

# 15.1 PCI/PCI-X DC Electrical Characteristics

This table provides the DC electrical characteristics for the PCI/PCI-X interface.

Table 51. PCI/PCI-X DC Electrical Characteristics<sup>1</sup>

| Parameter                                                     | Symbol          | Min  | Мах                    | Unit | Notes |

|---------------------------------------------------------------|-----------------|------|------------------------|------|-------|

| High-level input voltage                                      | V <sub>IH</sub> | 2    | OV <sub>DD</sub> + 0.3 | V    | _     |

| Low-level input voltage                                       | V <sub>IL</sub> | -0.3 | 0.8                    | V    | —     |

| Input current ( $V_{IN} = 0 V \text{ or } V_{IN} = V_{DD}$ )  | I <sub>IN</sub> | —    | ±5                     | μA   | 2     |

| High-level output voltage ( $OV_{DD} = min, I_{OH} = -2 mA$ ) | V <sub>OH</sub> | 2.4  | —                      | V    | —     |

| Low-level output voltage ( $OV_{DD} = min, I_{OL} = 2 mA$ )   | V <sub>OL</sub> | —    | 0.4                    | V    | —     |

Notes:

1. Ranges listed do not meet the full range of the DC specifications of the PCI 2.2 Local Bus Specifications.

2. The symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

# 15.2 PCI/PCI-X AC Electrical Specifications

This section describes the general AC timing parameters of the PCI/PCI-X bus. Note that the clock reference CLK is represented by SYSCLK when the PCI controller is configured for synchronous mode and by PCIn\_CLK when it is configured for asynchronous mode.

#### PCI/PCI-X

### Table 54. PCI-X AC Timing Specifications at 133 MHz (continued)

| Parameter                                        | Symbol              | Min | Max | Unit | Notes |

|--------------------------------------------------|---------------------|-----|-----|------|-------|

| HRESET to PCI-X initialization pattern hold time | t <sub>PCRHIX</sub> | 0   | 50  | ns   | 6, 12 |

Notes:

1. See the timing measurement conditions in the PCI-X 1.0a Specification.

- 2. Minimum times are measured at the package pin (not the test point). Maximum times are measured with the test point and load circuit.

- 3. Setup time for point-to-point signals applies to REQ and GNT only. All other signals are bused.

- 4. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 5. Setup time applies only when the device is not driving the pin. Devices cannot drive and receive signals at the same time.

- 6. Maximum value is also limited by delay to the first transaction (time for HRESET high to first configuration access, t<sub>PCRHFV</sub>). The PCI-X initialization pattern control signals after the rising edge of HRESET must be negated no later than two clocks before the first FRAME and must be floated no later than one clock before FRAME is asserted.

- 7. A PCI-X device is permitted to have the minimum values shown for t<sub>PCKHOV</sub> and t<sub>CYC</sub> only in PCI-X mode. In conventional mode, the device must meet the requirements specified in PCI 2.2 for the appropriate clock frequency.

8. Device must meet this specification independent of how many outputs switch simultaneously.

9. The timing parameter t<sub>PCIVKH</sub> is a minimum of 1.4 ns rather than the minimum of 1.2 ns in the PCI-X 1.0a Specification.

- 10. The timing parameter t<sub>PCRHFV</sub> is a minimum of 10 clocks rather than the minimum of 5 clocks in the *PCI-X 1.0a Specification.*

- 11. Guaranteed by characterization.

12. Guaranteed by design.

# 16 High-Speed Serial Interfaces (HSSI)

The device features one Serializer/Deserializer (SerDes) interface to be used for high-speed serial interconnect applications. The SerDes interface can be used for PCI Express and/or serial RapidIO data transfers.

This section describes the common portion of SerDes DC electrical specifications, which is the DC requirement for SerDes reference clocks. The SerDes data lane's transmitter and receiver reference circuits are also shown.

# 16.1 Signal Terms Definition

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

Figure 38 shows how the signals are defined. For illustration purpose, only one SerDes lane is used for the description. The figure shows a waveform for either a transmitter output (SD\_TX and  $\overline{SD}_TX$ ) or a receiver input (SD\_RX and  $\overline{SD}_RX$ ). Each signal swings between A volts and B volts where A > B.

Using this waveform, the definitions are as follows. To simplify the illustration, the following definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signaling environment.

• Single-ended swing

The transmitter output signals and the receiver input signals SD\_TX,  $\overline{SD}_TX$ ,  $\overline{SD}_RX$  and  $\overline{SD}_RX$  each have a peak-to-peak swing of A – B volts. This is also referred as each signal wire's single-ended swing.

- Differential output voltage,  $V_{OD}$  (or differential output swing): The differential output voltage (or swing) of the transmitter,  $V_{OD}$ , is defined as the difference of the two complimentary output voltages:  $V_{SD_TX} - V_{\overline{SD_TX}}$ . The  $V_{OD}$  value can be either positive or negative.

- Differential input voltage, V<sub>ID</sub> (or differential input swing): The differential input voltage (or swing) of the receiver, V<sub>ID</sub>, is defined as the difference of the two complimentary input voltages: V<sub>SD\_RX</sub> – V<sub>SD\_RX</sub>. The V<sub>ID</sub> value can be either positive or negative.

- Differential peak voltage,  $V_{DIFFp}$ The peak value of the differential transmitter output signal or the differential receiver input signal is defined as differential peak voltage,  $V_{DIFFp} = |A - B|$  volts.

- Differential peak-to-peak,  $V_{DIFFp-p}$ Because the differential output signal of the transmitter and the differential input signal of the receiver each range from A – B to –(A – B) volts, the peak-to-peak value of the differential transmitter output signal or the differential receiver input signal is defined as differential peak-to-peak voltage,  $V_{DIFFp-p} = 2 \times V_{DIFFp} = 2 \times |(A - B)|$  volts, which is twice of differential swing in amplitude, or twice of the differential peak. For example, the output differential peak-to-peak voltage can also be calculated as  $V_{TX-DIFFp-p} = 2 \times |V_{OD}|$ .

- Common mode voltage,  $V_{cm}$ The common mode voltage is equal to one half of the sum of the voltages between each conductor

# 17 PCI Express

This section describes the DC and AC electrical specifications for the PCI Express bus of the MPC8548E.

# 17.1 <u>DC Requirements</u> for PCI Express SD\_REF\_CLK and SD\_REF\_CLK

For more information, see Section 16.2, "SerDes Reference Clocks."

# **17.2 AC Requirements for PCI Express SerDes Clocks**

Table 55 lists the AC requirements for the PCI Express SerDes clocks.

| Table 55. SD_I | REF_CLK and SD | D_REF_CLK AC Re | quirements |

|----------------|----------------|-----------------|------------|

|----------------|----------------|-----------------|------------|

| Symbol             | Parameter Description                                                                     | Min | Тур | Max | Unit | Notes |

|--------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|------|-------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                         |     | 10  | —   | ns   | 1     |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles. | _   | —   | 100 | ps   | —     |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location.              | -50 |     | 50  | ps   | —     |

Note:

1. Typical based on PCI Express Specification 2.0.

# 17.3 Clocking Dependencies

The ports on the two ends of a link must transmit data at a rate that is within 600 parts per million (ppm) of each other at all times. This is specified to allow bit rate clock sources with a  $\pm$ 300 ppm tolerance.

# 17.4 Physical Layer Specifications

The following is a summary of the specifications for the physical layer of PCI Express on this device. For further details as well as the specifications of the transport and data link layer see *PCI Express Base Specification. Rev. 1.0a.*

# 17.4.1 Differential Transmitter (TX) Output

Table 56 defines the specifications for the differential output at all transmitters (TXs). The parameters are specified at the component pins.

#### PCI Express

The eye diagram must be valid for any 250 consecutive UIs.

A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The eye diagram is created using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI.

# NOTE

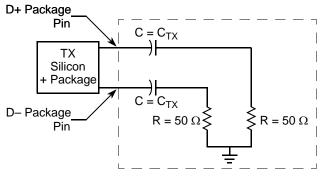

The reference impedance for return loss measurements is 50. to ground for both the D+ and D– line (that is, as measured by a vector network analyzer with 50- $\Omega$  probes—see Figure 50). Note that the series capacitors, CTX, are optional for the return loss measurement.

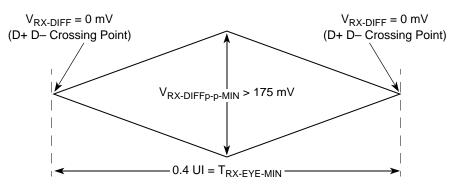

Figure 49. Minimum Receiver Eye Timing and Voltage Compliance Specification

# 17.5.1 Compliance Test and Measurement Load

The AC timing and voltage parameters must be verified at the measurement point, as specified within 0.2 inches of the package pins, into a test/measurement load shown in Figure 50.

# NOTE

The allowance of the measurement point to be within 0.2 inches of the package pins is meant to acknowledge that package/board routing may benefit from D+ and D- not being exactly matched in length at the package pin boundary.

Figure 50. Compliance Test/Measurement Load

# 18.8 Receiver Eye Diagrams

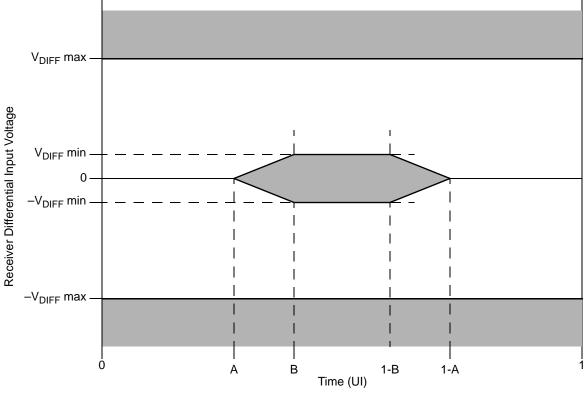

For each baud rate at which an LP-serial receiver is specified to operate, the receiver shall meet the corresponding bit error rate specification (Table 66, Table 67, and Table 68) when the eye pattern of the receiver test signal (exclusive of sinusoidal jitter) falls entirely within the unshaded portion of the receiver input compliance mask shown in Figure 54 with the parameters specified in Table 69. The eye pattern of the receiver test signal is measured at the input pins of the receiving device with the device replaced with a  $100-\Omega \pm 5\%$  differential resistive load.

Figure 54. Receiver Input Compliance Mask

Table 69. Receiver Input Compliance Mask Parameters Exclusive of Sinusoidal Jitter

| Receiver Type | V <sub>DIFF</sub> min<br>(mV) | V <sub>DIFF</sub> max<br>(mV) | A (UI) | B (UI) |

|---------------|-------------------------------|-------------------------------|--------|--------|

| 1.25 GBaud    | 100                           | 800                           | 0.275  | 0.400  |

| 2.5 GBaud     | 100                           | 800                           | 0.275  | 0.400  |

| 3.125 GBaud   | 100                           | 800                           | 0.275  | 0.400  |

# **18.9 Measurement and Test Requirements**

Since the LP-serial electrical specification are guided by the XAUI electrical interface specified in Clause 47 of IEEE Std. 802.3ae-2002, the measurement and test requirements defined here are similarly guided by Clause 47. Additionally, the CJPAT test pattern defined in Annex 48A of IEEE Std.

| Signal           | gnal Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    | Power<br>Supply  | Notes        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------|--------------|

|                  | Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                    |                  | 1            |

| RTC              | AF16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | —            |

| SYSCLK           | AH17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | —            |

|                  | JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    |                  | 1            |

| ТСК              | AG28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | —            |

| TDI              | AH28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 12           |

| TDO              | AF28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                  | OV <sub>DD</sub> | _            |

| TMS              | AH27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 12           |

| TRST             | AH23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 12           |

|                  | DFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                    |                  |              |

| L1_TSTCLK        | AC25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 25           |

| L2_TSTCLK        | AE22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 25           |

| LSSD_MODE        | AH20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 25           |

| TEST_SEL         | AH14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 25           |

|                  | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |                  |              |

| THERM0           | AG1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                  | _                | 14           |

| THERM1           | AH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                  |                  | 14           |

|                  | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                    |                  |              |

| ASLEEP           | AH18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                  | OV <sub>DD</sub> | 9, 19,<br>29 |

|                  | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                    |                  | •            |

| GND              | <ul> <li>A11, B7, B24, C1, C3, C5, C12, C15, C26, D8,<br/>D11, D16, D20, D22, E1, E5, E9, E12, E15, E17,<br/>F4, F26, G12, G15, G18, G21, G24, H2, H6, H8,<br/>H28, J4, J12, J15, J17, J27, K7, K9, K11, K27,<br/>L3, L5, L12, L16, N11, N13, N15, N17, N19, P4,<br/>P9, P12, P14, P16, P18, R11, R13, R15, R17,<br/>R19, T4, T12, T14, T16, T18, U8, U11, U13,<br/>U15, U17, U19, V4, V12, V18, W6, W19, Y4, Y9,<br/>Y11, Y19, AA6, AA14, AA17, AA22, AA23, AB4,<br/>AC2, AC11, AC19, AC26, AD5, AD9, AD22,<br/>AE3, AE14, AF6, AF10, AF13, AG8, AG27,<br/>K28, L24, L26, N24, N27, P25, R28, T24, T26,<br/>U24, V25, W28, Y24, Y26, AA24, AA27, AB25,<br/>AC28, L21, L23, N22, P20, R23, T21, U22, V20,<br/>W23, Y21, U27</li> </ul> | _                                                  |                  |              |

| OV <sub>DD</sub> | V16, W11, W14, Y18, AA13, AA21, AB11,<br>AB17, AB24, AC4, AC9, AC21, AD6, AD13,<br>AD17, AD19, AE10, AE8, AE24, AF4, AF12,<br>AF22, AF27, AG26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Power for PCI<br>and other<br>standards<br>(3.3 V) | OV <sub>DD</sub> | _            |

Table 72 provides the pin-out listing for the MPC8547E 783 FC-PBGA package.

### NOTE

All note references in the following table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

| Signal                          | Package Pin Number                                                                                                                                                                                                    |     | Power<br>Supply  | Notes    |  |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------|----------|--|--|

| PCI1 (One 64-Bit or One 32-Bit) |                                                                                                                                                                                                                       |     |                  |          |  |  |

| PCI1_AD[63:32]                  | PCI1_AD[63:32] AB14, AC15, AA15, Y16, W16, AB16, AC16,<br>AA16, AE17, AA18, W18, AC17, AD16, AE16,<br>Y17, AC18, AB18, AA19, AB19, AB21, AA20,<br>AC20, AB20, AB22, AC22, AD21, AB23, AF23,<br>AD23, AE23, AC23, AC24 |     |                  |          |  |  |

| PCI1_AD[31:0]                   | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15                         | I/O | OV <sub>DD</sub> | 17       |  |  |

| PCI1_C_BE[7:4]                  | AF15, AD14, AE15, AD15                                                                                                                                                                                                | I/O | OV <sub>DD</sub> | 17       |  |  |

| PCI1_C_BE[3:0]                  | AF9, AD11, Y12, Y13                                                                                                                                                                                                   | I/O | OV <sub>DD</sub> | 17       |  |  |

| PCI1_PAR64                      | W15                                                                                                                                                                                                                   | I/O | OV <sub>DD</sub> | —        |  |  |

| PCI1_GNT[4:1]                   | AG6, AE6, AF5, AH5                                                                                                                                                                                                    | 0   | OV <sub>DD</sub> | 5, 9, 35 |  |  |

| PCI1_GNT0                       | AG5                                                                                                                                                                                                                   | I/O | OV <sub>DD</sub> | —        |  |  |

| PCI1_IRDY                       | AF11                                                                                                                                                                                                                  | I/O | OV <sub>DD</sub> | 2        |  |  |

| PCI1_PAR                        | AD12                                                                                                                                                                                                                  | I/O | OV <sub>DD</sub> | —        |  |  |

| PCI1_PERR                       | AC12                                                                                                                                                                                                                  | I/O | OV <sub>DD</sub> | 2        |  |  |

| PCI1_SERR                       | V13                                                                                                                                                                                                                   | I/O | OV <sub>DD</sub> | 2, 4     |  |  |

| PCI1_STOP                       | W12                                                                                                                                                                                                                   | I/O | OV <sub>DD</sub> | 2        |  |  |

| PCI1_TRDY                       | AG11                                                                                                                                                                                                                  | I/O | OV <sub>DD</sub> | 2        |  |  |

| PCI1_REQ[4:1]                   | AH2, AG4, AG3, AH4                                                                                                                                                                                                    | I   | OV <sub>DD</sub> | —        |  |  |

| PCI1_REQ0                       | AH3                                                                                                                                                                                                                   | I/O | OV <sub>DD</sub> | —        |  |  |

| PCI1_CLK                        | AH26                                                                                                                                                                                                                  | I   | OV <sub>DD</sub> | 39       |  |  |

| PCI1_DEVSEL                     | AH11                                                                                                                                                                                                                  | I/O | OV <sub>DD</sub> | 2        |  |  |

| PCI1_FRAME                      | AE11                                                                                                                                                                                                                  | I/O | OV <sub>DD</sub> | 2        |  |  |

| PCI1_IDSEL                      | AG9                                                                                                                                                                                                                   | I   | OV <sub>DD</sub> | —        |  |  |

| PCI1_REQ64                      | AF14                                                                                                                                                                                                                  | I/O | OV <sub>DD</sub> | 2, 5,10  |  |  |

| PCI1_ACK64                      | V15                                                                                                                                                                                                                   | I/O | OV <sub>DD</sub> | 2        |  |  |

| Reserved                        | AE28                                                                                                                                                                                                                  | —   | —                | 2        |  |  |

| Reserved                        | AD26                                                                                                                                                                                                                  | _   | —                | 2        |  |  |

| Reserved                        | AD25                                                                                                                                                                                                                  | —   | —                | 2        |  |  |

### Table 72. MPC8547E Pinout Listing

Package Description

| Table 72 | . MPC8547E | <b>Pinout Listing</b> | (continued) |

|----------|------------|-----------------------|-------------|

|----------|------------|-----------------------|-------------|

| Signal       | Signal Package Pin Number                                                                                                                                                                                                                                                                                        |     |                  | Notes |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------|-------|

| Reserved     | AE26                                                                                                                                                                                                                                                                                                             | —   | —                | 2     |

| cfg_pci1_clk | AG24                                                                                                                                                                                                                                                                                                             | I   | OV <sub>DD</sub> | 5     |

| Reserved     | AF25                                                                                                                                                                                                                                                                                                             | _   | —                | 101   |

| Reserved     | AE25                                                                                                                                                                                                                                                                                                             | _   | —                | 2     |

| Reserved     | AG25                                                                                                                                                                                                                                                                                                             | _   | —                | 2     |

| Reserved     | AD24                                                                                                                                                                                                                                                                                                             | _   | —                | 2     |

| Reserved     | AF24                                                                                                                                                                                                                                                                                                             | _   | —                | 2     |

| Reserved     | AD27                                                                                                                                                                                                                                                                                                             | —   | —                | 2     |

| Reserved     | AD28, AE27, W17, AF26                                                                                                                                                                                                                                                                                            | _   | —                | 2     |

| Reserved     | AH25                                                                                                                                                                                                                                                                                                             | _   | —                | 2     |

|              | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                                       |     |                  | 1     |

| MDQ[0:63]    | L18, J18, K14, L13, L19, M18, L15, L14, A17,<br>B17, A13, B12, C18, B18, B13, A12, H18, F18,<br>J14, F15, K19, J19, H16, K15, D17, G16, K13,<br>D14, D18, F17, F14, E14, A7, A6, D5, A4, C8,<br>D7, B5, B4, A2, B1, D1, E4, A3, B2, D2, E3, F3,<br>G4, J5, K5, F6, G5, J6, K4, J1, K2, M5, M3, J3,<br>J2, L1, M6 | I/O | GV <sub>DD</sub> | _     |

| MECC[0:7]    | H13, F13, F11, C11, J13, G13, D12, M12                                                                                                                                                                                                                                                                           | I/O | GV <sub>DD</sub> | —     |

| MDM[0:8]     | M17, C16, K17, E16, B6, C4, H4, K1, E13                                                                                                                                                                                                                                                                          | 0   | GV <sub>DD</sub> | —     |

| MDQS[0:8]    | M15, A16, G17, G14, A5, D3, H1, L2, C13                                                                                                                                                                                                                                                                          | I/O | GV <sub>DD</sub> | —     |

| MDQS[0:8]    | L17, B16, J16, H14, C6, C2, H3, L4, D13                                                                                                                                                                                                                                                                          | I/O | GV <sub>DD</sub> | —     |

| MA[0:15]     | A8, F9, D9, B9, A9, L10, M10, H10, K10, G10,<br>B8, E10, B10, G6, A10, L11                                                                                                                                                                                                                                       | 0   | GV <sub>DD</sub> | _     |

| MBA[0:2]     | F7, J7, M11                                                                                                                                                                                                                                                                                                      | 0   | GV <sub>DD</sub> | —     |

| MWE          | E7                                                                                                                                                                                                                                                                                                               | 0   | GV <sub>DD</sub> | —     |

| MCAS         | H7                                                                                                                                                                                                                                                                                                               | 0   | GV <sub>DD</sub> | —     |

| MRAS         | L8                                                                                                                                                                                                                                                                                                               | 0   | GV <sub>DD</sub> | —     |

| MCKE[0:3]    | F10, C10, J11, H11                                                                                                                                                                                                                                                                                               | 0   | GV <sub>DD</sub> | 11    |

| MCS[0:3]     | K8, J8, G8, F8                                                                                                                                                                                                                                                                                                   | 0   | GV <sub>DD</sub> | —     |

| MCK[0:5]     | H9, B15, G2, M9, A14, F1                                                                                                                                                                                                                                                                                         | 0   | GV <sub>DD</sub> | —     |

| MCK[0:5]     | J9, A15, G1, L9, B14, F2                                                                                                                                                                                                                                                                                         | 0   | GV <sub>DD</sub> | —     |

| MODT[0:3]    | E6, K6, L7, M7                                                                                                                                                                                                                                                                                                   | 0   | GV <sub>DD</sub> | —     |

| MDIC[0:1]    | A19, B19                                                                                                                                                                                                                                                                                                         | I/O | GV <sub>DD</sub> | 36    |

Package Description

| Table 72. | MPC8547E | <b>Pinout Listing</b> | (continued) |

|-----------|----------|-----------------------|-------------|

|-----------|----------|-----------------------|-------------|

| Signal             | Signal Package Pin Number Pin Type               |       | Power<br>Supply  | Notes    |  |

|--------------------|--------------------------------------------------|-------|------------------|----------|--|

| IRQ[0:7]           | AG23, AF18, AE18, AF20, AG18, AF17, AH24, AE20   | I     | OV <sub>DD</sub> | _        |  |

| IRQ[8]             | AF19                                             | I     | OV <sub>DD</sub> |          |  |

| IRQ[9]/DMA_DREQ3   | AF21                                             | I     | OV <sub>DD</sub> | 1        |  |

| IRQ[10]/DMA_DACK3  | AE19                                             | I/O   | OV <sub>DD</sub> | 1        |  |

| IRQ[11]/DMA_DDONE3 | AD20                                             | I/O   | OV <sub>DD</sub> | 1        |  |

| IRQ_OUT            | AD18                                             | 0     | OV <sub>DD</sub> | 2, 4     |  |

|                    | Ethernet Management Interface                    |       |                  |          |  |

| EC_MDC             | AB9                                              | 0     | OV <sub>DD</sub> | 5, 9     |  |

| EC_MDIO            | AC8                                              | I/O   | OV <sub>DD</sub> | —        |  |

|                    | Gigabit Reference Clock                          |       |                  |          |  |

| EC_GTX_CLK125      | V11                                              | I     | LV <sub>DD</sub> | —        |  |

|                    | Three-Speed Ethernet Controller (Gigabit Etherne | et 1) |                  |          |  |

| TSEC1_RXD[7:0]     | R5, U1, R3, U2, V3, V1, T3, T2                   | I     | LV <sub>DD</sub> | —        |  |

| TSEC1_TXD[7:0]     | T10, V7, U10, U5, U4, V6, T5, T8                 | 0     | LV <sub>DD</sub> | 5, 9     |  |

| TSEC1_COL          | R4                                               | I     | LV <sub>DD</sub> | —        |  |

| TSEC1_CRS          | V5                                               | I/O   | LV <sub>DD</sub> | 20       |  |

| TSEC1_GTX_CLK      | U7                                               | 0     | LV <sub>DD</sub> | —        |  |

| TSEC1_RX_CLK       | U3                                               | I     | LV <sub>DD</sub> | —        |  |

| TSEC1_RX_DV        | V2                                               | I     | LV <sub>DD</sub> | —        |  |

| TSEC1_RX_ER        | T1                                               | I     | LV <sub>DD</sub> | —        |  |

| TSEC1_TX_CLK       | Т6                                               | I     | LV <sub>DD</sub> |          |  |

| TSEC1_TX_EN        | U9                                               | 0     | LV <sub>DD</sub> | 30       |  |

| TSEC1_TX_ER        | Т7                                               | 0     | LV <sub>DD</sub> | —        |  |

|                    | Three-Speed Ethernet Controller (Gigabit Etherne | et 2) |                  |          |  |

| TSEC2_RXD[7:0]     | P2, R2, N1, N2, P3, M2, M1, N3                   | I     | LV <sub>DD</sub> | —        |  |

| TSEC2_TXD[7:0]     | N9, N10, P8, N7, R9, N5, R8, N6                  | 0     | LV <sub>DD</sub> | 5, 9, 33 |  |

| TSEC2_COL          | P1                                               | I     | LV <sub>DD</sub> | —        |  |

| TSEC2_CRS          | R6                                               | I/O   | LV <sub>DD</sub> | 20       |  |

| TSEC2_GTX_CLK      | P6                                               | 0     | LV <sub>DD</sub> | —        |  |

| TSEC2_RX_CLK       | N4                                               | I     | LV <sub>DD</sub> | —        |  |

| TSEC2_RX_DV        | P5                                               | l     | LV <sub>DD</sub> | -        |  |

| TSEC2_RX_ER        | R1                                               | l     | LV <sub>DD</sub> | —        |  |

| TSEC2_TX_CLK       | P10                                              | I     | LV <sub>DD</sub> | -        |  |

| TSEC2_TX_EN        | P7                                               | 0     | LV <sub>DD</sub> | 30       |  |

Package Description

| Signal         | Package Pin Number                                                                                                                                                                                                                                                                                               | Pin Type | Power<br>Supply  | Notes |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| PCI1_TRDY      | AG11                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2     |

| PCI1_REQ[4:1]  | AH2, AG4, AG3, AH4                                                                                                                                                                                                                                                                                               | I        | OV <sub>DD</sub> |       |

| PCI1_REQ0      | AH3                                                                                                                                                                                                                                                                                                              | I/O      | OV <sub>DD</sub> | —     |

| PCI1_CLK       | AH26                                                                                                                                                                                                                                                                                                             | I        | OV <sub>DD</sub> | 39    |

| PCI1_DEVSEL    | AH11                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2     |

| PCI1_FRAME     | AE11                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2     |

| PCI1_IDSEL     | AG9                                                                                                                                                                                                                                                                                                              | I        | OV <sub>DD</sub> | _     |

| cfg_pci1_width | AF14                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 112   |

| Reserved       | V15                                                                                                                                                                                                                                                                                                              | —        | _                | 110   |

| Reserved       | AE28                                                                                                                                                                                                                                                                                                             | —        | —                | 2     |

| Reserved       | AD26                                                                                                                                                                                                                                                                                                             | —        | _                | 110   |

| Reserved       | AD25                                                                                                                                                                                                                                                                                                             | —        | _                | 110   |

| Reserved       | AE26                                                                                                                                                                                                                                                                                                             | —        | —                | 110   |

| cfg_pci1_clk   | AG24                                                                                                                                                                                                                                                                                                             | I        | OV <sub>DD</sub> | 5     |

| Reserved       | AF25                                                                                                                                                                                                                                                                                                             | —        | _                | 101   |

| Reserved       | AE25                                                                                                                                                                                                                                                                                                             | _        | —                | 110   |

| Reserved       | AG25                                                                                                                                                                                                                                                                                                             | —        | _                | 110   |

| Reserved       | AD24                                                                                                                                                                                                                                                                                                             | —        | _                | 110   |

| Reserved       | AF24                                                                                                                                                                                                                                                                                                             | —        | _                | 110   |

| Reserved       | AD27                                                                                                                                                                                                                                                                                                             | —        | _                | 110   |